Изобретение относится к вычислительной технике и может быть использовано в качестве расширителей в специализированных вычислителях.

Целью изобретения является повышение быстродействия за счет уменьшения числа итераций.

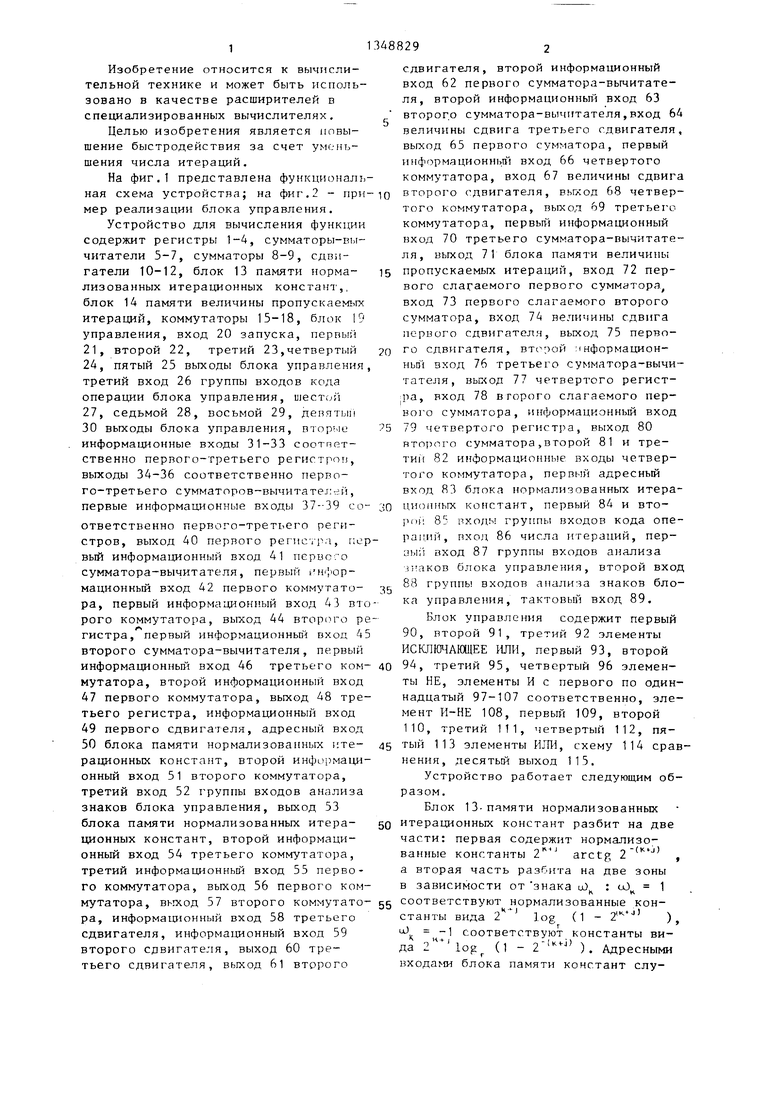

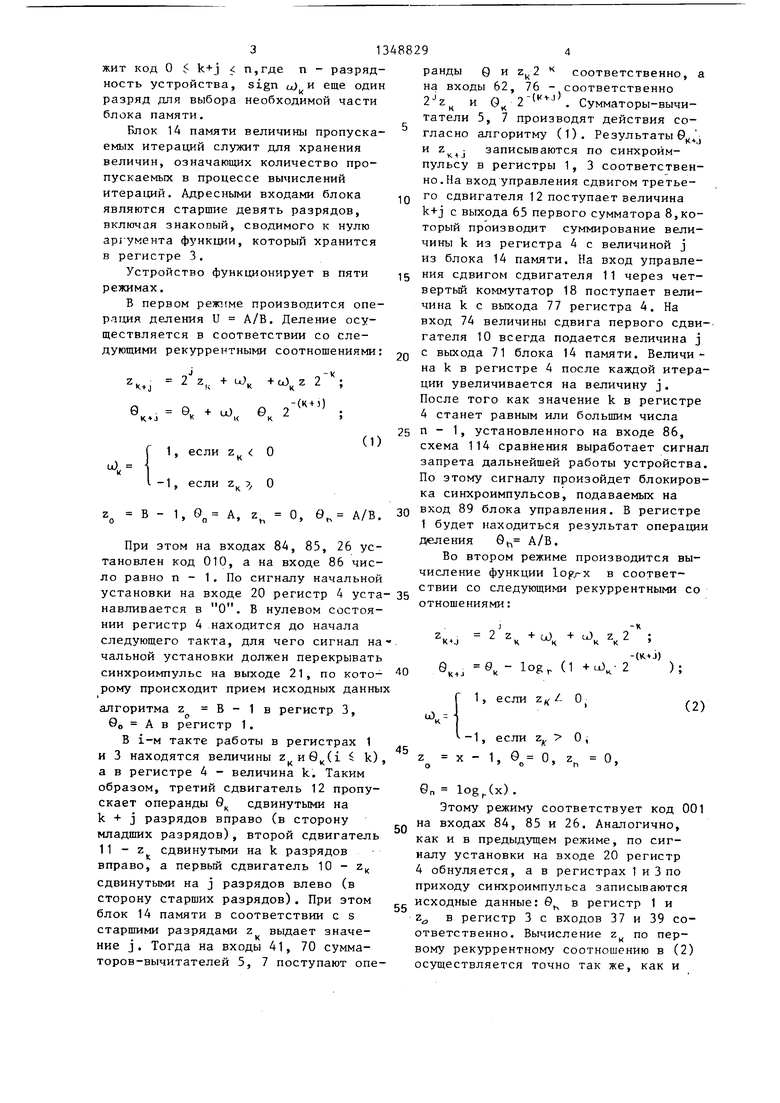

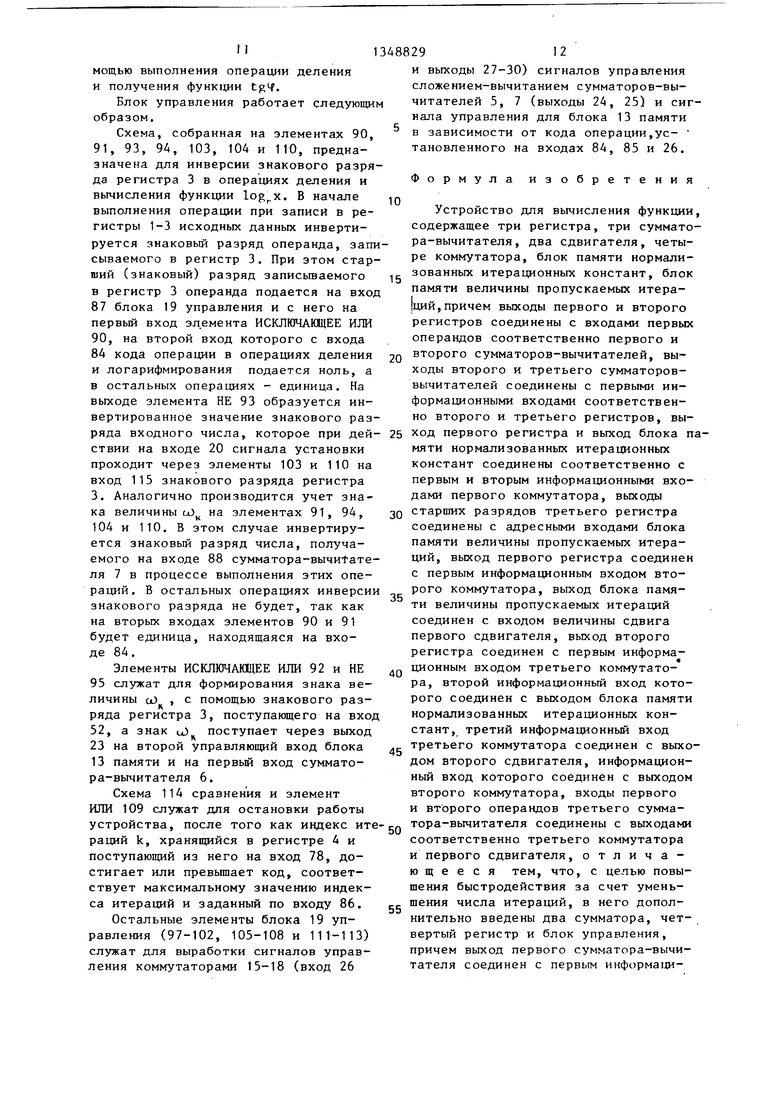

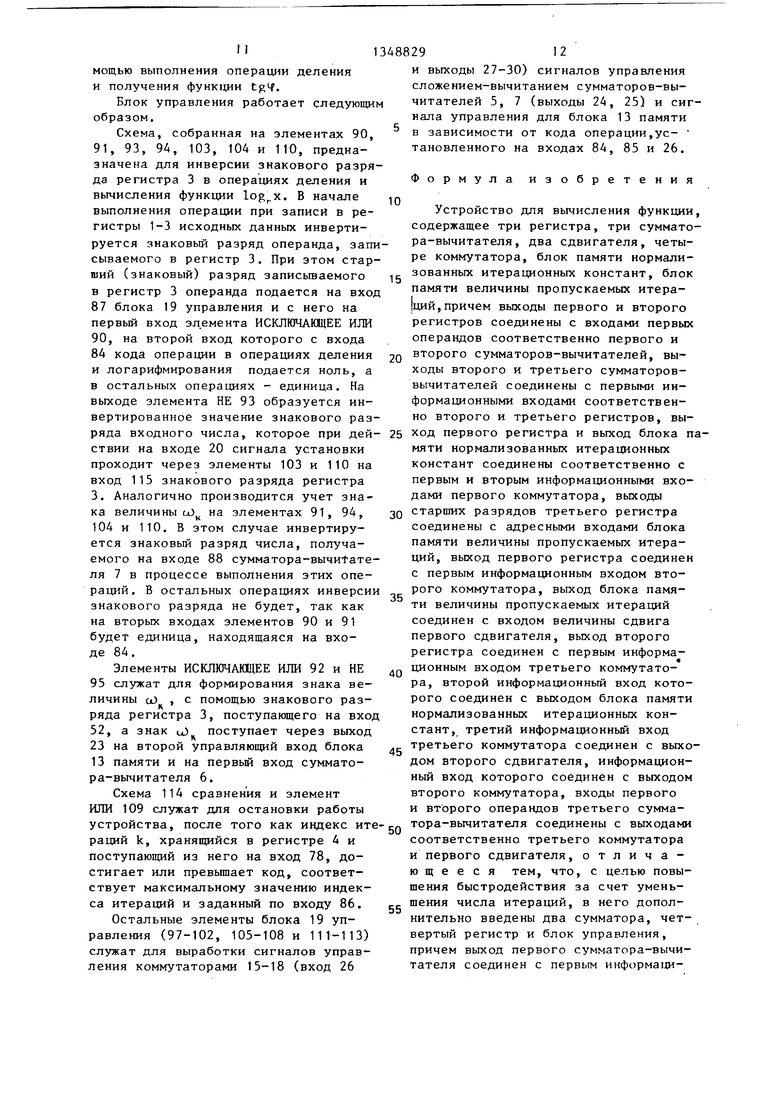

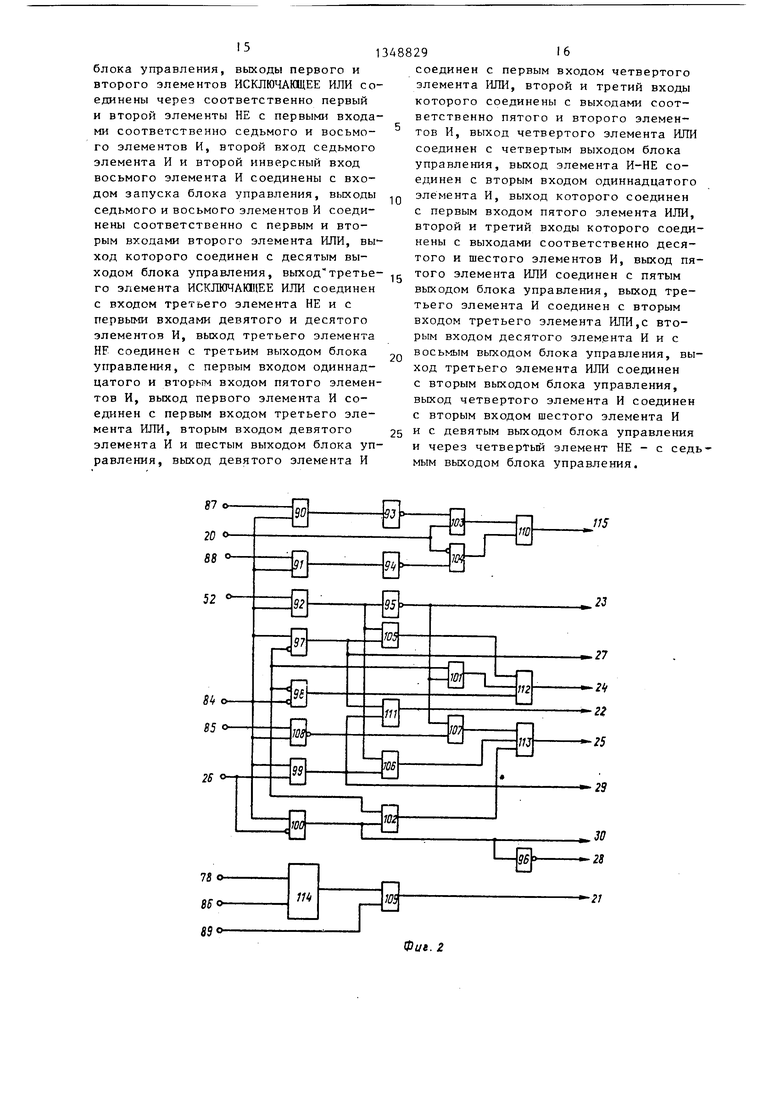

На фиг. 1 представлена функционал1 ная схема устройства; на фиг.2 - пример реализации блока управления.

Устройство для вычисления функции содержит регистры 1-4, сумматоры-вы- читатели 5-7, сумматоры 8-9, сдви- гатели 10-12, блок 13 памяти нормализованных итерационных констант,, блок 14 памяти величины nponycKaeMi rx итераций, коммутаторы 15-18, блок 19 управления, вход 20 запуска, первый 21, второй 22, третий 23,четвертый 24, пятый 25 выходы блока управления третий вход 26 группы входов кода операции блока управления, шестсл 27, седьмой 28, восьмой 29, депятыи 30 выходы блока управления, вторые информационные входы 31-33 соотпет- ственно первого-третьего регистрот, выходы 34-36 соответственно первого-третьего сумматоров-вычитате.г:еГ1, первые информационные входы 37--39 соответственно первого-третьего регистров, выход 40 первого periic ,-pa, г;ер вый информационный вход 41 первого сумматора-вычитателя, первый 1 нфор- мационный вход 42 первого коммутатора, первый информационный вход 43 вю рого коммутатора, выход 44 второго ре « , г

гистра, первый информационньш вход 4Ь второго сумматора-вычитателя, первый информационный вход 46 третьего коммутатора, второй информационный вход 47 первого коммутатора, выход 48 третьего регистра, информационный вход

49первого сдвигателя, адресный вход

50блока памяти нормализованных итерационных констант, второй инфо15маци- онный вход 51 второго коммутатора, третий вход 52 группы входов анализа знаков блока управления, выход 53 блока памяти нормализованных итерационных констант, второй информационный вход 54 третьего коммутатора, третий информационный вход 55 первого коммутатора, выход 56 первого коммутатора, выход 57 второго коммутатора, информационный вход 58 третьего сдвигателя, информационный вход 59 второго сдвигателя, выход 60 третьего сдвигателя, выход 61 второго

сдвигателя, второй информационный вход 62 первого сумматора-вьмитате- ля, второй информационный вход 63 второго сумматора-вычитателя,вход 64 величины сдвига третьего сдвигателя, выход 65 первого сумматора, первый информационньш вход 66 четвертого коммутатора, вход 67 величины сдвига

второго сдвигателя, выход 68 четвертого коммутатора, выход 69 третьего коммутатора, первьгй информационный вход 70 третьего сумматора-вычитателя, выход 71 блока памяти величины

пропускаемых итера1у й, вход 72 первого слагаемого первого сумматора вход 73 первого слагаемого второго сумматора, вход 74 величины сдвига пс-рвого сдвигателя, выход 75 первого сдвигателя, второй жформапион- ный вход 76 третьего сумматора-вычитателя, вькод 77 четвертого регистра, вход 78 второго слагаемого первого сумматора, информационный вход

79 четвертого регистра, выход 80 второго сумматора,второй 81 и третий 82 информационные входы четвертого коммутатора, первый адресный вход 83 блока нормализованных итерациопиых констант, первый 84 и вто- {UHi 85 входы группы входов кода операций, пход 86 числа итераций, пер- 3bi; i вход 87 группы входов анализа знаков блока управления, второй вход 88 группы входов анализа знаков блока управления, тактовый вход 89.

Блок управления содержит первый 90, второй 91, третий 92 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый 93, второй

94, третий 95, четвертый 96 элементы НЕ, элементы И с первого по одиннадцатый 97-107 соответственно, элемент И-НЕ 108, первый 109, второй 110, третий 111, четвертый 112, пятый 113 элементы , схему 114 сравнения, десятый выход 115.

Устройство работает следующим образом.

Блок 13-памяти нормализованных

итерационных констант разбит на две части: первая содержит нормализованные константы arctg , а вторая часть разбита на две зоны в зависимости от знака и) : оО 1

соответствуют нормализованные константы вида 2 log (1 - ), Jj, -1 соответствуют константы вида (1 - ). Адресными входами блока памяти констант слу

жит код о 6 k-t-j п,где ность устройства.

sign и)ч

п - разряд- еще один

разряд для выбора необходимой части блока памяти.

Блок 14 памяти величины пропускаемых итераций служит для хранения величин, означающих количество пропускаемых в процессе вычислений итераций. Адресными входами блока являются старшие девять разрядов, включая знаковый, сводимого к нулю api-умента функции, который хранится в регистре 3.

Устройство функционирует в пяти режимах.

В первом режиме производится операция деления U А/В. Деление осуществляется в соответствии со следующими рекуррентными соотнощениями

2%,

+ Lj

+

е, + ио., е,. 2

2

-(K + J)

и),.

Z

О, 0 А/В.

При этом на входах 84, 85, 26 установлен код 010, а на входе 86 число равно п - 1. По сигналу начальной установки на входе 20 регистр 4 уста навливается в О. В нулевом состоянии регистр 4 находится до начала следующего такта, для чего сигнал начальной установки должен перекрывать синхроимпульс на выходе 21, по кото- рому происходит прием исходных данны

алгоритма z В - 1 в регистр 3, ©о А в регистр 1.

В i-M такте работы в регистрах 1 и 3 находятся величины 0(1 i k) а в регистре 4 - величина k. Таким образом, третий сдвигатель 12 пропускает операнды 0, сдвинутыми на k+j разрядов вправо (в сторону младших разрядов), второй сдвигатель 11 - вправо,

сдвинутыми на j разрядов влево (в сторону старших разрядов). При этом блок 14 памяти в соответствии с s

z сдвинутыми на k разрядов а первый сдвигатель 10

старшими разрядами z выдает значение j. Тогда на входы 41, 70 сумма- торов-вычитателей 5, 7 поступают one

10

15

20

25

30

- 35 х

и татели

ранды 0 и соответственно, а на входы 62, 76 - соответственно

Q 2 . Сумматоры-вычи- 5, 7 производят действия согласно алгоритму (1). Результаты 0„/.

(

и записываются по синхроимпульсу в регистры 1, 3 соответственно. На вход управления сдвигом третьего сдвигателя 12 поступает величина k+j с выхода 65 первого сумматора 8,который производит суммирование величины k из регистра А с величиной j из блока 14 памяти. На вход управления сдвигом сдвигателя 11 через четвертый коммутатор 18 поступает величина k с выхода 77 регистра 4. На вход 74 величины сдвига первого сдвигателя 10 всегда подается величина j с выхода 71 блока 14 памяти. Величи на k в регистре 4 после каждой итерации увеличивается на величину j. После того как значение k в регистре 4 станет равным или большим числа п - 1, установленного на входе 86, схема 114 сравнения выработает сигнал запрета дальнейшей работы устройства. По этому сигналу произойдет блокировка синхроимпульсов, подаваемых на вход 89 блока управления. В регистре 1 будет находиться результат операции деления 0 А/В.

Во втором режиме производится вычисление функции loprx в соответствии со следующими рекуррентными со отношениями:

K+J

2 z + м + иЗ

к2

-к

0, - log, (1 +u3,- 2 1, если z Л 0

-(K+J)

);

(2)

z X

-1, если z О,

- n 0 о,

z

о.

0

5

0п log,(x).

Этому режиму соответствует код 001 на входах 84, 85 и 26. Аналогично, как и в предыдущем режиме, по сигналу установки на входе 20 регистр 4 обнуляется, а в регистрах 1 и 3 по приходу синхроимпульса записываются исходные данные: 9 в регистр 1 и

z в регистр 3 с входов ответственно. Вычисление

37 и 39 со- z по первому рекуррентному соотношению в (2) осуществляется точно так же, как и

5

в операции деления. Вычисление 0 в соответствии с вторым рекуррентным соотношением (2) осуществляется следующим образом. На вход сдвигателя 12 через коммутатор 15 поступает константа 2 log (1 ± 2 ), считанная по адресу u)jjj из блока 13 памяти нормализованных итерационных констант. На вход управления сдвигом третьего сдвигателя 12 поступает величина j с выхода первого сумматора 8, и трети сдвигатель 12 производит сдвиг на j разрядов вправо, т.е. на информационный вход сумматора-вычитателя 5 подается log (1 ± 2- ), на управляющем входе в соответствии с кодом операции устанавливается 1 и сум- матор-вычитатель 5 производит операцию вычитания Qg-log C 112- ) . Ре- зультат вычитания в начале следующего такта записывается в регистр 1.

В i-M такте в регистре 1 находится величина 0 , в регистре 3 - z

В нулевом такте по сигналу уст новки по входу 20 происходит обну ление регистра 4 и по синхроимпул су на входе 21 запись исходных да в регистры 1-3: QO регистр 2, z в регистр 3. В соответстви с кодом операции на первом коммут торе 15 выбирается вход 42, на вт ром коммутаторе 16 - вход 43, на тьем коммутаторе 17 - вход 54 и н четвертом коммутаторе 18 - вход 6 В первом такте z из регистра 3

а в регистре 4 - k(k. i j). На выходе 35 ступает на вход 49 сдвигателя 10.

65 сумматора 8 получена величина k + J, которая подается на вход управления сдвигом третьего сдвигателя 12 и на вход 83 блока 13 памяти нормализованных итерационных констант. На другой вход блока 13 памяти в соответствии с кодом операции из блока 19 управления подается О, а на третий вход - значение со ,

К

вьфабатываемое в блоке 19 управления в зависимости от кода операции и знакового разряда регистра 3. В соответствии с гчтим адресом из блока 13 памяти считывается нормализованная константа log (1 + ), которая подается через первый коммутатор 15 на вход сдвигателя 12 и сдвинута в нем на k + j разрядов вправо. Результат сдвига подается на вход 62 сумматора-вычитателя 5, на вход 41 которого подается величина 9 .С выхода 34 сумматора-вычитателя 5 величина (1 -(- ) запишется по входу 31 в регистр 1, При достижении регистром 4 состояния п - 1 схема 114 сравнения выработает сигнал запрета и останавливает вычислительный процесс. При этом в регистре 1 находится результат & log х,

Вычисление функции г осуществляется в соответствии со следующими рекуррентны ш соотношениями:

35

На вход 50 блока 14 памяти величи пропускаемых итераций поступают с шие S разрядов z, и на выходе 71 танавливается соответствующее зна

30 ние j, поступающее на вход 74 упр ления сдвигом сдвигателя первого и на вход 72 первого сумматора 8. входе управления сдвигом третьего второго сдвигателей 12 и 11 посту пает также величина j, но уже с в хода 65 первого сумматора 8. На в 76 сумматора-вычитателя 7 поступа величина 2 z, а на вход 70 через третий коммутатор 17 с выхода 53

4Q блока 13 памяти поступает нормали зованная константа 2 log (1+2 На управляющем входе сумматора-вы тателя 7 в соответствии с кодом о рации устанавливается 1, и сумм

45 тор-вычитатель 7 производит вычит ние согласно (3). На управляюпще ды сумматоров-вычитателей 5 и 7 и блока управления подается знак LI) (О при cJ 1 и 1 при и) На входы 41 и 45 сумматоров-вычит телей 5 и 7 из регистров 1 и 2 соо ветственно считывается значение QO а на входы 62 и 63 этих же суммат ров-вычитателей с выходов сдвигат лей 12 и 11 - величина 0 2 . Сум маторы-вычитатели производят сложение или вычитание в зависимости знака UL) . Результат, равньш 9 , записывается в начале следующего

50

55

K + J

2 Z.

- 2 log,(1 +

(К III

);

uJ + 2

бк,. . :

sign tJ sign z

()

2

.00

1, n 0, 0

uJ + 2

В этом режиме на входах 84, 85 и 26 кода операции устанавливается код 110.

В нулевом такте по сигналу установки по входу 20 происходит обнуление регистра 4 и по синхроимпульсу на входе 21 запись исходных данньсх в регистры 1-3: QO регистр 1 и 2, z в регистр 3. В соответствии с кодом операции на первом коммутаторе 15 выбирается вход 42, на втором коммутаторе 16 - вход 43, на третьем коммутаторе 17 - вход 54 и на четвертом коммутаторе 18 - вход 66. В первом такте z из регистра 3 поступает на вход 49 сдвигателя 10.

5

На вход 50 блока 14 памяти величины пропускаемых итераций поступают старшие S разрядов z, и на выходе 71 устанавливается соответствующее значе0 ние j, поступающее на вход 74 управления сдвигом сдвигателя первого 10 и на вход 72 первого сумматора 8. На входе управления сдвигом третьего и второго сдвигателей 12 и 11 поступает также величина j, но уже с выхода 65 первого сумматора 8. На вход 76 сумматора-вычитателя 7 поступает величина 2 z, а на вход 70 через третий коммутатор 17 с выхода 53

Q блока 13 памяти поступает нормализованная константа 2 log (1+2 ). На управляющем входе сумматора-вычитателя 7 в соответствии с кодом операции устанавливается 1, и сумма5 тор-вычитатель 7 производит вычитание согласно (3). На управляюпще входы сумматоров-вычитателей 5 и 7 из блока управления подается знак LI) (О при cJ 1 и 1 при и) 1); На входы 41 и 45 сумматоров-вычитателей 5 и 7 из регистров 1 и 2 соответственно считывается значение QO , а на входы 62 и 63 этих же сумматоров-вычитателей с выходов сдвигателей 12 и 11 - величина 0 2 . Сум- маторы-вычитатели производят сложение или вычитание в зависимости от знака UL) . Результат, равньш 9 , записывается в начале следующего

0

5

такта в регистры 1 и 2. В регистр 4 записывается с выхода первого сумматора 8 величина j, а в регистр 3 с выхода К-) регистра 3 - величина z ,.

Аналогично в i-м такте работы регистр 4 находится в состоянии k, в регистрах I и 2 - текущее значение 0, а в регистре 3 - текущее значение z, Третий и второй сдвигатели 12 h 11 производят сдвиг б на k +

Этому режиму соответствует код 111 на входах 84, 85, 26 кода операции. Аналогично, как и в предыдущих режимах, по сигналу на входе 20 регистр 4 устанавливается в О, а в регис- трах 1-3 по синхроимпульсу запи сыва- ются исходные данные: в регистр 1 - 0 ,в регистр 2 - и1д и в регистр 3 - 10 z, . В первом такте z, из регистра

(/ J разрядов вправо, л первый сдвигптелт: 10 - на j ра рядоь влево. Значение k j получается суммированием в

3 через сдвигатель 10 поступает на вход 76 сумматора-вьгчитателя 7 и одновременно через вход 51 коммутатора 1Ь, сдвигатель Т1 - на вход 63 сум- первои сумматоре 8 значения k и счи- ig матора-вычитателя 6. Переменная из танного из блока 14 памяти значения регистра 2 поступает на вход 45 сум- J. Из блока 13 памяти нормализованных матора-вычитателя 6 и одновременно итераи,ио5 .ных констант на вход 70 сум- через вход 46 коммутатора 17 - н&

вход 70 сумматора-вычитателя 7. Переменная 0„ из регистра 1 поступает на вход 41 сумматора-вычитателя 5, на вход 62 которого через вход 47 коммутатора 15 и сдвигателя 12 из блока 13 памяти подается константа 25 arctg 2 . Блок управления анализирует знаковый разряд регистра 3, поступивший па его вход 52, и выдает сигналы управления знаком алгебраиматора-вычитателя 7 считывается нор- мализпванная константа log ( ± + ). При этом на первый вход

20

блока 13 из дается О,

0-)ка 19 управления по- а иа вт.опой вход -

J с

u-,, ча вход - значение k + выхода 65 cyм aтopa В.

Таким образом, cyммaтop-вычитaтeлfJ 7 совместно с первым сдвигателем 10 производит вычисления со1 ласно первому рекурр(и тпому соотношению в (3),

ческого сложения на управляющие вхоа сумматоры-вычитатели 5 и 6 совмест- зо ды сумматоров-вычитателей 5-7, со- но со сдвигателями 12 и 11 - вычис- гласно алгоритму (4). При этом сдви- ления согласно второму соотношению в (3). Результаты вычислений z

в начале (i + 1)-го такта запигатель 12 производит сдвиг нормализованной константы 2 arctg 2 на j разрядов вправо, т.е. производит де- нормализацию константы. На вход 67 управления сдвигом сдвигателя 11 через вход 81 коммутатора 18 подается с выхода сумматора 9 значение 2k + j равное в первом такте j. Величина 2k + j получается в сумматоре 9 с помощью cyм шpoвaния значения k, хра нящегося в регистре 4 и значения j из блока 14 памяти, при этом для получения величины 2k выходы регистра

сываются в регистр 3 1 и 2.

и в регистры

После того как итерационный индекс k, хранящ11йся в регистре 4, достигает значения п - 1, установленного на входе 86 схемы 114 сравнения, схема вырабатывает сигнал запрета и вычисления заканчиваются.

Функция arctg у/х вычисляется в

у стройстве в соответствии со следую- подключаются к входу 78 сумматора 9 щими рекуррентными.соотношениями: со смещением влево на один разряд.

- 2 z - ;

-()

Ч.. + 2

-(K + J)

, QK + ч arctg 2 sign u3 sign

2, у, uJ X, 00 0, z 0, arctg y/x.

е

13488298

Этому режиму соответствует код 11 на входах 84, 85, 26 кода операции. Аналогично, как и в предыдущих режимах, по сигналу на входе 20 регистр 4 устанавливается в О, а в регис- трах 1-3 по синхроимпульсу запи сыва- ются исходные данные: в регистр 1 - 0 ,в регистр 2 - и1д и в регистр 3 - 10 z, . В первом такте z, из регистра

25

20

ческого сложения на управляющие входы сумматоров-вычитателей 5-7, со- гласно алгоритму (4). При этом сдви-

гатель 12 производит сдвиг нормализованной константы 2 arctg 2 на j разрядов вправо, т.е. производит де- нормализацию константы. На вход 67 управления сдвигом сдвигателя 11 через вход 81 коммутатора 18 подается с выхода сумматора 9 значение 2k + j, равное в первом такте j. Величина 2k + j получается в сумматоре 9 с помощью cyм шpoвaния значения k, хранящегося в регистре 4 и значения j из блока 14 памяти, при этом для получения величины 2k выходы регистра 4

В начале следующего такта результаты суммирования Q , и) и Zj записываются в регистры 1-3 соответственно,по синхроимпульсу с выхода 21,а

в регистр 4 - значение j с выхода

65 сумматора 8. Аналогично, в i-м

такте работы регистр 4 находится в

состоянии 0, k (i с k) . Таким образом, сдвигатель 12 пропускает нормаизованную константу arctg со сдвигом на k + j разрядов вправо, поскольку на выходе 65 суммато т

91

pa 8 установлено значение k + j. Сдвигатель 1 1 пропускает значение 7. из регистра 3, сдвинутым вправо на 2k + j разрядов, так как на выходе сумматора 9 устанавливается это значение, а сдвигатель 10 - значение z из регистра 3, сдвинутым на j разрядов влево, Сумматор-вычитатель 7 вы- лолняет действие (сложение или вычитание) согласно первому рекуррентному соотношению в (4), сумматор-вычи- татель 6 - согласно второму, а сум- матор-вычитатель 5 - согласно третьему. Полученные результаты в начале следующего такта записываются в регистры 3-1 соответственно. В регистр 4 записывается значение k + j. После того как состояние регистра 4 равно или больше кода, заданного по входу 86, сигнал на выходе схемы 114 сравнения заблокирует дальнейшие вычисления. При зтом в регистре 1 окажется результат операции, т.е. arctg у/х.

Вычисление функций k sin4иk cos осуществляется в соответствии со следующими рекуррентными соотношениями:

(k «.1)

Z , Z - иО u. 2

К К П

Ч К

-(,1 I

0,,, 29 -и) sign ijJ sign e

. I( И + I I

arctg 2

Zo 0,4 1, 00 ,

z k , oJ k cos f ;

en 0.

в начале выполнения операции на входах 84, 85 и 26 устанавливается код 100, а на входе 26 код, соответствующий максимально возможному числу итераций. По сигналу начальной установки на входе 20 и синхроимпульсу на выходе 21 в регистры 1-3 записываются исходные данные: z в регистр 1, иЗ в регистр 2 и 0 в регистр 3, регистр 4 обнуляется. На управляющих входах коммутаторов 15-18 в соответствии с кодом операции установлены коды, подключающие выход 40 регистра 1 через коммутатор 16 к входу 59 сдвигателя 11, выход 44 регистра 2 через коммутатор 15 к входу

ЗА8829

10

58 сдвигателя 10, выход 53 блока 13 памяти через коммутатор 17 к входу 70 сумматора-вычитателя 7 и выход 65 сумматора 8 к входу 67 сдвигателя 11. В следующем первом такте z из регистра 1 поступает на вход 41 сумматора-вычитателя 5 и через вход 43 коммутатора 16 и сдвигатель 11 на

вход 63 сумматора-вычитателя в,1л)

из регистра 2 - на вход 45 сумматора- вычитателя 6 и через вход 47 коммутатора 16 и сдвигатель 12 на вход 62 сумматора-вычитателя 5, 0,, из регистра 3 через сдвигатель 10 - на вход 76 сумматора-вычитателя 7. На вькоде 65 сумматора 8 устанавливается значение, равное j (количеству пропус- .Ix в зтом такте нулевых итераций), по лдресу j иа вход 83 из блока 13 памяти считывается константа 2 arctg 2 , которая через вход 54 коммутатора 17 поступ-чет на вход 70 сумматора-пычитателя /.

Таким образом, сдвигатели 12 и 11 сдиигают информацию на j разрядов вправо, а сдвигатель 10 - на j разрядов влево. Старщий (знаковый) разряд операнда 0 по входу 52 поступает в

блок 19 управления, вырабатывающ11Й алгебраического суммирования для сумматоров-вычитателей 5-7, которые производят действия согласно рекуррентным соотношениям (5) и результаты z , uJ и 0 по синхросигналу с выхода 21 записываются в регистры 1-3 соответственно.

В i-M такте работы устройства регистр 4 находится в состоянии k()

и сдвигатели 12 и 11 пропускают операнды, сдвинутыми вправо на k + j разрядов, а блок 13 памяти констант выдает по адресу k + j константу arctg 2 - . Сумматоры-вычитатели 5-7 производят действие -согласно алгоритму (5), результаты

K+j записываются в регистры 1-3 соответственно, а в регистр 4 записывается значение k + jj

После того как состояние регистра 4 достигает или превышает значение кода по входу 86 схемы 114 вырабатывается сигнал сравнения и запрещает дальнейшую работу устройства. При

этом в регистрах 1 и 2 оказываются записанными результаты z k и -0| k cosH . Учет коэффициента деформации вектора k в полученных соотношениях может быть проведен с помощью выполнения операции деления и получения функдаи tgif.

Блок управления работает следующим образом.

Схема, собранная на элементах 90, 91, 93, 94, 103, 104 и 110, предназначена для инверсии знакового разряда регистра 3 в операциях деления и вычисления функции . В начале выполнения операции при записи в регистры 1-3 исходных данных инвертируется знаковый разряд операнда, записываемого в регистр 3. При этом старший (знаковый) разряд записьгааемого в регистр 3 операнда подается на вход 87 блока 19 управления и с него на первый вход эдемеита ИСКЛЮЧАЮЩЕЕ ИЛИ 90, на второй вход которого с входа 84 кода операции в операциях деления и логарифмирования подается ноль, а в остальных операциях - единица. На выходе элемента НЕ 93 образуется инвертированное значение знакового разряда входного числа, которое при дей- ствии на входе 20 сигнала установки проходит через элементы 103 и 110 на вход 115 знакового разряда регистра 3. Аналогично производится учет знака величины (х) на элементах 91, 94, 104 и 110. В этом случае инвертируется знаковый разряд числа, получаемого на входе 88 сумматора-вычиТате- ля 7 в процессе выполнения этих операций, В остальных операциях инверсии знакового разряда не будет, так как на вторых входах элементов 90 и 91 будет единица, находящаяся на входе 84.

Элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 92 и НЕ 95 служат для формирования знака величины сх) , с помощью знакового разряда регистра 3, поступающего на вход 52, а знак и) поступает через выход 23 на второй управляющий вход блока 13 памяти и на первый вход суммато- ра-вычитателя 6.

Схема 114 сравнения и элемент ИЛИ 109 служат для остановки работы устройства, после того как индекс ите раций k, хранящийся в регистре 4 и поступающий из него на вход 78, достигает или превышает код, соответствует максимальному значению индекса итераций и заданный по входу 86.

Остальные элементы блока 19 управления (97-102, 105-108 и 111-113) служат для выработки сигналов управления коммутаторами 15-18 (вход 26

5 о

ц

Q g

5

и выходы 27-30) сигналов управления сложением-вычитанием сумматоров-вы- читателей 5, 7 (выходы 24, 25) и сигнала управления для блока 13 памяти в зависимости от кода операции,ус- тановленного на входах 84, 85 и 26.

Формула изобретения

Устройство для вычисления функции, содержащее три регистра, три суммато- ра-вычитателя, два сдвигателя, четыре коммутатора, блок памяти нормализованных итерационных констант, блок памяти величины пропускаемых итера- ций,причем выходы первого и второго регистров соединены с входами первых операндов соответственно первого и второго сумматоров-вычитателей, выходы второго и третьего сумматоров- вычитателей соединены с первыми информационными входами соответственно второго и третьего регистров, выход первого регистра и выход блока памяти нормализованных итерационных констант соединены соответственно с первым и вторым информационными входами первого коммутатора, выходы старших разрядов третьего регистра соединены с адресными входами блока памяти величины пропускаемых итераций, выход первого регистра соединен с первым информационным входом второго коммутатора, выход блока памяти величины пропускаемых итераций соединен с входом величины сдвига первого сдвигателя, выход второго регистра соединен с первым информационным входом третьего коммутатора, второй информационный вход которого соединен с выходом блока памяти нормализованных итерационных констант, третий информационный вход третьего коммутатора соединен с выходом второго сдвигателя, информационный вход которого соединен с выходом второго коммутатора, входы первого и второго операндов третьего сумма- тора-вычитателя соединены с выходами соответственно третьего коммутатора и первого сдвигателя, отличающееся тем, что, с целью повышения быстродействия за счет умень- шеьшя числа итераций, в него дополнительно введены два сумматора, чет- вертый регистр и блок управления, причем выход первого сумматора-вычи- тателя соединен с первым информаци13

о нным входом первого регистра, первый, второй н третий входы начальной установки данных устройства соединены с вторыми информационными входами соответственно первого, второго и третьего регистров, выход третьего регистра соединен с вторым информационным входом второго коммутатора и с информационным входом первого сдвигателя, выход первого коммутатора соединен с информационным входом третьего сдвигателя, выходы третьего и второго сдвигателей соединены с входами второго операнда соответственно первого и второго сум маторов-вычитателей, выход блока памяти величины пропускаемых итера1у1й соединен с входами первых слагаемых первого и второго сумматоров, вход второго слагаемого первого сумматора соединен с выходом четвертого регистра, информационный вход которого соединен с выходом первого сумматора выход четвертого регистра соединен с сдвигом на один разряд в сторону старших разрядов с входом второго слагаемого второго сумматора, выход первого сумматора соединен с входом величины сдвиг а третьего сдвигателя и первым информационным входом четвертого коммутатора, второй и третий информационные входы которого соединены соответственно с выходом второго сумматора и выходом четвертого .регистра, старший разряд из группы третьего входа начальной установки данных устройства и выходы старших разрядов третьего регистра и третьег сумматора-вычитателя соединены с группой входов анализа знаков итерационных переменных блока управления, вход запуска и тактовый вход устройства соединены с одноименными входам блока управления, группа входов кода операции устройства соединена с одноименной группой входов блока управления, вход числа итераций устройства соединен с одноименным входом блока управления, выход первого сумматора соединен с первым разрядом адресного входа блока памяти нормализованных итерационных констант и входом признака окончания итерации блока управления, первый выход блока управления соединен с синхронизирующими входами первого, второго и третьего регистров, второй выход блока управления соединен с вторым разрядом ад

10

25 8829J4

ресного входа блока памяти нормализованных итерационных констант,третий выход блока управления соединен с третьим разрядом адресного входа блока памяти итерационных констант и управляющим входом второго сумматора-вычитателя, четвертый и пятый выходы блока управления соединены с управляющими входами соответственно первого и третьего сумматоров-вычи5

0

0

5

5

0

5

0

5

тателей, третий вход группы входов кода операции блока управления и mte- стой выход блока управления соединены с управляющими входами первого коммутатора, управляющий вход второго коммутатора соединен с седьмым выходом блока управления, восьмой и девятый выходы блока управления соединены с управляющими входами третьего и четвертого коммутаторов, десятый выход блока, управления соединен с входом старшего разряда третьего регистра, вход начальной установки блока управления соединен с входами сброса первого, второго, третьего регистров и четвертого регистров, при- t

чем блок управления содержит три элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, четыре элемента НЕ, одиннадцать элементов N, элемент И-НЕ, пять элементов ИЛИ и схему сравнения, входы первого и второго операндов схемы сравнения соединены соответственно с входами признака окончания итерации и числа итераций блока управления, вькод схемы сравнения соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с тактовым входом блока управления, выход первого элемента ИЛИ соединен с первым выходом блока управления, первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с первого по третий, элементов И с первого по четвертый и элемента И-НЕ соединены с первым входом группы входов кода операции блока управления, второй вход которой соединен с вторыми инверсными входами первого и второго элементов . И, вторым входом элемента И-НЕ и с первыми входами пятого и шестого элементов И, третий вход группы входов кода операции соединен с вторыми входами третьего и четвертого элементов И, вторые входы элементов ИСКЛЮЧАЩЕЕ ИЛИ с первого по третий соединены соответственно с первым, третьим и вторым входами группы входов анали- i за знаков итерационных переменных

15

блока управления, выходы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены через соответственно первый и второй элементы НЕ с первыми входами соответственно седьмого и восьмого элементов И, второй вход седьмого элемента И и второй инверсный вход восьмого элемента И соединены с входом запуска блока управления, выходы седьмого и восьмого элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен с десятым выходом блока управления, выход третьего элемента ИСКЛЮЧАЩЕЕ ИЛИ соединен с входом третьего элемента НЕ и с первыми входами девятого и десятого элементов И, выход третьего элемента НЕ соединен с третьим выходом блока управления, с первым входом одиннадцатого и вторым входом пятого элемен тов И, выход первого элемента И соединен с первым входом третьего элемента ИЛИ, вторым входом девятого элемента И и шестым выходом блока уп равления, выход девятого элемента И

А882916

соединен с первым входом четвертого элемента ИЛИ, второй и третий входы которого соединены с выходами соответственно пятого и второго элемен- тов И, выход четвертого элемента ИЛИ соединен с четвертым выходом блока управления, выход элемента И-НЕ соединен с вторым входом одиннадцатого .Q элемента И, выход которого соединен с первым входом пятого элемента ИЛИ, второй и третий входы которого соединены с выходами соответственно десятого и шестого элементов И, выход того элемента ИЛИ соединен с пятым

выходом блока управления, выход третьего элемента И соединен с вторым входом третьего элемента ИЛИ,с вторым входом десятого элемента И и с восьмым выходом блока управления, выход третьего элемента ИЛИ соединен с вторым выходом блока управления, выход четвертого элемента И соединен с вторым входом шестого элемента И 25 и с девятым выходом блока управления и через четвертый элемент НЕ - с седьмым выходом блока управления.

20

S7 о

Sk о85 оГ Г

-24- 22

2В о780

29

,30 28

fiffo ejo

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь координат | 1981 |

|

SU1076903A1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Устройство для вычисления функций | 1986 |

|

SU1374219A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1370653A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1332313A1 |

| Устройство для вычисления гиперболических синуса и косинуса | 1987 |

|

SU1497615A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1130861A1 |

| Устройство для вычисления направляющих косинусов вектора в пространстве | 1982 |

|

SU1164700A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА | 1991 |

|

RU2006916C1 |

Изобретение относится к вычислительной технике и может быть исшш in 26 к ю гогз пользовано в специализированных вычислителях в устройствах, работающих в реальном масштабе, времени. Целью изобретения является повышение быстродействия за счет уменьшения числа операций. Устройство Содержит регистры 1-4, сумматоры-вычитатели 5-9, сдвигатели 10-12, блок 13 памяти нормализованных итерационных констант, блок 14 памяти величины пропускаемых итераций, коммутаторы 15-18, блок 19 управления. В устройстве используется разновидность итерационного алгоритма Волдера (метод симметричных итераций) для вычисления ряда элементарных функций. 2 ил. i (Л 00 00 00 to со Фи J

| Устройство для вычисления элементарных функций | 1982 |

|

SU1141399A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Байков В.Д., Смолов В.Б | |||

| Специализированные процессоры: итерационные алгоритмы и структуры | |||

| М.: Радио и связь, 1985, с.234-236, рис.5.17 - 5.19. | |||

Авторы

Даты

1987-10-30—Публикация

1986-04-28—Подача