Изобретение относится к вычислительной технике и может быть использовано в ЭВМ, особенно вычислителях, работающих в реальном масштабе времени, для сопряжения процессора с модулем памяти, имеющими различную длительность цикла.

Целвю изобретения является повышение достоверности работы процессора за счет обеспечения защиты от зависаний процессора при обращениях к памяти.

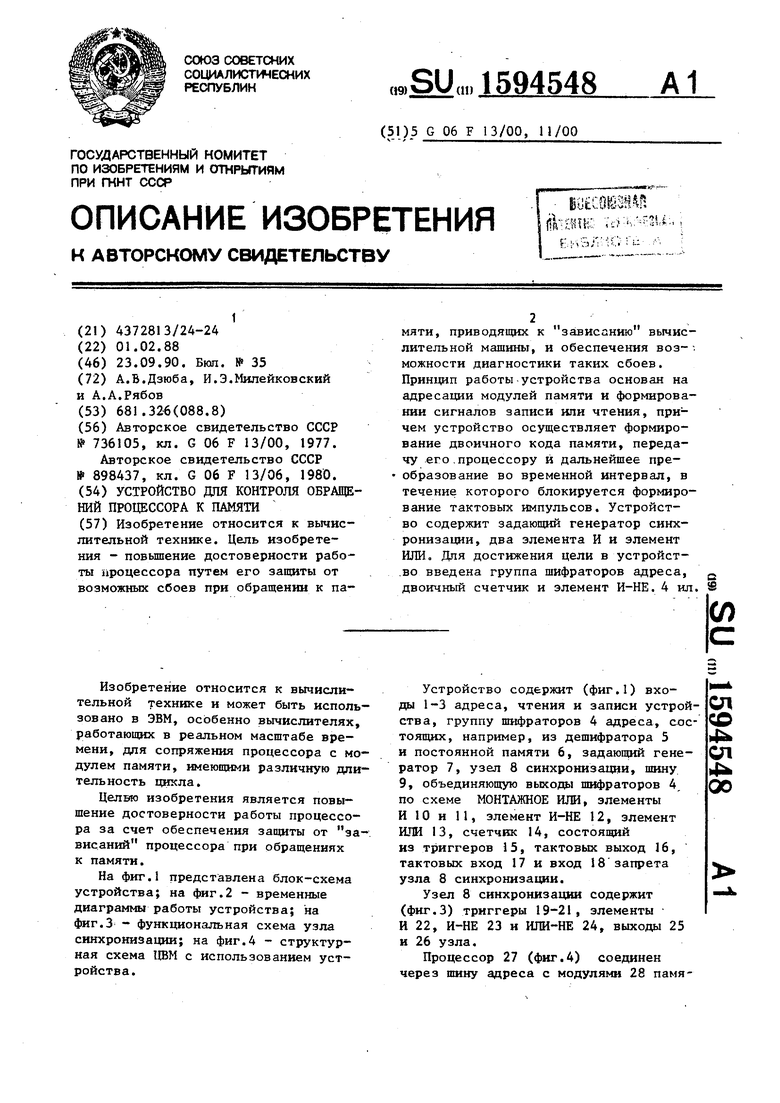

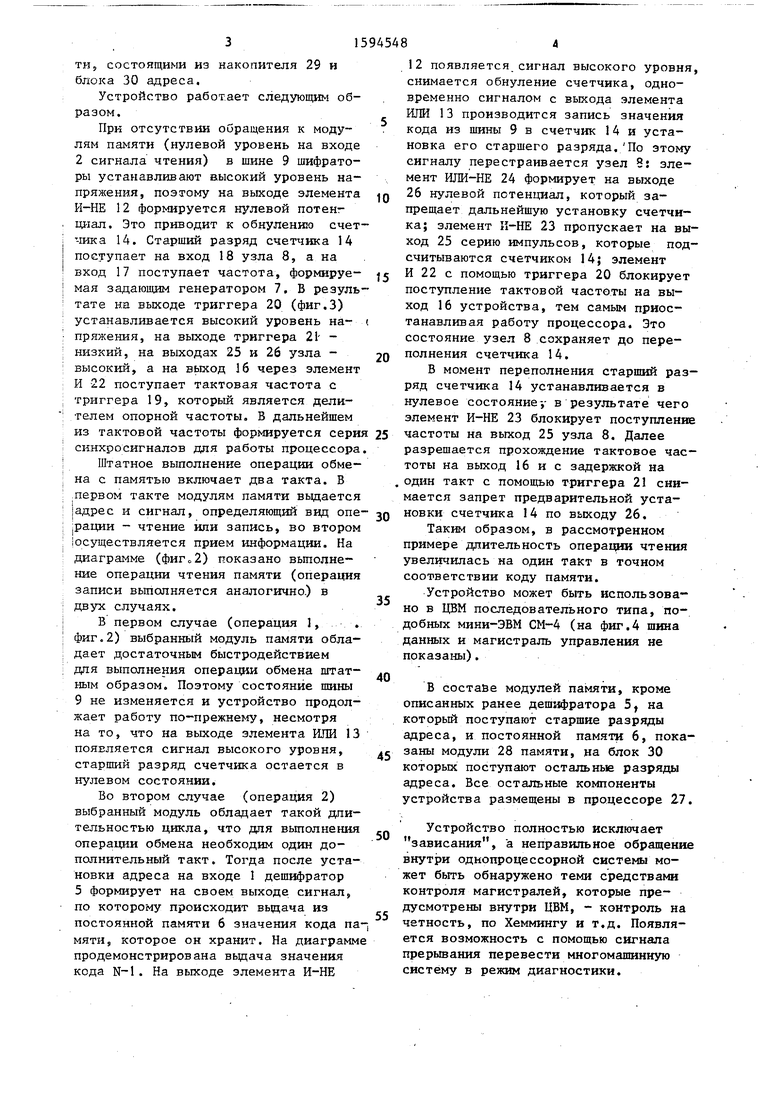

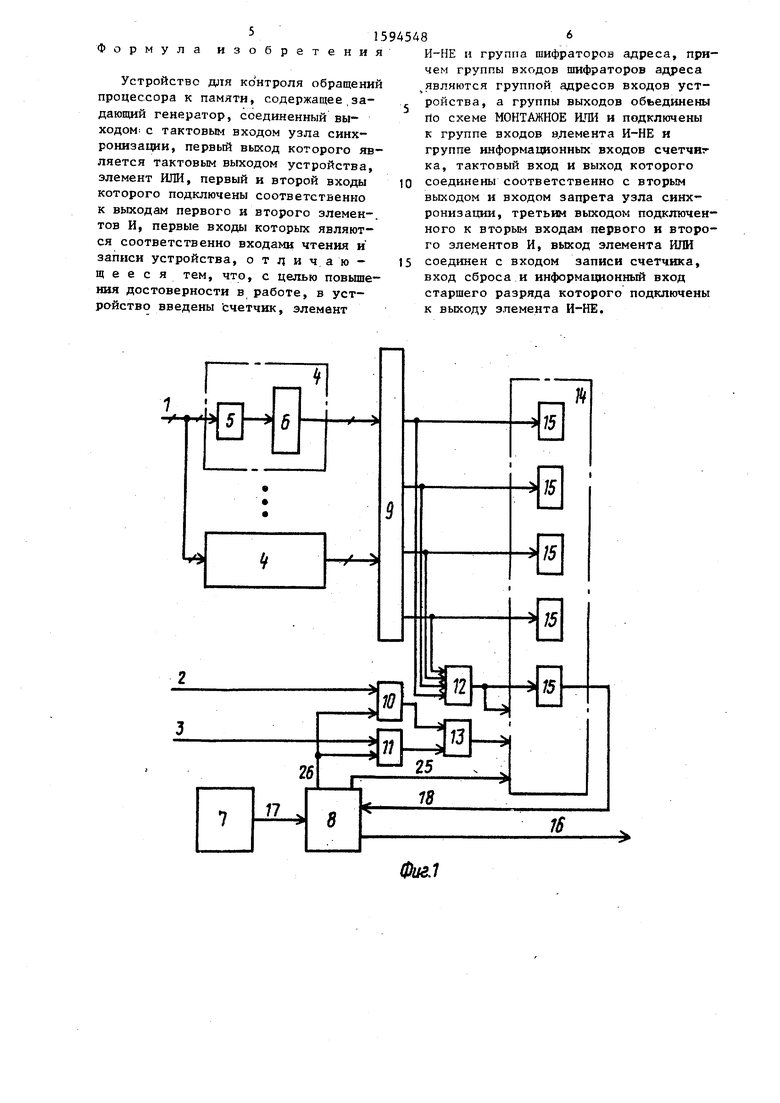

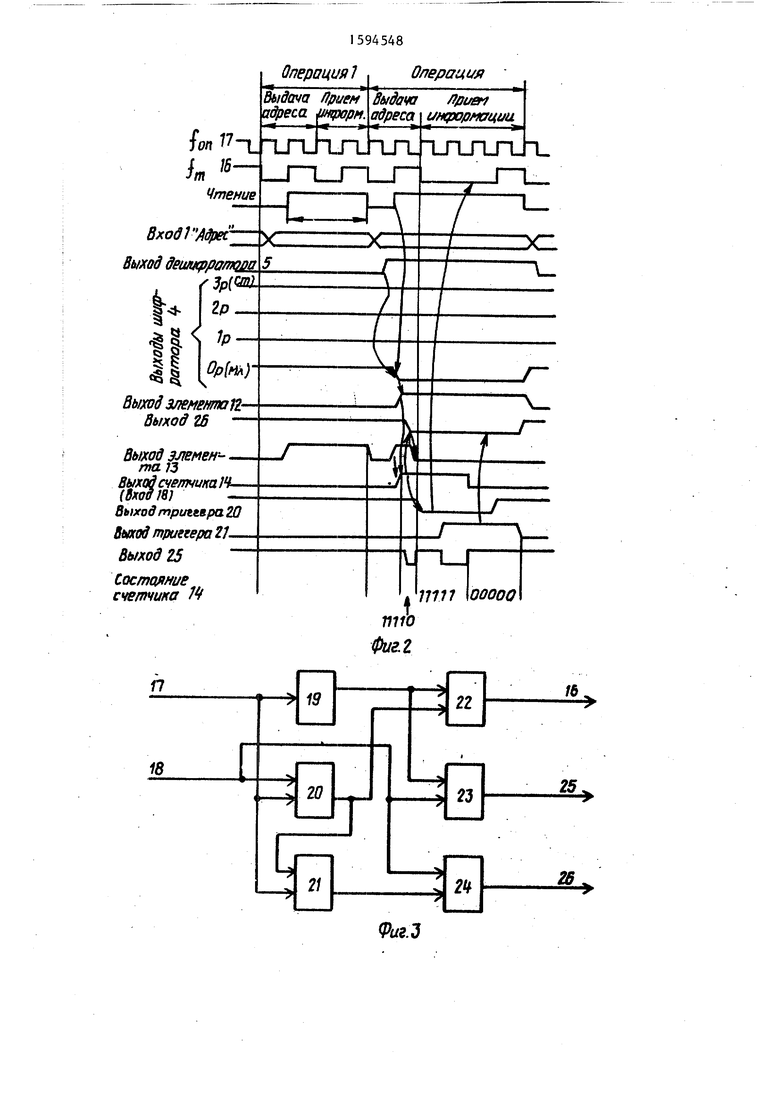

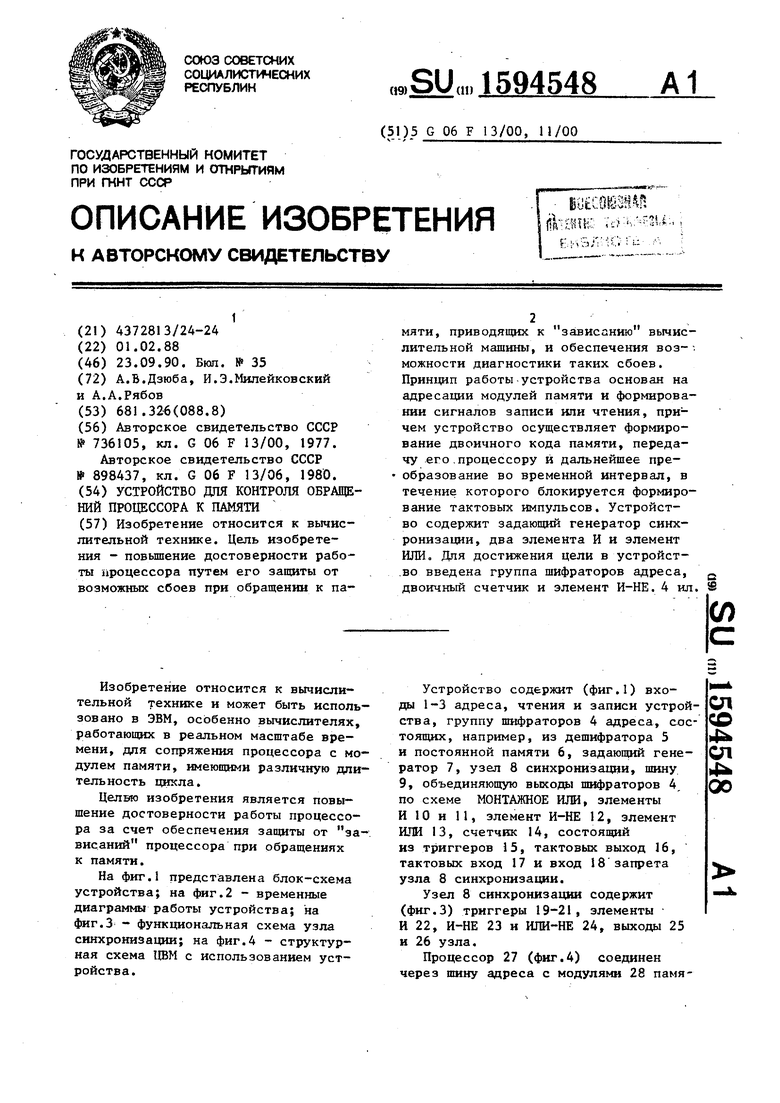

На фиг.1 представлена блок-схема устройства; на фиг.2 - временные диаграммы работы устройства; на фиг.З - функциональная схема узла синхронизации; на фиг.4 - структурная схема ЦВМ с использованием устройства.

Устройство содержит (фиг.1) входы 1-3 адреса, чтения и записи устройства, группу шифраторов 4 адреса, состоящих, например, из дешифратора 5 и постоянной памяти 6, задающий генератор 7, узел 8 синхронизации, шину 9, объединяющую выхода шифраторов 4. по схеме МОНТАЖНОЕ ИЛИ, элементы И 10 и 11, элемент И-НЕ 12, элемент ИЛИ 13, счетчик 14, состоящий из триггеров 15, тактовых выход 16, тактовых вход 17 и вход 18 запрета узла 8 синхронизации.

Узел 8 синхронизации содержит (фиг.З) триггеры 19-21, элементы И 22, И-НЕ 23 и ШШ-НЕ 24, выходы 25 и 26 узла.

Процессор 27 (фиг.4) соединен через шину адреса с модулями 28 памясд

со

4

сл

4

00

ти, состоящими из накопителя 29 и блока 30 адреса.

Устройство работает следуюнц - образом.

При отсутствии обращения к модулям памяти (нулевой уровень на входе 2 сигнала чтения) в шине 9 шифраторы устанавливают высокий уровень напряжения, поэтому на выходе элемента И-НЕ 12 формируется нулевой потенг циап. Это приводит к обнулению счет -шка 14. Старший разряд счетчика 14 поступает на вход 18 узла 8, а на вход 17 поступает частота, формируемая задающим генератором 7. В результате нн выходе триггера 20 (фиг.З) устанавливается высокий уровень на- пряжения, на выходе триггера 21- - низкий, на выходах 25 и 26 узла - высокий, а на вьпсод 16 через элемент И 22 поступает тактовая частота с триггера 19, который является делителем опорной частоты. В дальнейшем из тактовой частоты формируется сери синхросигналов для работы процессора

Штатное выполнение операции обмена с памятью включает два такта. В первом такте модулям памяти вьщается |адрес и сигнал, определяющий вид опе |рации - чтение или запись, во втором |осуществляется прием информации. На диаграмме (фиг ,2) показано вьшолне- ние операции чтения памяти (операция записи вьтолняется аналогично.) в двух случаях.

В первом случае (операция 1, . фиг.2) выбранный модуль памяти обладает достаточным быстродействием для выполнения операции обмена штатным образом. Поэтому состояние шины 9 не изменяется и устройство продолжает работу по-прежнему, несмотря на то, что на выходе элемента ИЛИ 13 появляется сигнал высокого уровня, старший разряд счетчика остается в нулевом состоянии.

Во втором случае (операция 2) выбранный модуль обладает такой дпи- тельностью цикла, что для вьтолнения операции обмена необходим один дополнительный такт. Тогда после установки адреса на входе 1 дешифратор 5 формирует на своем выходе сигнал, по которому происходит вьдача из постоянной памяти 6 значения кода па мяти, которое он хранит. На диаграмм продемонстрирована вьщача значени:я кода N-1. На выходе элемента И-НЕ

0

5

0

5

0

5

0

5

0

5

12 появляется сигнал высокого уровня, снимается обнуление счетчика, одновременно сигналом с выхода элемента ИЛИ 13 производится запись значения кода из шины 9 в счетчик 14 и установка его старшего разряда. По этому сигналу перестраивается узел 8; элемент ИЛИ-НЕ 24 формирует на выходе 26 нулевой потенциал, который запрещает дальнейшую установку счетчика; элемент И-НЕ 23 пропускает на выход 25 серию импульсов, которые подсчитываются счетчиком 14; элемент И 22 с помощью триггера 20 блокирует поступление тактовой частоты на выход 16 устройства, тем самым приостанавливая работу процессора. Это состояние узел 8 сохраняет до переполнения счетчика 14.

В момент переполнения старший разряд счетчика 14 устанавливается в нулевое состояние у в результате чего элемент И-НЕ 23 блокирует поступление частоты на выход 25 узла 8. Далее разрешается прохождение тактовое частоты на выход 16 и с задержкой на , один такт с помош;ью триггера 21 снимается запрет предварительной установки счетчика 14 по выходу 26.

Таким образом, в рассмотренном примере длительность операции чтения увеличилась на один такт в точном соответствии коду памяти.

Устройство может быть использовано в ЦВМ последовательного типа, подобных мини-ЭВМ СМ-4 (на фиг.4 шина данных и магистраль управления не показаны).

В состаЗе модулей памяти, кроме описанных ранее дешифратора 5, на который поступают старшие разряды адреса, и постоянной памяти 6, показаны модули 28 памяти, на блок 30 которых поступают остальные разряды адреса. Все остальные компоненты устройства размешены в процессоре 27.

Устройство полностью исключает зависания, а неправильное обращение внутри однопроцессорной системы может быть обнаружено теми средствами контроля магистралей, которые предусмотрены внутри ЦВМ, - контроль на четность, по Хеммингу и т.д. Появляется возможность с помощью сигнала прерывания перевести многомашинную систему в режим диагностики.

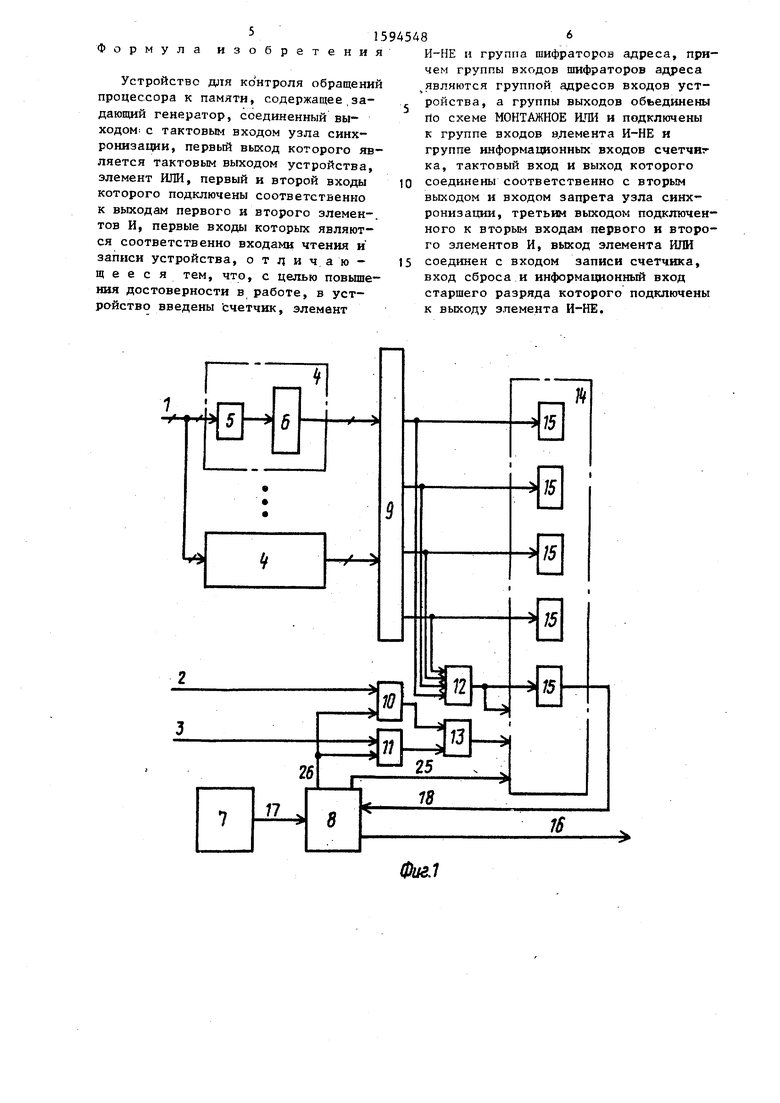

Формула изобретени

Устройство для контроля обращений процессора к памяти, содержащее.задающий генератор, соединенный выходом с тактовым входом узла синхронизации, первый выход которого является тактовым выходом устройства элемент ИЛИ, первый и второй входы которого подключены соответственно к вькодам первого и второго элементов И, первые входы которых являются соответственно входами чтения и записи устройства, от ичаю- щ е е с я тем, что, с целью повьше- иия достоверности в работе, в устройство введены счетчик, элемент

15

1594548

И-НЕ н группа шифраторов адреса, причем группы входов шифраторов адреса являются группой адресов входов устройства, а группы выходов обьединены rto схеме МОНТАЖНОЕ ИЛИ и подключены к группе входов влемента И-НЕ и группе информационных входов счетчиг ка, тактовый вход и выход которого

соединены соответственно с вторым выходом и входом запрета узла синхронизации, третьим выходом подключенного к вторым входам первого и второго элементов И, выход элемента ИЛИ

соединен с входом записи счетчика, вход сброса и информационный вход старшего разряда которого подключены к выходу элемента И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для сопряжения ЦВМ с накопителями на магнитной ленте | 1985 |

|

SU1288708A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для сопряжения цифровой вычислительной машины с внешними устройствами | 1987 |

|

SU1413635A2 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1985 |

|

SU1298762A2 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

Изобретение относится к вычислительной технике. Цель изобретения - повышение достоверности работы процессора путем его защиты от возможных сбоев при обращении к памяти, приводящих к "зависанию" вычислительной машины, и обеспечения возможности диагностики таких сбоев. Принцип работы устройства основан на адресации модулей памяти и формировании сигналов записи или чтения, причем устройство осуществляет формирование двоичного кода памяти, передачу его процессору и дальнейшее преобразование во временной интервал, в течение которого блокируется формирование тактовых импульсов. Устройство содержит задающий генератор синхронизации, два элемента И и элемент ИЛИ. Для достижения цели в устройство введена группа шифраторов адреса, двоичный счетчик и элемент И-НЕ. 4 ил.

(Риг.

| Устройство для сопряжения основной памяти с процессором | 1977 |

|

SU736105A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения процессора с памятью | 1980 |

|

SU898437A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-09-23—Публикация

1988-02-01—Подача