1

Изобретение относится к цифровым вычислительным устройствам, а именно к устройствам управления основной памятью, используемым в составе процессара.

Известны устройства , вход5пцие в состав блока памяти и предназначенн1г1е для сопряжений основной памяти с процессором и коррекции считанной из памяти информации, содержащие элемент памя-. ти, регистр информации, элемент ИЛИ для формирования слова записи, формирователь кода коррекции записываемой инфс мации, дешифратор синдрома, узел коррекции Г.,5

Недостаток этих устройств заключается в значительном объеме оборудования, необходимого для коррекции данных при больших объемах памяти и линейно возрастающего с ростом числа блоков памя- 20 ти.

Наиболее близким к данному по сущности технического решения является Устройство для сопряжения основной памяти с процессором, содержащее по чис- пу групп блоков памяти регистры адреса, информационные регистры и вькодные регистры, узел коррекции,- формирователь корректирущего кода и группу элементов И-ИЛИ, соответственно соединенных входами с группой вькодов узла коррекции и первой группой информационньк выходов устройства, первая группа информационньк входов и группа адресных входов которого подключены соответственно ко входам информационнък регистров и входам регистров адреса, выходы которых являются адресными выходами устройства, вторая группа информационньк входов устройства соединена с первыми информационными входами соответствующих выходнък регистров, выходы элементов И-ИЛИ группы соединены с соответствующими входами формирователя корректирующего кода |2.

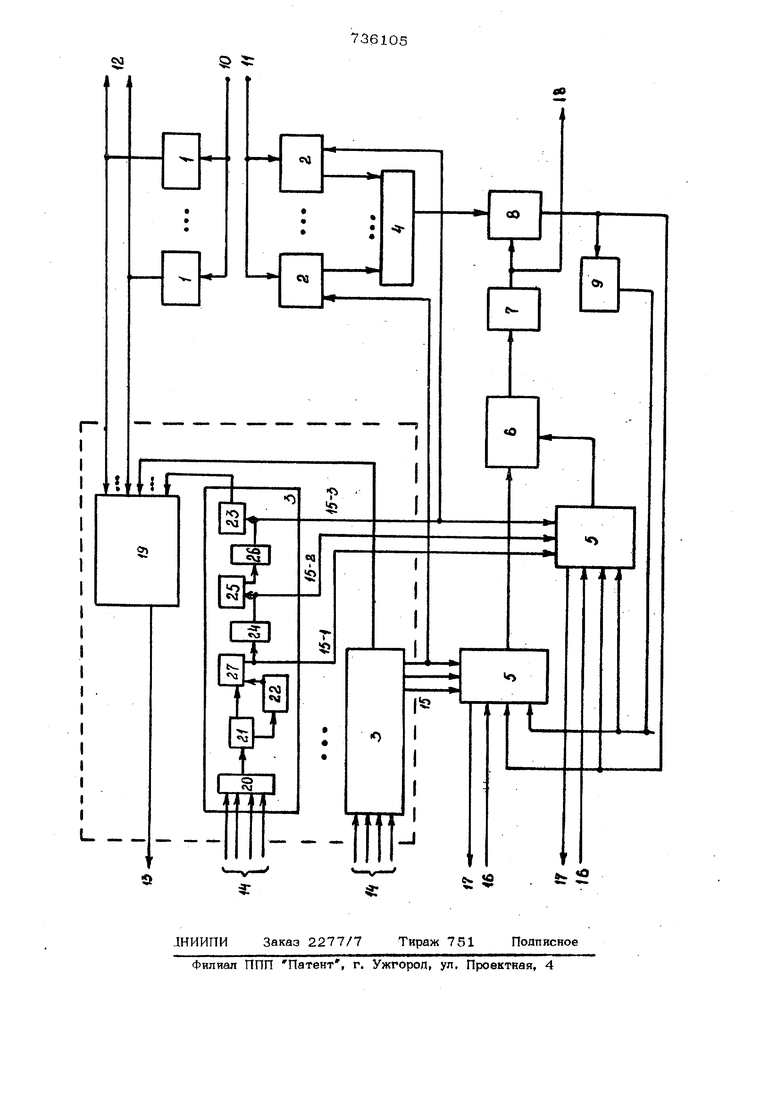

Недостаток указанного устройства заключается в большом количестве оборудования, поскольку оно требует для каж дого двойного слова, счит1,1ваемого из разньк блоков памяти, отдельного корректора, элементов И-ИЛИ, формирователей корректирующего кода. Этот недостаток особенно проявляется при увеличении количества одновременно работающих блоков памяти. Цель изобретения - сок)ащение аппаратурных затрат. Поставленная цель достигается тем, что в устройство введены узел выборки группы блоков памяти, два элемента ИЛИ и узлы синхронизации по числу групп блоков памяти, причем выходы информационных регистров подключены к соответствующим входам первого элемен та ИЛИ, выход которого соединен с первым входом группы элементов И-ИЛИ, второй и третий информационные входы выходиьк регистров, первые выходы которых соединены с соответствующими вы ходами второй группы информационных выходов устройства, подключены соответ ственно к выходам группы элементОВ И-ИЛИ и вьосодам формирователя корректирующего кода, вторые выходы вькодны регистров соединены с соответствующими входами второго элемента ИЛИ, подключенного выходом ко входу узла коррекции, входы каждого узла синхронизации являются соответствующими управляющими входами устройства, первьй, второй и третий выходы каждого узла синхронизации подключены к соответствующим управляющим входам одноименного вьрсодного регистра, третий и четвертьй выходы каждого узла синхронизации соединены соответственно с управляющим входом одноименного информационного регистра и соответствующим управляющим входом узла выборки блока памяти, входы которого подключены к вькодам соответствующих регистров адреса, а вы ход является управляющим выходом устройства. На чертеже изображена блок-схема устройства. Устройство содержит регистры 1 адреса, информационные регистры 2, узлы 3 синхронизации логических блоков памяти, первый элемент ИЛИ 4, выходные регистры 5, второй элемент ИЛИ 6 узел 7 коррекции-, группу 8 элементов И-ИЛИ,- формирователь 9 корректир;;,тоще го кода записываемой информации, групп адресных входов 10, первую группу инфо мацнонных входов 11, адресные вьрсоды 12, управляюишй выход 13, управл5теэщи входы 11, выходы 15 узлов синхронизации, вторую группу информационных входов 16, вторую группу информационных выходов 17, первую группу информационных выходов 18, узел 19 вьсборки блока памяти. Узел 3 включает элемент ИЛИ 20, триггеры 21 - 26, элемент И 27. Данное устройство предназначено для сопряжения процессора с оперативной памятью, которая может включать до 16 независимых блоков памяти, разделенных на четьфе группы блоков памяти (логические блоки памяти). Под логическим блоком понимается определенный комплект блоков памяти (в данном случае до четьфех), объединенных общими адресными и информационными шинами. Адресные и информационные регистры этих логических блоков находятся в устройстве сопряжения. В принципе данное устройство сопряжения выполнено в виде четьфех симметричных схем, имеющих общие элементы коррекции, выдачи информации в процессор, формирования двойного слова записи в память, формирования корректирующего кода. Оперативная память функционирует таким образом, что независимо от режима Запись или Чтение сначала происходит считьшание информации из памяти, прием в устройство сопряжения, анализ и коррекция принятой из памяти информации, а затем либо запись новой информации в реж.име Запись, либо регенерация считанной из памяти информации в режиме Чтение. Устройство работает следующим образом. Все операции, связанные с обслуживанием запросов к памяти, начинаются с последовательного приема от одного да четьфех запросных слов из блока управления памятью. На регистры 1 принимаются адреса памяти, на регистры 2 записываемая информация и маркеры ( в режиме Запись). Одновременно с приемйм запросного слова узел 19 формирует сигнал Чтение для соответствующего логического блока памяти и передается в память по управляющему выходу 13. Адрес ячейки памяти по адресным выходам 12 поступает в память и сохраняется на вькодах до конца цик- ла памяти. После окончания цикла чтения память посылает в устройство сопряжения сигнал готовности информации по управляющим входам 14 и считанную информацию по второй группе информационных входов 16. В режиме Запись считанная информация игнорируется, а с соответствующего регистра 2 через первый элемент ИЛИ 4 записьшаемая информация поступает на группу 8 элементов И-ИЛИ, и с выхода которой - на формирователь 9 и выходные регистры 5. Формирователь 9 из 64-разрядной информации по коду Хэмминга формирует 8 разрядов корректирующего кода, который вместе с информацией записывается в выходной регис 5, соответствующий запущенному блоку. С этого регистра сформированное двойное слово (72 разряда) передается на вторую группу информационных выходов в блок па мяти и сохраняется на шинах до конца цик ла памяти. Одновременно с информацией в блок памяти передается сигнал Запис по управляющему выходу 13. В режиме Чтение информация из памяти поступает на выхогшой регистр 5и содержит 64 информационных разряда и 8 разрядов корректирующего кода. Информация с выхода этого регистра поступает через второй элемент ИЛИ 6на вход узла 7 коррекции. В узле 7 принятая информация анализируется и, если обнаруживается одиночная ошибка, корректируется. Если ошибки нет, то информация проходит через узел 7 без изменения на первую группу информационных выходов 18 и поступает в процессор. Двойные и некоторые многократные ошибки обнаруживаются, но не корректируются. В режиме Чтение на выход группы 8 проходит считанная из памяти информация с узла 7. Также как в режиме Запись формирователь 9 вырабатывает код коррекции, которьш вместе с информацией записьшается в один из выходных регистров 5. Информация на второй группе информационных выходов сохраняется до конца цикла памяти. В режиме записи отдельньрс байтов информации считьюание и контроль инфор мации аналогичны операции Чтение. Отдельные байты, которые должны быть согласно маркерам записаны в память, принимаются группой 8 элементов И-ИЛ с информационного регистра, а остальные байты двойного слова принимаются группой 8 из узла 7 коррекции. Собранное таким образом 72-разрядное слово с вновь сформированным байтом корректирующего кода через соответствующий ВЫХОДНОЙ регистр передается в блок памяти. Управление приемом в регистры и выдачей с регистров осуществляет блок управления запросами, показанный на чертеже пунктиром. На входы поступают сигналы готовности информации из памяти по управляющим входам 14, соответствующим логическим блокам памяти. Поскольку в каждый момент времени может работать только один из блоков памяти в каждом логическом блоке, то на каждый узел приходит только один сигнал готовности. С помощью элемента ИЛИ 20 и цепочки последовательно соединенных триггеров 21 - 26, а также элемента И 27 формируется серия управляющих сигналов. Выход элемента И 27 (выход 15-1) стробирует прием информации из памяти на выходной регистр 5, выход триггера 24 (вькод 15-2) стробирует вькод вькодного регистра 5 на элемент ИЛИ 6, выход триггера 26 (выход 15-3) стробирует вькод информационного регистра 2 на элемент ИЛИ 4, а также прием записываемой информации . на выходной регистр 5 для передачи в память, выход триггера 23 формирует сигнал Запись в блоки памяти. Все блоки оперативной памяти должны иметь одинаковые параметры, т. е. время чтения и время записи у них должно быть одинаковым. Поэтому при последовательном обращении к логическим блокам памяти (на каждом следующем такте синхронизации процессора запускается следующий блок) сигналы готовности информации по управляющим входим 14 из памяти приходят в той же последовательности и с теми же промежутками времени между ними (равные одному такту синхронизации) , как и при запуске, что позволяет проводить последовательную выдачу с выходных регистров 5, последовательный анализ считанной информации в узел 7, последовательное формирование 72-разрядног:о слова для записи в память с новым кодом коррекции на одном и том же оборудовании. Режим одновременной работы блоков памяти, описанный вьпде, к назьшаемьгй режимом работы памяти с расслоением, является для современных ЭВМ основным; Устройство реализует работу оперативной памяти в режиме расслоения с коррекцией считанной из памяти информации при использовании одного корректора, одной группы элементов И-ИЛИ и одного формирователя корректирующего кода, т. е. с меньшим объемом оборудования по сравненшо с известным. Формула и 30 бретения Устройство для сопряжения основной памяти с процессором, содержащее по числу групп блоков памяти регистры адре са информационные регистры и выходные регистры, узел корреляции, формиро15а тель корректирующего кода и группу эле ментов И-ИЛИ, соответственно соединен ных входами с группой вькодов узла кор рекции и первой группой информационных выходов устройства, первая группа информационных входов и группа адресных входов которого подключены соответственно ко входам информадионньрс регистров и входам регистров адреса, выходы которых являются адресными выходами устройства, вторая группа информационных входов устройства соединена с первыми информационными входами соответствующих вьрсодных регистров, выходы группы элементов И-ИЛИ соединены с соответствующими входами формирователя корректирующего кода, отличающееся тем, что, с целью сок ращения аппаратурных затрат, в устройство введены узел выборки группы блоков памяти, два элемента ИЛИ и узлы синхронизации по числу групп блоков па мяти, причем выходы информационных регистров подключены-к соответствующи входам первого элемента ИЛИ, выход к 5 торого соединен с первым входом группы элементов И-ИЛИ, второй и третий информационные входы выходных регистров, первые выходы которых соединены с соответствующими выходами второй группы инфсрмаднонных выходов устройства, подключены соответственно к выходам элементов И-ИЛИ группы и вькодам формирователя кс эректкрующего кода, вторые выходы выходных регистров соединены с соответствующими входами второго элемента ИЛИ, подключенного выходом ко входу узла коррекции, входы каждого узла синхронизации являются соответствующими управляющими входами устройства, первьй, второй и третий выходы каждого узла синхронизации подключены к соответствующим управляющим входам одноименного выходного регистра, третий и четвертый выходы каждого узла синхронизации соединены соответственно с управляющим входом одноименного информационного регистра и соответствующим управляющим входом узла выборки блока памяти, входы которого подключены к выходам соответствующих регистров адреса, а выход является управляющим выходом устройства. Источники информации, принятые во внимание при экспертизе 1. Патент США № 3814921, кл. 340-172.5, 1972, 2.:)BNv Wvainietiatice Libtxin 5422-б8бОчэ S stem/1970 NVodeE 155 Ttieo - oi Opev-otion tAannat p4-1,diaio-rc3tm -1ОО ,97О

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения основной памяти с процессором | 1982 |

|

SU1037236A1 |

| Устройство для сопряжения памяти с процессором | 1982 |

|

SU1136176A1 |

| Устройство сопряжения контролируемого процессора с основной памятью | 1980 |

|

SU877550A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Устройство для контроля программ | 1987 |

|

SU1418720A1 |

| Устройство для сопряжения канала ввода-вывода с внешними устройствами | 1977 |

|

SU656050A1 |

| Запоминающее устройство с контролем | 1983 |

|

SU1120412A1 |

| ЭВМ | 1990 |

|

RU2024928C1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

Авторы

Даты

1980-05-25—Публикация

1977-06-06—Подача