1 CfipecE- Ы1 : вход б,гслй 8 ; r;iii lOHiibj,

рон

1€-.ПИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля кодовых жгутов постоянных запоминающих устройств | 1988 |

|

SU1603439A1 |

| Устройство для контроля прошивки кодовых жгутов ПЗУ | 1985 |

|

SU1309087A1 |

| Устройство для контроля кодовых жгутов ПЗУ | 1985 |

|

SU1336120A1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1411838A2 |

| Устройство для контроля постоянной памяти | 1984 |

|

SU1191944A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Устройство для программного управления с самоконтролем | 1983 |

|

SU1130832A1 |

| Способ контроля прошивки кодовых жгутов постоянного запоминающего устройства и устройство для его осуществления | 1984 |

|

SU1247950A1 |

| Устройство для формирования входных воздействий в системе программного контроля | 1980 |

|

SU920729A1 |

| Устройство для моделирования радиотелеграфного канала связи | 1981 |

|

SU1034053A1 |

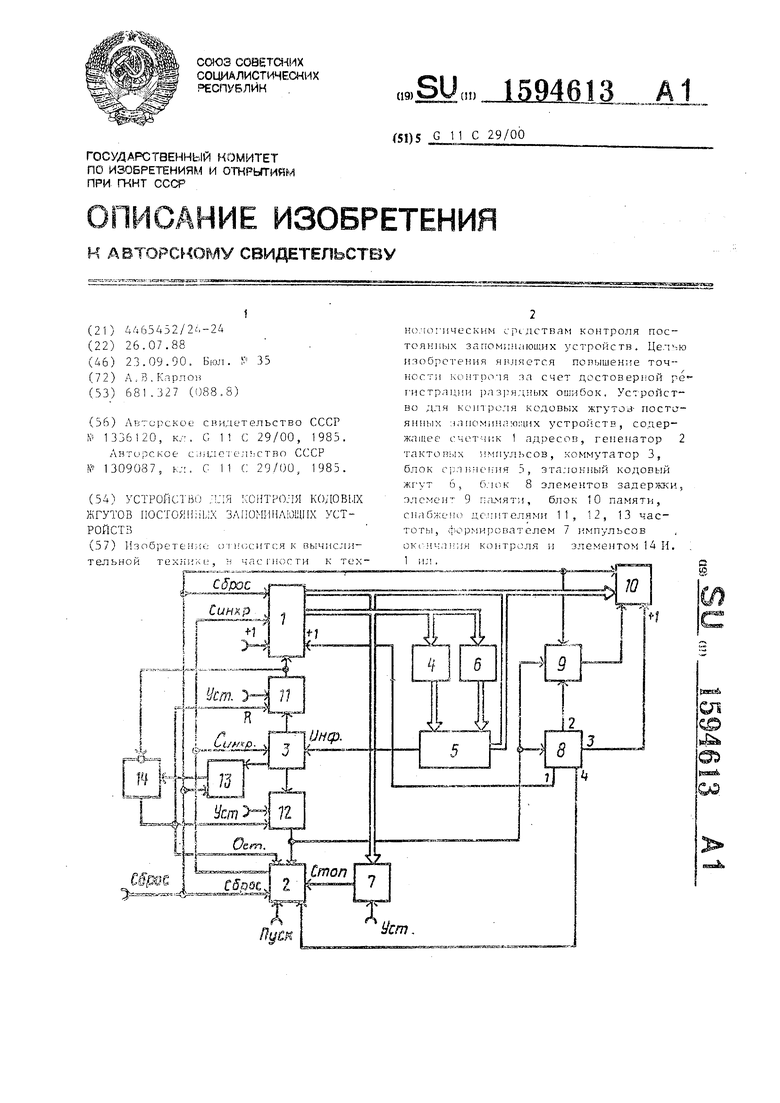

Изобретение относится к вычислительной технике, в частности к технологическим средствам контроля постоянных запоминающих устройств. Целью изобретения является повышение точности контроля за счет достоверной регистрации разрядных ошибок. Устройство для контроля кодовых жгутов постоянных запоминающих устройств, содержащее счетчик 1 адресов, генератор 2 тактовых импульсов, коммутатор 3, блок сравнения 5, эталонный кодовый жгут 6, блок 8 элементов задержки, элемент 9 памяти, блок 10 памяти, снабжено делителями 11,12,13 частоты, формирователем 7 импульсов окончания контроля и элементом 14 И. 1 ил.

;ОИ ус- Быхсдо: третий

оого сее :v;veMo:- o 4

iHCTuas инфрр

, „,-,,- л i ; ,., 1 7

TOIiljlX И,1.;ГУЛ.:С:С В . ;Л к : -ь: ;

-|3рез . i по г р/л:-с л

/ которое ypeMfi ., с:- ;. -- ; /г

СЧД УКИДМ :iji6:- i b i O .п--;

комкута 1 оре о,, ь л.сл ад л;.-;-- .:-..,..,- .- изет ся сигнал с оотЕетс «и;: xHWL jM i.iMi

жгутов 4 и i: в каждом илфог:- ц--- но

Н ооврде (адрес ЗУ),

Ирь: эиги5; :а в fipcu;:.5bX : ;:: ;;,; ; - 1лент 9 загшсываетср е p.Rsp j: ; ; a-sK запись в блок i О и :фор -1а1и- л cR -дс;; ::е и характере опкбкч н; :- ер, рЯЯИОЙ ОИЮлбКН

в случае правильной прошивки ПЗУ по данному адресу содержимое счетчика 1 увеличивается на 1 для контроля следующих информагшонных проводов ПЗУ.

Достоверность результата обеспечивается многократностью сразнения информации по одному и тому же адресу, например, бинарным считыванием. При этом переход к очередной ячейке контроля осуществляется заданным в делителях 11 и 12 количеством либо ошибок, либо правильных результатов контроля данного информационного провода ПЗУ.

При поступлении на вход делителя 11 заданного количества импульсов правипьного результата контроля сигналом с его выхода содержимое счетчика i увеличивается на 1. В противном случае Рхоммутатор 3 посылает на вход делителя 12 импульсы ошибки, количество которых (для получения на входах генератора 2, блока 8 и элемента 9 сигнала гарантированной ошибки) не; должно быть меньше заданного. В этом случае сигналом элемента 9 в блек 10 зяписыва п гея адррс и разряд ошибки. Затем сигналами блока 8 элемент 9 сбрасывается, содержимое ад- ряса в блоке 10 и в счетчике 1 увеличивается на 1, после чего запускается генератор 2, останавливаемый при правильных результатах лишь формирователем 7,

При правильном и неправильном результатах в одном дакле опроса жгутов 4 .и 6 устройством не регистрируется в блоке 10 адрес, а счетчик 1 не изменяет своего адреса. Генератор 2 в этом случае сигналом с элемента И 14 останавливается, как только делитель 13 установит окончание цикла контроля, состоящего из нескольких тактов опроса жгутов 4 и 6.

Формула изобретения

Устройство для контроля кодовых жгутов постоянных запоминающих устройств, содержащее счетчик адресов, первый тактовый вход которого является входом увеличения адреса устройства, второй тактовый вход соединен с первым выходом блока элементов задержраа, информационные выходы первой группы - с соответствующими ин- формацнонньгми входами блока памяти, информационные выходы второй груп94613

пы - с соответствующими входами контролируемого и эталонного кодовых жгутов, а вход сброса является входом устройства и подключен к соответст- вующему входу генератора тактовых импульсов и первым установочным входам блока памяти и элемента- памяти, выход которого соединен с разрешающим .п входом блока памяти, а второй уста- HOBD4HbDi вход блока памяти соединен с вторым выходом блока элементов задержки, третий выход блока элементов задержки подключен к адресному входу .г блока памяти, а четвертый выход - к первому входу запуска генератора, второй вход запуска которого является соответствующим входом устройства, а выход соединен с синхровходамт; счет- 2Q чиков адресов и коммутатора, информационный вход которого подключен к выходу результата блока сравнения, первый и второй входы которого соеди нены с выходами контр9лируемого и 25 эталонного кодовых жгутов, о т л и - чающееся тем, что, с целью повьп1 ения точности ко1 троля, оно содержит первый, второй.и третий делители частоты и формирователь импульсов окончания контроля, установочные входь которых являются соответствующими установочными входами устройства, и элемент И, причем 1нформаци- онные входы первого и второго делителей частоты подключены к соответст- 35 вуюишм информац};онным выходам коммутатора, входы сброса - к выходу элемента И, а выходы - соответственно к третьему тактовому входу сч.ет- чика адресов и входу блока элементов задержки, входу записи элеме та памя- ти и первому входу останова генератора тактовых импульсов, выход л инфор- ма 1 1онные входы формирователя и шyль- сов окончания контроля соединены со- 45 ответственно с вторым входом останова генератора тактовых импульсов и с со- ответствующ1ми информационньпчи выходами nepBOf: группы счетчика адресов, инфopмaщ oнныe выходы блока сраБнения 50 подключены к соответствуюш,им информа- ционньм входам блока памяти, информационный вход третьего делителя частоты соединен с синхровыходом коммутатора, вход сброса - с соответствую- 55 щим входом устройства, а выход - с первым входом, элемента Н, второй вход которого подключен к выходу первого делителя частоты, а выход - к третьему входу останова генератора.

30

Авторы

Даты

1990-09-23—Публикация

1988-07-26—Подача