о о

СО

со ю

Изобретение относится к вычислительной технике, в частности к техническим средствам контроля запоминающих устройств, и может быть использовано при организации технологических процессов автоматизированного производства накопителей запоминающих блоков.

Целью изобретения являзтся повышение точности контроля за счет идентификации ошибок и правильных результатов.

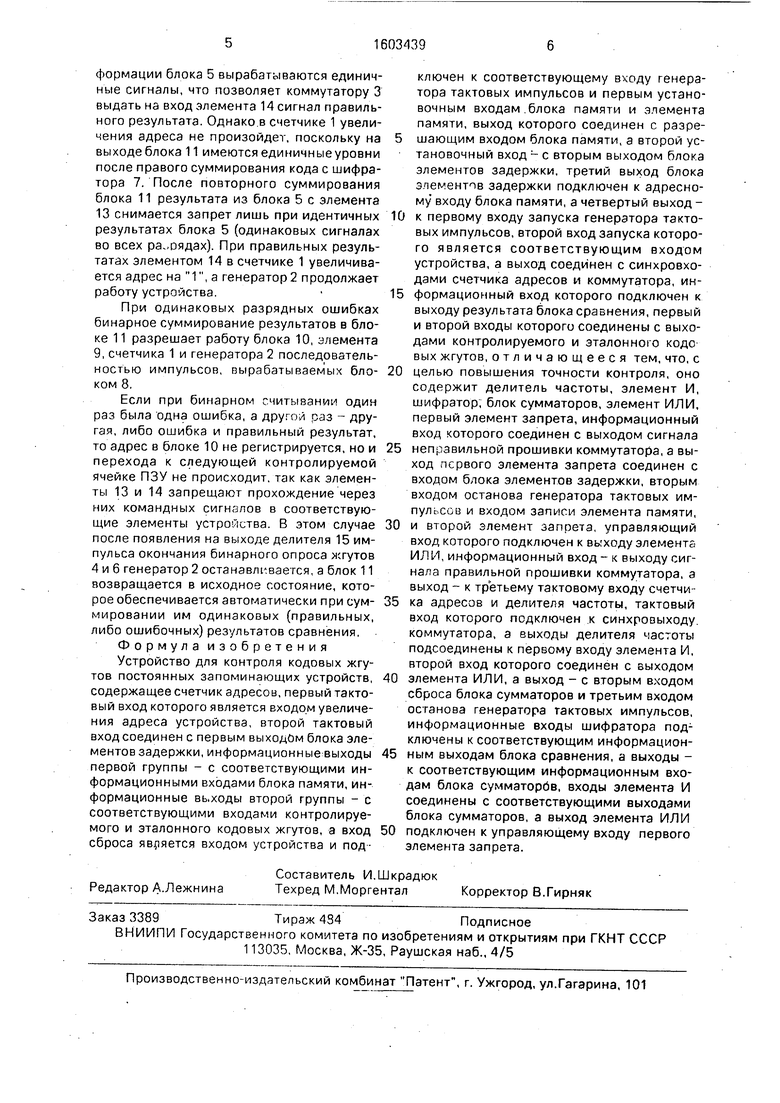

На чертеже схематично изображено предлагаемое устройство.

Устройство содержит счетчик 1 адресов, генератор 2 тактовых импульсов, коммутатор 3, контролируемый кодовый жгут 4, блок 5 сравнения, эталонный кодовый жгут 6, шифратор 7, блок 8 элементов задержки, узел 9 памяти, блок 10 памяти, блок 11 сумматоров, элемент ИЛИ 12, элементы 13 и 14 запрета, делитель 15 частоты и элемент И 16.

В статическом состоянии в устройстве первый тактовый вход счетчика 1 адреса является входом увеличения адреса устройства, второй тактовый вход соединен с первым выходом блока 8 элементов задержки, информационные выходы первой группы соединены с соответствующими информационными входами блока 10 памяти, информационные выходы второй группы - с соответствующими входами контролируемого 4 и эталонного 6 кодовых жгутов, син- хровход соединен с выходом генератора 2 тактовых импульсов, а вход сброса является соответствующим входом устройства и подключен к первому входу сброса генератора 2 тактовых импульсов и первому установочному входу элемента 9 памяти, выход которого соединен с разрешающим входом блока 10 памяти, а второй установочный вход - с вторым выходом блока В элемента задержки, третий выход которого подключен к адресному входу блока 10 памяти, а четвертый выход - к первому входу запуска генератора 2 тактовых импульсов, второй вход запуска которого является соответствующим входом устройстЁа, а выход соединен с синхровходами счетчика 1 адресов и коммутатора 3. Вход останова генератора 2 подключен к одному из информационных , выходов первой группы счетчика 1 адресов. Информационный вход коммутатора 3 соединен с выходом результата блока 5 сравнения, первый и второй входы которого подключены соответственно к выходам контролируемого 4 и эталонного 6 кодовых жгутов. Информационный вход элемента 13 запрета соединен с первым информационным выходом коммутатора 3, а выход - с входом блока 8 элементов задержки, входом останова генератора 2 и входом записи элемента 9 памяти. Управляющий вход элемента 14 запрета подключен к выходу элемента ИЛИ 12, информационный вход - к выходу сигнала правильной прошивки коммутатора 3, а выход - к третьему тактовому входу счетчика 1 адресов. Первый вход сброса блока 11 сумматоров соединен с входами сбррса блока 10 памяти, счетчика 0 1 адресов и делителя 15 частоты, тактовый вход которого подключен к синхровыходу коммутатора 3, а выход - к первому входу элемента И 16, второй вход которого соединен с выходом элемента ИЛИ 12, а выход - 5 с вторым входом сброса блока 11 сумматоров и третьим входом останова генератора 2. Информационные входы шифратора 7 подключены к соответствующим информационным выходам блока сравнения, а 0 информационные выходы - к соответствующим информационным входам блока 11 сумматоров. Входы элемента ИЛИ 12 соединены с соответствующ ими выходами блока сумматоров, а выход - с управляю- 5 щим входом первого элемента 13 запрета.

Устройство работает следующим образом.

По входу Сброс устройство приводится в исходное состояние, а сигналом по 0 входу Пуск генератор 2 выходными импульсами через счетчик.1 поочередно считывает информацию со жгутов 4 и 6, а через некоторое время, определяемое соответствующим элементом в коммутаторе 3, в по- 5 следнем вырабатывается сигнал соответствия информации жгутов 4 и 6 в каждом информационном проводе (адресе ПЗУ).

При ошибке в прошивке ПЗУ в элемент 0 9 записывается 1, разрешающая запись в блок 10 информации об адресе и характере ошибки, например, разрядной ошибки.

В случае правильной прошивки ПЗУ по данному адресу содержимое счетчика 1 уве- 5 личивается на 1 для контроля следующих информационных проводов ПЗУ.

Достоверность результата обеспечивается многократностью сравнения информации по одному и тому же адресу, например, 0 бинарным считыванием. При этом переход к очередной ячейке контроля осуществляется заданным количеством либо ошибок, либо правильных результатов контроля данного информационного провода ПЗУ. 5 Закодированный в шифраторе 7 результат одновременного считывания информации со жгутов 4 и 6 поступает на разрядные .элементы суммирования блока 11.

При соотве1тствии информации жгутов 4 и 6 на всех элементах воспроизведения информации блока 5 вырабатываются единичные сигналы, что позволяет коммутатору 3 выдать на вход элемента 14 сигнал правильного результата. Однако.в счетчике 1 увеличения адреса не произойдет, поскольку на выходе блока 11 имеются единичныеуровни после правого суммирования кода с шифратора 7. После повторного суммирования блока 11 результата из блока 5 с элемента 13 снимается запрет лишь при идентичных результатах блока 5 (одинаковых сигналах во всех ра.,оядах). При правильных результатах элементом 14 в счетчике 1 увеличивается адрес на 1, а генератор 2 продолжает работу устройства.

При одинаковых разрядных ошибках бинарное суммирование результатов в блоке 11 разрешает работу блока 10, алемента 9, счетчика 1 и генератора 2 последовательностью импульсов, вырабатываемых блоком 8.

Если при бинарном считывании один раз была одна ошибка, а другой раз - другая, либо ошибка и правильный результат, то адрес в блоке 10 не регистрируется, но и перехода к следующей контролируемой ячейке ПЗУ не происходит, так как элементы 13 и 14 запрещают прохождение через них командных сигналов в соответствующие элементы устройства. В этом случае после появления на выходе делителя 15 импульса окончания бинарного опроса жгутов 4 и 6 генератор 2 останавливается, а блок 11 возвращается в исходное состояние, которое обеспечивается автоматически при суммировании им одинаковых (правильных, либо ошибочных) результатов сравнения, Формула изобретения Устройство для контроля кодовых жгутов постоянных запоминающих устройств, содержащее счетчик адресов, первый тактовый вход которого является входом увеличения адреса устройства, второй тактовый вход соединен с первым выходим блока элементов задержки, информационньЮ Выходы первой группы - с соответствующими информационными входами блока памяти, информационные выходы второй группы - с соответствующими входами контролируемого и эталонного кодовых жгутов, а вход сброса яв{1яется входом устройства и подключен к соответствующему входу генератора тактовых импульсов и первым установочным входам.блока памяти и элемента памяти, выход которого соединен с разре- 5 шающим входом блока памяти, а второй установочный вход - с вторым выходом блока элементов задержки, третий выход блока элементов задержки подключен к адресному входу блока памяти, а четвертый выход - 10 к первому входу запуска генератора тактовых импульсов, второй вход запуска которого является соответствующим входом устройства, а выход соединен с синхровхо- дами счетчика адресов и коммутатора, ин- 15 формационный вход которого подключен к выходу результата блока сравнения, первый и второй входы которого соединены с выходами контролируемого и эталонного кодо вых жгутов, отличающееся тем, что, с 20 целью повышения точности контроля, оно содержит делитель частоты, элемент И, шифратор; блок сумматоров, элемент ИЛИ, первый элемент запрета, информационный вход которого соединен с выходом сигнала 5 неправильной прошивки коммутатора, а выход первого элемента запрета соединен с входом блока элементов задержки, вторым входом останова генератора тактовых импульсов и входом записи элемента памяти, 0 и второй элемент запрета, управляющий вход которого подключен к выходу элемента ИЛИ, информационный вход - к выходу сигнала правильной прошивки коммутатора, а выход - к третьему тактовому входу счетчи- 5 ка адресов и делителя частоты, тактовый вход которого подключен .к синхрооыходу. коммутатора, а выходы делителя частоты подсоединены к первому входу элемента И, второй вход которого соединен с выходом 0 элемента ИЛИ, а выход - с вторым входом сброса блока сумматоров и третьим входом останова генератора тактовых импульсов, информационные входы шифратора подключены к соответствующим информацион- 5 ным выходам блока сравнения, а выходы - к соответствующим информационным входам блока сумматорбв, входы элемента И соединены с соответствующими выходами блока сумматоров, а выход элемента ИЛИ 0 подключен к управляющему входу первого элемента запрета.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля кодовых жгутов постоянных запоминающих устройств | 1988 |

|

SU1594613A1 |

| Устройство для контроля прошивки кодовых жгутов ПЗУ | 1985 |

|

SU1309087A1 |

| Устройство для контроля кодовых жгутов ПЗУ | 1985 |

|

SU1336120A1 |

| Устройство для регистрации простоев оборудования | 1986 |

|

SU1374262A1 |

| Способ контроля прошивки кодовых жгутов постоянного запоминающего устройства и устройство для его осуществления | 1984 |

|

SU1247950A1 |

| Устройство для ввода информации | 1982 |

|

SU1062683A1 |

| Телеметрическая система со сжатием информации | 1991 |

|

SU1837349A1 |

| Устройство для контроля памяти | 1981 |

|

SU985831A1 |

| Многоканальное устройство для сопряжения | 1985 |

|

SU1282142A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

Изобретение относится к вычислительной технике, в частности к техническим средствам контроля кодовых жгутов постоянных запоминающих устройств. Цель изобретения - повышение точности контроля за счет идентификации ошибок и правильных результатов. Указанная цель достигается тем, что устройство, содержащее счетчик адресов 1, генератор 2 тактовых импульсов, коммутатор 3, блок 5 сравнения, эталонный кодовый жгут 6, шифратор 7, блок 8 элементов задержки, узел 9 памяти, блок 10 памяти, дополнительно снабжено блоком 11 сумматоров, элементом ИЛИ 12, элементами 13 и 14 запрета, делителем 15 частоты и элементом И 16. 1 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля прошивки кодовых жгутов ПЗУ | 1985 |

|

SU1309087A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1990-10-30—Публикация

1988-07-26—Подача