вход второго блока сравнения соединены с выходом счетчика, выход дешифратора соединен с вторым входом коммутатора, выход

формирователя адресных сигналов и четвертый выход формирователя управляющих сигналов являются выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля постоянной памяти | 1987 |

|

SU1411838A2 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU886059A1 |

| Устройство для контроля электрического монтажа | 1985 |

|

SU1390616A1 |

| Устройство для контроля электрического монтажа | 1985 |

|

SU1345212A1 |

| Устройство для контроля постоянных запоминающих устройств | 1976 |

|

SU563697A1 |

| Устройство для контроля постоянных запоминающих устройств | 1976 |

|

SU622175A2 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1151991A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1138809A1 |

| Устройство для контроля памяти | 1982 |

|

SU1020865A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСТОЯННОЙ ПАМЯТИ, содержащее блок элементов коммутации, блок управления, блок ввода контрольных сигналов, блок элементов И-ИЛИ, счетчик, генератор тока, блок индуктивных датчиков, формирователь информационных сигналов, формирователь адресных сигналов, первый блок сравнения, блок регистрации ошибок, первый вход которого соединен с первым входом первого блока сравнения и является входом устройства, выход первого блока сравнения соединен с первым входом блока управления, второй вход первого блока сравнения и первый вход блока элементов И-ИЛИ соединен с первым выходом блока ввода контрольных сигналов, второй выход которого соединен с вторыми входами блока управления и блока элементов И-ИЛЙ, первый выход блока элементов коммутации соединен с входом блока ввода контрольных сигналов, второй выход блока элементов коммутации соединен с третьим входом блока элементов И-ИЛИ, третий выход элементов коммутации соединен с четвертым входом блока элементов И-ИЛИ, третий вход блока управления соединен с выходом блока регистрации ошибок, второй вход которого соединен с первым выходом блока управления, второй выход которого соединен с первым входом счетчика, второй вход которого соединен с выходом блока элементов ИИЛИ, выход счетчика соединен с третьим входом блока регистрации ошибок и первым входом форм ирователя адресных сигналов, выход генератора тока соединен с первым входом блока индуктивных датчиков, выход которого соединен с первым входом формирователя информационных сигналов, выход, которого соединен с третьим входом первого блока сравнения, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены формирователь управляющих сигналов, регистр адреса, второй блок сравнения, дешифратор,, коммутатор, блок контроля контактирования кодовых жгутов и элемент задержки, выход которого соединен с вторым входом формирователя информационных сигналов, второй вход блока индуктивных датчиков соединен с первым выходом коммутатора, второй выi ход которого соединен с входом блока кон(Л троля контактирования кодовых жгутов, выход которого соединен с первым входом формирователя управляющих сигналов, второй вход которого соединен с вторым выходом блока ввода контрольных сигналов, третий и четвертый выходы формирователя управляющих сигналов соединены соответственно с третьим и четвертым входами блока управления, четвертый вход которого со соединен с выходом второго блока сравне ния, первый вход которого соединен с выхо ;о 4;: дом регистра адреса, первый и второй входы которого соединены соответственно с третьим и четвертым выходами блока элементов коммутации, пятый выход которого соединен с пятым выходом блока управления и блока формирования управляющих сигналов, первый выход которого соединен с вторым входом формирователя адресных сигналов, второй выход формирователя управляющих сигналов соединен с шестым входом блока управления, третий выход формирователя управляющих сигналов соединен с входом элемента задержки и первым входом дешифратора, второй вход дешифратора, первый вход коммутатора и второй

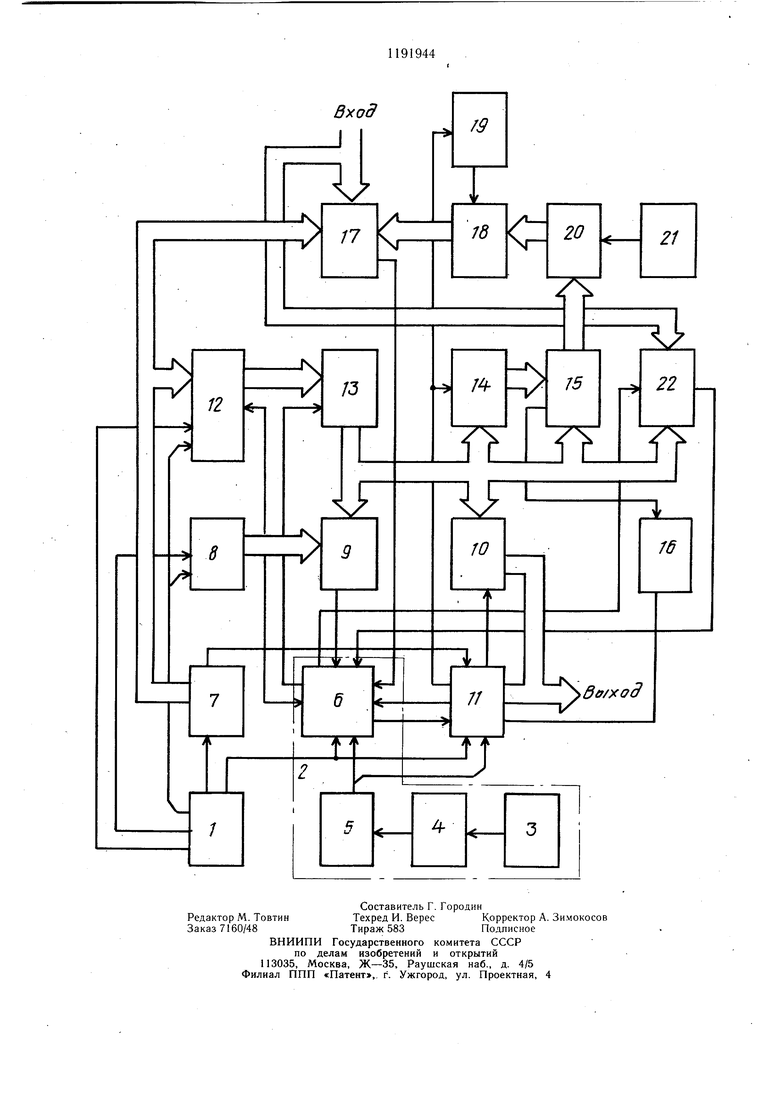

Изобретение относится к вычислительной технике, а именно к устройствам контроля, и может быть использовано для контроля правильности хранения информации в постоянных запоминающих устройствах. Целью изобретения является повышение быстродействия устройства. На чертеже представлена структурная схема устройства. Устройство для контроля постоянной памяти содержит блок 1 элементов коммутации, блок 2 управления, состоящий из мультивибратора 3, делителя 4 частоты, формирователя 5 тактовых импульсов и распределителя 6 тактовых импульсов, блок 7 ввода контрольных сигналов, регистр 8 адреса, второй блок 9 сравнения, формирователь 10 адресных сигналов, формирователь 11 управляющих сигналов, блок 12 элементов И-ИЛИ, счетчик 13, дешифратор 14, коммутатор 15, блок 16 контроля контактирования кодовых жгутов, первый блок 17 сравнения, формирователь 18 информационных сигналов, элемент 19 задержки, блок 20 индуктивных датчиков, генератор 21 тока, блок 22 регистрации ошибок. Устройство работает следующим образом. При контроле блоков постоянной памяти они подключаются к входу и выходу устройства. При контроле кодовых жгутов они укладываются на сердечники индуктивных датчиков. При проверке осуществляется сравнение чисел в двоичном коде, считанных с контролируемого блока памяти или кодового жгута с контрольными числами. При проверке по перфоркартам работа устройства начинается .от пускового сигнала с первого выхода блока 1 на вход блока 7. По мере продвижения перфокарты числовая информация поступает на второй вход блока 17, а адресная - через первый вход блока И-ИЛИ на второй вход счетчика. Одновременно на втором выходе блока 7 формируется сигнал сопровождения и т.д. При проверке кодовых жгутов сигнал опроса кодового жгута формируется дещифратором по стробирующему импульсу, поступающему на второй вход с одного из выходов блока 11. После опроса кодового жгута формируются сигналы, которые поступают на вход формирователя 18. Так как эти сигналы имеют колебательный характер, то производится их стробирование задержанным сигналом опроса через элемент 19 и после формирования они поступают на третий вход блока 17.

| Устройство для контроля постоянных запоминающих устройств | 1976 |

|

SU563697A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU886059A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-11-15—Публикация

1984-04-16—Подача