Изобретение относится ic импульсной технике и мозкет использоваться , при производстве пересчетных схем, сдвигаюпсих и параллелыых регистров, а также в автоматике, вычислитель-- ных и информа1да онно-измерительных комплексах.

Целью изобретения является повышение быстродействия за счет введени новых конструктивных признаков, обес печивакядих уменьшение задержки сигнала от входа триггера к его выходу.

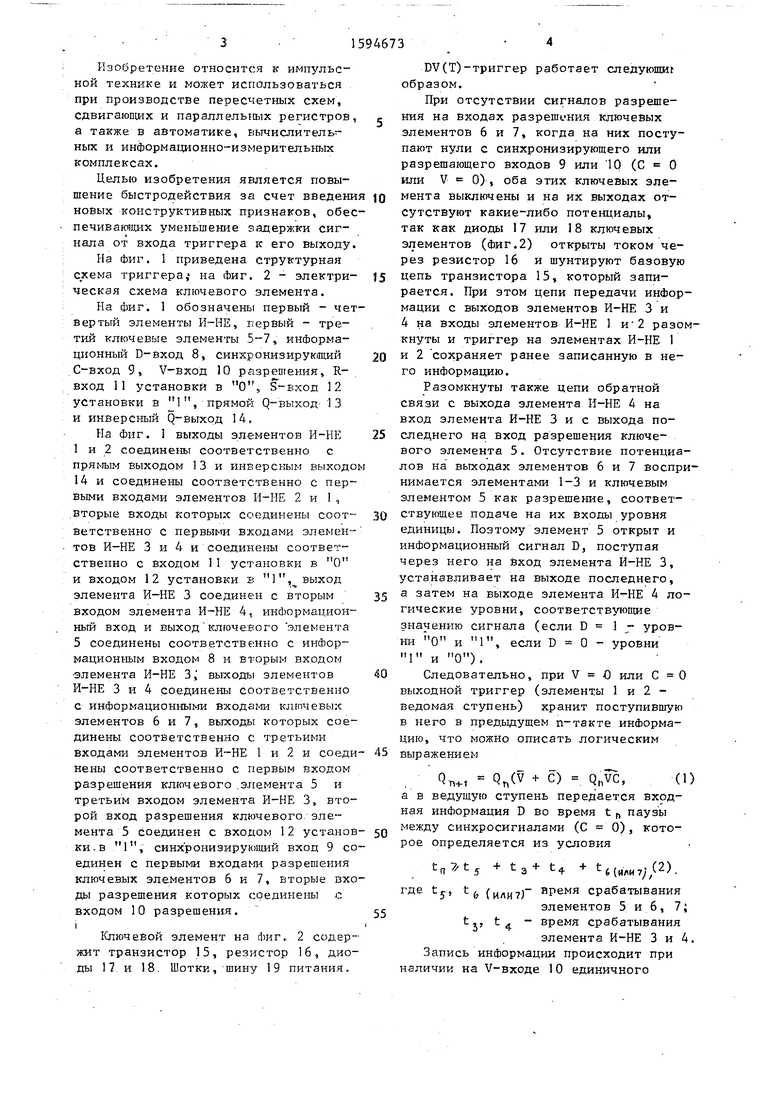

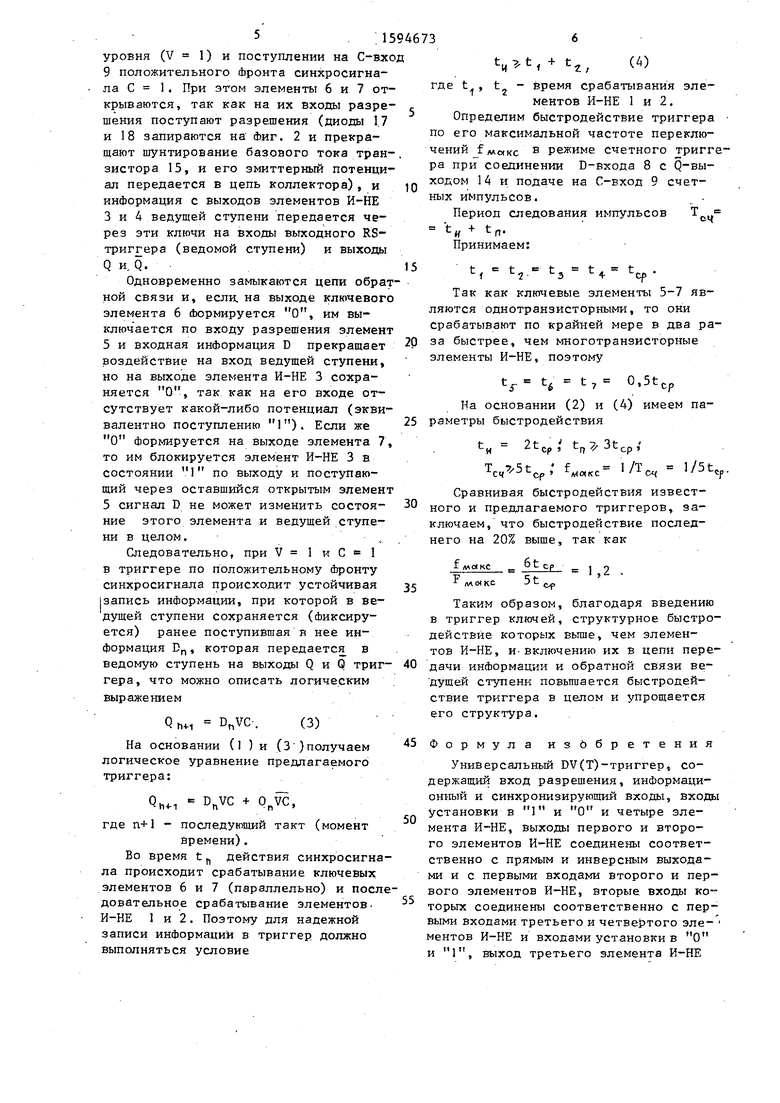

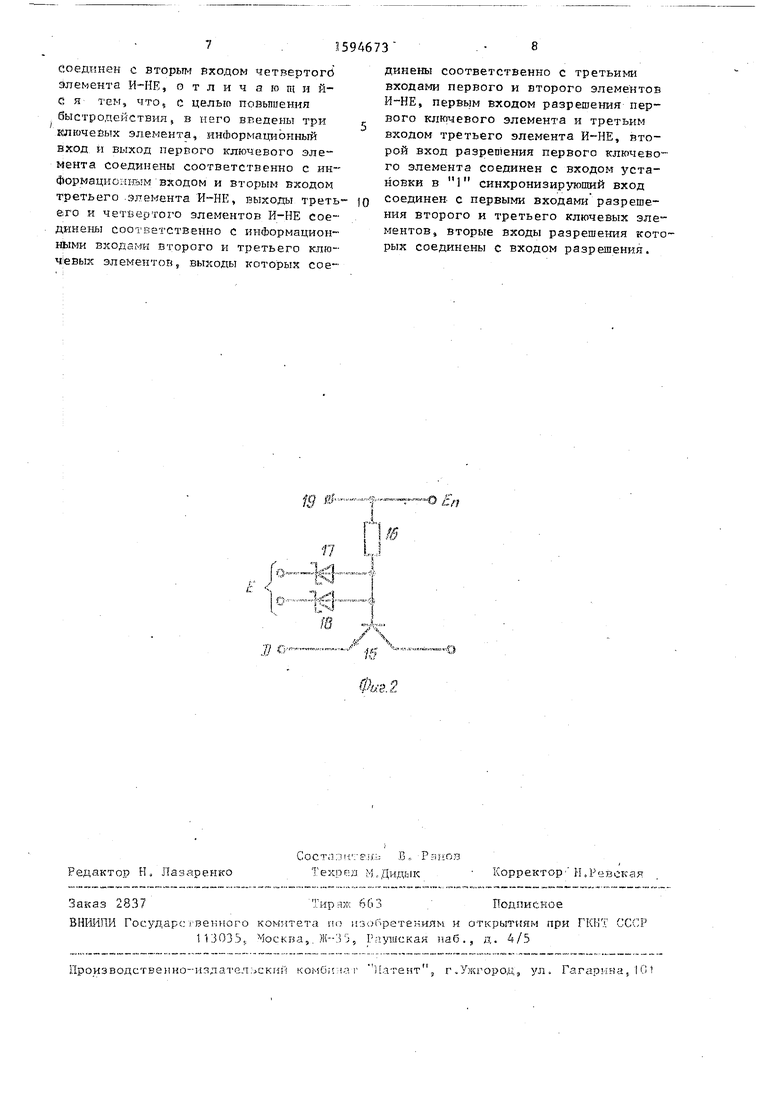

На фиг. 1 приведена структурная схема триггера, на Фиг. 2 - электри- ческая схема ключевого элемента.

На фиг. 1 обозначешз первый - четвертый элементы И-НЕ, первый - третий ключевые элементы 5-7, информа- ционньш D-вход 8, синхронизирующий С-вход 9, V-вход 10 разрешения, R- вход 11 установки в О, S -вхоп 12 установки в I, прямой Q-выход 13 и инверсный Q-выход 14,

На Фиг. выходы элементов И-НЕ 1 и 2 соединены соответственно с прямым выходом 13 и инверсным выходо 14 и соединены соответственно с первыми входами элементов И-ИЕ 2 и 1 ,, ,вторые входы которых со«гдинены соот- ветственно с первыми входами элементов И-НЕ 3 и 4 и соединены соответственно с входом 11 установки в О и входом 12 установки в 1,выход элемента И--НЕ 3 соединен с вторым входом элемента И-НЕ 4, информационный вход и выход ключевого элемента 5 соединены соответственно с инфор- мационьшм входом 8 и вторым входом элемента И-НЕ 3j выходы элементов И-НЕ 3 и 4 соединены соответственно с информационными вжодаг-ш ключевых элементов 6 и 7, выходы которых соединены соответственно с третьими входами элементов И-НЕ 1 и 2 и соеди иены соответственно с первым входом разрешения ключевого .элемента 5 и третьим входом элемента И-НЕ 3, второй вход разрешения ключевого, элемента 5 соединен с входом 12 установ ки-в 1, синхронизирующий вход 9 соединен с пepвы Jи входами разрешения ключевых элементов 6 и 7, вторые входы разрешения которых соединены с входом 10 разрешения.

i

Ключевой элемент на Фиг., 2 содержит транзистор 15, резистор 16, диоды 17. и 18. Шотки, шину 19 питания.

ОУ(Т)-триггер работает следующиг образом.

При отсутствии сигналов разрешения на входах разрешения ключевых элементов 6 и 7, когда на них поступают нули с синхронизирующего или разрешающего входов 9 или 10 (С О или V 0), оба этих ключевых элемента выключены и на их выходах отсутствуют какие-либо потенциалы, так как диоды 17 или 18 ключевых элементов (фиг.2) открыты током через резистор 16 и шунтируют базовую цепь транзистора 15, который запирается. Нри этом цепи передачи информации с выходов элементов И-НЕ 3 и 4 на входы элементов И-НЕ 1 и 2 разокнуты и триггер на элементах И-НЕ 1 и 2 сохраняет ранее записанную в него информацию.

Разомкнуты также цепи обратной связи с выхода элемента И-НЕ 4 на вход элемента И-НЕ 3 и с выхода последнего на вход разрешения ключевого элемента 5. Отсутствие потенциалов на выходах элементов 6 и 7 воспрнимается элементами 1-3 и ключевым элементом 5 как разрешение, соответствующее подаче на их входы уровня единицы. Ноэтому элемент 5 открыт и информационный сигнал D, поступая через него на вход элемента И-НЕ 3, устанавливает на выходе последнего, а затем на выходе элемента И-НЕ 4 логические уровни, соответствующие значению сигнала (если D 1 j- уровни О и 1, если D О - уровни 1 и О).

Следовательно, при V О или С О выходной триггер (элементы 1 и 2 - ведомая ступень) хранит поступившую в него в предьщушем п-такте информацию, что можно описать логическим выражением

Qn, Q(V + С) Q,VC, ( а в ведущуЕо ступень передается входная информация D во время t пауз ы между синхросигналами (С 0), которое определяется из условия

+ t , + t.

- Ч(или7;Я).

где tj-, t (или7) время срабатывания элементов 5 и 6, 7i tj, t - время срабатывания

элемента И-НЕ 3 и 4. Запись информации происходит при наличии на V-входе 10 единичного

5: 15

уровня (V 1) и поступлении на С-вхо 9 положительного Лронта синхросигнала С 1. При этом элементы 6 и 7 от- крываются, так как на их входы разрешения поступают разрешения (диоды 1.7 и 18 запираются на Фиг. 2 и прекращают шунтирование базового тока транзистора 15, и его эмиттерный потенциал передается в цепь коллектора), и информация с выходов элементов И-НЕ 3 и 4 ведущей ступени передается через эти ключи на входы выходного RS- триггера (ведомой ступени) и выходы Q и Q.

Одновременно замыкаются цепи обратной связи и, если, на выходе ключевого элемента 6 Формируется О, им выключается по входу разрешения элемент 5 и входная информация D прекращает воздействие на вход ведущей ступени, но на выходе элемента И-НЕ 3 сохраняется О, так как на его входе отсутствует какой-либо потенциал (экви

валентно поступлению 1). Если же О формируется на выходе элемента 7 то им блокируется элемент И-НЕ 3 в состоянии 1 по выходу и поступающий через оставшийся открытым элемен 5 сигнал D не может изменить состояние этого элемента и ведущей ступени в целом.,

Следовательно, при V 1 к С 1 в триггере по положительному Фронту синхросигнала происходит устойчивая запись информации, при которой в ведущей ступени сохраняется (Фиксируется) ранее поступившая в нее информация D, которая передается в ведомую ступень на выходы Q и О триггера, что можно описать логическим выражением

Q hM . (3)

На основании (l ) и (З )получаем логическое уравнение предлагаемого триггера:

+ . где n+1 - последующий такт (момент

времени).

Во время t fi действия синхросигнала происходит срабатывание ключевых элементов 6 и 7 (параллельно) и последовательное срабатывание элементов. И-НЕ 1 и 2. Поэтому для надежной записи информации в триггер должно выполняться условие

t ч,

(4)

, t - время срабатывания элементов И-НЕ 1 и 2.

Определим быстродействие триггера по его максимальной частоте переклю- чений лАО(кс режиме счетного триггра при соединении D-входа 8 с Q-вы- ходом 14 и подаче на С-вход 9 счетных импульсов.

Период следования импульсов Т.

П

Ч + t, Принимаем:

t, t.

сч

ta Ч

f 2- Э -4 Cf Так как ключевые элементы 5-7 являются однотранзисторными, то они срабатывают по крайней мере в два раза быстрее, чем многотранзисторные элементы И-НЕ, поэтому

6

0,5t,

J- --б - 7 - f -tp

На основании (2) и (4) имеем па- раметры быстродействия

7t-

5

сч - Ь р

,- млкс сч

Сравнивая быстродействия известного и предлагаемого триггеров, заключаем, что быстродействие последнего на 20% выше, так как

35

f такс

1 ДА 01 КС

1,2

0

5

0

Таким образом, благодаря введению в триггер ключей, структурное быстродействие которых выше, чем элементов И-НЕ, и-включению их в цепи передачи информации и обратной связи ведущей ступени повышается быстродействие триггера в целом и упрощается его структура.

Формула изббретения

Универсальный DV(Т)-триггер, содержащий вход разрешения, информационный и синхронизирующий входы, входы установки в I и О и четыре элемента И-НЕ, выходы первого и второго элементов И-НЕ соединены соответственно с прямым и инверсным выходами и с первыми входами второго и первого элементов И-НЕ, вторые входы которых соединены соответственно с первыми входами третьего и четвертого эле- ментов И-НЕ и входами установки в О и 1, выход третьего элемента И-НЕ

соединен с вторым входом четвертого элемента И-НЕ, отличаю щ и й- CS я тем, ЧТО; с целью повьпиения .быстродействия, в него введены три ключевых элемента, информационный вход и выход первого ключевого элемента соединены соответственно с ин-- Формационшш входом и вторым входом третьего .элемента И-НЕ, выходы третьего и четвертого элементов И-НЕ соединены соответственно с ннформацион- HbiMH входами второго и третьего клю- элеь{ентов, выходы которых сое

динены соответственно с третьими входами первого и второго элементов И-НЕ, первым входом разрешения первого ключевого элемента и третьим входом третьего элемента И-НЕ, второй вход разреп1ения первого ключевого элемента соединен с входом установки в 1 синхронизирующий вход соединен с первыми входами разрешения второго и третьего ключевых элементов, вторые входы разрешения которых соединены с входом разрешения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Универсальный DV(Т)-триггер | 1989 |

|

SU1698957A1 |

| Универсальный Д(Т)-триггер | 1988 |

|

SU1561200A1 |

| Универсальный DV(Т)-триггер | 1987 |

|

SU1552358A1 |

| Устройство обработки информации | 1989 |

|

SU1631549A1 |

| Мультимикропрограммная система управления | 1985 |

|

SU1291981A1 |

| Устройство для считывания графической информации | 1987 |

|

SU1550549A1 |

| Устройство для воспроизведения информации с многодорожечного магнитного носителя | 1978 |

|

SU763953A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ КОДОВОГО СИГНАЛА | 2007 |

|

RU2345479C1 |

| Устройство для синхронизации импульсов | 1977 |

|

SU741441A1 |

Изобретение относится к импульсной технике и может использоваться при производстве пересчетных схем, сдвигающих и параллельных регистров, а также в автоматике, вычислительных и информационно-измерительных комплексах. Цель изобретения - повышение быстродействия достигается за счет ведения ключевых элементов 5-7. Триггер также содержит элементы И-НЕ 1-4, информационный D-вход 8, синхронизирующий C-вход 9V-вход 10 разрешения, R-вход установки в "0", S-вход установки в "1", прямой Q-выход 13 и инверсный Q-выход 14. В предлагаемом DV /T/-триггере сокращена задержка распространения сигнала от входа триггера к его выходу. 2 ил.

W fff-f -.- -Q En

rj

i r xj .i

™„1й 1„„„-,: Ы

/Tj

„.s,,

I ч

1 с-- - 0

fe.2

„.s,,...

I ч

| Якубовский С,Е, Аналоговые и 1ци4|ровь е интегральные схемы,-М.: Советское радио, 1979, с,67-68, рис, 3, | |||

| Приспособление для удаления таянием снега с железнодорожных путей | 1920 |

|

SU176A1 |

| Валиев К,А, и др , Микромошные интегральные схемы,- М,: Советское радио, 1975, с.95, рис,4,12. | |||

Авторы

Даты

1990-09-23—Публикация

1988-11-21—Подача