Изобретение относится к вычислительной технике и может быть использовано как самостоятельное устройство цифровой обработки сигналов, так и ,. ля создания мультимикропроцессорных , систем (МТГС).

Цель изобретения - расширение обасти применения и функциональных озможностей за счет организации в д ультимикропроцессорные системы на основе конвейерных, дистрибутивных, ассоциативных и универсальных структур с возможностью работы в режимах обработки данных типа сортировки, yno-j5

ядочивания, группировки, прореживаия.

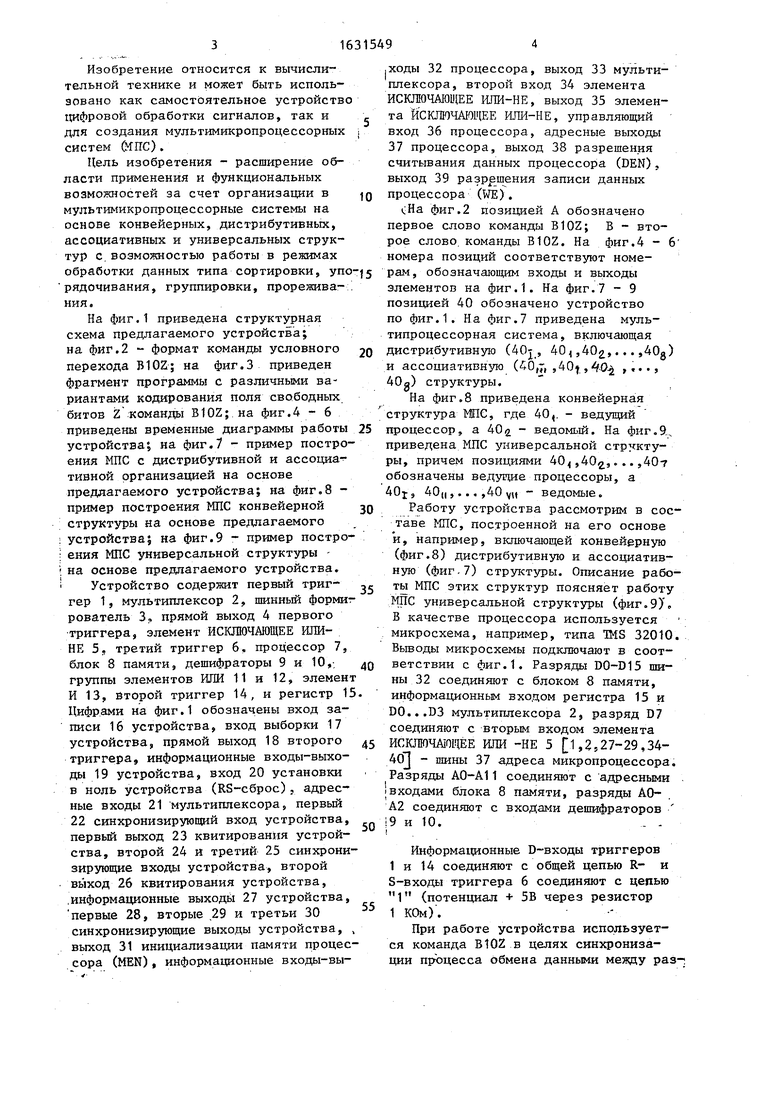

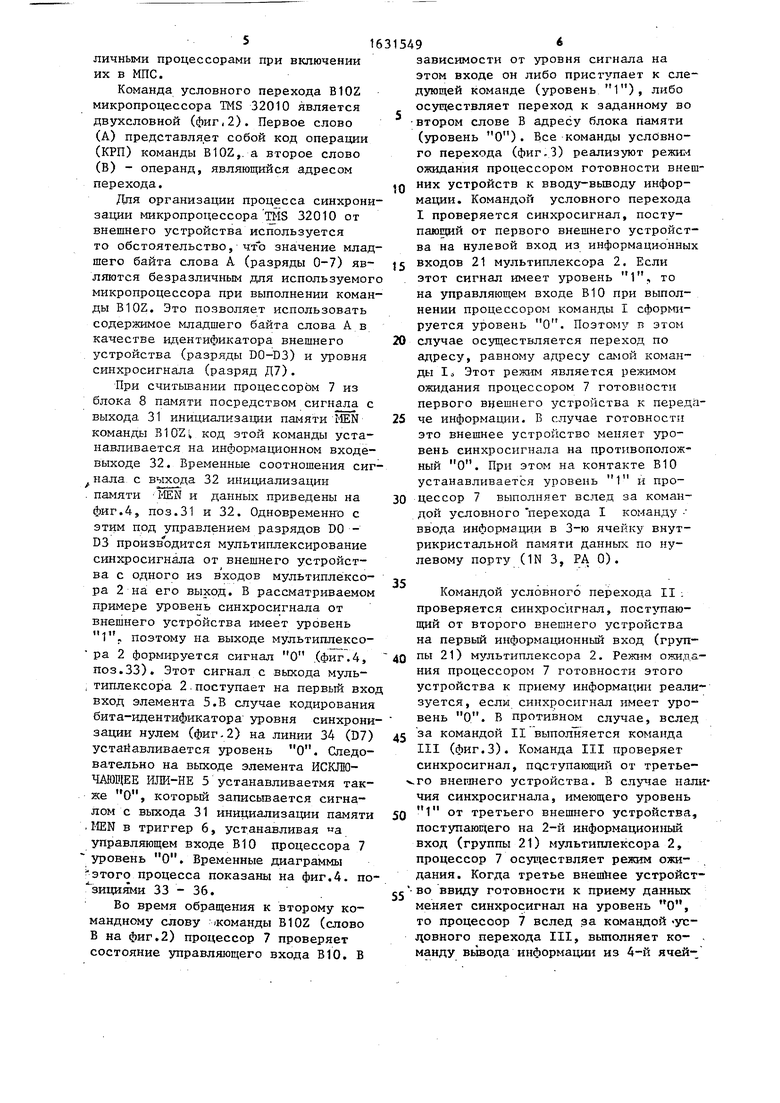

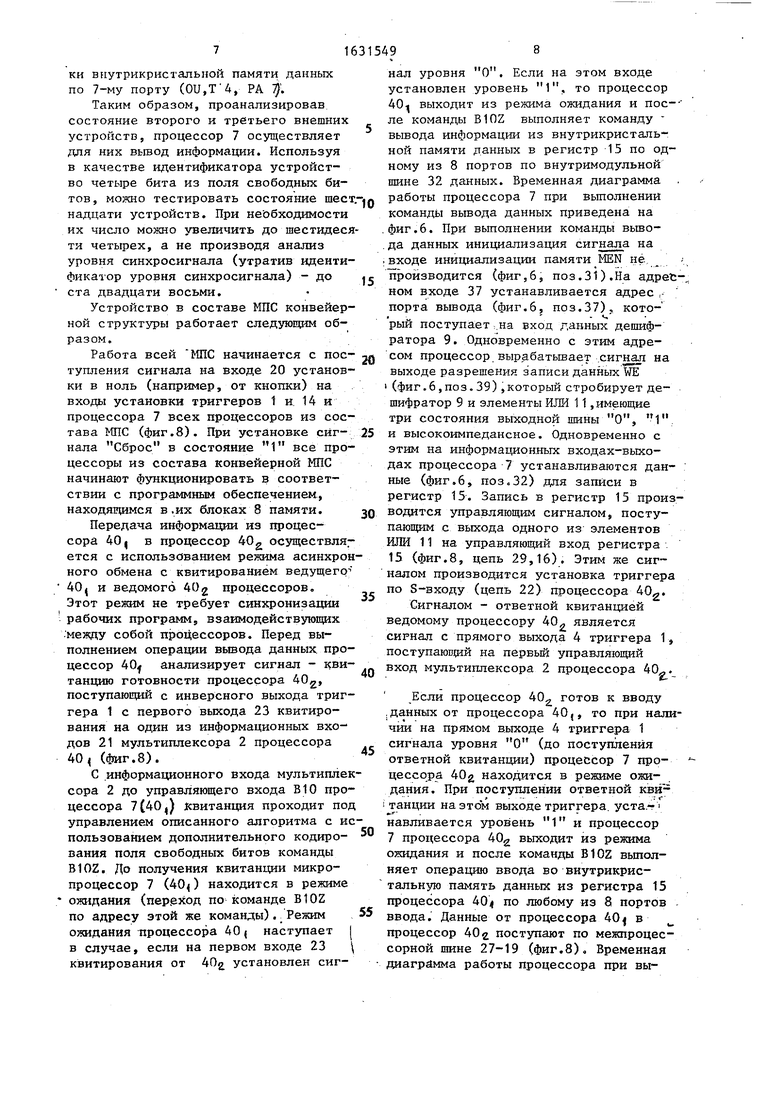

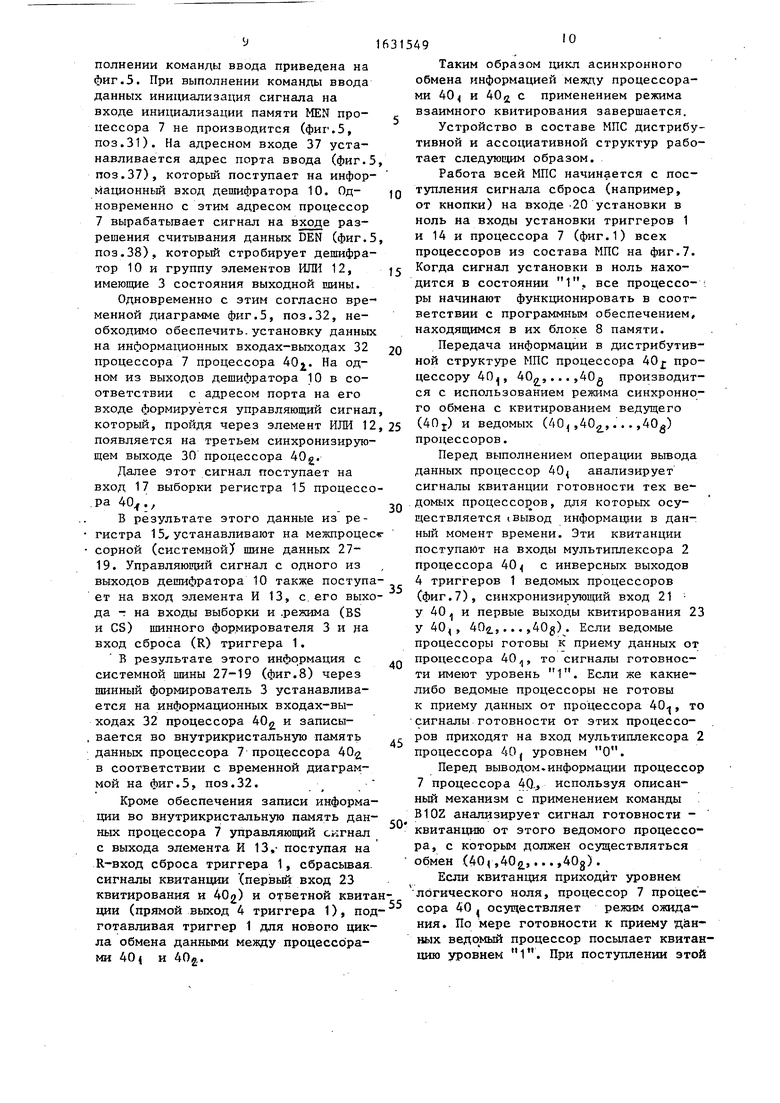

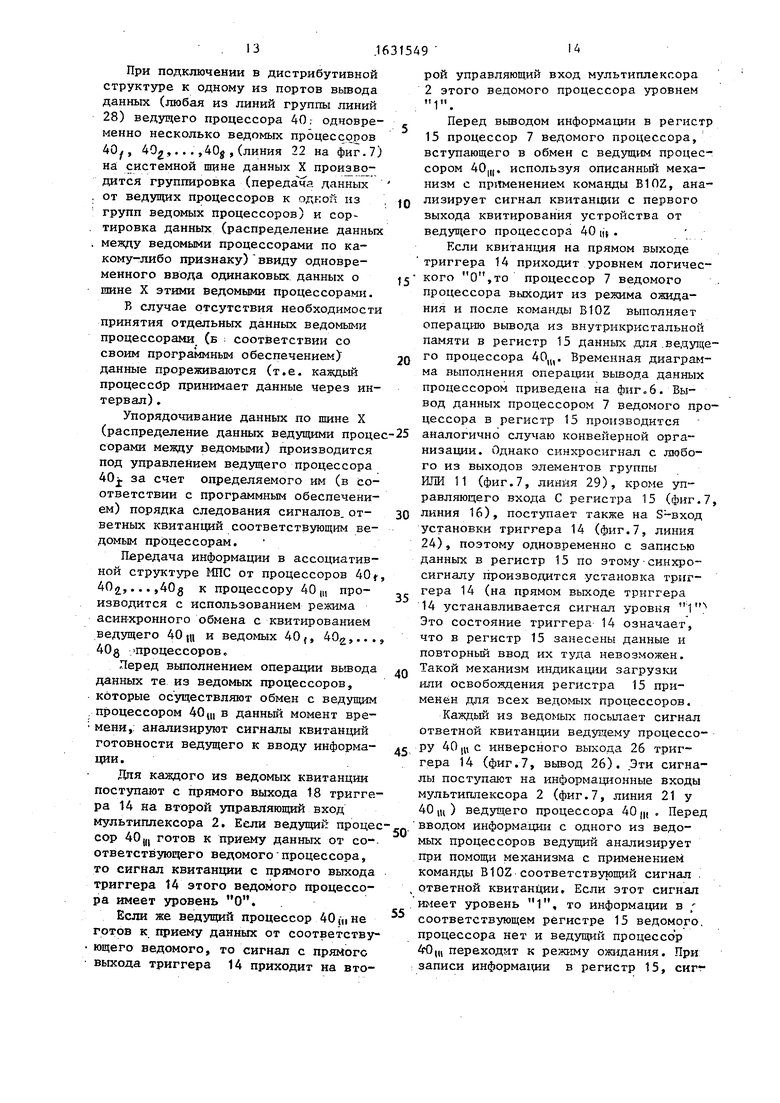

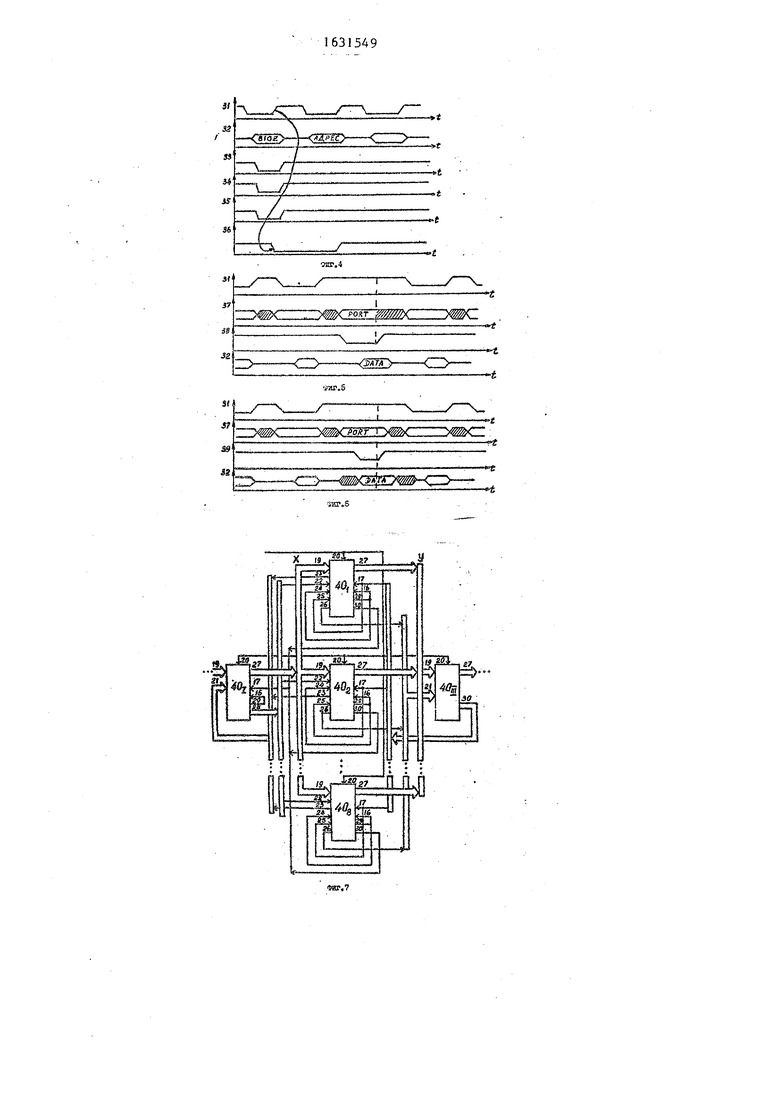

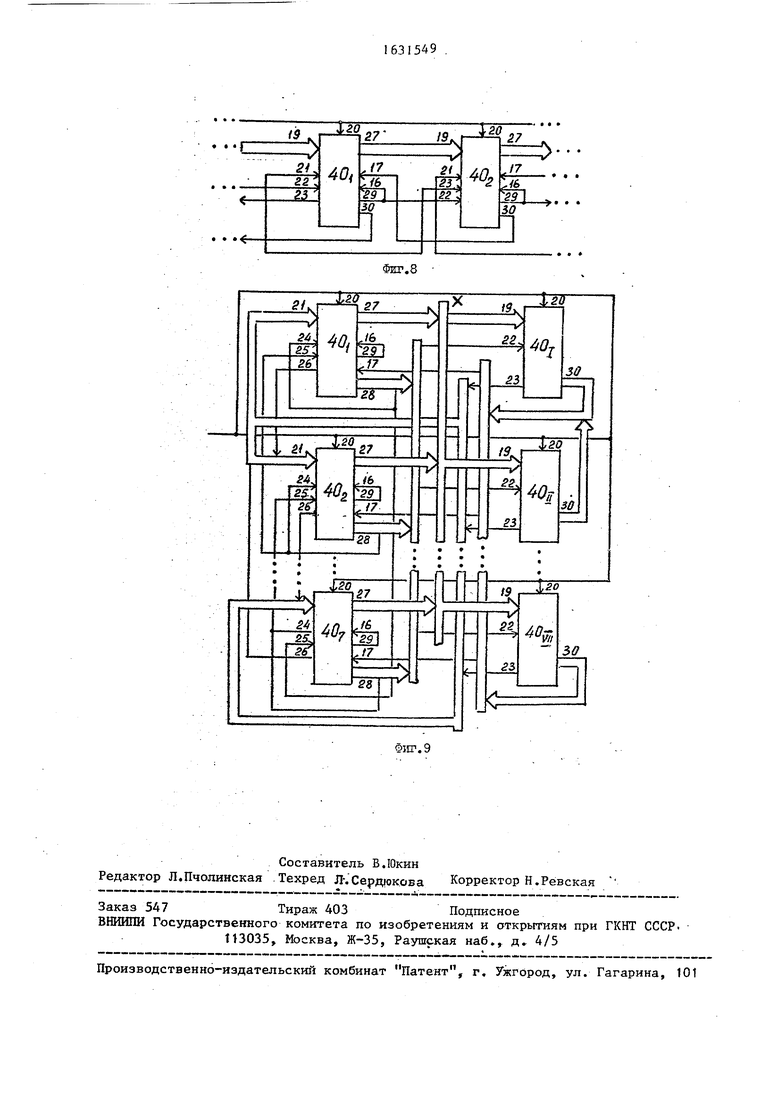

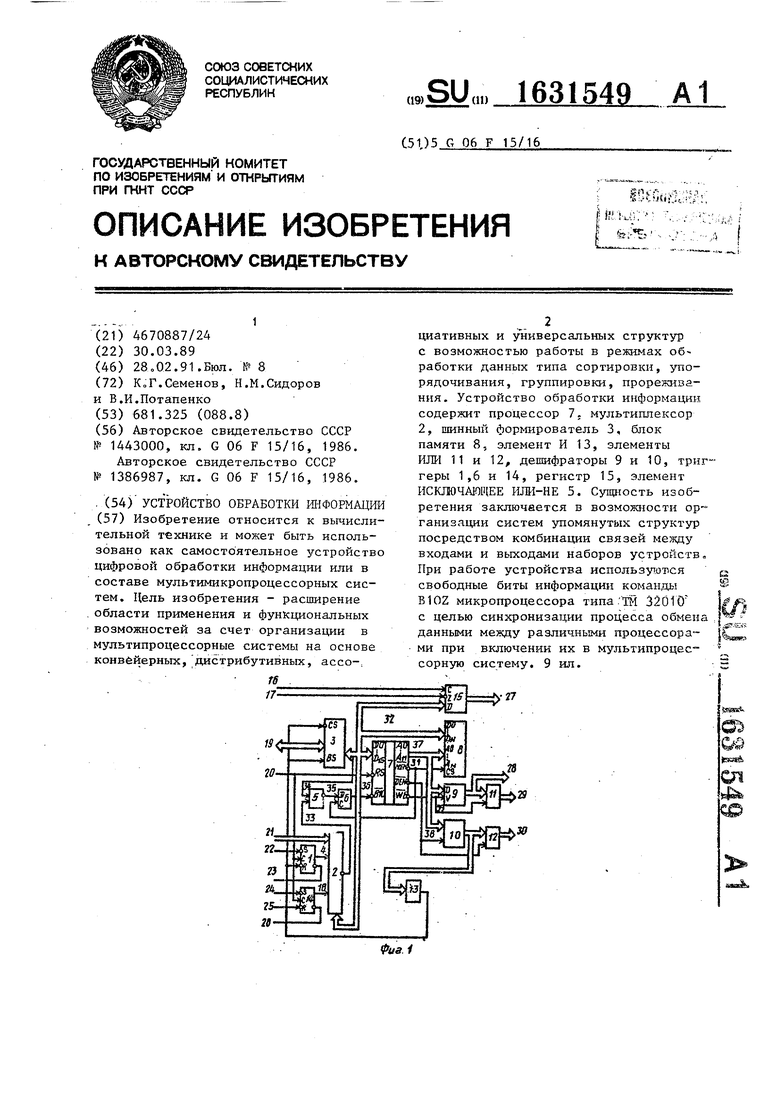

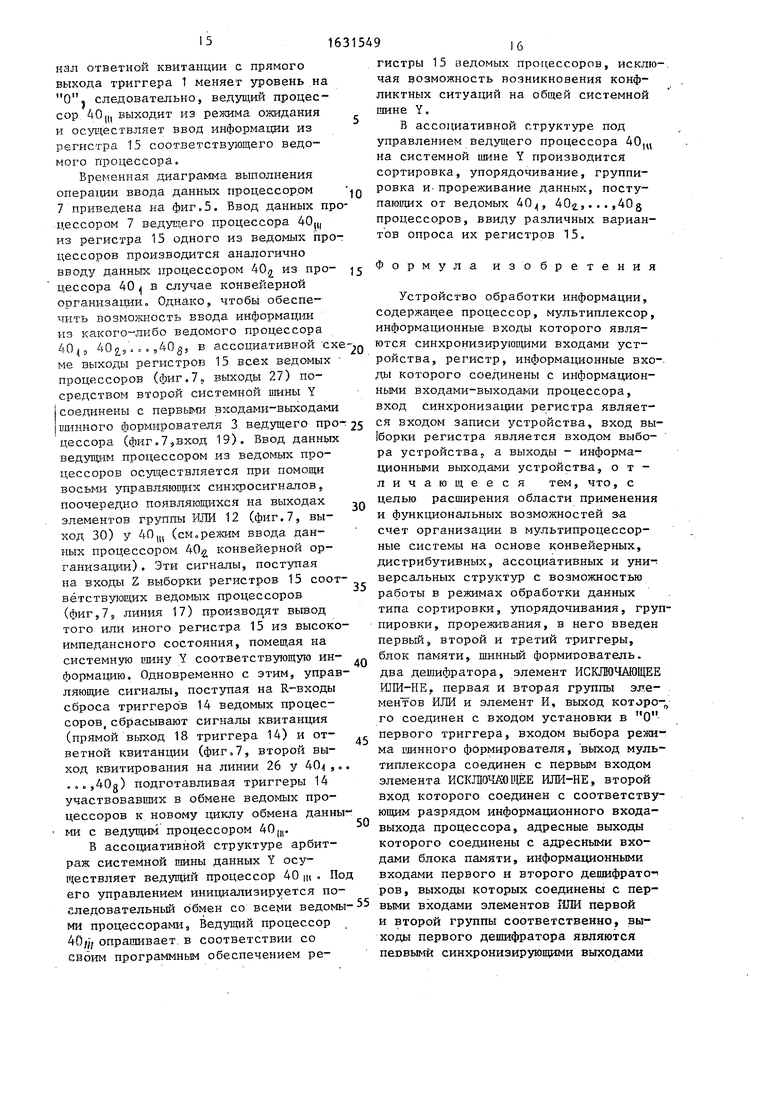

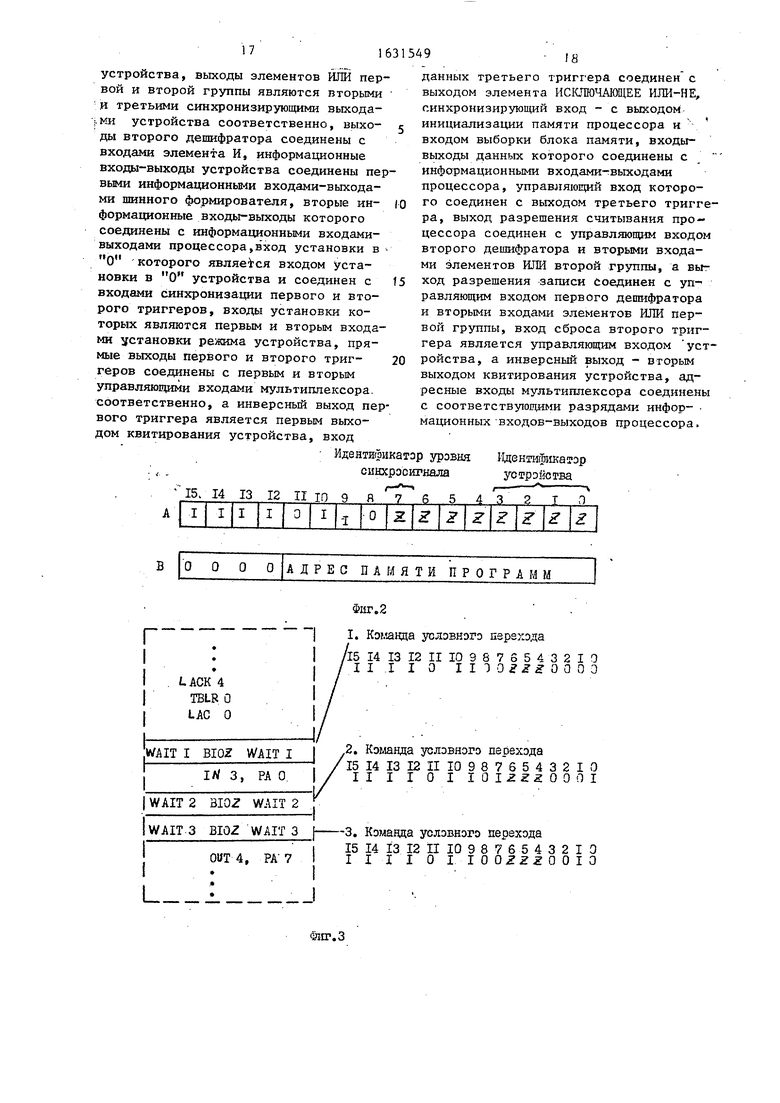

На фиг.1 приведена структурная схема предлагаемого устройств ; на фиг.2 - формат команды условного 20 перехода B10Z; на фиг.З приведен фрагмент программы с различными вариантами кодирования поля свободных битов Z команды B10Z; на фиг.4 - 6 приведены временные диаграммы работы 25 устройства; на фиг.7 - пример построения МПС с дистрибутивной и ассоциативной организацией на основе предлагаемого устройстваj на фиг.8 - пример построения МПС конвейерной JQ структуры на основе предлагаемого устройства; на фиг.9 - пример построения МПС универсальной структуры на основе предлагаемого устройства.

Устройство содержит первый триг- 35 гер 1, мультиплексор 2, шинный формирователь 3, прямой выход 4 первого триггера, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ- НЕ 5, третий триггер 6, процессор 7, блок 8 памяти, дешифраторы 9 и 10, 40 группы элементов ИЛИ 11 и 12, элемент И 13, второй триггер 14, и регистр 15. Цифрами на фиг.1 обозначены вход записи 16 устройства, вход выборки 17 устройства, прямой выход 18 второго 45 триггера, информационные входы-выходы 19 устройства, вход 20 установки в ноль устройства (RS-сброс), адресные входы 21 мультиплексора, первый 22 синхронизирующий вход устройства, первый выход 23 квитирования устройства, второй 24 и третий 25 синхронизирующие входы устройства, второй выход 26 квитирования устройства, .информационные выходы 27 устройства, первые 28, вторые ,29 и третьи 30 синхронизирующие выходы устройства, , выход 31 инициализации памяти процессора (MEN), информационные входы-вы55

.

Q

5 0 5

5

,ходы 32 процессора, выход 33 мультиплексора, второй вход 34 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, выход 35 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, управляющий вход 36 процессора, адресные выходы 37 процессора, выход 38 разрешения считывания данных процессора (DEN), выход 39 разрешения записи данных процессора (WE).

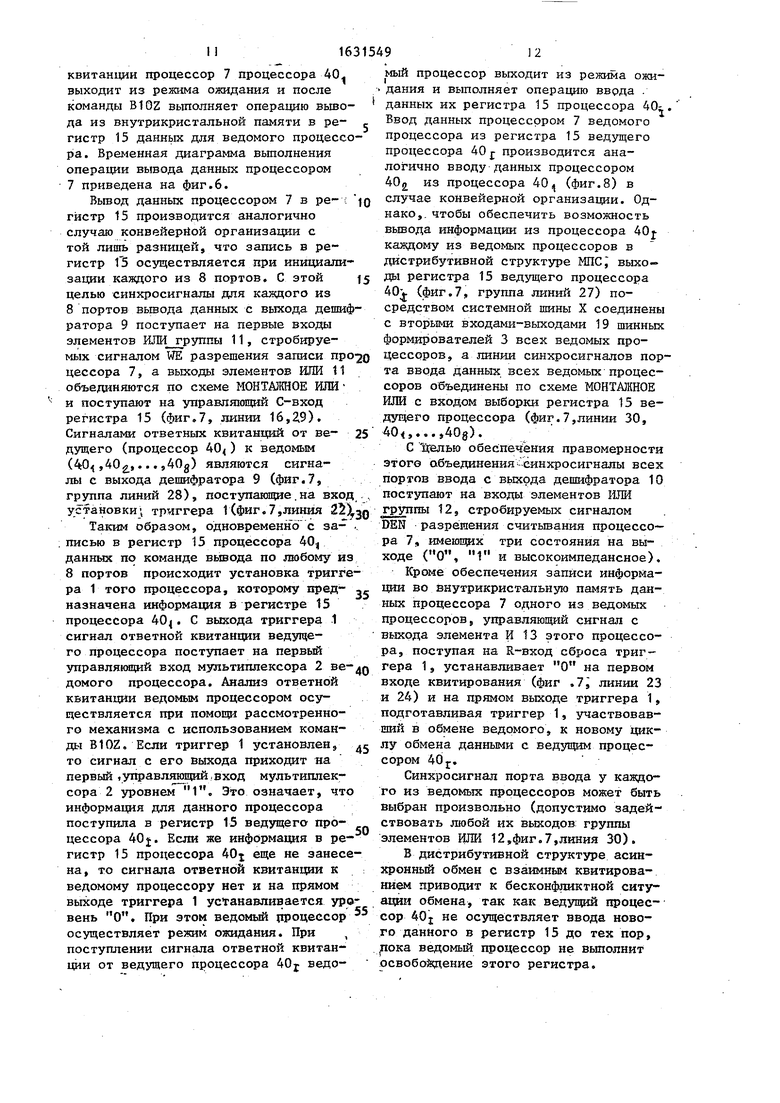

фиг.2 позицией А обозначено первое слово команды B10Z; В - второе слово команды B10Z. На фиг.4 - 6 номера позиций соответствуют номерам, обозначающим входы и выходы элементов на фиг.1. На фиг.7 - 9 позицией 40 обозначено устройство по фиг.1. На фиг.7 приведена мультипроцессорная система, включающая дистрибутивную (40j, 40,40,...,408) и ассоциативную (40,7, ,40j , 40 , « 40о) структуры.

На фиг.8 приведена конвейерная структура МПС, где 40,. - ведущий процессор, а 402 - ведомый. На фиг.9, приведена МПС универсальной структуры, причем позициями 40 ч,40г,...,40 обозначены ведущие процессоры, а 40j, 40((,.., ,40 vlt - ведомые.

Работу устройства рассмотрим в сос- таве МПС, построенной на его основе и, например, включающей конвейерную (фиг.8) дистрибутивную и ассоциативную (фиг.7) структуры. Описание работы МПС этих структур поясняет работу МПС универсальной структуры (фиг.9), В качестве процессора используется микросхема, например, типа MS 32010. Выводы микросхемы подключают в соответствии с фиг.1. Разряды DO-D15 шины 32 соединяют с блоком 8 памяти, информационным входом регистра 15 и DO...D3 мультиплексора 2, разряд D7 соединяют с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ -НЕ 5 1,2,27-29.34- 40J - шины 37 адреса микропроцессора, |Разряды АО-А11 соединяют с адресными jвходами блока 8 памяти, разряды АО- А2 соединяют с входами дешифраторов 9 и 10.

Информационные D-входы триггеров 1 и 14 соединяют с общей цепью R- и S-входы триггера 6 соединяют с цепью 1 (потенциал + 5В через резистор 1 КОм).

При работе устройства используется команда B10Z в целях синхронизации процесса обмена данными между различными процессорами при включении их в МПС.

Команда условного перехода B10Z микропроцессора TMS 32010 является двухсловной (фиг,2). Первое слово

(A)представляет собой код операции (КРП) команды B10Z, а второе слово

(B)- операнд, являющийся адресом перехода.

Для организации процесса синхронизации микропроцессора TMS 32010 от внешнего устройства используется то обстоятельство, что значение младшего байта слова А (разряды 0-7) являются безразличным для используемого микропроцессора при выполнении команды B10Z. Это позволяет использовать содержимое младшего байта слова А в качестве идентификатора внешнего устройства (разряды DO-D3) и уровня синхросигнала (разряд Д7).

При считывании процессором 7 из блока 8 памяти посредством сигнала с выхода 31 инициализации памяти MEN команды В , код этой команды устанавливается на информационном входе- выходе 32. Временные соотношения сигнала с выхода 32 инициализации памяти MEN и данных приведены на фиг.4, поз.31 и 32. Одновременно с этим под управлением разрядов DO - D3 производится мультиплексирование синхросигнала от внешнего устройства с одного из входов мультиплексора 2 на его выход. В рассматриваемом примере уровень синхросигнала от внешнего устройства имеет уровень Ч, поэтому па выходе мультиплексора 2 формируется сигнал 0м (фиг.4, поз.33). Этот сигнал с выхода мультиплексора 2 поступает на первый вход вход элемента 5.В случае кодирования бита-идентификатора уровня синхронизации нулем (фиг.2) на линии 34 (D7) устанавливается уровень О. Следовательно на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 5 устанавливаетмя также О, который записывается сигналом с выхода 31 инициализации памяти

HEN в триггер 6, устанавливая «а управляющем входе В10 процессора 7 уровень О. Временные диаграммы

этого процесса показаны на фиг.4. позициями 33 - 36.

Во время обращения к второму командному слову команды B10Z (слово В на фиг.2) процессор 7 проверяет состояние управляющего входа В10. В

5

0

5

0

5

0

5

0

5

зависимости от уровня сигнала на этом входе он либо приступает к следующей команде (уровень 1), либо осуществляет переход к заданному во втором слове В адресу блока памяти (уровень О). Все команды условного перехода (фиг,3) реализуют режим ожидания процессором готовности внешних устройств к вводу-выводу информации. Командой условного перехода I проверяется синхросигнал, поступающий от первого внешнего устройства на нулевой вход из информационных входов 21 мультиплексора 2. Если этот сигнал имеет уровень 1, то на управляющем входе В10 при выполнении процессором команды I сформируется уровень О. Поэтому в этом случае осуществляется переход по адресу, равному адресу самой команды I Этот режим является режимом ожидания процессором 7 готовности первого внешнего устройства к передаче информации. В случае готовности это внешнее устройство меняет уровень синхросигнала на противоположный О. При этом на контакте В10 устанавливается уровень 1 и процессор 7 выполняет вслед за командой условного перехода I команду ввода информации в 3-ю ячейку внутрикристальной памяти данных по нулевому порту (1N 3, РА 0).

Командой условного перехода II . проверяется синхросигнал, поступающий от второго внешнего устройства на первый информационный вход (группы 21) мультиплексора 2. Режим ожидания процессором 7 готовности этого устройства к приему информации реали- зуется, если синхросигнал имеет уровень О. В противном случае, вслед за командой II выполняется команда III (фиг.З). Команда III проверяет синхросигнал, наступающий от третье- .го внешнего устройства. В случае наличия синхросигнала, имеющего уровень 1 от третьего внешнего устройства, поступающего на 2-й информационный вход (группы 21) мультиплексора 2, процессор 7 осуществляет режим ожидания. Когда третье внешнее устройство ввиду готовности к приему данных меняет синхросигнал на уровень О, то процессор 7 вслед за командой «ус- довного перехода III, выполняет команду вывода информации из 4-й ячейки внутрикристальной памяти данных по 7-му порту (OU,T 4, РА 7}.

Таким образом, проанализировав состояние второго и третьего внешних устройств, процессор 7 осуществляет для них вывод информации. Используя в качестве идентификатора устройство четыре бита из поля свободных битов, можно тестировать состояние шестл надцати устройств. При необходимости их число можно увеличить до шестидесяти четырех, а не производя анализ уровня синхросигнала (утратив идентификатор уровня синхросигнала) - до ста двадцати восьми.

Устройство в составе МПС конвейерной структуры работает следующим образом.

Работа всей МПС начинается с поступления сигнала на входе 20 установки в ноль (например, от кнопки) на входы установки триггеров 1 и 14 и процессора 7 всех процессоров из состава МПС (фиг.8). При установке сигнала Сброс в состояние 1 все процессоры из состава конвейерной МПС начинают функционировать в соответствии с программным обеспечением, находящимся в,их блоках 8 памяти.

Передача информации из процессора 40| в процессор 40 г осуществляется с использованием режима асинхронного обмена с квитированием ведущего1

40 и ведомого 40g процессоров. Этот режим не требует синхронизации рабочих программ, взаимодействующих между собой процессоров. Перед выполнением операции вывода данных процессор 40f анализирует сигнал - квитанцию готовности процессора 40g, поступающий с инверсного выхода триггера 1 с первого выхода 23 квитирования на один из информационных входов 21 мультиплексора 2 процессора

40 ( (фиг.8).

С информационного входа мультиплексора 2 до управляющего входа В10 процессора 7(404) Квитанция проходит под управлением описанного алгоритма с использованием дополнительного кодирования поля свободных битов команды B10Z. До получения квитанции микропроцессор 7 (40) находится в режиме

ожидания (переход по команде B10Z по адресу этой же команды). Режим ожидания процессора 40 наступает | в случае, если на первом входе 23 квитирования от 40 установлен сиг 1

0

5

0

5

0

5

0

5

0

5

этом входе то процессор

нал уровня О. Если на установлен уровень 1, 40-. выходит из режима ожидания и пос-- ле команды B10Z выполняет команду - вывода информации из внутрикристальной памяти данных в регистр 15 по одному из 8 портов по внутримодульной шине 32 данных. Временная диаграмма работы процессора 7 при выполнений команды вывода данных приведена на фиг.6. При выполнении команды вывода данных инициализация сигнала на входе инициализации памяти MEN не производится (фиг,6, поз.31).На адрес-, ном входе 37 устанавливается адрес порта вывода (фиг.6, поз.37), который поступает на вход данных дешифратора 9. Одновременно с этим адресом процессор вырабатывает сигнал на выходе разрешения записи данных WE 1 (фиг.6,поз.39),который стробирует дешифратор 9 и элементы ИЛИ 11,имеющие три состояния выходной шины О, 1 и высокоимпедансное. Одновременно с этим на информационных входах-выходах процессора 7 устанавливаются данные (фиг.6, поз.32) для записи в регистр 15. Запись в регистр 15 производится управляющим сигналом, поступающим с выхода одного из элементов ИЛИ 11 на управляющий вход регистра 15 (фиг.8, цепь 29,16). Этим же сигналом производится установка триггера по S-входу (цепь 22) процессора 402.

Сигналом - ответной квитанцией ведомому процессору 40 является сигнал с прямого выхода 4 триггера 1, поступающий на первый управляющий вход мультиплексора 2 процессора 40

Если процессор 40 данных от процессора 40

. - готов к вводу

I, то при наличии на прямом выходе 4 триггера 1 сигнала уровня О (до поступления ответной квитанции) процессор 7 процессора 40g находится в режиме ожидания. При поступлении ответной квй- танции на этом выходе триггера уста- навливается уровень 1 и процессор 7 процессора 402 выходит из режима ожидания и после команды B10Z выполняет операцию ввода во внутрикристальную память данных из регистра 15 процессора 40 по любому из 8 портов ввода. Данные от процессора 40j в процессор 40Ј поступают по межпроцессорной шине 27-19 (фиг.8). Временная диаграмма работы процессора при выполнении команлы ввода приведена на фиг.5. При выполнении команды ввода данных инициализация сигнала на входе инициализации памяти MEN процессора 7 не производится (фиг.5, поз.31). На адресном входе 37 устанавливается адрес порта ввода (фиг.5, поз.37), который поступает на информационный вход дешифратора 10. Одновременно с этим адресом процессор 7 вырабатывает сигнал на входе разрешения считывания данных DEN (фиг.5, поз.38), который стробирует дешифратор 10 и группу элементов ИЛИ 12, имеющие 3 состояния выходной шины.

Одновременно с этим согласно временной диаграмме фиг.5, поз.32, необходимо обеспечить.установку данных на информационных входах-выходах 32 процессора 7 процессора 40. На одном из выходов дешифратора 10 в соответствии с адресом порта на его входе формируется управляющий сигнал,

10

Таким образом цикл асинхронного обмена информацией между процессор ми 404 и 40 д с применением режима взаимного квитирования завершается

Устройство в составе МПС дистри тивной и ассоциативной структур ра тает следующим образом.

Работа всей МПС начинается с по тупления сигнала сброса (например от кнопки) на входе -20 установки в ноль на входы установки триггеров и 14 и процессора 7 (фиг.1) всех процессоров из состава МПС на фиг Когда сигнал установки в ноль нахо дится в состоянии 1. все процесс ры начинают функционировать в соо ветствии с программным обеспечение находящимся в их блоке 8 памяти.

Передача информации в дистрибут ной структуре МПС процессора 40Ј п цессору 40, 40,...,40g производ ся с использованием режима синхрон го обмена с квитированием ведущего

15

20

который, пройдя через элемент ИЛИ 12,25 (40 г) и ведомых (40,40,...,40g)

10

63154910

Таким образом цикл асинхронного обмена информацией между процессорами 404 и 40 д с применением режима взаимного квитирования завершается.

Устройство в составе МПС дистрибутивной и ассоциативной структур работает следующим образом.

Работа всей МПС начинается с поступления сигнала сброса (например, от кнопки) на входе -20 установки в ноль на входы установки триггеров 1 и 14 и процессора 7 (фиг.1) всех процессоров из состава МПС на фиг.7. Когда сигнал установки в ноль находится в состоянии 1. все процессоры начинают функционировать в соответствии с программным обеспечением, находящимся в их блоке 8 памяти.

Передача информации в дистрибутивной структуре МПС процессора 40Ј процессору 40, 40,...,40g производится с использованием режима синхронного обмена с квитированием ведущего

15

20

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1501077A1 |

| Устройство индикации состояния ЭВМ | 1989 |

|

SU1667067A1 |

| Устройство для связи в многопроцессорной системе | 1985 |

|

SU1259279A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1288709A1 |

| Устройство для ввода информации | 1988 |

|

SU1674142A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1357959A1 |

| Устройство для контроля микропроцессорной системы | 1989 |

|

SU1640693A1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

Изобретение относится к вычислительной технике и может быть использовано как самостоятельное устройство цифровой обработки информации или в составе мультимикропроцессорных систем. Цель изобретения - расширение области применения и функциональных возможностей за счет организации в мультипроцессорные системы на основе конвейерных, дистрибутивных, ассоТ6 17 циативных и универсальных структур с возможностью работы в режимах обработки данных типа сортировки, упорядочивания, группировки, прореживания. Устройство обработки информации содержит процессор 7. мультиплексор 2, шинный формирователь 3, блок памяти 8, элемент И 13, элементы ИЛИ 11 и 12, дешифраторы 9 и 10, триггеры 1,6 и 14, регистр 15, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 5. Сущность изобретения заключается в возможности организации систем упомянутых структур посредством комбинации связей между входами и выходами наборов устройств. При работе устройства используемся свободные биты информации команда; B10Z микропроцессора типа ГМ 32010 с целью синхронизации процесса обмена данными между различными процессорами при включении их в мультипроцессорную систему. 9 ил. в к

35

появляется на третьем синхронизирующем выходе 30 процессора 40g.

Далее этот сигнал поступает на вход 17 выборки регистра 15 процессе- Ра40./30

В результате этого данные из регистра 15, устанавливают на межпроцес - сорной (системной шине данных 27- 19. Управляющий сигнал с одного из выходов дешифратора 10 также поступает на вход элемента И 13, с его выхода - на входы выборки и .режима (BS и CS) шинного формирователя 3 и на вход сброса (R) триггера 1.

В результате этого информация с системной шины 27-19 (фиг.8) через шинный формирователь 3 устанавливается на информационных входах-выходах 32 процессора 402 и записывается во внутрикристальную память данных процессора 7 процессора 40 в соответствии с временной диаграммой на фиг.5, поз.32.

Кроме обеспечения записи информации во внутрикристальную память данных процессора 7 управляющий сигнал с выхода элемента И 13,- поступая на R-вход сброса триггера 1, сбрасывая сигналы квитанции (первый вход 23 квитирования и 40Ј) и ответной квитан40

45

50процессоров.

Перед выполнением операции вывода данных процессор 40 анализирует сигналы квитанции готовности тех ведомых процессоров, для которых осуществляется (Вывод информации в данный момент времени. Эти квитанции поступают на входы мультиплексора 2 процессора 40 с инверсных выходов 4 триггеров 1 ведомых процессоров (фиг.7), синхронизирующий вход 21 у 401 и первые выходы квитирования 23 у 40 , 40g.,... ,40g) . Если ведомые процессоры готовы к приему данных от процессора 40,,, то сигналы готовности имеют уровень 1. Если же какие- либо ведомые процессоры не готовы к приему данных от процессора 40, то сигналы готовности от этих процессоров приходят на вход мультиплексора 2 процессора 40 j уровнем О.

Перед выводом информации процессор 7 процессора 4Q используя описанный механизм с применением команды B10Z анализирует сигнал готовности - квитанцию от этого ведомого процессора, с которым должен осуществляться обмен (40,40,...,40g).

Если квитанция приходит уровнем логического ноля, процессор 7 процесции (прямой выход 4 триггера 1), под-55 сора 40 , осуществляет режим ожидания. По мере готовности к приему данных ведомый процессор посылает квитан цию уровнем 1. При поступлении этой

готавливая триггер 1 для нового цикла обмена данными между процессорами 40 ( и 40g.

5

0

0

5

0процессоров.

Перед выполнением операции вывода данных процессор 40 анализирует сигналы квитанции готовности тех ведомых процессоров, для которых осуществляется (Вывод информации в данный момент времени. Эти квитанции поступают на входы мультиплексора 2 процессора 40 с инверсных выходов 4 триггеров 1 ведомых процессоров (фиг.7), синхронизирующий вход 21 у 401 и первые выходы квитирования 23 у 40 , 40g.,... ,40g) . Если ведомые процессоры готовы к приему данных от процессора 40,,, то сигналы готовности имеют уровень 1. Если же какие- либо ведомые процессоры не готовы к приему данных от процессора 40, то сигналы готовности от этих процессоров приходят на вход мультиплексора 2 процессора 40 j уровнем О.

Перед выводом информации процессор 7 процессора 4Q используя описанный механизм с применением команды B10Z анализирует сигнал готовности - квитанцию от этого ведомого процессора, с которым должен осуществляться обмен (40,40,...,40g).

Если квитанция приходит уровнем логического ноля, процессор 7 процес5 сора 40 , осуществляет режим ожидасора 40 , осуществляет режим ожидания. По мере готовности к приему данных ведомый процессор посылает квитанцию уровнем 1. При поступлении этой

квитанции процессор 7 процессора 40 выходит из режима ожидания и после команды B10Z выполняет операцию вывода из внутрикристальной памяти в ре- с гистр 15 данных для ведомого процессора. Временная диаграмма выполнения операции вывода данных процессором

7приведена на фиг.6.

Вывод данных процессором 7 в ре- гистр 15 производится аналогично случаю конвейерной организации с той лишь разницей, что запись в регистр Г5 осуществляется при инициализации каждого из 8 портов. С этой $ целью синхросигналы для каждого из

8портов вывода данных с выхода дешифратора 9 поступает на первые входы элементов ИЛИ группы 11, стробируе- мых сигналом WE разрешения записи цессора 7, а выходы элементов ИЛИ 11 объединяются по схеме МОНТАЖНОЕ ИЛИ

и поступают на управляющий С-вход регистра 15 (фиг.7, линии 16,2.9). Сигналами ответных квитанций от ве- 25 дущего (процессор 40) к ведомым (40,40Ј,...,40g) являются сигналы с выхода дешифратора 9 (фиг.7, группа линий 28), поступающие.на вход , установки триггера 1(фиг.7,линия

Таким образом, одновременно с за- . писью в регистр 15 процессора 40 данных по команде вывода по любому из 8 портов происходит установка триггера 1 того процессора, которому пред- назначена информация в регистре 15 процессора 40|. С выхода триггера 1 сигнал ответной квитанции ведущего процессора поступает на первый управляющий вход мультиплексора 2 ве-до домого процессора. Анализ ответной квитанции ведомым процессором осуществляется при помощи рассмотренного механизма с использованием команды B10Z. Если триггер 1 установлен, 45 то сигнал с его выхода приходит на первый tуправляющий,вход мультиплексора 2 уровнем 1. Это означает, что информация для данного процессора поступила в регистр 15 ведущего процессора 40 j. Если же информация в регистр 15 процессора 40j еще не занесена, то сигнала ответной квитанции к ведомому процессору нет и на прямом выходе триггера 1 устанавливается уровень О. При этом ведомый процессор осуществляет режим ожидания. При , поступлении сигнала ответной квитанции от ведущего процессора 40j ведо50

55

,

мый процессор выходит из режима ожи- дания и выполняет операцию вврда . данных их регистра 15 процессора 40;.. Ввод данных процессором 7 ведомого процессора из регистра 15 ведущего процессора 40 Ј производится аналогично вводу данных процессором 40г из процессора 40 (фиг.8) в случае конвейерной организации. Однако, чтобы обеспечить возможность вывода информации из процессора 40Г каждому из ведомых процессоров в дистрибутивной структуре МПС выходы регистра 15 ведущего процессора 40 (фиг.7, группа линий 27) посредством системной шины X соединены с вторыми входами-выходами 19 шинных формирователей 3 всех ведомых процессоров, а линии синхросигналов порта ввода данных всех ведомых процессоров объединены по схеме МОНТАЖНОЕ ИЛИ с входом выборки регистра 15 ведущего процессора (фиг.7,линии 30, 40,...,40g).

С целью обеспечения правомерности этого объединения синхросигналы всех портов ввода с выхода дешифратора 10 поступают на входы элементов ИЛИ группы 12, стробируемых сигналом DEN разрешения считывания процессора 7 имеющих три состояния на выходе (О, 1 и высокоимпедансное).

Кроме обеспечения записи информации во внутрикристальную память данных процессора 7 одного из ведомых процессоров, управляющий сигнал с выхода элемента И 13 этого процессора, поступая на R-вход сброса триггера 1, устанавливает О на первом входе квитирования (фиг ,7, линии 23 и 24) и на прямом выходе триггера 1, подготавливая триггер 1, участвовавший в обмене ведомого, к новому циклу обмена данными с ведущим процессором 40 г.

Синхросигнал порта ввода у каждого из ведомых процессоров может быть выбран произвольно (допустимо задействовать любой их выходов группы элементов ИЛИ 12,фиг.7,линия 30).

В дистрибутивной структуре асинхронный обмен с взаимным квитированием приводит к бесконфликтной ситуации обмена, так как ведущий процессор 40j не осуществляет ввода нового данного в регистр 15 до тех пор, пока ведомый процессор не выполнит освобождение этого регистра.

При подключении в дистрибутивной структуре к одному из портов вывода данных (любая из линий группы линий 28) ведущего процессора 40,- одновре- менно несколько ведомых процессоров 40,, 40,...,40g,(линия 22 на фиг.7) на системной шине данных X производится группировка (передача данных от ведущих процессоров к одной из групп ведомых процессоров) и сортировка данных (распределение данных между ведомыми процессорами по какому-либо признаку)ввиду одновременного ввода одинаковых данных о шине X этими ведомыми процессорами.

В случае отсутствия необходимости принятия отдельных данных ведомыми процессорами, (в соответствии со своим программным обеспечением} данные прореживаются (т.е. каждый процессбр принимает данные через интервал) .

Упорядочивание данных по шине X (распределение данных ведущими проце сорами между ведомыми) производится под управлением ведущего процессора 40j. за счет определяемого им (в соответствии с программным обеспечением) порядка следования сигналов, от- ветных квитанций соответствующим ведомым процессорам.

Передача информации в ассоциативной структуре МПС от процессоров 40t , . ,.,40g к процессору 40 |м про- изводится с использованием режима асинхронного обмена с квитированием ведущего 40 щ и ведомых 40,, 402,... 40g -процессоров«

Перед выполнением операции вывода данных те из ведомых процессоров, которые осуществляют обмен с ведущим процессором 40щ в данный момент времени, анализируют сигналы квитанций готовности ведущего к вводу информа- ции.

Для каждого из ведомых квитанции поступают с прямого выхода 18 триггера 14 на второй управляющий вход мультиплексора 2. Если ведущий процесор 40ш готов к приему данных от соответствующего ведомогопроцессора, то сигнал квитанции с прямого выхода триггера 14 этого ведомого процессора имеет уровень О.

Если же ведущий процессор 40(ц не готов к приему данных от соответствующего ведомого, то сигнал с прямого выхода триггера 14 приходит на вто

0

5 0

,.

д

0

рой управляющий вход мультиплексора 2 этого ведомого процессора уровнем 1.

Перед выводом информации в регистр 15 процессор 7 ведомого процессора, вступающего в обмен с ведущим процессором 40,,,. используя описанный механизм с применением команды B10Z, анализирует сигнал квитанции с первого выхода квитирования устройства от ведущего процессора 40 щ.

Если квитанция на прямом выходе триггера 14 приходит уровнем логического О,то процессор 7 ведомого процессора выходит из режима ожидания и после команды B10Z выполняет операцию вывода из внутрикристальной памяти в регистр 15 данных для ведущего процессора 40Ш. Временная диаграмма выполнения операции вывода данных процессором приведена на фиг.6. Вывод данных процессором 7 ведомого процессора в регистр 15 производится аналогично случаю конвейерной организации. Однако синхросигнал с любого из выходов элементов группы ИЛИ 11 (фиг.7, линия 29), кроме управляющего входа С регистра 15 (фиг.7, линия 16), поступает также на S-вход установки триггера 14 (фиг.7, линия 24), поэтому одновременно с записью данных в регистр 15 по этому синхросигналу производится установка триггера 14 (на прямом выходе триггера 14 устанавливается сигнал уровня 1 Это состояние триггера 14 означает, что в регистр 15 занесены данные и повторный ввод их туда невозможен. Такой механизм индикации загрузки или освобождения регистра 15 применен для всех ведомых процессоров.

Каждый из ведомых посылает сигнал ответной квитанции ведущему процессору 40 ц, с инверсного выхода 26 триггера 14 (фиг.7, вывод 26). Эти сигналы поступают на информационные входы мультиплексора 2 (фиг.7, линия 21 у 40 щ) ведущего процессора 40 ц( . Перед вводом информации с одного из ведомых процессоров ведущий анализирует при помощи механизма с применением команды B10Z соответствующий сигнал ответной квитанции. Если этот сигнал имеет уровень 1, то информации в ; соответствующем регистре 15 ведомого, процессора нет и ведущий процессор 44),„ переходят к режиму ожидания. При записи информации в регистр 15, сигнал ответной квитанции с прямого выхода триггера 1 меняет уровень на О, следовательно, ведущий процессор 40 л, выходит из режима ожидания и осуществляет ввод информации из регистра 15 соответствующего ведомого процессора.

Временная диаграмма выполнения операции ввода данных процессором 7 приведена на фиг.5. Ввод данных процессором 7 ведущего процессора 40(„ из регистра 15 одного из ведомых процессоров производится аналогично вводу данных процессором 40 из про- цессора 40 в случае конвейерной организации. Однако, чтобы обеспечить возможность ввода информации из какого-либо ведомого процессора

40 „ 40

,40,

в ассоциативной схе

ме выходы регистров 15 всех ведомых - процессоров (фиг.7 выходы 27) посредством второй системной шины Y соединены с первыми входами-выходами шинного формирователя 3 ведущего процессора (фиг,7,вход 19). Ввод данных ведущим процессором из ведомых процессоров осуществляется при помощи восьми управляющих синхросигналов, поочередно появляющихся на выходах элементов группы ИЛИ 12 (фиг.7, выход 30) у 40 Н( (см„режим ввода данных процессором 40 конвейерной организации) . Эти сигналы, поступая на входы Z выборки регистров 15 соответствующих ведомых процессоров (фиг,7s линия 17) производят вывод того или иного регистра 15 из высоко импедансного состояния, помещая на системную шину Y соответствующую ин- формацию. Одновременно с этим, управляющие сигналы, поступая на R-входы сброса триггеров 14 ведомых процессоров, сбрасывают сигналы квитанция (прямой выход 18 триггера 14) и ответной квитанции (фиг.7, второй выход квитирования на линии 26 у 40,. ...,40g) подготавливая триггеры 14 участвовавших в обмене ведомых процессоров к новому циклу обмена данными с ведущим процессором 40(|1.

В ассоциативной структуре арбитраж системной шины данных Y осуществляет ведущий процессор 40 щ. По его управлением инициализируется последовательный обмен со всеми ведомы ми процессорами. Ведущий процессор 40//; опрашивает в соответствии со своим программным обеспечением ре

$

0

0

5

5

50

55

гистры 15 ведомых процессоров, исключая возможность возникновения конфликтных ситуаций на общей системной шине Y.

В ассоциативной структуре под управлением ведущего процессора 40Ш на системной шине Y производится сортировка, упорядочивание, группировка и- прореживание данных, поступающих от ведомых 40 ,|, 402.,...,40g процессоров, ввиду различных вариантов опроса их регистров 15.

Формула изобретения

Устройство обработки информации, содержащее процессор, мультиплексор, информационные входы которого являются синхронизирующими входами устройства, регистр, информационные входы которого соединены с информационными входами-выходами процессора, вход синхронизации регистра является входом записи устройства, вход выборки регистра является входом выбора устройства, а выходы - информационными выходами устройства, отличающее ся тем, что, с целью расширения области применения и функциональных возможностей з-а счет организации в мультипроцессорные системы на основе конвейерных, дистрибутивных, ассоциативных и универсальных структур с возможностью работы в режимах обработки данных типа сортировки, упорядочивания, группировки, прореживания, в него введен первый, второй и третий триггеры, блок памяти, шинный формирователь, два дешифратора, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, первая и вторая группы элементов ИЛИ и элемент И, выход которо-0 го соединен с входом установки в О первого триггера, входом выбора режима шинного формирователя, выход мультиплексора соединен с первым входом элемента ИСКЛЮЧЙОЩЕЕ ИЛИ-НЕ, второй вход которого соединен с соответствующим разрядом информационного входа- выхода процессора, адресные выходы которого соединены с адресными входами блока памяти, информационными входами первого и второго дешифратор ров, выходы которых соединены с первыми входами элементов ИЛИ первой и второй группы соответственно, выходы первого дешифратора являются пеовымй синхронизирующими выходами

устройства, выходы элементов ИЛИ первой и второй группы являются вторыми И третьими синхронизирующими выходами устройства соответственно, выходы второго дешифратора соединены с входами элемента И, информационные входы-выходы устройства соединены первыми информационными входами-выходами шинного формирователя, вторые информационные входы-выходы которого соединены с информационными входами- выходами процессора,вход установки в О которого является входом установки в О устройства и соединен с входами синхронизации первого и второго триггеров, входы установки которых являются первым и вторым входами установки режима устройства, прямые выходы первого и второго триггеров соединены с первым и вторым управляющими входами мультиплексора соответственно, а инверсный выход первого триггера является первым выходом квитирования устройства, вход

Г

LACK 4 TBLR О LAG О

WAIT I BIQZ WAIT I Iti 3, PA О

| WAIT 2 BI02 WAIT 2

WAIT 3 BIOZ WAIT 3

OUT 4, PA 7

данных третьего триггера соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, синхронизирующий вход - с выходом инициализации памяти процессора и входом выборки блока памяти, входы- выходы данных которого соединены с информационными входами-выходами процессора, управляющий вход котороQ го соединен с выходом третьего триггера, выход разрешения считывания процессора соединен с управляющим входом второго дешифратора и вторыми входами элементов ИЛИ второй группы, а выход разрешения записи соединен с уп- равляющим входом первого дешифратора и вторыми входами элементов ИЛИ первой группы, вход сброса второго триггера является управляющим входом уст0 ройства, а инверсный выход - вторым выходом квитирования устройства, адресные входы мультиплексора соединены с соответствующими разрядами информационных входов-выходов процессора.

Фиг.2

I. Команда условного перехода /15 14 13 12 II 10 9 8 7 6 5 4 3 2 I О

II i i о 11тог гоооэ

15 14 13 12 II 10 9 8 7 6 5 4 3 2 I О II I I 0 I

-3. Команда условного перехода 15 14 13 12 II 10 9 8 7 6 5 4 3 2 I О IIIIOIIOQ2ZZ0010

и

Oa«jLUtM

fva«a SЈ

S 5Ј a

X

ы

1 Ul

J

4D

rT3

я. п. ч «

«. t

« r

| Ячейка однородной вычислительной среды | 1986 |

|

SU1443000A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1386987A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-02-28—Публикация

1989-03-30—Подача