Изобретение относится к вычислительной технике и может быть использовано в качестве управляющей подсистемы в системах контроля и управления сбором и обработкой информации.

Цель изобретения - повышение быстродействия системы.

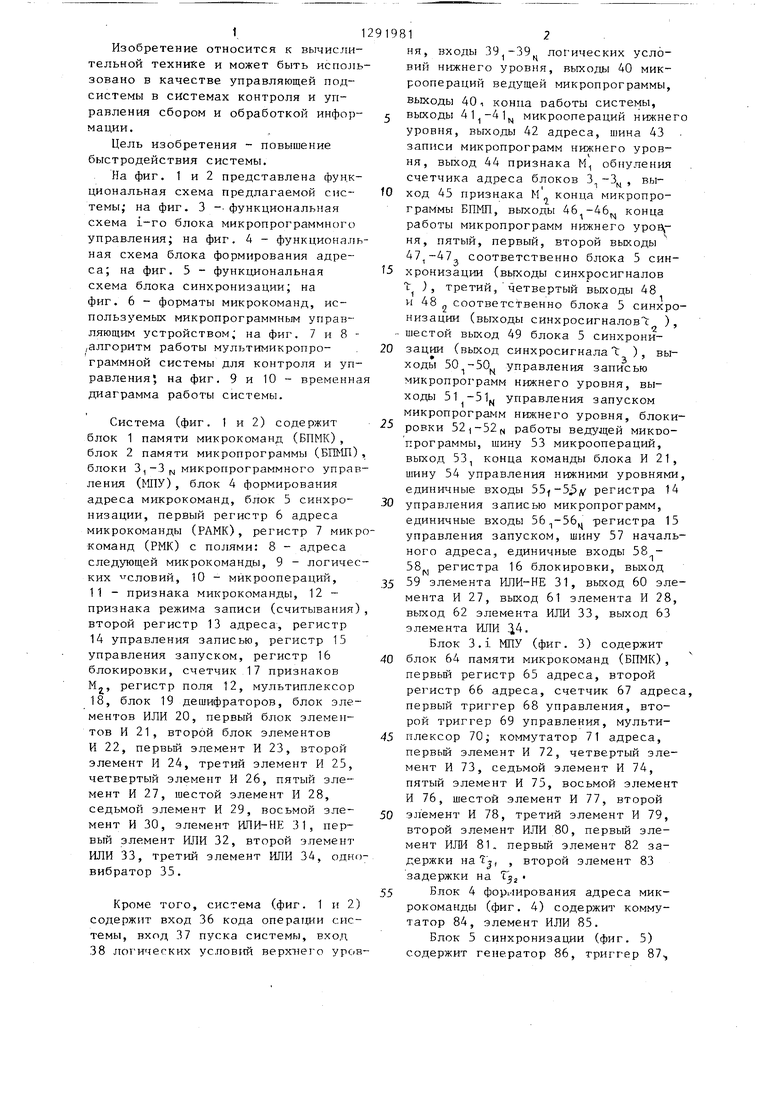

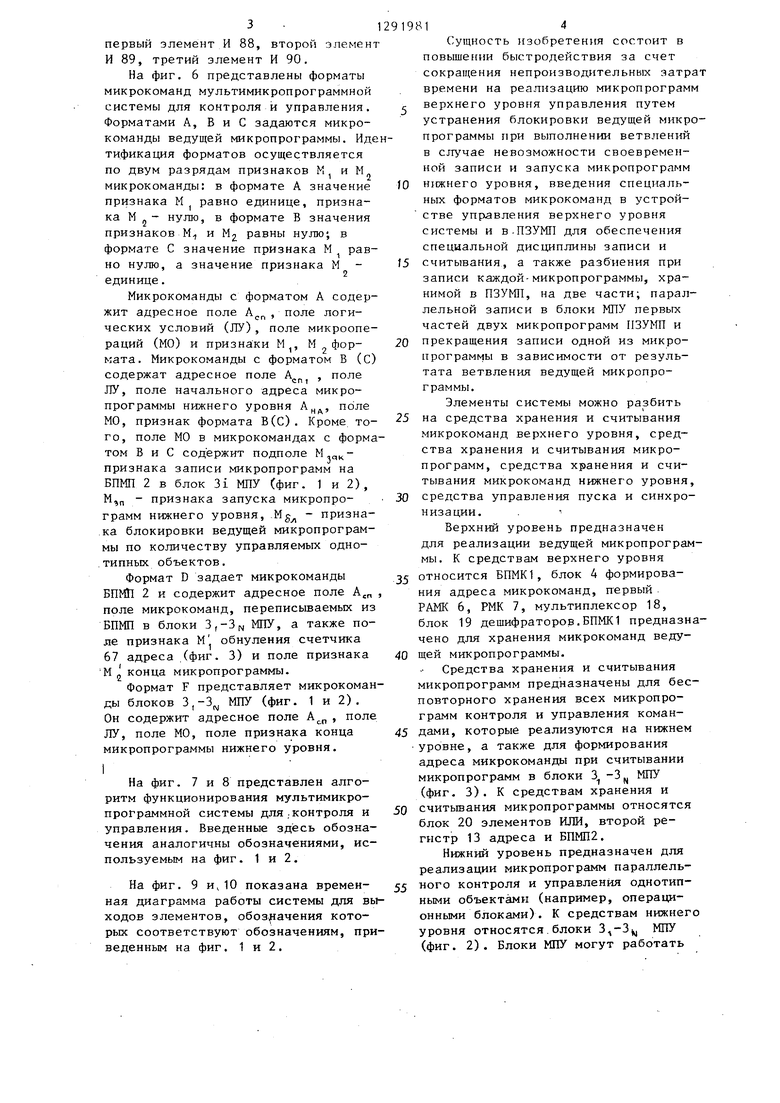

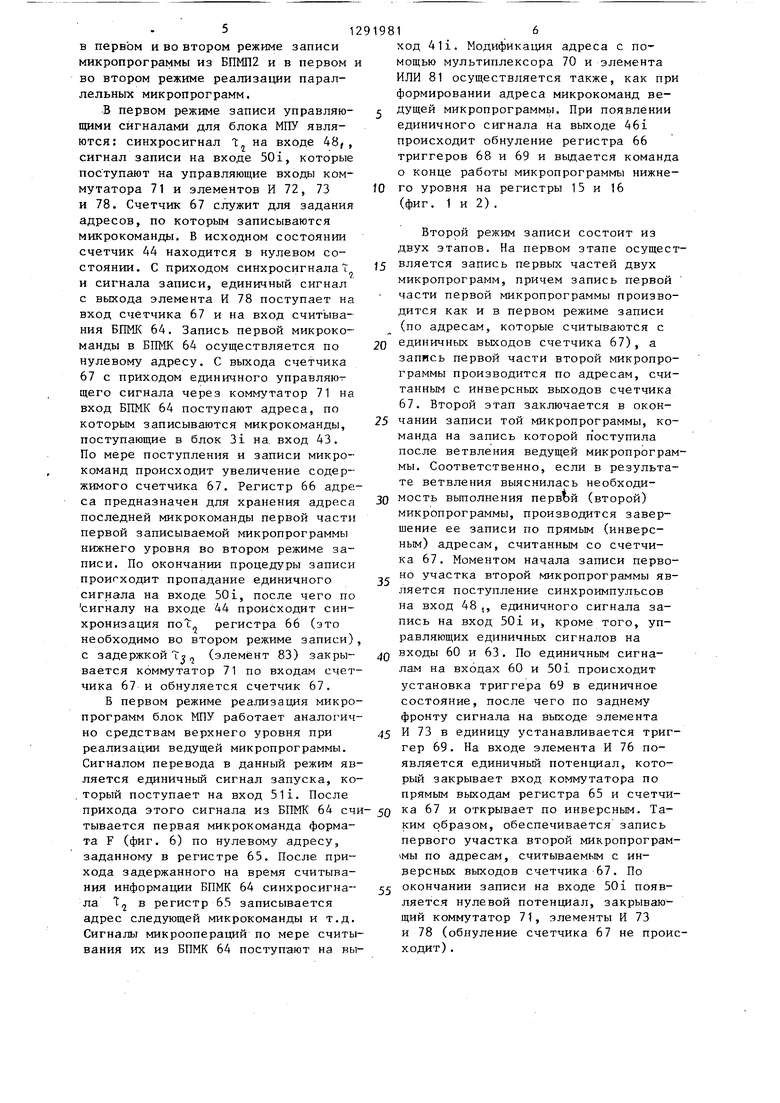

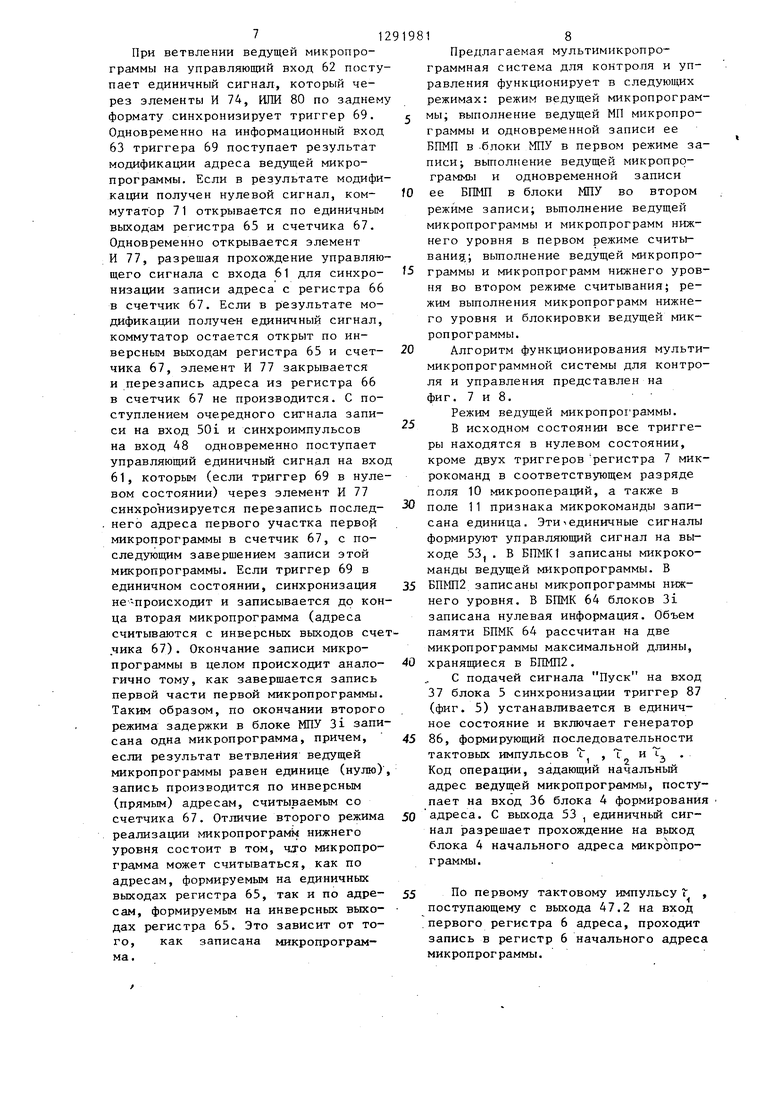

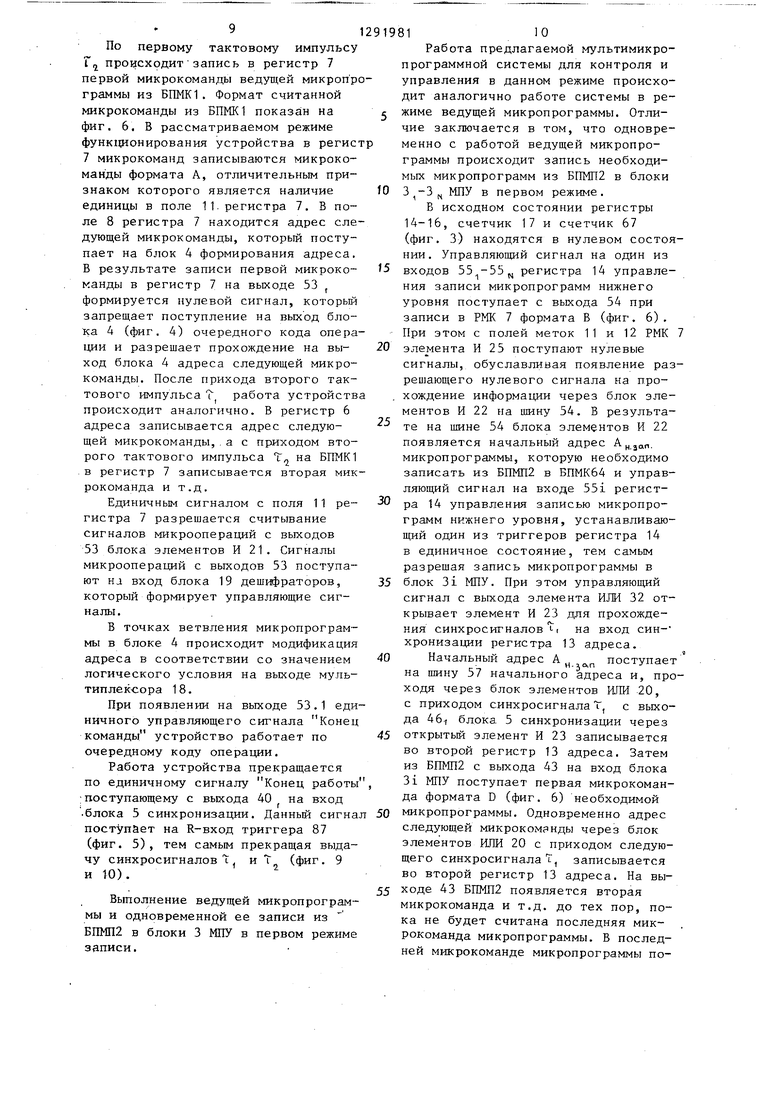

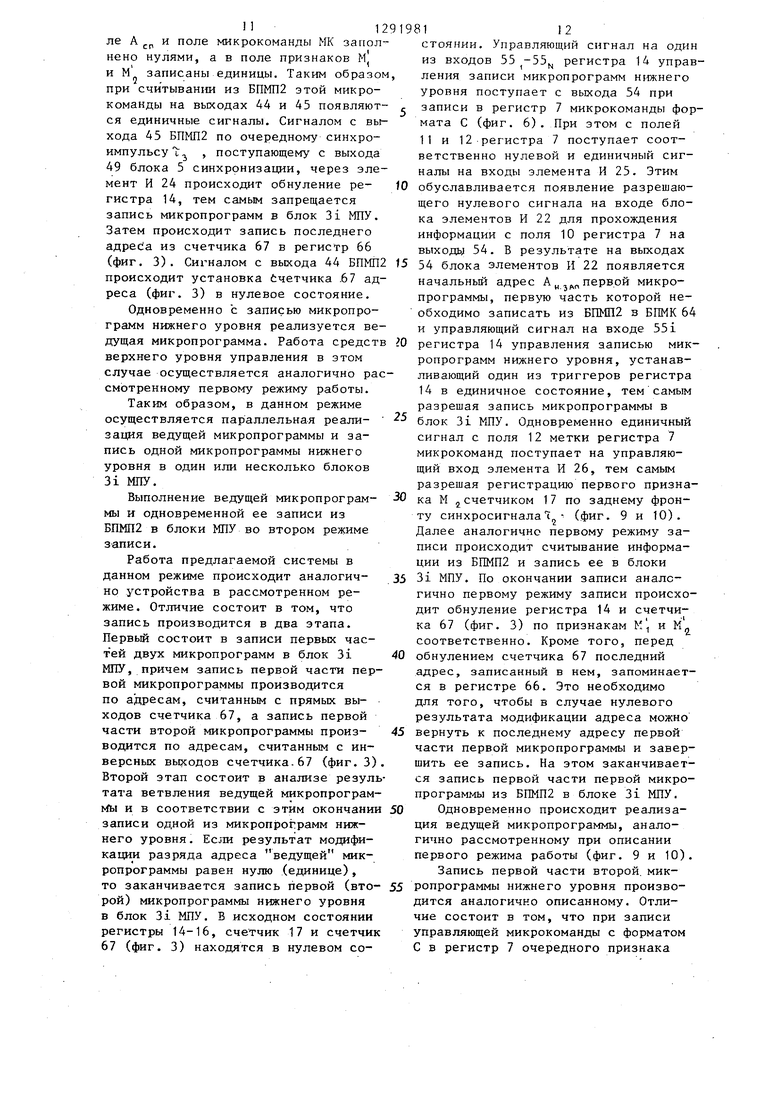

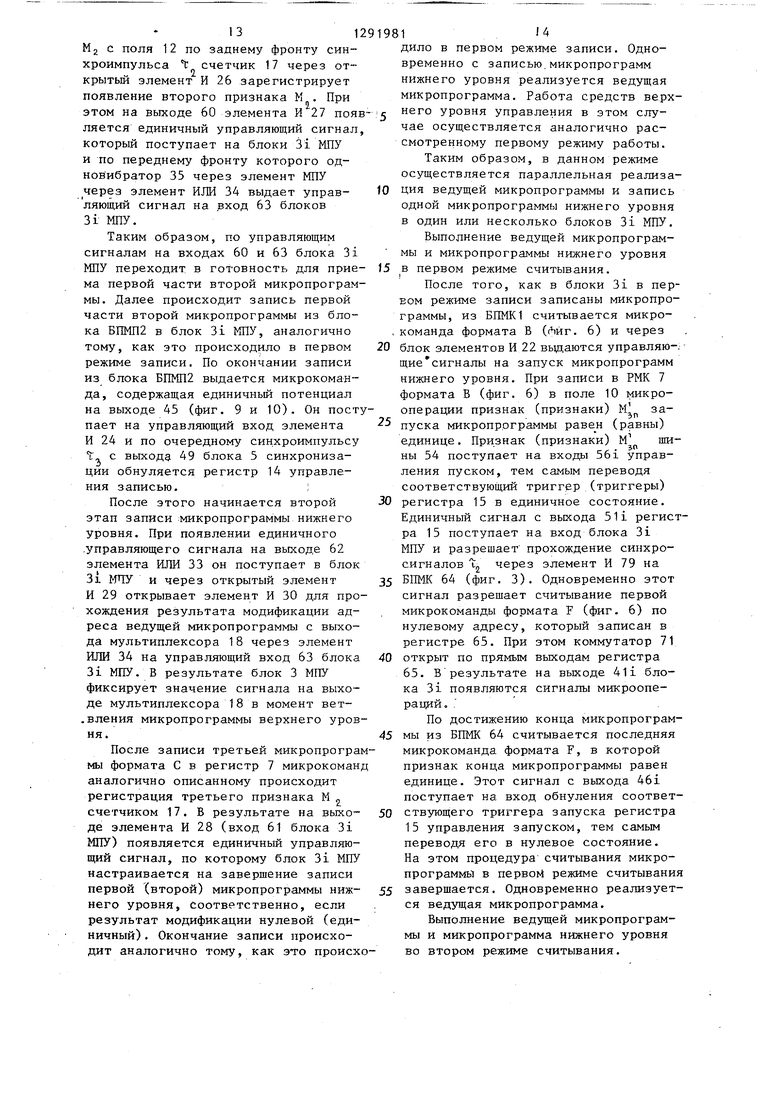

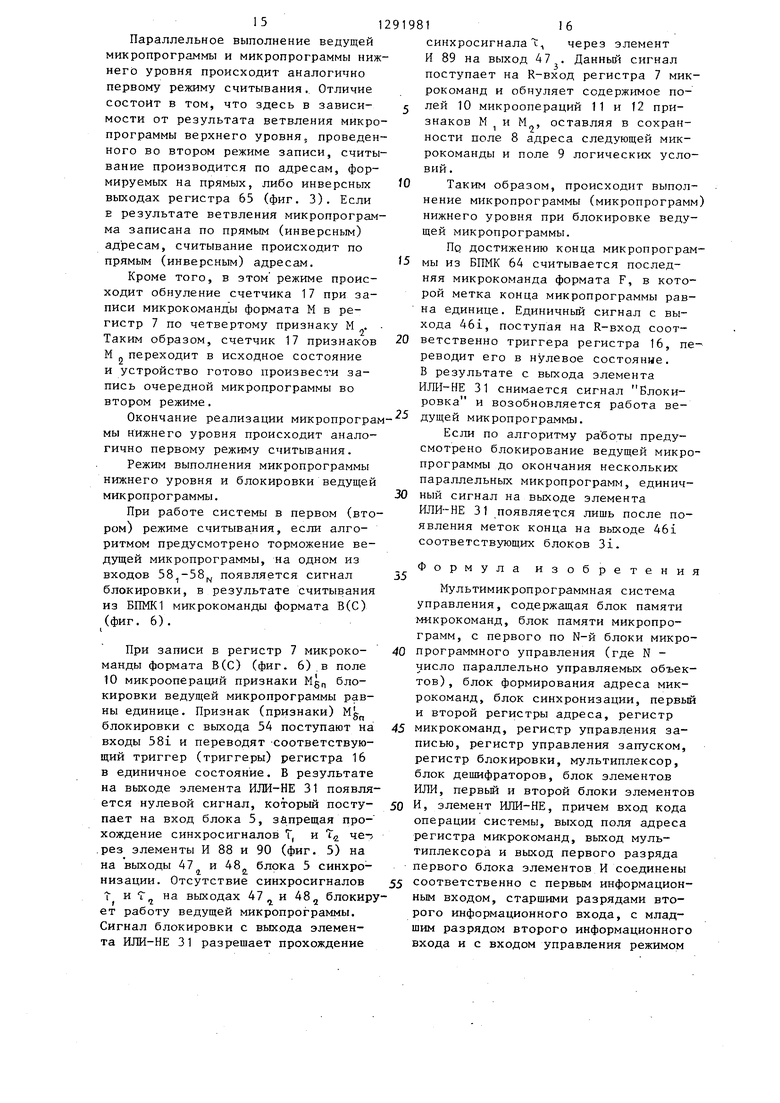

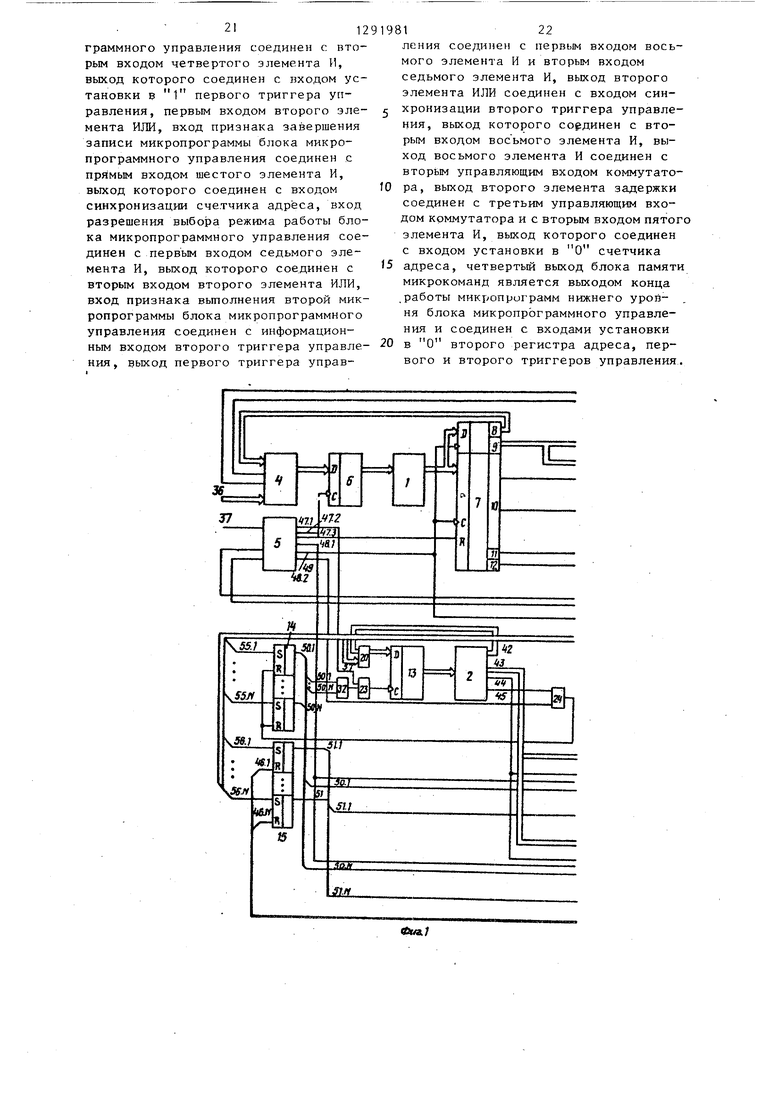

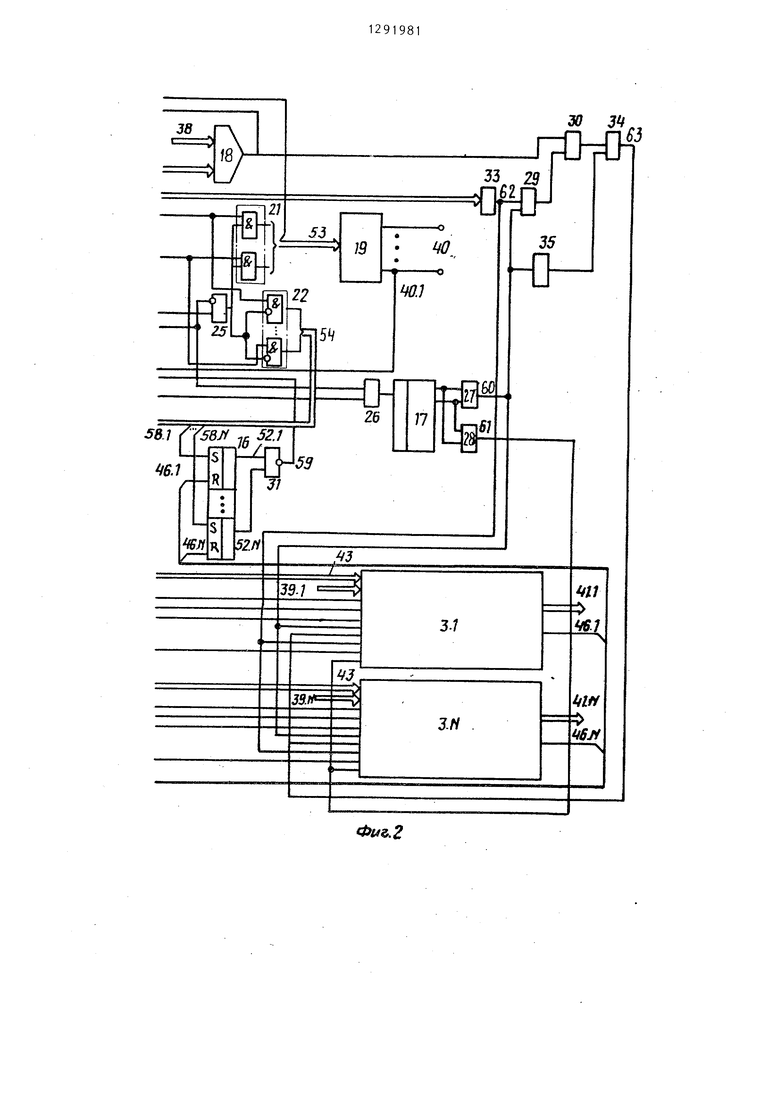

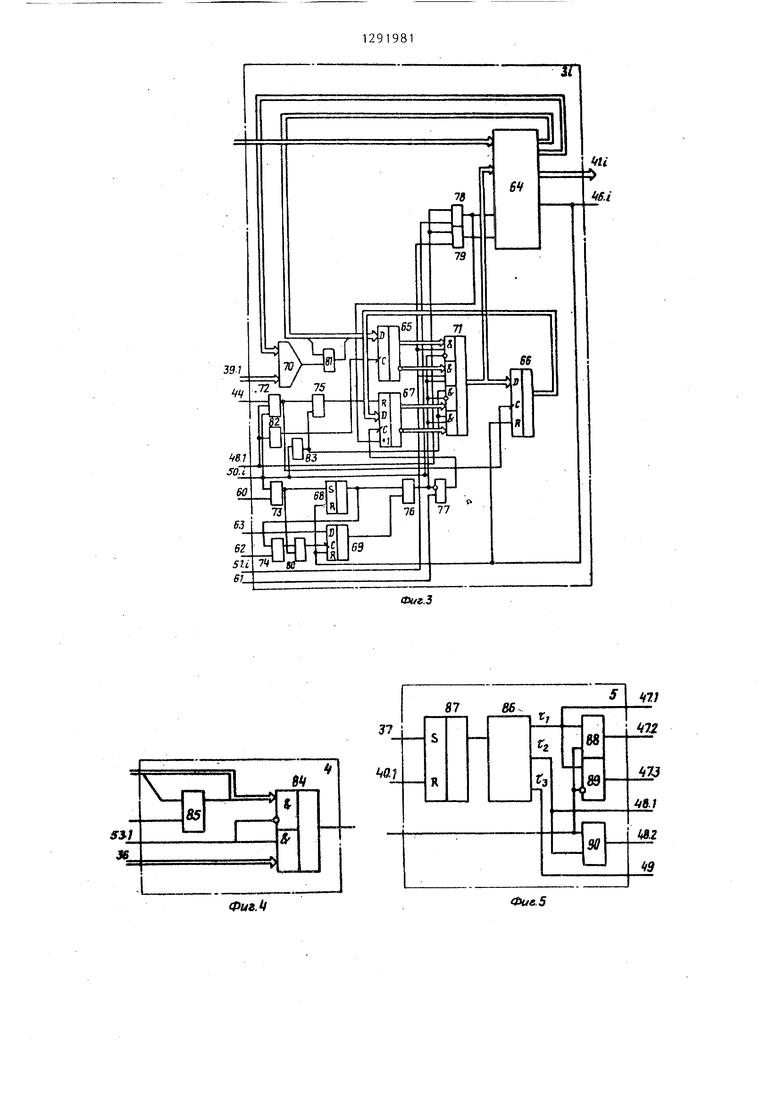

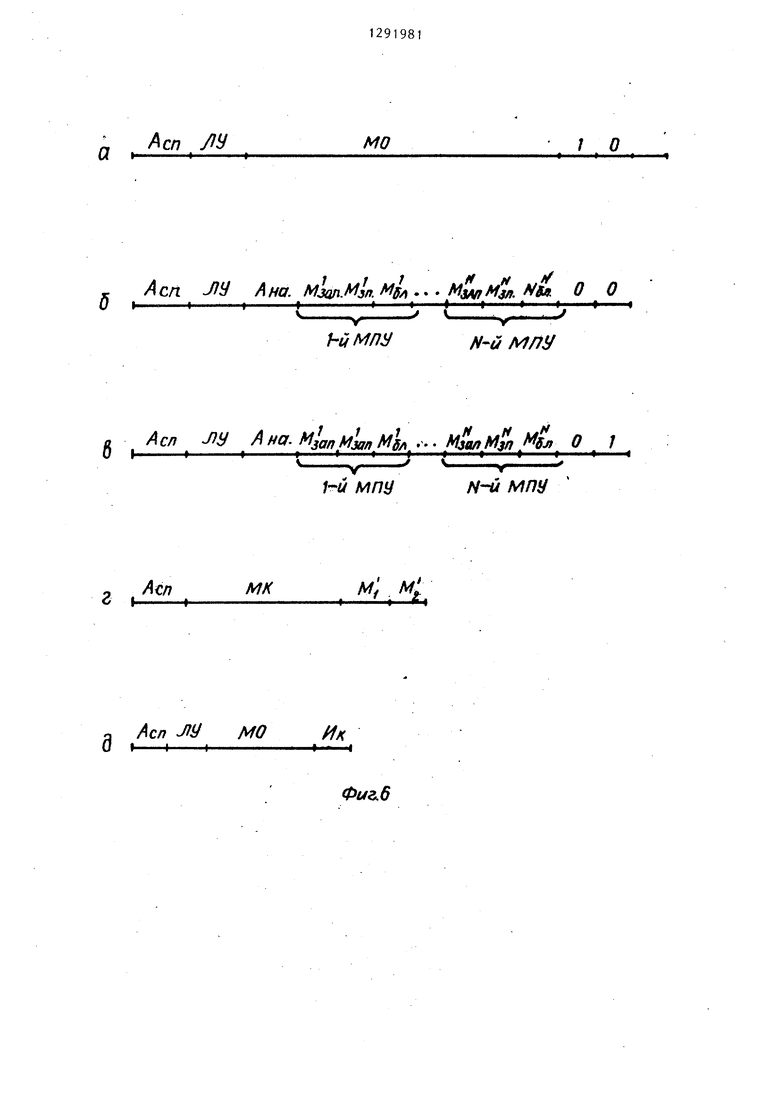

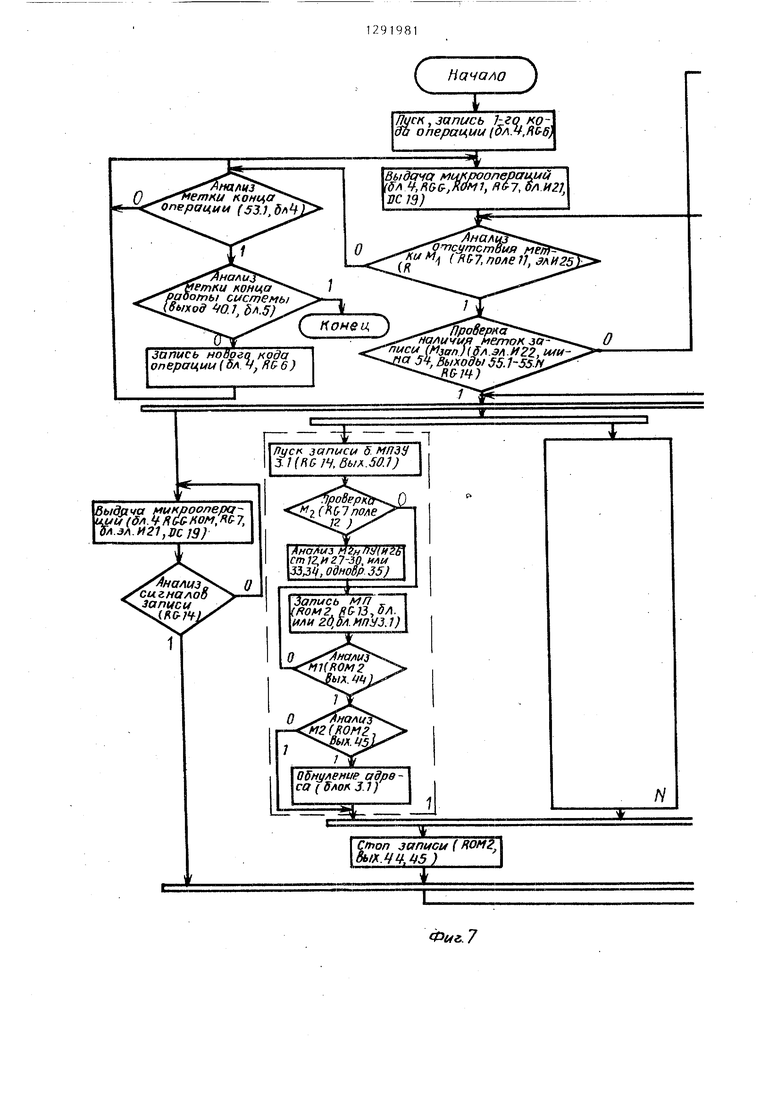

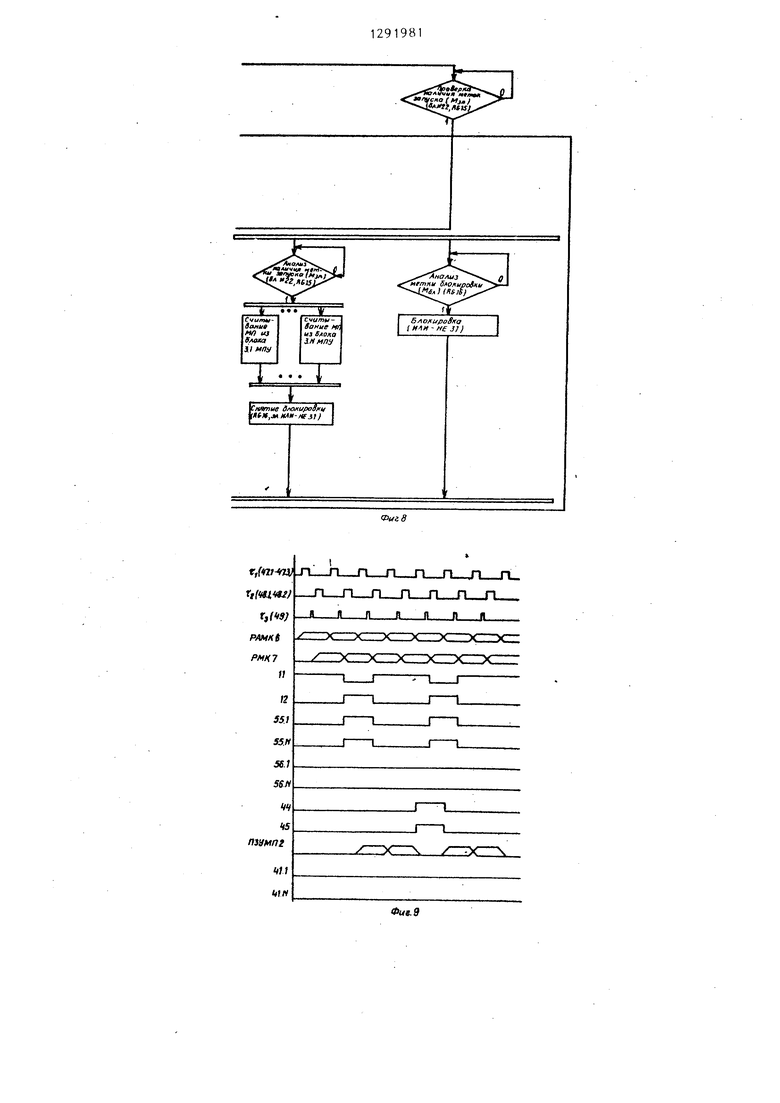

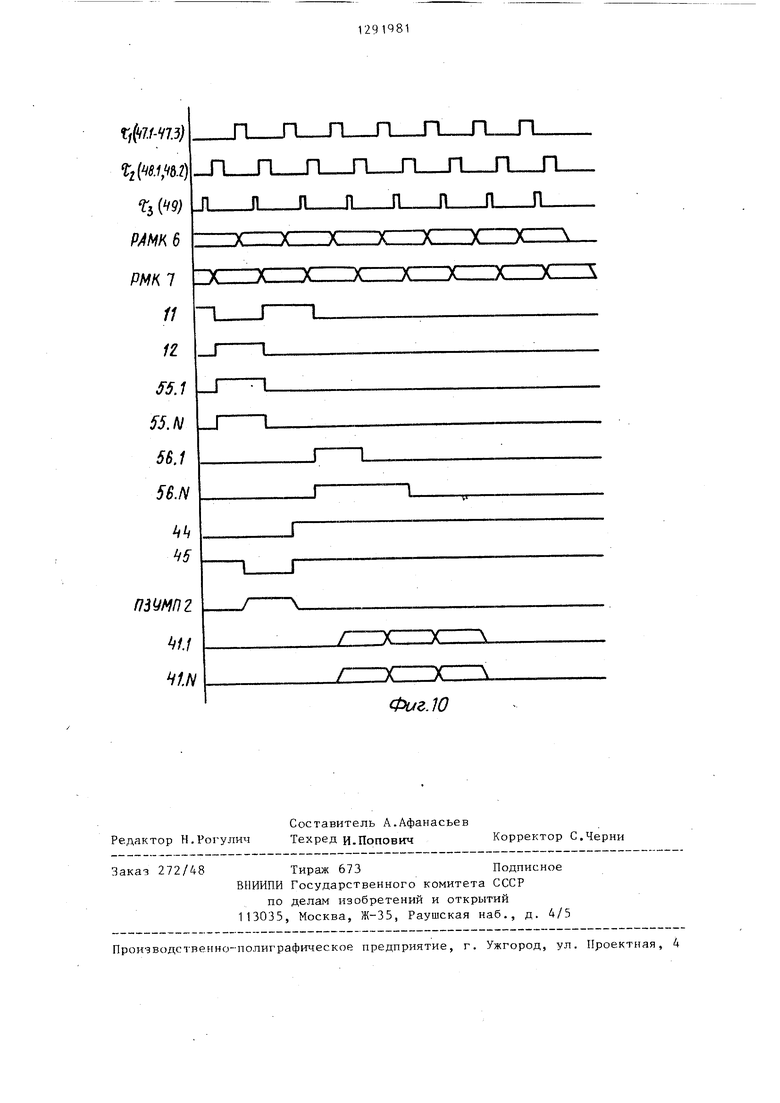

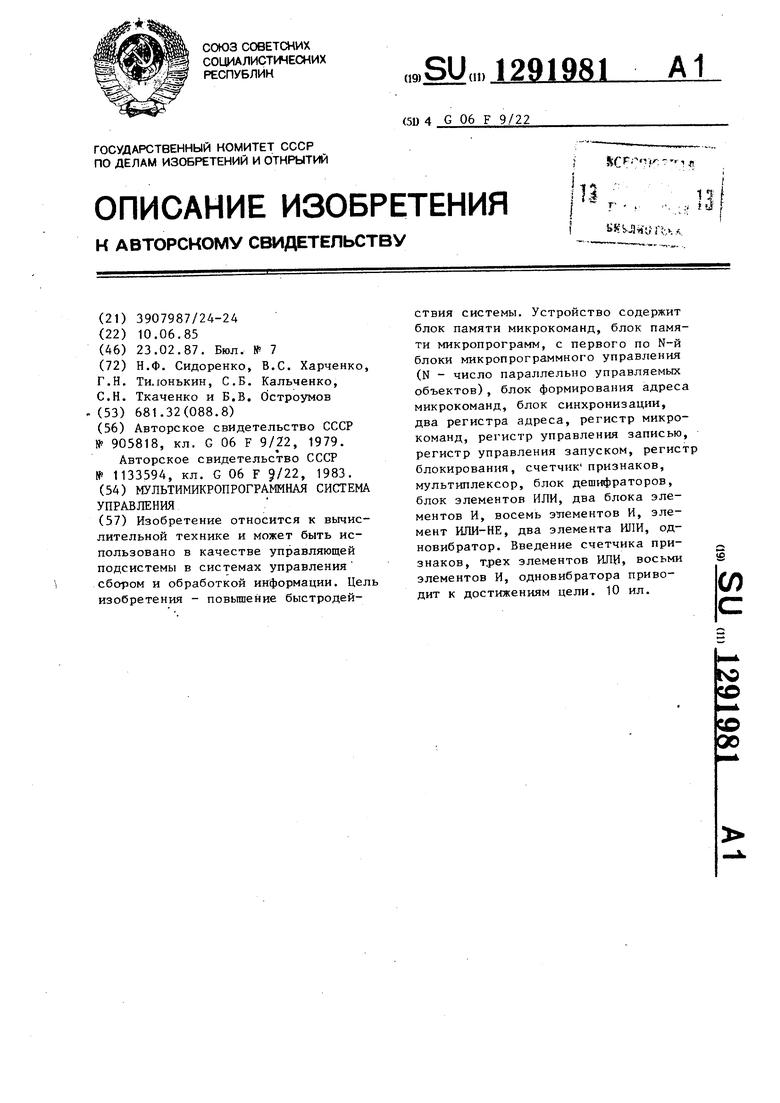

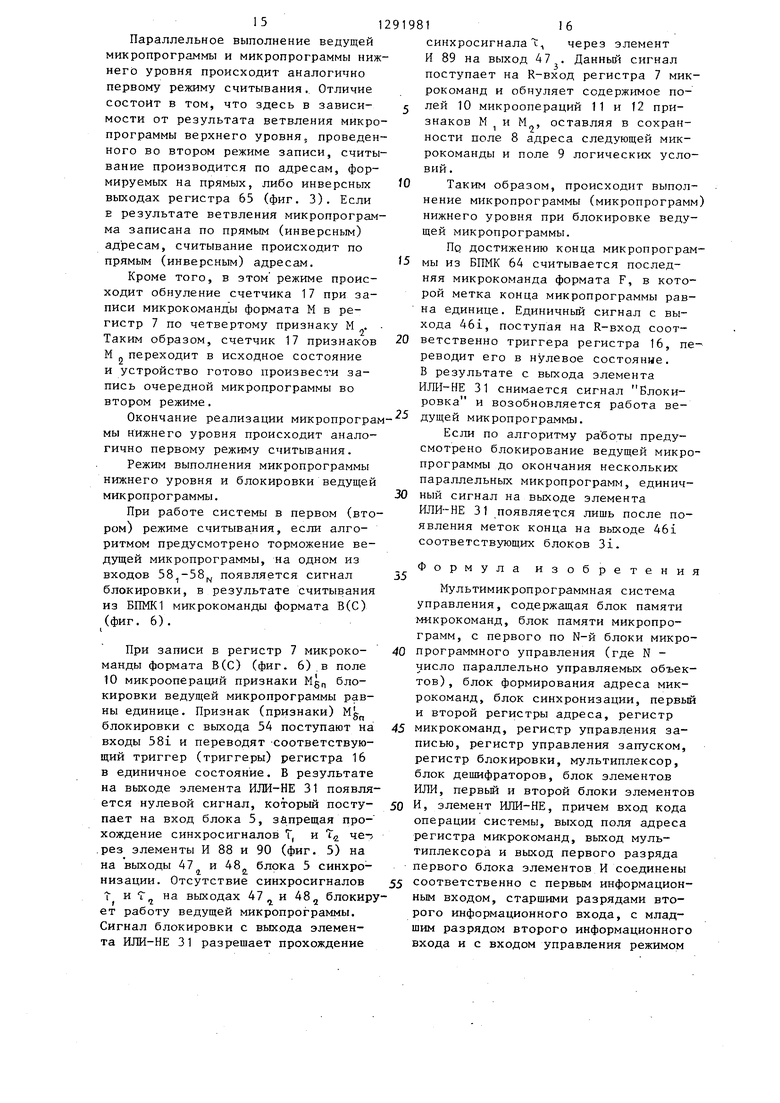

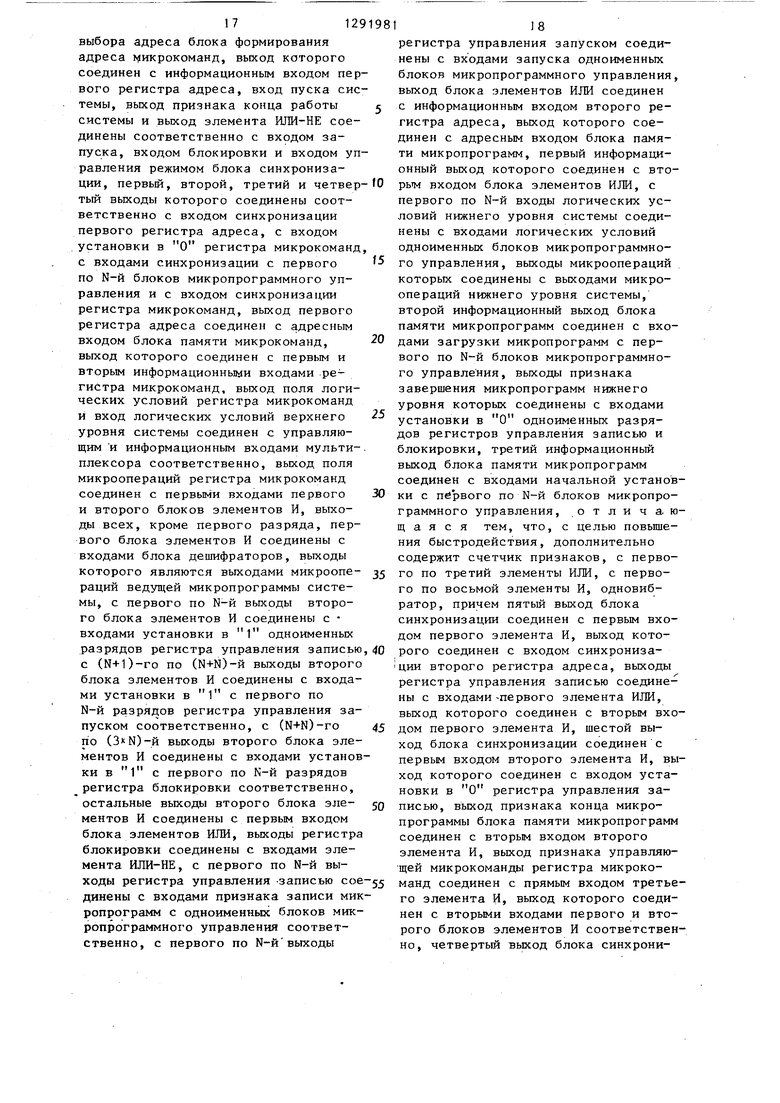

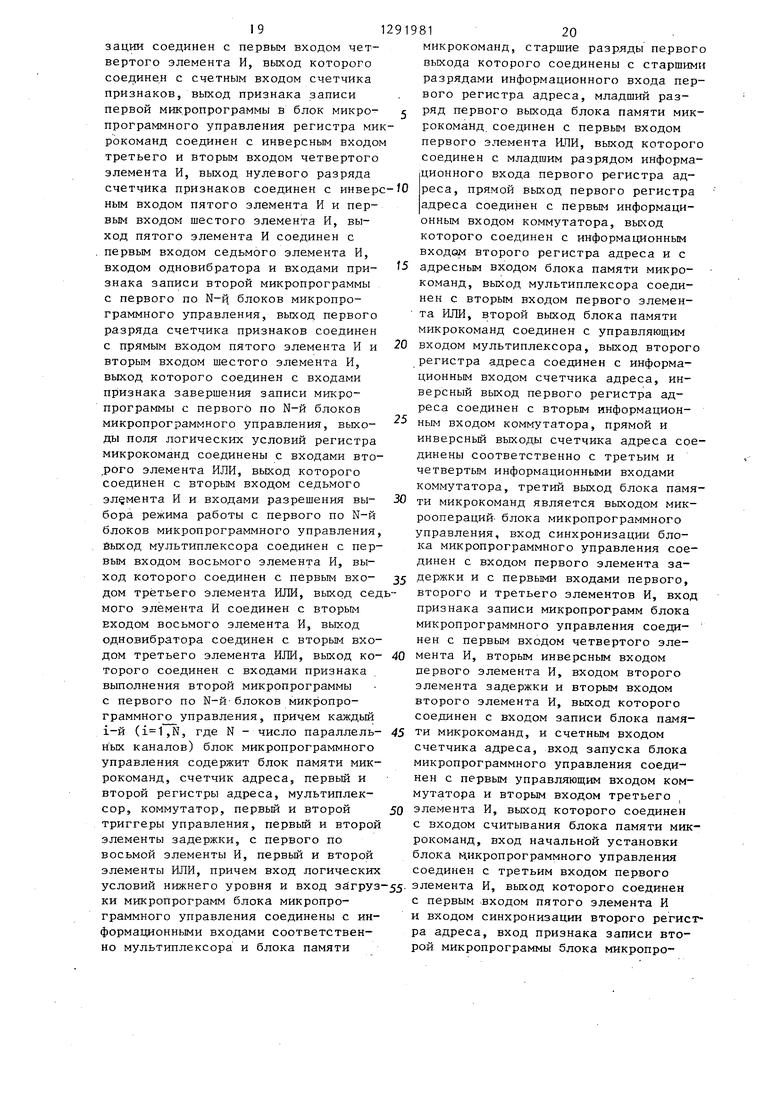

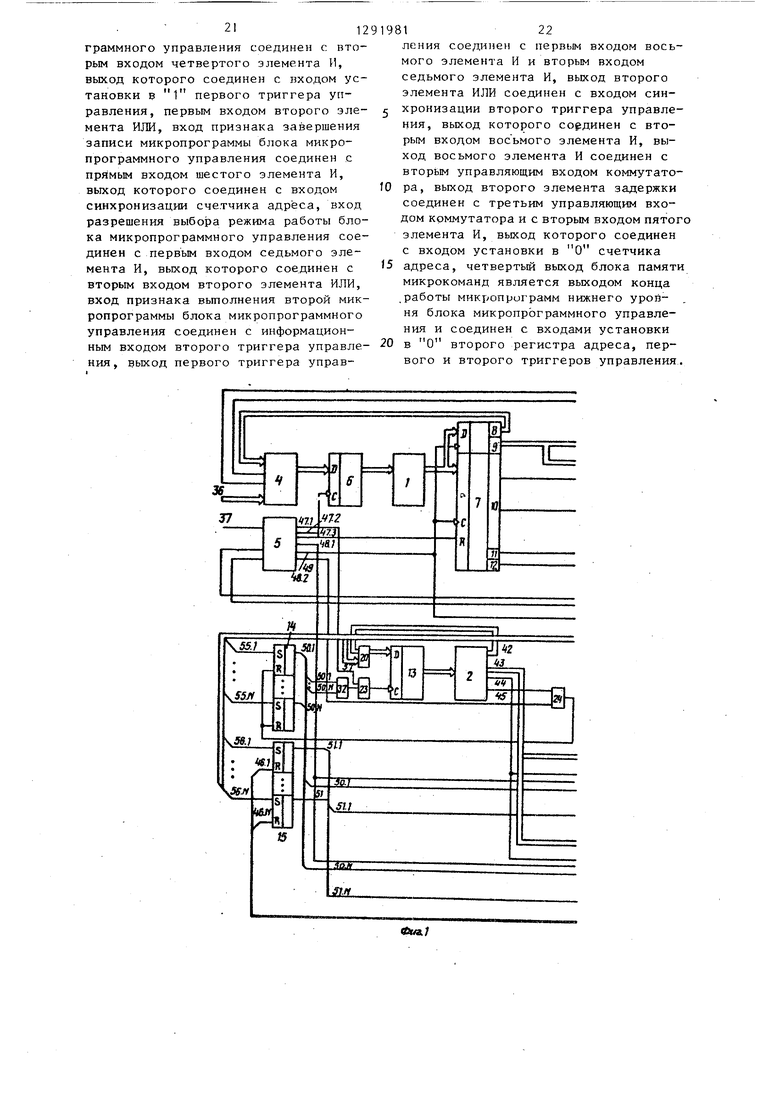

На фиг. 1 и 2 представлена функциональная схема предлагаемой системы; на фиг. 3 --функциональная схема i-ro блока микропрограммного управления; на фиг. 4 - функциональная схема блока формирования адреса; на фиг. 5 - функциональная схема блока синхронизации; на фиг. 6 - форматы микрокоманд, используемых микропрограммным управляющим устройством; на фиг. 7 и 8 - (алгоритм работы мультимикропро- граммной системы для контроля и управления; на фиг. 9 и 10 - временна диаграмма работы системы.

Система (фиг. 1 и 2) содержит блок 1 памяти микрокоманд (БПМК), блок 2 памяти микропрограммы (БПМП), блоки 3,-3fg микропрограммного управления (ШУ) , блок 4 формирования адреса микрокоманд, блок 5 синхронизации, первый регистр 6 адреса микрокоманды (РАМК), регистр 7 микрокоманд (РМК) с полями: 8 - адреса следующей микрокоманды, 9 - логических cлoвий, Ю - микроопераций, 11 - признака микрокоманды, 12 - признака режима записи (считывания) второй регистр 13 адреса, регистр 14 управления записью, регистр 15 управления запуском, регистр 16 блокировки, счетчик 17 признаков М, регистр поля 12, мультиплексор 18, блок 19 дешифраторов, блок элементов ИЛИ 20, первый блок элементов И 21, второй блок элементов И 22, первьм элемент И 23, второй элемент И 24, третий элемент И 25, четвертый элемент И 26, пятый элемент И 27, шестой элемент И 28, седьмой элемент И 29, восьмой элемент И 30, элемент ИЛИ-НЕ 31, первый элемент ИЛИ 32, второй элемент ИЛИ 33, третий элемент ИЛИ 34, одно вибратор 35.

Кроме того, система (фиг. 1 и 2) содержит вход 36 кода операции системы, вход 37 пуска системы, вход 38 логических условий верхнего урс/вня, входы логических условий нижнего уровня, выходы 40 микроопераций ведущей микропрограммы,

выходы 401 конца работы системы,

вькоды микроопераций нижнего уровня, выходы 42 адреса, шина 43 записи микропрограмм нижнего уровня, выход 44 признака М обнуления счетчика адреса блоков , выход 45 признака М „ конца микропрограммы БПМП, выходы конца работы микропрограмм нижнего ня, пятый, первый, второй выходы 47,-47 соответственно блока 5 синхронизации (вькоды синхросигналов 1 ), третий, четвертый выходы 48 и 48 2 соответственно блока 5 синхронизации (выходы синхросигналов : ), шестой выход 49 блока 5 синхронизации (выход синхросигналаt ), выходы управления записью микропрограмм нижнего уровня, выходы управления запуском микропрограмм нижнего уровня, блокировки 521-52 работы ведущей микропрограммы, шину 53 микроопераций, вьгход 53, конца команды блока И 21, шину 54 управления нижними уровнями, единичные входы 55-f-5 f/ регистра 14

управления записью микропрограмм, единичные входы регистра 15 управления запуском, шину 57 начального адреса, единичные входы 58 - 58| регистра 16 блокировки, выход

59 элемента ИЛИ-НЕ 31, выход 60 элемента И 27, выход 61 элемента И 28, выход 62 элемента ИЛИ 33, выход 63 элемента ИЛИ .

Блок 3.1 МЛУ (фиг. 3) содержит

блок 64 памяти микрокоманд (БПМК), первьв регистр 65 адреса, второй регистр 66 адреса, счетчик 67 адреса, первый триггер 68 управления, второй триггер 69 управления, мультиплексор 70; коммутатор 71 адреса, первый элемент И 72, четвертый элемент И 73, седьмой элемент И 74, пятый элемент И 75, восьмой элемент И 76, шестой элемент И 77, второй

элемент И 78, третий элемент И 79, второй элемент ИЛИ 80, первый элемент ИЛИ 81.. первьй элемент 82 задержки на Tj, , второй элемент 83 задержки на Tjj

Блок 4 фор1-1ирования адреса микрокоманды (фиг. 4) содержит коммутатор 84, элемент ИЛИ 85.

Блок 5 синхронизации (фиг. 5) содержит генератор 86, триггер 87.,

первый элемент И 88, второй элемен И 89, третий элемент И 90.

На фиг, 6 лредставлены форматы микрокоманд мультимикропрограммной системы для контроля и управления. Форматами А, В и С задаются микрокоманды ведущей микропрограммы. Идетификация форматов осуществляется по двум разрядам признаков М, и М микрокоманды; в формате А значение признака М равно единице, признака М - нулю, в формате В значения признаков М и М, равны нулю; в формате С значение признака М равно нулю, а значение признака М - единице.

Микрокоманды с форматом А содержит адресное поле А, поле логических условий (ЛУ), поле микроопераций (МО) и признаки М,, М Фор- мата. Микрокоманды с форматом В (С) содержат адресное поле А , поле ЛУ, поле начального адреса микропрограммы нижнего уровня А, по ле МО, признак формата В(С). Кроме то- го, поле МО в микрокомандах с форматом В и С содержит подполе М,,- признака записи микропрограмм на БПМП 2 в блок 31 МПУ (фиг. 1 и 2), М,п - признака запуска микропро- грамм нижнего уровня,,М - признака блокировки ведущей микропрограммы по количеству управляемых однотипных объектов .

Формат D задает микрокоманды 2 и содержит адресное поле А„ поле микрокоманд, переписьшаемых из БПМП в блоки 3,-3 МПУ, а также поле признака М обнуления счетчика 67 адреса (фиг. 3) и поле признака М 2 конца микропрограммы.

Формат F представляет микрокоманды блоков 3,-3 МПУ (фиг. 1 и 2). Он содержит адресное поле А, поле ЛУ, поле МО, поле признака конца микропрограммы нижнего уровня.

I

На фиг. 7 и 8 представлен алгоритм функционирования мультимикропрограммной системы для ..контроля и управления. Введенные здесь обозначения аналогичны обозначениями, используемым на фиг. 1 и 2.

На фиг. 9 показана времен- ная диаграмма работы системы для выходов элементов, обозначения которых соответствуют обозначениям, приведенным на фиг. 1 и 2.

Сущность изобретения состоит в повышении быстродействия за счет сокращения непроизводительных затр времени на реализацию микропрограм верхнего уровня управления путем устранения блокировки ведущей микрпрограммы при выполнении ветвлений в невозможности своевременной записи и запуска микропрограмм нижнего уровня, введения специальных форматов микрокоманд в устройстве управления верхнего уровня системы и в.ИЗУМИ для обеспечения специальной дисциплины записи и считывания, а также разбиения при записи каждой-микропрограммы, хранимой в ИЗУМИ, на две части; параллельной записи в блоки МПУ первых частей двух микропрограмм ПЗУМП и прекращения записи одной из микропрограммы в зависимости от результата ветвления ведущей микропрограммы.

Элементы системы можно разбить на средства хранения и считывания микрокоманд верхнего уровня, средства хранения и считывания микропрограмм, средства хранения и считывания микрокоманд нижнего уровня средства управления пуска и синхронизации. .

Верхний уровень предназначен для реализации ведущей микропрограммы. К средствам верхнего уровня относится БПМК1, блок 4 формирования адреса микрокоманд, первый РАЖ 6, РМК 7, мультиплексор 18, блок 19 дешифраторов.БПМК1 предназнчено для хранения микрокоманд ведущей микропрограммы.

Средства хранения и считывания микропрограмм предназначены для бесповторного хранения всех микропрограмм контроля и управления командами, которые реализуются на нижнем уровне, а также для формирования адреса микрокоманды при считывании микропрограмм в блоки 3. -3 МПУ (фиг, 3). К средствам хранения и считьшания микропрограммы относятся блок 20 элементов ИЛИ, второй регистр 13 адреса и БПМП2.

Нижний уровень предназначен для реализации микропрограмм параллельного контроля и управления однотипными объектами (например, операционными блоками) . К средствам нижнег уровня относятся, блоки Зд-3,, МПУ (фиг. 2). Блоки МПУ могут работать

512

в первом и во втором режиме записи микропрограммы из БПМП2 и в первом и во втором режиме реализагщи параллельных микропрограмм.

В первом режиме записи управляющими сигналами для блока МПУ являются: синхросигнал 1 на входе 48, сигнал записи на входе 501, которые поступают на управляющие входы коммутатора 71 и элементов И 72, 73 и 78. Счетчик 67 служит для задания адресов, по которым записываются микрокоманды. В исходном состоянии счетчик 44 находится в нулевом состоянии. С приходом синхросигнала Т и сигнала записи, единичный сигнал с выхода элемента И 78 поступает на вход счетчика 67 и на вход считывания БПЖ 64. Запись первой микрокоманды в БПМК 64 осуществляется по нулевому адресу. С выхода счетчика 67 с приходом единичного управляющего сигнала через коммутатор 71 на вход БПМК 64 поступают адреса, по которым записываются микрокоманды, поступающие в блок 31 на вход 43. По мере поступления и записи микрокоманд происходит увеличение содержимого счетчика 67. Регистр 66 адреса предназначен для хранения адреса последней микрокоманды первой части первой записываемой микропрограммы нижнего уровня во втором режиме записи. По окончании процедуры записи происходит пропадание единичного сигнала на входе 501, после чего по сигналу на входе 44 происходит синхронизация not регистра 66 (это необходимо во втором режиме записи) с задержкой 7 (элемент 83) закрывается коммутатор 71 по входам счетчика 67 и обнуляется счетчик 67.

В первом режиме реализация микропрограмм блок МПУ работает аналогично средствам верхнего уровня при реализации ведущей микропрограммы. Сигналом перевода в данный режим является единичный сигнал запуска, ко . торый поступает на вход 511. После прихода этого сигнала из 64 счтывается первая микрокоманда формата F (фиг. 6) по нулевому адресу, заданному в регистре 65. После прихода задержанного на время считывания информации БПМК 64 синхросигнала t в регистр 65 записывается адрес следующей микрокоманды и т.д. Сигналы микроопераций по мере считывания их из БПМК 64 поступают на вы16

ход 411. Модификация адреса с помощью мультиплексора 70 и элемента ИЛИ 81 осуществляется также, как при формировании адреса микрокоманд ведущей микропрограммы. При появлении единичного сигнала на выходе 461 происходит обнуление регистра 66 триггеров 68 и 69 и выдается команда о конце работы микропрограммы нижнего уровня на регистры 15 и 16 (фиг. 1 и 2).

Вторрй режим записи состоит из двух этапов. На первом этапе осущест- вляется запись первых частей двух микропрограмм, причем запись первой части первой микропрограммы производится как и в первом режиме записи (по адресам, которые считываются с единичных выходов счетчика 67), а запись первой части второй микропрограммы производится по адресам, считанным с инверсных выходов счетчика 67. Второй этап заключается в окон- чании записи той микропрограммы, команда на запись которой п оступила после ветвления ведущей микропрограммы. Соответственно, если в результате ветвления выяснилась необходи- мость вьтолнения первой (второй) микропрограммы, производится завершение ее записи по прямым (инверсным) адресам, считанным со счетчика 67. Моментом начала записи перво- но участка второй микропрограммы является поступление синхроимпульсов на вход 48 , единичного сигнала запись на вход 501 и, кроме того, управляющих единичных сигналов на входы 60 и 63. По единичным сигналам на входах 60 и 501 происходит установка триггера 69 в единичное состояние, после чего по заднему фронту сигнала на выходе элемента И 73 в единицу устанавливается триггер 69. На входе элемента И 76 появляется единичньш потенциал, который закрывает вход коммутатора по прямым выходам регистра 65 и счетчи- ка 67 и открывает по инверсным. Таким образом, обеспечивается запись первого участка второй микропрограм- 1МЫ по адресам, считываемым с инверсных выходов счетчика 67. По окончании записи на входе 501 появляется нулевой потенциал, закрывающий коммутатор 71, элементы И 73 и 78 (обнуление счетчика 67 не происходит) .

71

При ветвлении ведущей микропрограммы на управляющий вход 62 поступает единичный сигнал, который через элементы И 74, ИЛИ 80 по заднем формату синхронизирует триггер 69. Одновременно на информационный вход 63 триггера 69 поступает результат модификации адреса ведущей микропрограммы. Если в результате модификации получен нулевой сигнал, ком- мутатор 71 открывается по единичным выходам регистра 65 и счетчика 67, Одновременно открывается элемент И 77, разрешая прохождение управляющего сигнала с входа 61 для синхро- низации записи адреса с регистра 66 в Счетчик 67. Если в результате модификации получен единичный сигнал, коммутатор остается открыт по инверсным выходам регистра 65 и счетчика 67, элемент И 77 закрывается и перезапись адреса из регистра 66 в счетчик 67 не производится. С поступлением очередного сигнала записи на вход 501 и синхроимпульсов на вход 48 одновременно поступает управляющий единичный сигнал на вхо 61, которым (если триггер 69 в нулевом состоянии) через элемент И 77 синхронизируется перезапись последнего адреса первого участка первой микропрограммы в счетчик 67, с последующим завершением записи этой микропрограммы. Если триггер 69 в единичном состоянии, синхронизация не-происходит и записывается до конца вторая микропрограмма (адреса считываются с инверсных выходов сче чика 67), Окончание записи микропрограммы в целом происходит анало- гично тому, как завершается запись первой части первой микропрограммы. Таким образом, по окончании второго режима задержки в блоке МПУ 3i записана одна микропрограмма, причем, если результат ветвления ведущей микропрограммы равен единице (нулю) запись производится по инверсным (прямым) адресам, считываемым со счетчика 67, Отличие второго режима реализации микропрограмм нижнего уровня состоит в том, чл о микропрограмма может считываться, как по адресам, формируемым на единичных выходах регистра 65, так и по адре- сам, формируемым на инверсных выхо- дах регистра 65, Это зависит от того, как записана микропрограмма.

0

5

10 -5 5 0 5 0 5

0

Предлагаемая мультимикропро- граммная система для контроля и управления функционирует в следующих режимах: режим ведущей микропрограммы; выполнение ведущей МП микропрограммы и одновременной записи ее БПМП в -блоки МПУ в первом режиме записи; выполнение ведущей микропрограммы и одновременной записи ее БПМП в блоки МПУ во втором режиме записи; вьшолнение ведущей микропрограммы и микропрограмм нижнего уровня в первом режиме считы- ванид,; выполнение ведущей микропрограммы и микропрограмм нижнего уровня во втором режиме считывания; режим выполнения микропрограмм нижнего уровня и блокировки ведущей микропрограммы.

Алгоритм функционирования мульти- микропрограммной системы для контроля и управления представлен на фи г. 7 и 8.

Режим ведущей микропрограммы.

В исходном состоянии все триггеры находятся в нулевом состоянии, кроме двух триггеров регистра 7 микрокоманд в соответствующем разряде поля 10 микроопераций, а также в поле 11 признака микрокоманды записана единица. Эти eдиничныe сигналы формируют управляющий сигнал на выходе 53 , В БПМК1 записаны микрокоманды ведущей микропрограммы, В БПМП2 записаны микропрограммы нижнего уровня, В БПМК 64 блоков 3i записана нулевая информация. Объем памяти БПМК 64 рассчитан на две микропрограммы максимальной длины, хранящиеся в БПМП2,

С подачей сигнала Пуск на вход 37 блока 5 синхронизации триггер 87 (фиг, 5) устанавливается в единичное состояние и включает генератор 86, формирующий последовательности тактовых импульсов 7г , Т з Код операции, задающий начальный адрес ведупа,ей микропрограммы, поступает на вход 36 блока 4 формирования адреса, С выхода 53 , единичный сигнал разрешает прохождение на вькод блока 4 начального адреса микропро- г раммы.

По первому тактовому импульсу f , поступающему с выхода 47.2 на вход первого регистра 6 адреса, проходит запись в регистр 6 начального адреса микропрограммы.

По

первому тактовому импульсу

Г происходитзапись в регистр 7 первой микрокоманды ведуп1ей микропрограммы из БПМК1, Формат считанной микрокоманды из БПЖ1 показан на фиг. 6, В рассматриваемом режиме функционирования устройства в регист

7микрокоманд записываются микрокоманды формата А, отличительным признаком которого является наличие единицы в поле 11.регистра 7. В поле 8 регистра 7 находится адрес следующей микрокоманды, которьй поступает на блок 4 формирования адреса.

8результате записи первой микрокоманды в регистр 7 на выходе 53 формируется нулевой сигнал, который запрещает поступление на выход блока 4 (фиг. 4) очередного кода операции и разрешает прохождение на выход блока 4 адреса следующей микрокоманды. После прихода второго тактового импульса Т работа устройств происходит аналогично. В регистр 6 адреса записывается адрес следующей микрокоманды,.а с приходом второго тактового импульса T,j на БПМК1

в регистр 7 записывается вторая микрокоманда и т.д.

Единичным сигналом с поля 11 регистра 7 разрешается считывание сигналов микроопераций с выходов 53 блока элементов И 21. Сигналы микроопераций с выходов 53 поступают на вход блока 19 дешифраторов, который формирует управляющие сигналы.

В точках ветвления микропрограммы в блоке 4 происходит модификация адреса в соответствии со значением логического условия на выходе мультиплексора 18.

При появлении на выходе 53.1 единичного управляющего сигнала Конец команды устройство работает по очередному коду операции.

Работа устройства прекращается по единичному сигналу Конец работы :поступающему с выхода 40 на вход

.блока 5 синхронизации. Данный сигнал 50 микропрограммы. Одновременно адрес

поступает на R-вкод триггера 87 (фиг. 5), тем самым прекращая выдачу синхросигналовt и Т (фиг. 9 и 10).

Выполнение ведущей микропрограммы и одновременной ее записи из БПМП2 в блоки 3 МПУ в первом режиме записи.

Работа предлагаемой мультимикро- программной системы для контроля и управления в данном режиме происходит аналогично работе системы в режиме ведущей микропрограммы. Отличие заключается в том, что одновременно с работой ведущей микропрограммы происходит запись необходимых микропрограмм из БПМП2 в блоки 3, в первом режиме.

В исходном состоянии регистры 14-16, счетчик 17 и счетчик 67 (фиг. 3) находятся в нулевом состоянии. Управляющий сигнал на один из входов регистра 14 управления записи микропрограмм нижнего уровня поступает с выхода 54 при записи в РМК 7 формата В (фиг. 6). При этом с полей меток 11 и 12 РМК 7 элемента И 25 поступают нулевые сигналы, обуславливая появление разрешающего нулевого сигнала на прохождение информации через блок элементов И 22 на шину 54. В результате на шине 54 блока элементов И 22 появляется начальный адрес . микропрограммы, которую необходимо записать из БПМ112 в БПМК64 и управляющий сигнал на входе 55i регистра 14 управления записью микропрограмм нижнего уровня, устанавливающий один из триггеров регистра 14 в единичное состояние, тем самым разрешая запись микропрограммы в

блок 31 МПУ. При этом управляющий сигнал с вькода элемента ИЛИ 32 открывает элемент И 23 для прохождения синхросигналов -, на вход син- хронизации регистра 13 адреса.

Начальный адрес А поступает на шину 57 начального адреса и, проходя через блок элементов ИЛИ 20, с приходом синхросигнала Т, с выхода 46i блока 5 синхронизации через открытый элемент И 23 записывается во второй регистр 13 адреса. Затем из БПМП2 с выхода 43 на вход блока 31 МПУ поступает первая микрокоманда формата D (фиг. 6) необходимой

следующей микрокоманды через блок элементов ИЛИ 20 с приходом следующего синхросигнала Т, записывается во второй регистр 13 адреса. На вы- ходе 43 БПМП2 появляется вторая

микрокоманда и т.д. до тех пор, пока не будет считана последняя микрокоманда микропрограммы. В последней микрокоманде микропрограммы поле А J.J, и поле микрокоманды МК заполнено нулями, а в поле признаков М и М записаны единицы. Таким образом при считывании из БПМП2 этой микрокоманды на выходах 44 и 45 появляют- ся единичные сигналы. Сигналом с выхода 45 БПМП2 по очередному синхроимпульсу t . , поступающему с выхода 49 блока 5 синхронизации, через элемент И 24 происходит обнуление ре- гистра 14, тем самым запрещается запись микропрограмм в блок 3i МПУ. Затем происходит запись последнего адреса из счетчика 67 в регистр 66 (фиг. 3). Сигналом с выхода 44 БПМП2 происходит установка &четчика .67 адреса (фиг. 3) в нулевое состояние.

Одновременно с записью микропрограмм нижнего уровня реализуется ведущая микропрограмма. Работа средств верхнего уровня управления в этом случае осуществляется аналогично рассмотренному первому режиму работы.

Таким образом, в данном режиме осуществляется параллельная реали- зация ведущей микропрограммы и запись одной микропрограммы нижнего уровня в один или несколько блоков 31 МПУ.

Выполнение ведущей микропрограм- мы и одновременной ее записи из БПМП2 в блоки МПУ во втором режиме записи.

Работа предлагаемой системы в данном режиме происходит аналогич- но устройства в рассмотренном режиме. Отличие состоит в том, что запись производится в два этапа. Первьй состоит в записи первых час- т ей двух микропрограмм в блок 31 МПУ, причем запись первой части первой микропрограммы производится по адресам, считанным с прямых выходов счетчика 67, а запись первой части второй микропрограммы произ- водится по адресам, считанным с инверсных выходов счетчика.67 (фиг. 3) Второй этап состоит в анализе результата ветвления ведущей микропрограм- bftji и в соответствии с этим окончании записи одной из микропрограмм нижнего уровня. Ecjra результат модификации разряда адреса ведущей микропрограммы равен нулю (единице), то заканчивается запись первой (вто- рой) микропрограммы нижнего уровня в блок 31 МПУ. В исходном состоянии регистры 14-16, счетчик 17 и счетчик 67 (фиг. 3) находятся в нулевом состоянии. Управляющий сигнал на один из входов регистра 14 управления записи микропрограмм нижнего уровня поступает с выхода 54 при записи в регистр 7 микрокоманды формата С (фиг. 6). При этом с полей 11 и 12 регистра 7 поступает соответственно нулевой и единичный сигналы на входы элемента И 25. Этим обуславливается появление разрешающего нулевого сигнала на входе блока элементов И 22 для прохождения информации с поля 10 регистра 7 на выходь; 54. В результате на выходах 54 блока элементов И 22 появляется начальный адрес А , „ первой микропрограммы, первую часть которой необходимо записать из БПМП2 Б БПМК 64 и управляющий сигнал на входе 551 регистра 14 управления записью микропрограмм нижнего уровня, устанавливающий один из триггеров регистра 14 в единичное состояние, тем самым разрешая запись микропрограммы в блок 31 МПУ. Одновременно единичный сигнал с поля 12 метки регистра 7 микрокоманд поступает на управляющий вход элемента И 26, тем самым разрешая регистрацию первого признака М Jсчетчиком 17 по заднему фронту синхросигнала - (фиг. 9 и 10). Далее аналогично первому режиму записи происходит считывание информации из БПМП2 и запись ее в блоки 31 МПУ. По окончании записи аналогично первому режиму записи происходит обнуление регистра 14 и счетчика 67 (фиг. 3) по признакам К и М соответственно. Кроме того, перед обнулением счетчика 67 последний адрес, записанный в нем, запоминается в регистре 66. Это необходимо для того, чтобы в случае нулевого результата модификации адреса можно вернуть к последнему адресу первой части первой микропрограммы и завершить ее запись. На этом заканчивается запись первой части первой микропрограммны из БПМП2 в блоке 31 МПУ,

Одновременно происходит реализация ведущей микропрограммы, аналогично рассмотренному при описании первого режима работы (фиг. 9 и 10).

Запись первой части второй, микропрограммы нижнего уровня производится аналогично описанному. Отличие состоит в том, что при записи управляющей микрокоманды с форматом С в регистр 7 очередного признака

1312

Mj с поля 12 по заднему фронту синхроимпульса счетчик 17 через открытый элемент И 26 зарегистрирует появление второго признака М . При этом на выходе 60 элемента И 27 появляется единичный управляющий сигнал, который поступает на блоки 3i МПУ и по переднему фронту которого од- новибратор 35 через элемент МПУ через элемент ИЛИ 34 выдает управляющий сигнал на вход 63 блоков Зг МПУ.

Таким образом, по управляющим сигналам на входах 60 и 63 блока 31 МПУ переходит в готовность для приема первой части второй микропрограммы. Далее происходит запись первой части второй микропрограммы из блока БПМП2 в блок 31 МПУ, аналогично тому, как это происходило в первом режиме записи. По окончании записи из блока БПМП2 выдается микрокоманда, содержащая единичный потенциал на выходе 45 (фиг. 9 и 10). Он поступает на управляющий вход элемента И 24 и по очередному синхроимпульсу t- с выхода 49 блока 5 синхронизации обнуляется регистр 14 управления записью.;

После этого начинается второй этап записи микропрограммы нижнего уровня. При появлении единичного .управляющего сигнала на выходе 62 элемента ИЛИ 33 он поступает в блок 3i МПУ и через открытый элемент И 29 открывает элемент И 30 для прохождения результата модификации адреса ведущей микропрограммы с выхода мультиплексора 18 через элемент ИЛИ 34 на управляющий вход 63 блока 31 МПУ. В результате блок 3 МПУ фиксирует значение сигнала на выходе мультиплексора 18 в момент вет- .вления микропрограммы верхнего уровня.

После записи третьей микропрограммы формата С в регистр 7 микрокоманд аналогично описанному происходит регистрация третьего признака М „ счетчиком 17. В результате на выходе элемента И 28 (вход 61 блока 31 МПУ) появляется единичный управляющий сигнал, по которому блок 31 МПУ настраивается на завершение записи первой (второй) микропрограммы нижнего уровня, Соответственно, если результат модификации нулевой (единичный) . Окончание записи происходит аналогично тому, как это происхо1М

дило в первом режиме записи. Одновременно с записью.микропрограмм нижнего уровня реализуется ведущая микропрограмма. Работа средств верхнего уровня управления в этом случае осуществляется аналогично рассмотренному первому режиму работы. Таким образом, в данном режиме осуществляется параллельная реализаЦия ведущей микропрограммы и запись одной микропрограммы нижнего уровня в один или несколько блоков 31 МПУ. Выполнение ведущей микропрограммы и микропрограммы нижнего уровня

в первом режиме считывания.

После того, как в блоки 31 в первом режиме записи записаны микропрограммы, из БПМК1 считывается микро- команда формата В (Лиг. 6) и через

блок элементов И 22 выдаются управляю-, щие сигналы на запуск микропрограмм нижнего уровня. При записи в РМК 7 формата В (фиг. 6) в поле 10 микрооперации признак (признаки) М запуска микропрограммы (равны) единице. Признак (признаки) М шины 54 поступает на входы 561 управления пуском, тем самым переводя соответствующий триггер (триггеры)

регистра 15 в единичное состояние. Единичный сигнал с выхода 511 регистра 15 поступает на вход блока 31 МПУ и разрешает прохождение синхросигналов t через элемент И 79 на

Б1ТМК 64 (фиг. 3). Одновременно этот сигнал разрешает считывание первой микрокоманды формата F (фиг. 6) по нулевому адресу, который записан в регистре 65. При этом коммутатор 71

открыт по прямым выходам регистра 65. В результате на выходе 411 блока 31 появляются сигналы микроопераций.

По достижению конца микропрограммы из БПМК 64 считывается последняя микрокоманда, формата F, в которой признак конца микропрограммы равен единице. Этот сигнал с выхода 461 поступает на. вход обнуления соответствующего триггера запуска регистра 15 управления запуском, тем самым переводя его в нулевое состояние. На этом процедура считывания микропрограммы в первом режиме считывания

завершается. Одновременно реализуется ведущая микропрограмма.

Выполнение ведущей микропрограммы и микропрограмма нижнего уровня во втором режиме считывания.

15

Параллельное выполнение ведущей микропрограммы и микропрограммы нижнего уровня происходит аналогично первому режиму считывания. Отличие состоит в том, что здесь в зависимости от результата ветвления микропрограммы верхнего уровня, проведенного во втором режиме записи, считывание производится по адресам, формируемых на прямых, либо инверсных выходах регистра 65 (фиг. 3). Если в результате ветвления микропрограмма записана по прямым (инверсным) адресам, считывание происходит по прямым (инверсным) адресам.

Кроме того, в этом режиме происходит обнуление счетчика 17 при записи микрокоманды формата М в регистр 7 по четвертому признаку М . Таким образом, счетчик 17 признаков М - переходит в исходное состояние и устройство готово произвести запись очередной микропрограммы во втором режиме,

синхросигнала L,

16 чер

знаков М и М , ности поле

JO

И 89 на выход 47 . Да поступает на R-вход р рокоманд и обнуляет с лей 10 микроопераций

оставл адреса сл рокоманды и поле 9 ло вий.

Таким образом, прои нение микропрограммы нижнего уровня при бло щей микропрограммы.

По достижению конца 15 мы из БПМК 64 считывае няя микрокоманда форма рой метка конца микроп на единице. Единичньй хода 461, поступая на ветственно триггера ре реводит его в нулевое В результате с выхода ИЛИ-НЕ 31 снимается си ровка и возобновляетс

20

Окончание реализации микропрограм- ДУЩей микропрограммы.

мы нижнего уровня происходит аналогично первому режиму считывания.

Режим выполнения микропрограммы нижнего уровня и блокировки ведущей микропрограммы.

При работе системы в первом (втором) режиме считывания, если алгоритмом предусмотрено торможение ведущей микропрограммы, на одном из входов , появляется сигнал блокировки, в результате считывания из БПЖ1 микрокоманды формата В(С)

(фиг. 6).

t

При записи в регистр 7 микрокоманды формата В(С) (фиг. 6).в поле 10 микроопераций признаки Mgn блокировки ведущей микропрограммы равны единице. Признак (признаки) Mg

Если по алгоритму ра боты предусмотрено блокирование ведущей микро программы до окончания нескольких параллельных микропрограмм, единич- 30 ный сигнал на выходе элемента

ИЛИ-НЕ 31 появляется лишь после появления меток конца на выходе 46i соответствующих блоков 31.

.Формула изобретения

Мультимикропрограммная система управления, содержащая блок памяти микрокоманд, блок памяти микропрограмм, с первого по N-й блоки микро- 40 программного управления (где N число параллельно управляемых объектов), блок формирования адреса микрокоманд, блок синхронизации, первьй и второй регистры адреса, регистр

блокировки с выхода 54 поступают на 45 микрокоманд, регистр управления завходы 581 и переводят -соответствующий триггер (триггеры) регистра 16 в единичное состояние. В результате на выходе элемента ИЛИ-НЕ 31 появляется нулевой сигнал, который посту- 50 И, элемент ИЛИ-НЕ, причем вход кода

пает на вход блока 5, запрещая про- хождение синхросигналов Т, и Т че-7 .рез элементы И 88 и 90 (фиг. 5) на на выходы 47 и 48, блока 5 синхронизации. Отсутствие синхросигналов и Т„ на выходах 47„ и 48„ блокируI и I пса ооол. ,ci -т/ fi -т W л

ет работу ведущей микропрограммы. Сигнал блокировки с выхода элемента ИЛИ-НЕ 31 разрешает прохождение

синхросигнала L,

16 через элемент

знаков М и М , ности поле

O

И 89 на выход 47 . Данный сигнал поступает на R-вход регистра 7 микрокоманд и обнуляет содержимое полей 10 микроопераций 11 и 12 приоставляя в сохран- адреса следующей микрокоманды и поле 9 логических условий.

Таким образом, происходит выполнение микропрограммы (микропрограмм) нижнего уровня при блокировке ведущей микропрограммы.

По достижению конца микропрограм- 5 мы из БПМК 64 считывается последняя микрокоманда формата F, в которой метка конца микропрограммы равна единице. Единичньй сигнал с выхода 461, поступая на R-БХОД соответственно триггера регистра 16, переводит его в нулевое состояние. В результате с выхода элемента ИЛИ-НЕ 31 снимается сигнал Блокировка и возобновляется работа ве0

Если по алгоритму ра боты предусмотрено блокирование ведущей микропрограммы до окончания нескольких параллельных микропрограмм, единич- ный сигнал на выходе элемента

ИЛИ-НЕ 31 появляется лишь после появления меток конца на выходе 46i соответствующих блоков 31.

Формула изобретения

Мультимикропрограммная система управления, содержащая блок памяти микрокоманд, блок памяти микропрограмм, с первого по N-й блоки микро- программного управления (где N число параллельно управляемых объектов), блок формирования адреса микрокоманд, блок синхронизации, первьй и второй регистры адреса, регистр

писью, регистр управления запуском, регистр блокировки, мультиплексор, блок дешифраторов, блок злементо.в ИЛИ, первьй и второй блоки элементов

операции системы, выход поля адреса регистра микрокоманд, выход мультиплексора и выход первого разряда первого блока элементов И соединены соответственно с первым информационным входом, старшими разрядами второго информационного входа, с младшим разрядом второго информационного входа и с входом управления режимом

7129

выбора адреса блока формирования адреса г икрокоманд, выход которого соединен с информационным входом первого регистра адреса, вход пуска системы, выход признака конца работы системы и выход элемента ИЛИ-НЕ соединены соответственно с входом запуска, входом блокировки и входом управления режимом блока синхронизации, первьм, второй, третий и четвертый выходы которого соединены соответственно с входом синхронизации первого регистра адреса, с входом установки в О регистра микрокоманд с входами синхронизации с первого по N-й блоков микропрограммного управления и с входом синхронизации регистра микрокоманд, выход первого регистра адреса соединен с адресным входом блока памяти микрокоманд, выход которого соединен с первым и вторым информационными входами регистра микрокоманд, выход поля логических условий регистра микрокоманд и вход логических условий верхнего уровня системы соединен с управляющим и информационным входами мультиплексора соответственно, выход поля микроопераций регистра микрокоманд соединен с первыми входами первого и второго блоков элементов И, выходы всех, кроме первого разряда, первого блока элементов И соединены с входами блока дешифраторов, выходы которого являются выходами микроопе- раций ведущей микропрограммы системы, с первого по N-й выходы второго блока элементов И соединены с входами установки в 1 одноименных разрядов регистра управления записью с (N+1)-ro по (N+N)-й выходы второго блока элементов И соединены с входами установки в 1 с первого по N-Й разрядов регистра управления запуском соответственно, с (N+N)-ro по (ЗхЫ)-й выходы второго блока элементов И соединены с входами установки в 1 с первого по N-й разрядов регистра блокировки соответственно, остальные выходы второго блока эле- ментов И соединены с первым входом блока элементов ИЛИ, выходы регистра блокировки соединены с входами элемента ИЛИ-НЕ, с первого по N-й выходы регистра управления -записью сое динены с входами признака записи микропрограмм с одноименных блоков микропрограммного управления соответственно, с первого по N-й выходы

t18

регистра управления запуском соединены с входами запуска одноименных блоков микропрограммного управления выход блока элементов ИЛИ соединен с информационным входом второго регистра адреса, выход которого соединен с адресным входом блока памяти микропрограмм, первый информационный выход которого соединен с вто- рьтм входом блока элементов ИЛИ, с первого по N-й входы логических условий нижнего уровня системы соединены с входами логических условий одноименных блоков микропрограммного управления, выходы микроопераций которых соединены с выходами микроопераций нижнего уровня системы, второй информационный выход блока памяти микропрограмм соединен с входами загрузки микропрограмм с первого по N-й блоков микропрограммного управления, выходы признака завершения микропрограмм нижнего уровня которых соединены с входами установки в О одноименных разрядов регистров управления записью и блокировки, третий информационньш выход блока памяти микропрограмм соединен с входами начальной установки с пе рвого по N-й блоков микропрограммного управления, отличающаяся тем, что, с целью повышения быстродействия, дополнительно содержит счетчик признаков, с первого по третий элементы ИЛИ, с первого по восьмой элементы И, одновиб- ратор, причем пятый выход блока синхронизации соединен с первым входом первого элемента И, выход которого соединен с входом синхронизаiции второго регистра адреса, выходы регистра управления записью соединены с входами первого элемента ИЛИ, выход которого соединен с вторым входом первого элемента И, шестой выход блока синхронизации соединен с первым входом второго элемента И, выход которого соединен с входом установки в О регистра управления записью, выход признака конца микропрограммы блока памяти микропрограмм соединен с вторым входом второго элемента И, выход признака управляющей микрокоманды регистра микрокоманд соединен с прямым входом третьего элемента И, выход которого соединен с вторыми входами первого и второго блоков элементов И соответственно, четвертый выход блока синхрони19

зации соединен с первым входом вертого элемента И, выход которого соединен с счетным входом счетчика признаков, выход признака записи первой мик.ропрограммы в блок микро- 5 программного управления регистра микрокоманд соединен с инверсным входом третьего и вторым входом четвертого элемента И, выход нулевого разряда счетчика признаков соединен с инверс- О ным входом пятого элемента И и первым входом шестого элемента И, выход пятого элемента И соединен с первым входом седьмого элемента И, входом одновибратора и входами признака записи второй микропрограммы с первого по N-й. блоков микропрограммного управления, выход первого разряда счетчика признаков соединен

и

с прямым входом пятого элемента И вторым входом шестого элемента И, выход которого соединен с входами признака завершения записи микропрограммы с первого по N-Й блоков микропрограммного управления, выходы поля логических условий регистра микрокоманд соединены с входами второго элемента ИЛИ, выход которого соединен с вторым входом седьмого элемента И и входами разрешения выбора режима работы с первого по N-й блоков микропрограммного управления, йыход мультиплексора соединен с первым входом восьмого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход седьмого элемента И соединен с вторым входом восьмого элемента И, выход одновибратора соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с входами признака выполнения второй микропрограммы с первого по N-Й-блоков микропрограммного управления, причем каждый i-й (,N, где N - число параллель- н ых каналов) блок микропрограммного управления содержит блок памяти микрокоманд, счетчик адреса, первый и второй регистры адреса, мультиплексор, коммутатор, первый и второй триггеры управления, первый и второй элементы задержки, с первого по восьмой элементы И, первьй и второй элементы ИЛИ, причем вход логических

129198120

чет- микрокоманд, старшие разряды первого выхода которого соединены с старшими разрядами информадионного входа первого регистра адреса, младший разряд первого выхода блока памяти микрокоманд соединен с первым входом первого элемента ИЛИ, выход которого соединен с младшим разрядом информадионного входа первого регистра адреса, прямой выход первого регистра адреса соединен с первым информационным входом коммутатора, выход которого соединен с информационным входом второго регистра адреса и с адресным входом блока памяти микрокоманд, выход мультиплексора соединен с вторым входом первого элемента ИЛИ, второй выход блока памяти микрокоманд соединен с управляющим входом мультиплексора, выход второго регистра адреса соединен с информаf5

20

25

30

35

40

45

50

ционным входом счетчика адреса, инверсный выход первого регистра адреса соединен с вторым информационным входом коммутатора, прямой и инверсньй выходы счетчика адреса соединены соответственно с третьим и четвертым информационными входами коммутатора, третий выход блока памяти микрокоманд является выходом микроопераций- блока микропрограммного управления, вход синхронизации блока микропрограммного управления соединен с входом первого элемента задержки и с первыми входами первого, второго и третьего элементов И, вход признака записи микропрограмм блока микропрограммного управления соеди- нен с первым входом четвертого элемента И, вторым инверсным входом первого элемента И, входом второго элемента задержки и вторым входом второго элемента И, выход которого соединен с входом записи блока памяти микрокоманд, и счетным входом счетчика адреса, вход запуска блока микропрограммного управления соединен с первым управляющим входом коммутатора и вторым входом третьего элемента И, выход которого соединен с входом считывания блока памяти микрокоманд, вход начальной установки блока никропрограммного управления соединен с третьим входом первого

условий нижнего уровня и вход загруз-55- элемента И, выход которого соедннен ки микропрограмм блока микропро- с первым входом пятого элемента И граммного управления соединены с ий- и входом синхронизации второго регист- формационными входами соответствен- ра адреса, вход признака записи вто- но мультиплексора и блока памяти РОЙ микропрограммы блока микропро5 - О

ь

9198120

микрокоманд, старшие разряды первого выхода которого соединены с старшими разрядами информадионного входа первого регистра адреса, младший разряд первого выхода блока памяти микрокоманд соединен с первым входом первого элемента ИЛИ, выход которого соединен с младшим разрядом информадионного входа первого регистра адреса, прямой выход первого регистра адреса соединен с первым информационным входом коммутатора, выход которого соединен с информационным входом второго регистра адреса и с адресным входом блока памяти микрокоманд, выход мультиплексора соединен с вторым входом первого элемента ИЛИ, второй выход блока памяти микрокоманд соединен с управляющим входом мультиплексора, выход второго регистра адреса соединен с информаf5

20

5

0

5

0

5

0

ционным входом счетчика адреса, инверсный выход первого регистра адреса соединен с вторым информационным входом коммутатора, прямой и инверсньй выходы счетчика адреса соединены соответственно с третьим и четвертым информационными входами коммутатора, третий выход блока памяти микрокоманд является выходом микроопераций- блока микропрограммного управления, вход синхронизации блока микропрограммного управления соединен с входом первого элемента задержки и с первыми входами первого, второго и третьего элементов И, вход признака записи микропрограмм блока микропрограммного управления соеди- нен с первым входом четвертого элемента И, вторым инверсным входом первого элемента И, входом второго элемента задержки и вторым входом второго элемента И, выход которого соединен с входом записи блока памяти микрокоманд, и счетным входом счетчика адреса, вход запуска блока микропрограммного управления соединен с первым управляющим входом коммутатора и вторым входом третьего элемента И, выход которого соединен с входом считывания блока памяти микрокоманд, вход начальной установки блока никропрограммного управления соединен с третьим входом первого

2112

граммного управления соединен с вторым входом четвертого элемента И, выход которого соединен с входом установки в 1 первого триггера управления, первым входом второго элемента ИЛИ, вход признака завершения записи микропрограммы блока микропрограммного управления соединен с прямым входом шестого элемента И, вькод которого соединен с входом синхронизации счетчика адреса, вход разрешения выбора режима работы блока микропрограммного управления соединен с перв ым входом седьмого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, вход признака вьтолнения второй микропрограммы блока микропрограммного управления соединен с информационным входом второго триггера управления, выход первого триггера управ10

98122

ления соединен с первым входом восьмого элемента И и вторым входом седьмого элемента И, выход второго элемента ИЛИ соединен с входом син- хронизации второго триггера управления, выход которого соединен с вторым входом восьмого элемента И, выход восьмого элемента И соединен с BTOpbiM управляющим входом коммутатора, выход второго элемента задержки соединен с третьим управляющим входом коммутатора и с вторым входом пятог элемента И, выход которого соединен с входом установки в О счетчика t5 адреса, четвертый выход блока памяти микрокоманд является выходом конца работы микропрограмм нижнего уровня блока микропрограммного управления и соединен с входами установки в О второго регистра адреса, первого и второго триггеров управления

20

Фttг.2

61

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1168936A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1278847A1 |

| Устройство для управления и обмена данными | 1986 |

|

SU1319042A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве управляющей подсистемы в системах управления сбсфом и обработкой информации. Цель изобретения - повьшение быстродействия системы. Устройство содержит блок памяти микрокоманд, блок памяти микропрограмм, с первого по N-й блоки микропрограммного управления (N - число параллельно управляемых объектов), блок формирования адреса микрокоманд, блок синхронизации, два регистра адреса, регистр микрокоманд, регистр управления записью, регистр управления запуском, регистр блокирования, счетчик признаков, мультиплексор, блок дешифраторов, блок элементов ИЛИ, два блока элементов И, восемь этгементов И, элемент Ш1И-НЕ, два элемента ИЛИ, од- новибратор. Введение счетчика признаков, трех элементов ИЛИ, восьми элементов И, одновибратора приводит к достижениям цели. 10 ил. (Л

Фиг. if

Фил. 5

;, Асп /iyМОJO

U I I

Acn JJy Ана. Mjan. м}... . вл О О

-- 1 . f

МЛУ

.J . .-/ 4

в , сл Ана.М апм1апМ1А...м мМзп1 6л , .

1 -««Шв.

Ы М/7«//V-tf М/7У

,, Л//ГЛ/ АС

г Ii1 (

я Асп ЛУ МОИк

О I11I . I

Фи&б

Фи&.7

Б л offupoSxa (ИЛИ- не })

и

12

55 55.Н Я.1 5SH

ЧЧ 5

умпг

41}

ItlN

Редактор Н.Рогулич

Составитель А.Афанасьев

Техред И.Попович Корректор С.Черни

272/48

Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Микропрограммное устройство управления | 1979 |

|

SU905818A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-23—Публикация

1985-06-10—Подача