информационные шины 1-3, четыре настроечные шины 4-7, две шины 8 и 9 питания, три элемента НЕ 10-12, два элемента 2-2И-ЗИЛИ 13 и 14, элемент 2-2И-2ИЛИ 15, элемент 2-ЗИ-2ИЛИ 18, два элемента ИЛИ 16 и 17, одну выходную тину 19. При подаче на информационные шины двоичных переменных Х,

Х, Х на настроечные шины - сигналы настройки, принадлежащие множеству на выходной шине реализуется некоторая симметрическая булевая функция трех переменных (7,, X

1 лг

Х3), определяемая вектором настройки

П (F )(П 1 табл

о

П

П., ГЦ)о 1

ил,

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический модуль | 1991 |

|

SU1793542A1 |

| Многофункциональный логический модуль | 1990 |

|

SU1753589A1 |

| Многофункциональный логический модуль | 1990 |

|

SU1732462A1 |

| Многовходовый логический модуль | 1990 |

|

SU1793547A1 |

| Мультиплексор | 1990 |

|

SU1774491A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1676093A1 |

| Мультиплексор | 1990 |

|

SU1780185A1 |

| Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ | 1991 |

|

SU1811002A1 |

| Мультиплексор | 1988 |

|

SU1538248A1 |

| Многофункциональный логический модуль | 1985 |

|

SU1274148A1 |

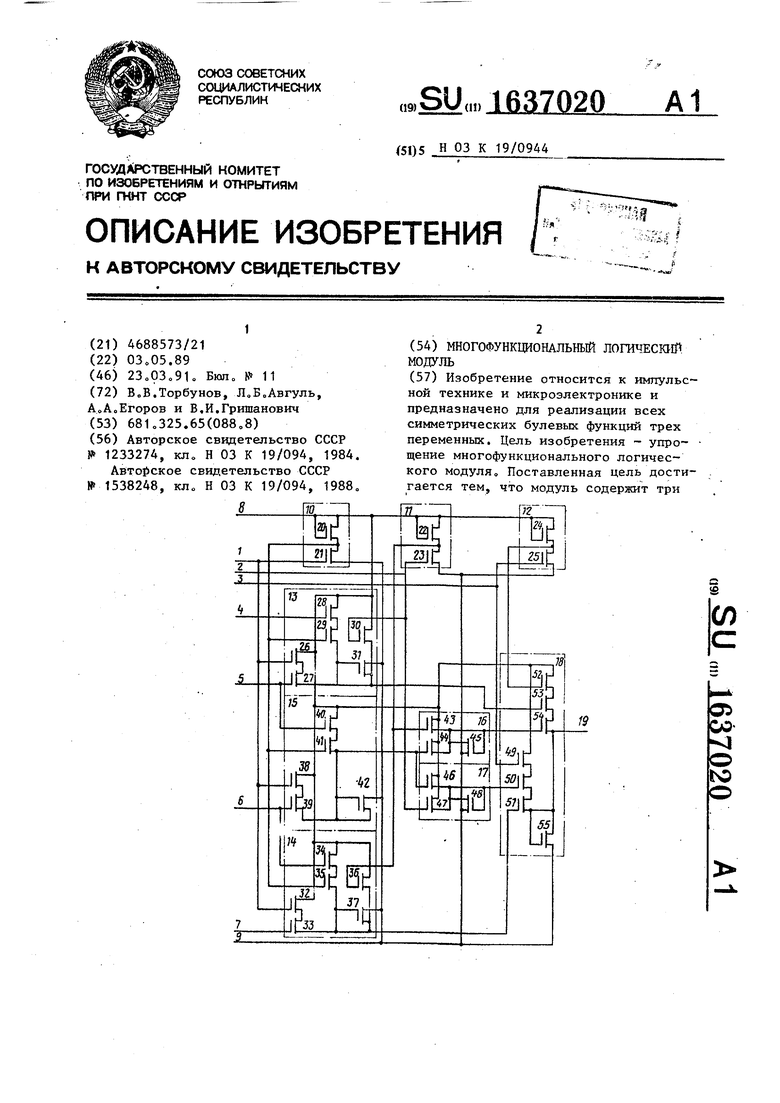

Изобретение относится к импульсной технике и микроэлектронике и предназначено для реализации всех симметрических булевых функций трех переменных. Цель изобретения упрощение многофункционального логического модуля. Поставленная цель достигается тем, что модуль содержит три (Л о со-

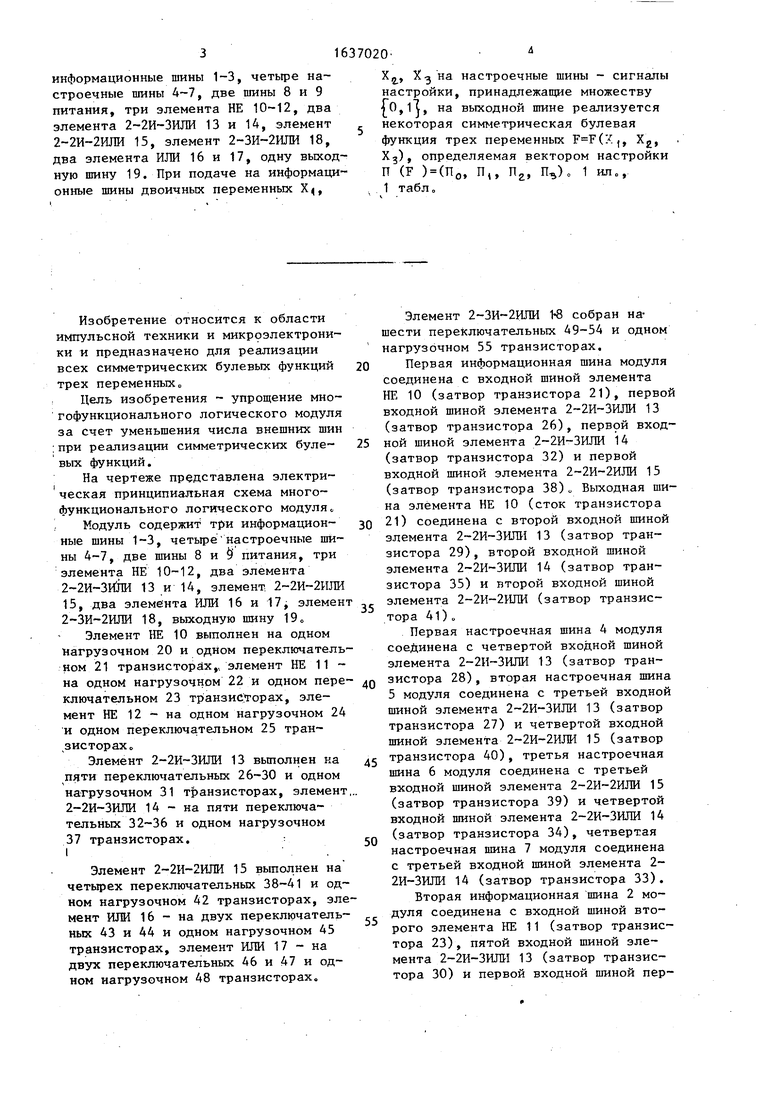

Изобретение относится к области импульсной техники и микроэлектроники и предназначено для реализации всех симметрических булевых функций трех переменных„

Цель изобретения - упрощение многофункционального логического модуля за счет уменьшения числа внешних шин при реализации симметрических буле- вых функций.

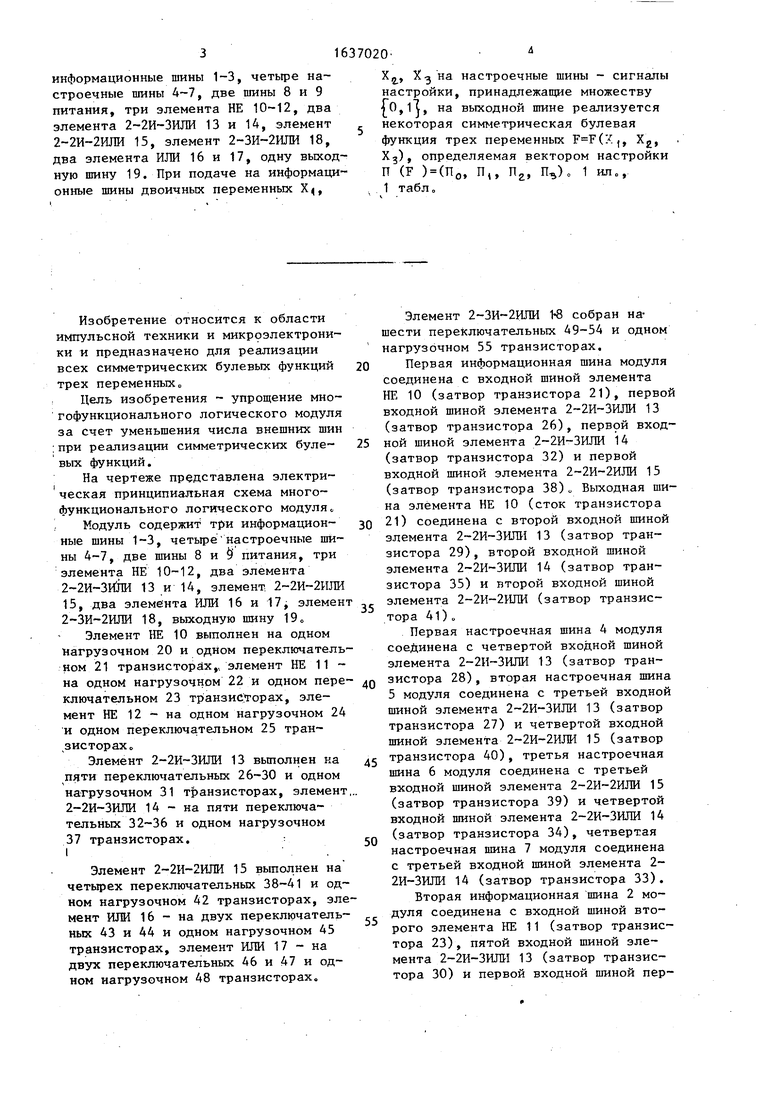

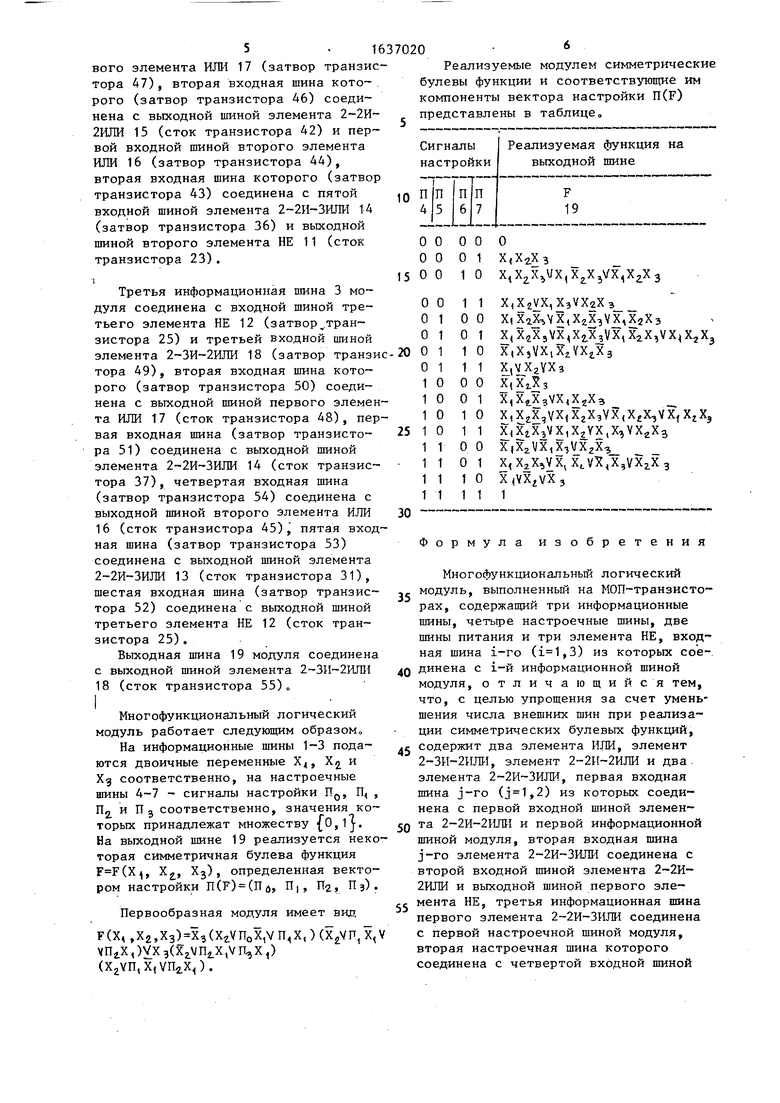

На чертеже представлена электрическая принципиальная схема многофункционального логического модуля,,

Модуль содержит три информацией- ные шины 1-3, четыре настроечные шины 4-7, две шины 8 и 9 питания, три элемента НЕ 10-12, два элемента 2-2И-ЗИЛИ 13 и 14, элемент 2-2И-2ИЛИ 15, два элемента ИЛИ 16 и 17, элемен 2-ЗИ-2ИЛИ 18, выходную шину 19„

Элемент НЕ 10 выполнен на одном нагрузочном 20 и одном переключательном 21 транзисторах,, элемент НЕ 11 - на одном нагрузочном 22 и одном переключательном 23 транзисторах, элемент НЕ 12 - на одном нагрузочном 24 и одном переключательном 25 тран- чзис торах

Элемент 2-2И-ЗИЛИ 13 выполнен ка пяти переключательных 26-30 и одном нагрузочном 31 транзисторах, элемент 2-2И-ЗИЛИ 14 на пяти переключательных 32-36 и одном нагрузочном 37 транзисторах.

I

Элемент 2-2И-2ИЛИ 15 выполнен на четырех переключательных 38-41 и одном нагрузочном 42 транзисторах, элемент ИЛИ 16 - на двух переключательных 43 и 44 и одном нагрузочном 45 транзисторах, элемент ИЛИ 17 - на двух переключательных 46 и 47 и одном нагрузочном 48 транзисторах.

0 ,

0

5

0

5

Элемент 2-ЗИ-2ИЛИ 1-8 собран нашести переключательных 49-54 и одном нагрузочном 55 транзисторах.

Первая информационная шина модуля соединена с входной шиной элемента НЕ 10 (затвор транзистора 21), первой входной шиной элемента 2-2И-ЗИЛИ 13 (затвор транзистора 26), первой входной шиной элемента 2-2И-ЗИЛИ 14 (затвор транзистора 32) и первой входной шиной элемента 2-2И-2ИЛИ 15 (затвор транзистора 38)„ Выходная шина элемента НЕ 10 (сток транзистора 21) соединена с второй входной шиной элемента 2-2И-ЗИЛИ 13 (затвор транзистора 29), второй входной шиной элемента 2-2И-ЗИЛИ 14 (затвор транзистора 35) и второй входной шиной элемента 2-2И-2ИЛИ (затвор транзистора 41) „

Первая настроечная шина 4 модуля соединена с четвертой входной шиной элемента 2-2И-ЗИЛИ 13 (затвор транзистора 28), вторая настроечная шина 5 модуля соединена с третьей входной шиной элемента 13 (затвор транзистора 27) и четвертой входной шиной элемента 2-2И-2ИЛИ 15 (затвор транзистора 40), третья настроечная шина 6 модуля соединена с третьей входной шиной элемента 2-2И-2ИЛИ 15 (затвор транзистора 39) и четвертой входной шиной элемента 2-2И-ЗИЛИ 14 (затвор транзистора 34), четвертая настроечная шина 7 модуля соединена с третьей входной шиной элемента 2- 2И-ЗИЛИ 14 (затвор транзистора 33). Вторая информационная шина 2 модуля соединена с входной шиной второго элемента НЕ 11 (затвор транзистора 23), пятой входной шиной элемента 2-2И-ЗИЛИ 13 (затвор транзистора 30) и первой входной шиной пер

5 - 1 вого элемента ИЛИ 17 (затвор транзистора 47), вторая входная шина которого (затвор транзистора 46) соединена с выходной шиной элемента 2-2И- 2ИЛИ 15 (сток транзистора 42) и первой входной шиной второго элемента ИЛИ 16 (затвор транзистора 44), вторая входная шина которого (затвор транзистора 43) соединена с пятой входной шиной элемента 2-2И-ЗИЛИ 14 (затвор транзистора 36) и выходной шиной второго элемента НЕ 11 (сток транзистора 23).

1

Третья информационная шина 3 модуля соединена с входной шиной третьего элемента НЕ 12 (затвор,транзистора 25) и третьей входной шиной элемента 2-ЗИ-2ИЛИ 18 (затвор транзи тора 49), вторая входная шина которого (затвор транзистора 50) соединена с выходной шиной первого элемента ИЛИ 17 (сток транзистора 48), первая входная шина (затвор транзисто- ра 51) соединена с выходной шиной элемента 2-2И-ЗИЛИ 14 (сток транзистора 37), четвертая входная шина (затвор транзистора 54) соединена с выходной шиной второго элемента ИЛИ 16 (сток транзистора 45), пятая входная шина (затвор транзистора 53) соединена с выходной шиной элемента 2-2И-ЗИЛИ 13 (сток транзистора 31), шестая входная шина (затвор транзистора 52) соединена с выходной шиной третьего элемента НЕ 12 (сток транзистора 25).

Выходная шина 19 модуля соединена с выходной шиной элемента 2-ЗИ-2ИЛИ 18 (сток транзистора 55)„

Многофункциональный логический модуль работает следующим образом

На информационные шины 1-3 подаются двоичные переменные Х4, Х и Хд соответственно, на настроечные шины 4-7 - сигналы настройки П0, П , П0 и Пя соответственно, значения коГ 1

торых принадлежат множеству {0,1j. На выходной шине 19 реализуется некоторая симметричная булева функция (X, Х, Х3) , определенная вектором настройки П(Р) (Пй, П|, ГТ2, П з) .

Первообразная модуля имеет вид F(X, ,X2,X3bX,(XiVn0X,Vn,X,)(XiVniX,V

vnix,)Vx3(Xj,vnix,VE,x1) (xzvn,x,vn4x).

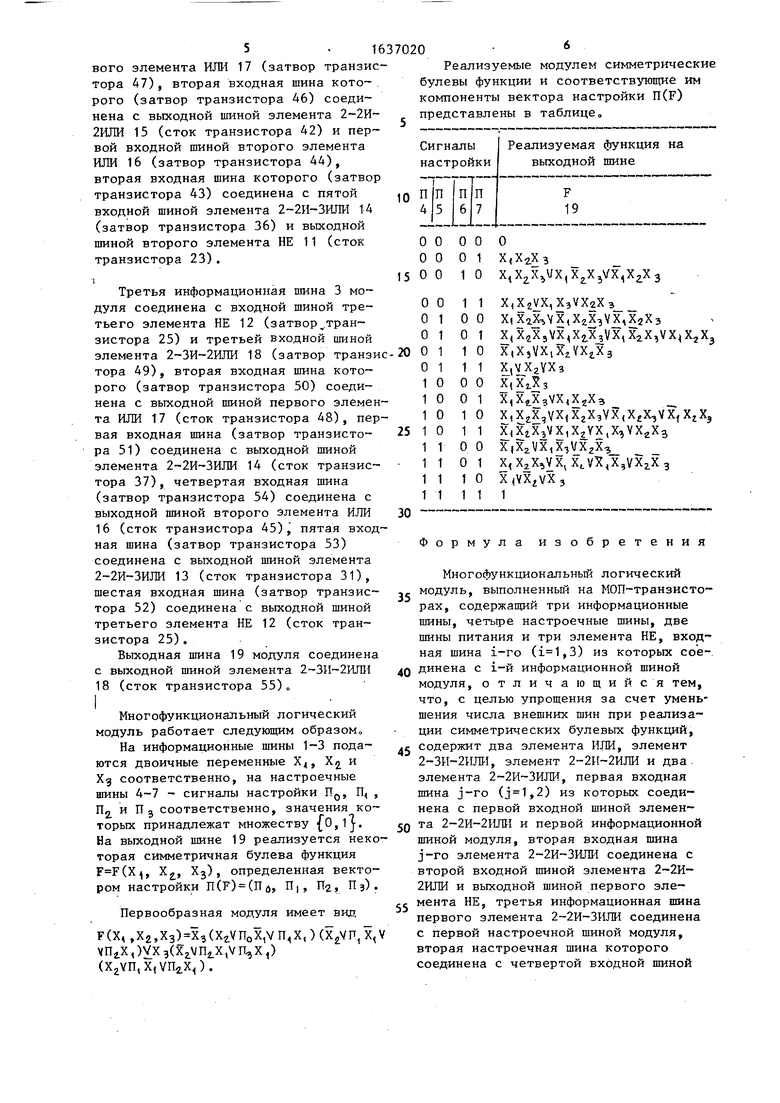

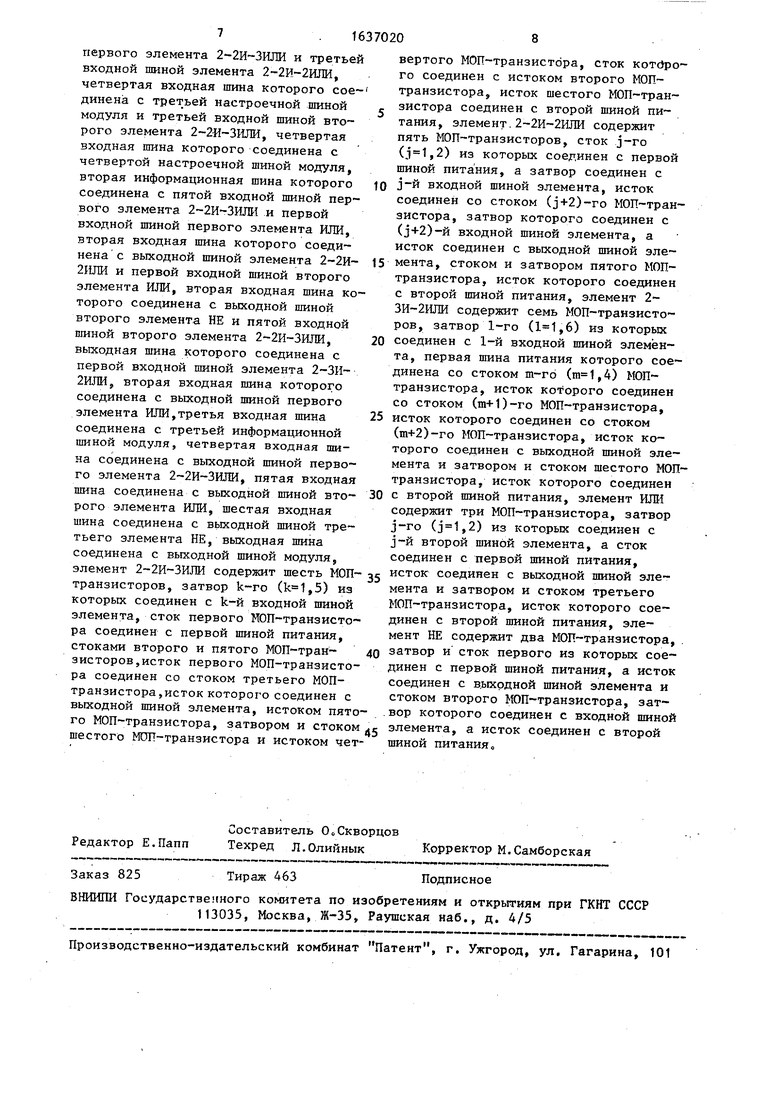

Реализуемые модулем симметрические булевы функции и соответствующие им компоненты вектора настройки П(Р) представлены в таблице

10

702

Формула изобретения

Многофункциональный логический модуль, выполненный на МОП-транзисторах, содержащий три информационные шины, четыре настроечные шины, две шины питания и три элемента НЕ, вход ная шина 1-го (,3) из которых соединена с i-й информационной шиной модуля, отличающийся тем, что, с целью упрощения за счет уменьшения числа внешних шин при реализации симметрических булевых функций,

содержит два элемента ИЛИ, элемент 2-ЗИ-2ИЛИ, элемент 2-2И-2ИЛИ и два элемента 2-2И-ЗИЛИ, первая входная шина j-го (,2) из которых соединена с первой входной шиной элемен-

та 2-2И-2ИЛИ и первой информационной шиной модуля, вторая входная шина j-ro элемента 2-2И-ЗИЛИ соединена с второй входной шиной элемента 2-2И- 2ИЛИ и выходной шиной первого элеента НЕ, третья информационная шина ервого элемента 2-2И-ЗИЛИ соединена первой настроечной шиной модуля, торая настроечная шина которого оединена с четвертой входной шиной

первого элемента 2-2И-ЗИЛИ и третьей входной шиной элемента 2-2И-2ИЛИ, четвертая входная шина которого сое- динена с третьей настроечной шиной модуля и третьей входной шиной второго элемента 2-2И-ЗИЛИ, четвертая входная шина которого соединена с четвертой настроечной шиной модуля, вторая информационная шина которого соединена с пятой входной шиной первого элемента и первой входной шиной первого элемента ИЛИ, вторая входная шина которого соединена с выходной шиной элемента 2-2И- 2ИЛИ и первой входной шиной второго элемента ИЛИ, вторая входная шина которого соединена с выходной шиной второго элемента НЕ и пятой входной шиной второго элемента 2-2И-ЗИЛИ, выходная шина которого соединена с первой входной шиной элемента 2-ЗИ- 2ИЛИ, вторая входная шина которого соединена с выходной шиной первого элемента ИЛИ,третья входная шина соединена с третьей информационной шиной модуля, четвертая входная шина соединена с выходной шиной первого элемента 2-2И-ЗИЛИ, пятая входная шина соединена с выходной шиной второго элемента ИЛИ, шестая входная шина соединена с выходной шиной третьего элемента НЕ, выходная шина соединена с выходной шиной модуля,

вертого МОП-транзистора, сток котдро- го соединен с истоком второго МОП- транзистора, исток шестого МОП-транзистора соединен с второй шиной питания, элемент.2-2И-2ИЛИ содержит пять МОП-транзисторов, сток j-ro (,2) из которых соединен с первой шиной питания, а затвор соединен с

10 j-й входной шиной элемента, исток

соединен со стоком (j+2)-ro МОП-транзистора, затвор которого соединен с (j+2)-u входной шиной элемента, а исток соединен с выходной шиной эле15 мента, стоком и затвором пятого МОП- транзистора, исток которого соединен с второй шиной питания, элемент 2- ЗИ-2ИЛИ содержит семь МОП-транзисторов, затвор 1-го (,6) из которых

20 соединен с 1-й входной шиной элемента, первая шина питания которого соединена со стоком m-ro (,4) МОП- транзистора, исток которого соединен со стоком (т+1)-го МОП-транзистора,

25 исток которого соединен со стоком (т+2)-го МОП-транзистора, исток которого соединен с выходной шиной элемента и затвором и стоком шестого МОП транзистора, исток которого соединен

30 с второй шиной питания, элемент ИЛИ содержит три МОП-транзистора, затвор j-го (,2) из которых соединен с j-й второй шиной элемента, а сток соединен с первой шиной питания,

элемент 2-2И-ЗИЛИ содержит шесть МОП- 35 исток соединен с выходной шиной эле- транзисторов, затвор k-го (,5) из мента и затвором и стоком третьего которых соединен с k-й входной шиной

МОП-транзистора, исток которого соединен с второй шиной питания, элемент НЕ содержит два МОП-транзистора затвор и сток первого из которых соединен с первой шиной питания, а исток соединен с выходной шиной элемента и стоком второго МОП-транзистора, затвор которого соединен с входной шиной

элемента, сток первого МОП транзисто ра соединен с первой шиной питания, стоками второго и пятого МОП-тран- зисторов,исток первого МОП-транзистора соединен со стоком третьего МОП- транзистора,исток которого соединен с

МОП-транзистора, исток которого соединен с второй шиной питания, элемент НЕ содержит два МОП-транзистора затвор и сток первого из которых сое динен с первой шиной питания, а исто соединен с выходной шиной элемента и стоком второго МОП-транзистора, затвор которого соединен с входной шино

выходной шиной элемента, истоком пятого МОП-транзистора, затвором и стоком лг элемента, а исток соединен с второй шестого МОП-транзистора и истоком чет- шиной питания

Редактор Е.Папп

Составитель О, Скворцов Техред Л.Олийнык

Заказ 825

Тираж 463

ВНИИПИ Государстве.чного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

вертого МОП-транзистора, сток котдро- го соединен с истоком второго МОП- транзистора, исток шестого МОП-транзистора соединен с второй шиной питания, элемент.2-2И-2ИЛИ содержит пять МОП-транзисторов, сток j-ro (,2) из которых соединен с первой шиной питания, а затвор соединен с

j-й входной шиной элемента, исток

соединен со стоком (j+2)-ro МОП-транзистора, затвор которого соединен с (j+2)-u входной шиной элемента, а исток соединен с выходной шиной элемента, стоком и затвором пятого МОП- транзистора, исток которого соединен с второй шиной питания, элемент 2- ЗИ-2ИЛИ содержит семь МОП-транзисторов, затвор 1-го (,6) из которых

0 соединен с 1-й входной шиной элемента, первая шина питания которого соединена со стоком m-ro (,4) МОП- транзистора, исток которого соединен со стоком (т+1)-го МОП-транзистора,

5 исток которого соединен со стоком (т+2)-го МОП-транзистора, исток которого соединен с выходной шиной элемента и затвором и стоком шестого МОП- транзистора, исток которого соединен

0 с второй шиной питания, элемент ИЛИ содержит три МОП-транзистора, затвор j-го (,2) из которых соединен с j-й второй шиной элемента, а сток соединен с первой шиной питания,

исток соединен с выходной шиной эле- мента и затвором и стоком третьего

МОП-транзистора, исток которого соединен с второй шиной питания, элемент НЕ содержит два МОП-транзистора, затвор и сток первого из которых соединен с первой шиной питания, а исток соединен с выходной шиной элемента и стоком второго МОП-транзистора, затвор которого соединен с входной шиной

элемента, а исток соединен с второй шиной питания

Корректор М.Самборская

Подписное

| Программируемый логический модуль | 1984 |

|

SU1233274A1 |

| Мультиплексор | 1988 |

|

SU1538248A1 |

Авторы

Даты

1991-03-23—Публикация

1989-05-03—Подача