Изобретение относится к микроэлек- тропике и импульсной технике и предназначено для реализации симметрически булевых функций (с,б.ф.)п переменных.

Цель изобретения - повышение быстродействия многофункционального логиче- ского модуля.

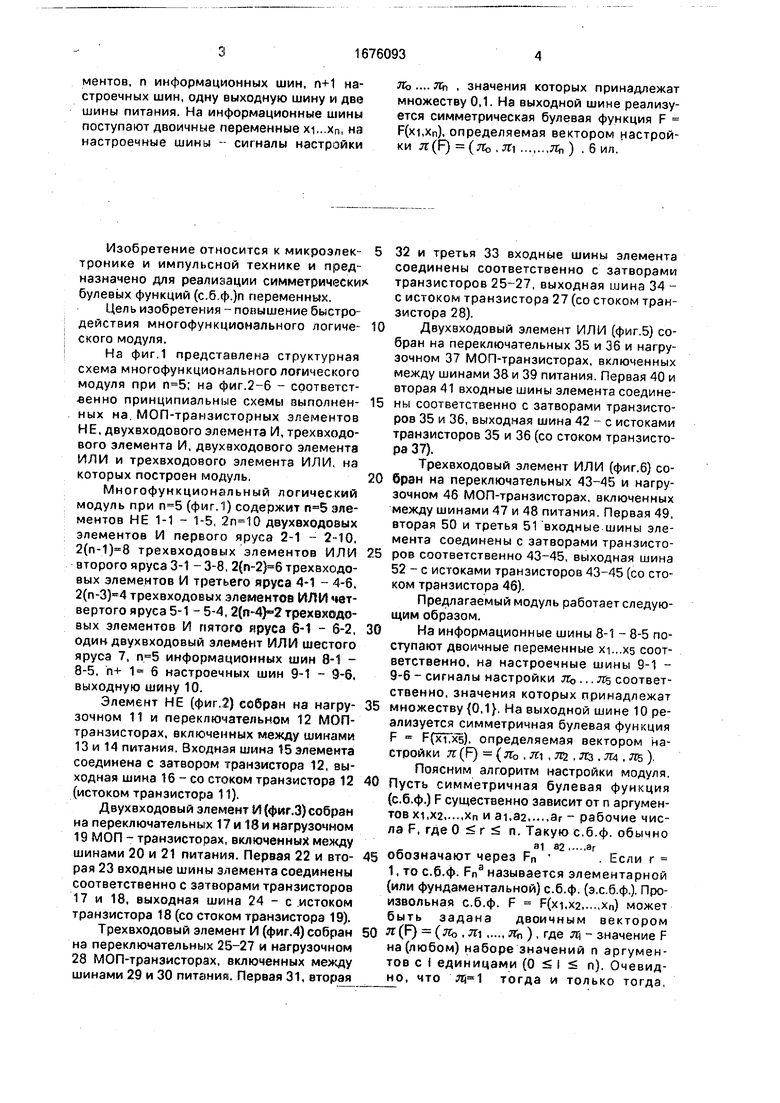

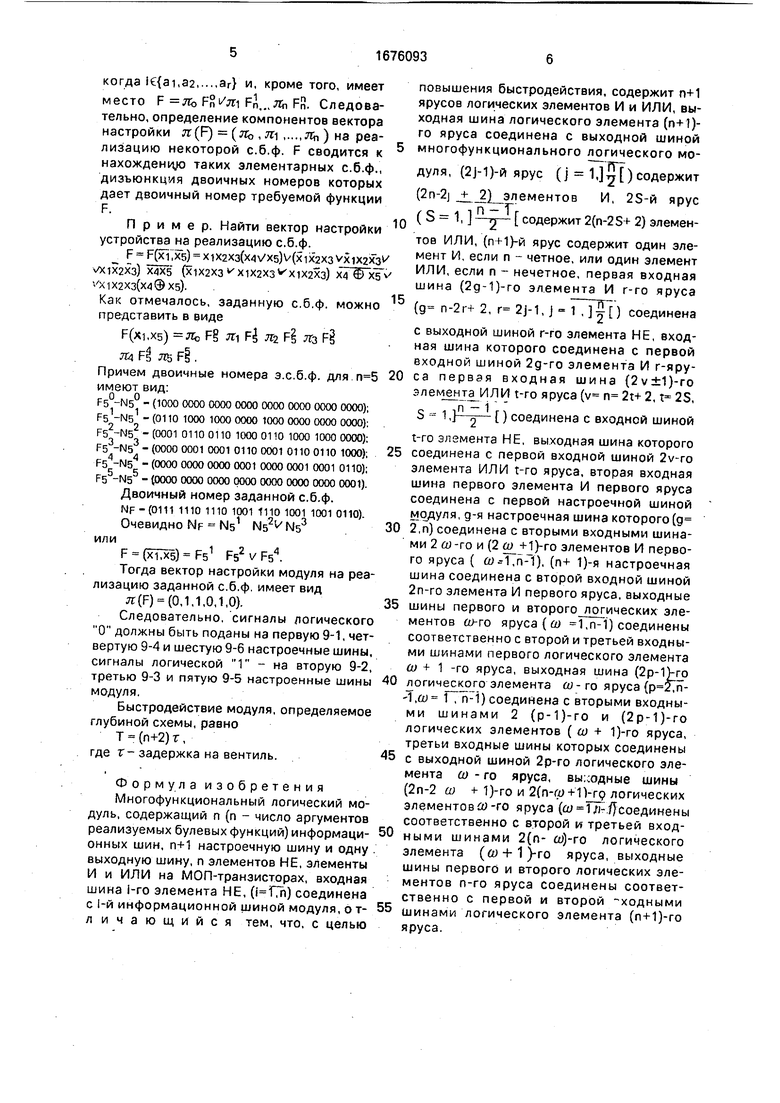

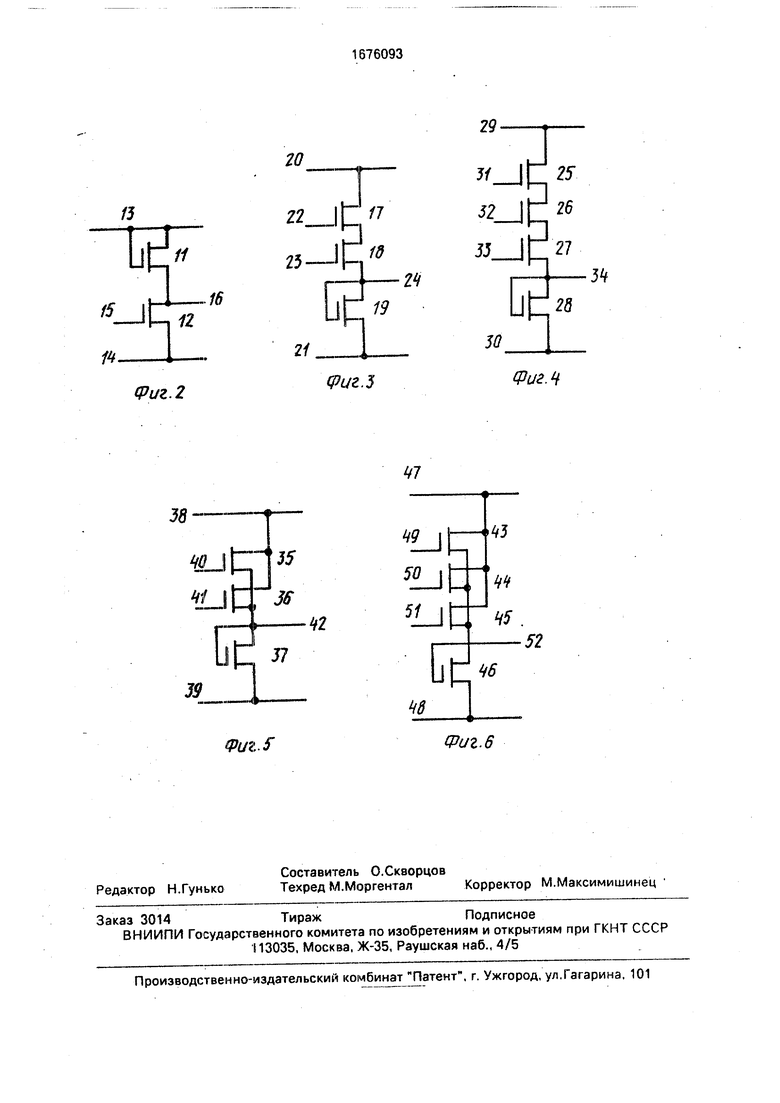

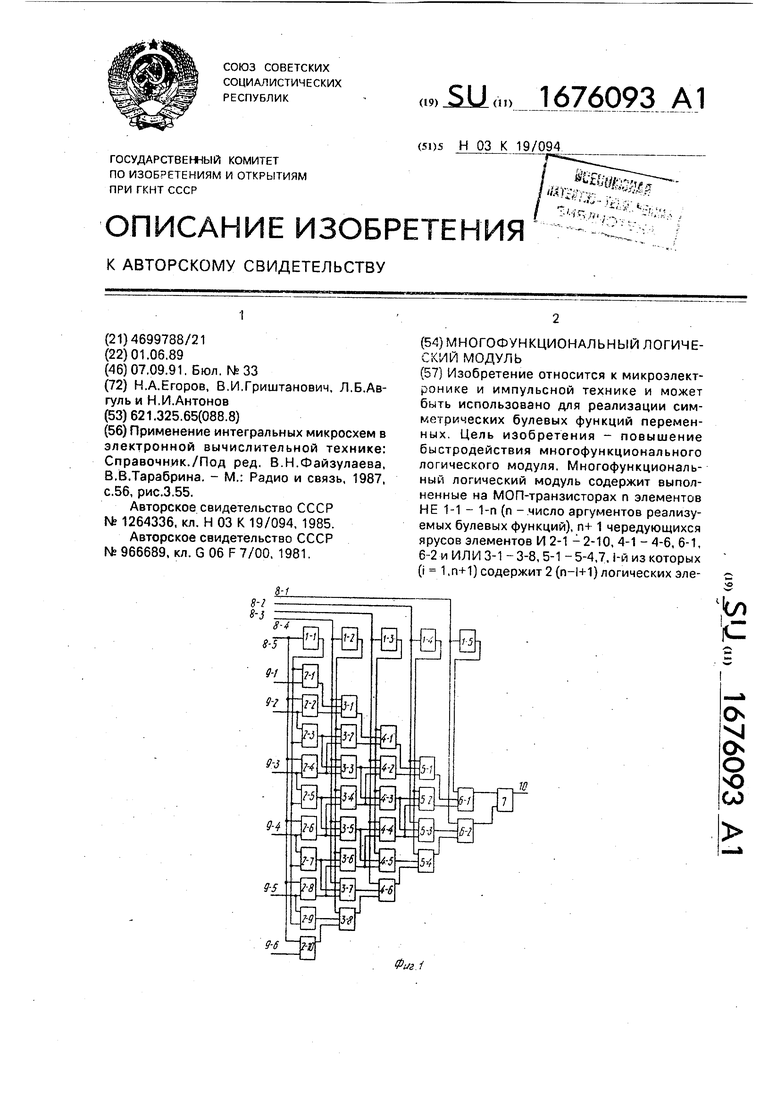

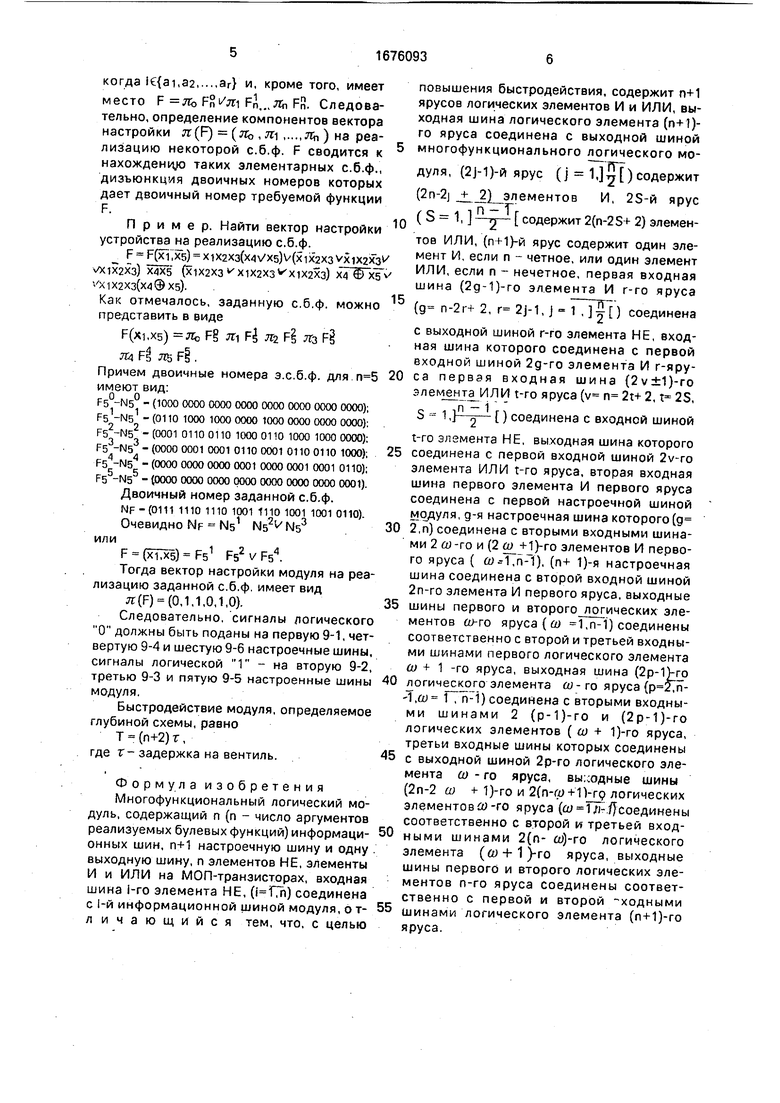

На фиг.1 представлена структурная схема многофункционального логического модуля при на фиг.2-6 - соответственно принципиальные схемы выполнен- ных на МОП-транзисторных элементов НЕ, двухвходового элемента И, трехвходо- вого элемента И, двухвходового элемента ИЛИ и трехвходового элемента ИЛИ, на которых построен модуль.

Многофункциональный логический модуль при (фиг.1) содержит элементов НЕ 1-1 - 1-5, двухвходовых элементов И первого яруса 2-1 - 2-10, 2(п-1)8 трехвходовых элементов ИЛИ второго яруса 3-1 - 3-8, 2(п-2)6 трехвходовых элементов И третьего яруса 4-1 - 4-6, 2( трехвходовых элементов ИЛИ четвертого яруса 5-1 - 5-4,2(п-4)2 трехвходовых элементов И пятого яруса 6-t - 6-2, один двухвходовый элемент ИЛИ шестого яруса 7, информационных шин 8-1 - 8-5, п+ 1 6 настроечных шин 9-1 - 9-6. выходную шину 10.

Элемент НЕ (фиг.2) собран на нагру- зочном 11 и переключательном 12 МОП- транзисторах, включенных между шинами 13 и 14 питания. Входная шина 15 элемента соединена с затвором транзистора 12, выходная шина 16 - со стоком транзистора 12 (истоком транзистора 11).

Двухвходовый элемент И (фиг.З)собран на переключательных 17 и 18 и нагрузочном 19 МОП - транзисторах, включенных между шинами 20 и 21 питания. Первая 22 и вто- рая 23 входные шины элемента соединены соответственно с затворами транзисторов 17 и 18, выходная шина 24 - с истоком транзистора 18 (со стоком транзистора 19).

Трехвходовый элемент И (фиг.4) собран на переключательных 25-27 и нагрузочном 28 МОП-транзисторах, включенных между шинами 29 и 30 питания. Первая 31, вторая

32 и третья 33 входные шины элемента соединены соответственно с затворами транзисторов 25-27, выходная шина 34 - с истоком транзистора 27 (со стоком транзистора 28).

Двухвходовый элемент ИЛИ (фиг.5) собран на переключательных 35 и 36 и нагрузочном 37 МОП-транзисторах, включенных между шинами 38 и 39 питания. Первая 40 и вторая 41 входные шины элемента соединены соответственно с затворами транзисторов 35 и 36, выходная шина 42 - с истоками транзисторов 35 и 36 (со стоком транзистора 37).

Трехвходовый элемент ИЛИ (фиг.6) собран на переключательных 43-45 и нагрузочном 46 МОП-транзисторах, включенных между шинами 47 и 48 питания. Первая 49, вторая 50 и третья 51 входные шины элемента соединены с затворами транзисторов соответственно 43-45, выходная шина 52 - с истоками транзисторов 43-45 (со стоком транзистора 46).

Предлагаемый модуль работает следующим образом.

На информационные шины 8-1 - 8-5 поступают двоичные переменные xi...xs соответственно, на настроечные шины 9-1 - 9-6 - сигналы настройки ль ... лЈ соответственно, значения которых принадлежат множеству {0,1}. На выходной шине 10 реализуется симметричная булевая функция F F(xi,X5), определяемая вектором настройки П (F) ( ЛЬ , Л1 , Л2 , ЛЗ , ПА , Л5 ).

Поясним алгоритм настройки модуля. Пусть симметричная булевая функция (с.б.ф.) F существенно зависит от п аргументов xi,X2,...,Xn и ai,32Эг - рабочие числа F, где 0 г п. Такую с.б.ф. обычно

31 82аг

обозначают через Fn . Если г 1. то с.б.ф. Fna называется элементарной (или фундаментальной) с.б.ф. (э.с.б.ф,). Произвольная с.б.ф. F F(xi,X2xn) может

быть задана двоичным вектором

Л (г-) (ль , ), где Л) - значение F

на (любом) наборе значений п аргументов с I единицами (О Ј п). Очевидно, что Л)1 тогда и только тогда,

когда K{ai,a2аг} и, кроме того, имеет

место F лъ Fn... ль Fn. Следовательно, определение компонентов вектора настройки л(Р) (лъ , ) на реализацию некоторой с.б.ф. F сводится к нахождение таких элементарных с.б.ф., дизъюнкция двоичных номеров которых дает двоичный номер требуемой функции F.

Пример. Найти вектор настройки устройства на реализацию с.б.ф.

F F(xl,) X1X2X3(X4VX5)V(X1X2X3 ШхЬ vO 1Х2ХЗ) Х4Х5 (X1Х2ХЗ v X1Х2ХЗ w X1 Х2Хз) Х4 Ф $ V X1X2X3(X4@X5).

Как отмечалось, заданную с.б.ф, можно представить в виде

F(xi,xs) Лс F§ Л1 F Л2 FЈ лз F§

Я4 Fg Л5 Fg .

Причем двоичные номера э.с.б.ф. для имеют вид:

F5°-N5° - (1000 0000 0000 0000 0000 0000 0000 0000); F51-N51 -(0110 1000 10000000 1000000000000000), F52-N52 - (0001 0110 0110 10000110 1000 1000 0000): F53-N53 - (0000 0001 0001 01100001 01100110 1000); F54-N54 - (0000 0000 0000 0001 0000 0001 0001 0110); F55-N55 - (0000 0000 0000 0000 0000 0000 0000 0001).

Двоичный номер заданной с.б.ф.

NF -(01111110 1110 1001 fno 1001 1001 0110).

Очевидно NF Ns1 N52(/N53 или

F (xTx5) F51 F52VF54.

Тогда вектор настройки модуля на реализацию заданной с.б.ф. имеет вид л (F) (0,1,1,0,1,0).

Следовательно, сигналы логического О должны быть поданы на первую 9-1, четвертую 9-4 и шестую 9-6 настроечные шины, сигналы логической 1 - на вторую 9-2, третью 9-3 и пятую 9-5 настроенные шины модуля.

Быстродействие модуля, определяемое глубиной схемы, равно

Т - (п+2) т, где г-задержка на вентиль.

Формула изобретения Многофункциональный логический модуль, содержащий п (п - число аргументов реализуемых булевых функций) информаци- онных шин, п+1 настроечную шину и одну выходную шину, п элементов НЕ, элементы И и ИЛИ на МОП-транзисторах, входная шина 1-го элемента НЕ, () соединена с 1-й информационной шиной модуля, о т- личающийся тем, что, с целью

0

5

0

5

0

5

0

5

0 5

повышения быстродействия, содержит п+1 ярусов логических элементов И и ИЛИ, выходная шина логического элемента (п+1)- го яруса соединена с выходной шиной многофункционального логического модуля, (2Н)-й ярус ( IJ-jDсодержит (2n-2j ±.2 элементов И, 25-й ярус ( S 1, -п- содержит 2(n-2S + 2) элементов ИЛИ, (пМ)-й ярус содержит один элемент И, если п - четное, или один элемент ИЛИ, если п - нечетное, первая входная шина (2д-1)-го элемента И r-го яруса

(д п-2г+ 2, r 2j-1, j 1 ,«) соединена

с выходной шиной r-го элемента НЕ, входная шина которого соединена с первой входной шиной 2д-го элемента И г-яру- са первая входная шина (2v±1)-ro элементами Л И t-ro яруса (v n 2t+ 2, t 2S.

S - 1,-s- ) соединена с входной шиной

t-ro элемента НЕ, выходная шина которого соединена с первой входной шиной 2v-ro элемента ИЛИ t-ro яруса, вторая входная шина первого элемента И первого яруса соединена с первой настроечной шиной модуля, g-я настроечная шина которого (д 2,п) соединена с вторыми входными шинами 2 ш-го и (2 )-ro элементов И первого яруса ( ,), (п+ 1)-я настроечная шина соединена с второй входной шиной 2п-го элемента И первого яруса, выходные шины первого и второго логических элементов со-ro яруса ( ш 1,п-1) соединены соответственно с второй и третьей входными шинами первого логического элемента а + 1 -го яруса, выходная шина (2p-lWp логического элемента (У- го яруса ( -1,со 1 , п-i) соединена с вторыми входными шинами 2 (р-1)-го и (2р-1)-го логических элементов ( ш + 1)-го яруса, третьи входные шины которых соединены с выходной шиной 2р-го логического элемента ш - го яруса, выгодные шины (2n-2 w + 1)-го и 2(n-ft)+1Vro логических элементов а) -го яруса (# 17|-/}соединены соответственно с второй и третьей входными шинами 2Јn- cd)-ro логического элемента ()-го яруса, выходные шины первого и второго логических элементов n-го яруса соединены соответственно с первой и второй ходными шинами логического элемента (п+1)-го яруса.

39

1

J7

Б

Ю

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический модуль | 1990 |

|

SU1753589A1 |

| Многофункциональный логический модуль | 1991 |

|

SU1793542A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1598161A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1637020A1 |

| Многофункциональный логический модуль | 1990 |

|

SU1732462A1 |

| Устройство для вычисления симметрических булевых функций | 1988 |

|

SU1559337A1 |

| Многофункциональный логический модуль | 1980 |

|

SU924697A1 |

| Многовходовый логический модуль | 1990 |

|

SU1793547A1 |

| Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ | 1991 |

|

SU1811002A1 |

| Устройство для вычисления симметрических булевых функций | 1990 |

|

SU1742811A1 |

Изобретение относится к микроэлектронике и импульсной технике и может быть использовано для реализации симметрических булевых функций переменных. Цель изобретения - повышение быстродействия многофункционального логического модуля. Многофункциональный логический модуль содержит выполненные на МОП-транзисторах п элементов НЕ 1-1 - 1-п (п - число аргументов реализуемых булевых функций), п+ 1 чередующихся ярусов элементов И 2-1 - 2-10, 4-1 - 4-6, 6-1, 6-2 и ИЛ И 3-1 - 3-8, 5-1 - 5-4,7,1-й из которых (I 1,п+1) содержит 2 (п-1+1) логических эле

Фиг.

Фиг. 6

| Применение интегральных микросхем в электронной вычислительной технике: Справочник./Под ред | |||

| В.Н.Файзулаева, В.В.Тарабрина | |||

| - М.: Радио и связь, 1987, с.56, рис.3.55 | |||

| Универсальный логический модуль | 1985 |

|

SU1264336A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Многофункциональный модуль | 1981 |

|

SU966689A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-09-07—Публикация

1989-06-01—Подача