т

К процессору

Изобретение относится к вычислительной технике и может быть использовано в устройствах ввода-вьтода ЭВМ, содержащих реверсируемые пери- .ферийные шины.

Цель изобретения - упрощение устройства. ,

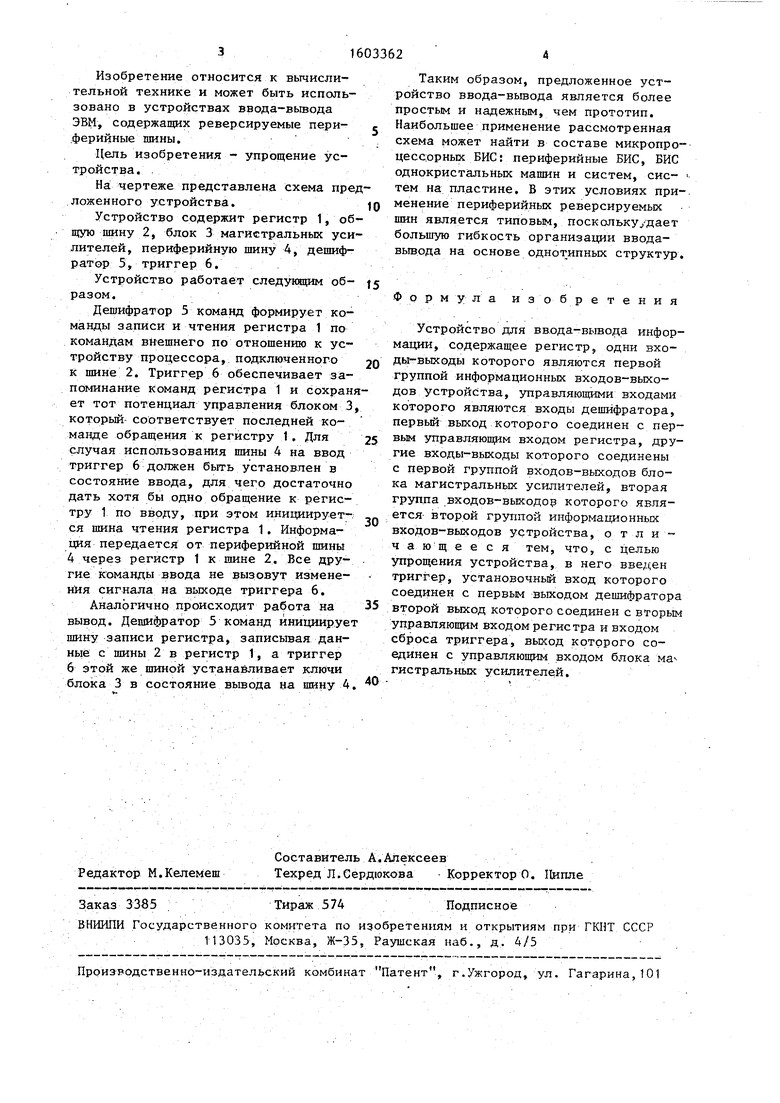

На чертеже представлена схема пред ложенного устройства.

Устройство содержит регистр 1, общую шину 2, блок 3 магистральных усилителей, периферийную шину 4, дешифратор 5, триггер 6.

Устройство работает следунхцим образом.

Дешифратор 5 команд формирует команды записи и чтения регистра 1 по командам внешнего по отношению к устройству процессора, подключенного К шине 2. Триггер 6 обеспечивает запоминание Команд регистра 1 и сохраняет тот потенциал управления блоком 3, которьй- соответствует последней ко- манде обращения к регистру 1. Для случая использования шины 4 на ввод триггер 6 должен быть установлен в состояние ввода, для чего достаточно дать хотя бы одно обращение к регистру 1 по вводу, при этом инициируется шина чтения регистра 1. Информация передается от периферийной шины 4 через регистр 1 к шине 2. Все другие команды ввода не вызовут изменения сигнала на выходе триггера 6.

Аналогично происходит работа на вывод. Дешифратор 5 команд инициирует шину записи регистра, записьшая данные с шины 2 в регистр 1, а триггер 6 этой же шиной устанайливает ключи блока 3 в состояние вывода на шину 4.

Таким образом, предложенное устройство ввода-вьшода является более простым и надежньм, чем прототип. Наибольшее применение рассмотренная схема может найти в составе микропроцессорных БИС: периферийные БИС, БИС однокристальных машин и систем, сие- - тем на пластине. В этих условиях при-, менение периферийных реверсируемых шин является типовым, поскольку/дает большую гибкость организации ввода- вывода на основе однот ипных структур.

Формула изобретения

Устройство для ввода-вывода информации, содержащее регистр, одни входы-выходы которого являются первой группой информационных входов-выходов устройства, управляющими входами которого являются входы дешифратора, первый выход которого соединен с первым управляющим входом регистра, другие входы-выходы которого соединены с первой группой входов-выходов блока магистральных усилителей, вторая группа .входов-вькодор которого явля- ется- второй группой информационных входов-выходов устройства, о т л и - ч а е ее я тем, что, с целью упрощения устройства, в него введен триггер, установочньй вход которого соединен с первым выходом дешифратора второй выход которого соединен с вторым управляющим входом регистра и входом сброса триггера, выход которого соединен с управляющим входом блока магистральных усилителей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между процессором и периферийными устройствами | 1987 |

|

SU1501078A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| Устройство для сопряжения ЭВМ с магистралью ввода-вывода периферийных устройств | 1983 |

|

SU1160426A1 |

| Устройство для сопряжения двух магистралей | 1987 |

|

SU1418728A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1501077A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1984 |

|

SU1251093A1 |

| Устройство для объема информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1679497A1 |

| СПОСОБ И УСТРОЙСТВО ОГРАНИЧЕНИЯ ДОСТУПА К ЗАПИСАННЫМ НА НОСИТЕЛЕ ЦИФРОВЫМ ДАННЫМ | 2004 |

|

RU2277720C2 |

| УСТРОЙСТВО ОГРАНИЧЕНИЯ ДОСТУПА К СЕКТОРАМ ЖЕСТКОГО ДИСКА | 2007 |

|

RU2359317C2 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1456963A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах ввода-вывода ЭВМ, содержащих двунаправленные периферийные шины. Целью изобретения является упрощение устройства. Устройство содержит регистр 1, общую шину 2, блок 3 магистральных усилителей, периферийную шину 4, дешифратор 5, триггер 6. Наибольшее применение изобретение может найти в периферийных БИС, БИС однокристальных машин и систем, систем из пластика. 1 ил.

| Микропроцессорные комплекты интегральных схем | |||

| Справочник, Массовая библиотека инженера | |||

| Электроника, вып„ 31, М, : Радио и связь, .1982, с, 61,96 | |||

| Component Data Catalog, Intel, January, 1981, p,8-85« |

Авторы

Даты

1990-10-30—Публикация

1988-04-08—Подача