О)

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1984 |

|

SU1367015A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1304027A1 |

| Устройство для формирования тестовых воздействий | 1987 |

|

SU1476473A1 |

| Устройство для регистрации местоположения подвижного объекта | 1984 |

|

SU1180943A1 |

| Устройство для регистрации движущихся транспортных средств | 1983 |

|

SU1129634A1 |

| Многоканальная время-импульсная телеизмерительная система | 1984 |

|

SU1288738A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Устройство для контроля дискретных систем | 1983 |

|

SU1117640A1 |

| Многоканальная телеизмерительная система | 1985 |

|

SU1357993A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

Изобретение относится к вычислительной технике может быть использовано при контроле сложных цифровых узлов при их изготовлении или эксплуатации и является усовершенствованием изобретения по авторскому свидетельству N 1304027. Целью изобретения является повышение достоверности контроля. С этой целью в устройство, содержащее генератор синхроимпульсов, два элемента И, генератор тестов, схему сравнения, две группы формирователей импульсов, первый элемент ИЛИ, первый элемент задержки, триггер и эталонный цифровой блок, введены группа из N селекторов задержки, где N - число выходов контролируемого цифрового блока, второй и третий элементы ИЛИ и второй элемент задержки. 1 з.п.ф-лы, 2 ил.

Изобретение относится к вьиисли- тельной технике, может быть использовано при контроле сложных цифровых узлов на стадии Изготовления и эксплуатации и является дополнительным к авт.ев. If 1304027.

Целью изобретения является повышение достоверности контроля за счет осуществления селекции и фиксирования ложных сигналов любой длителыюсти при контроле узлов с внутренним тактированием.

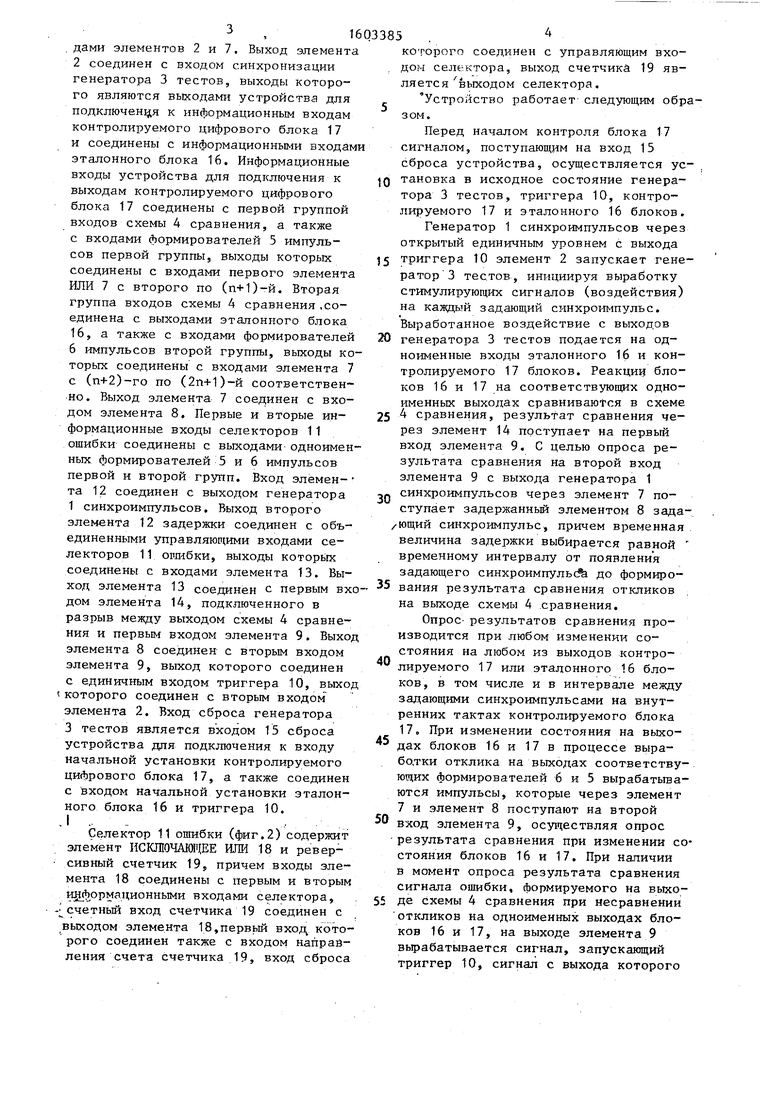

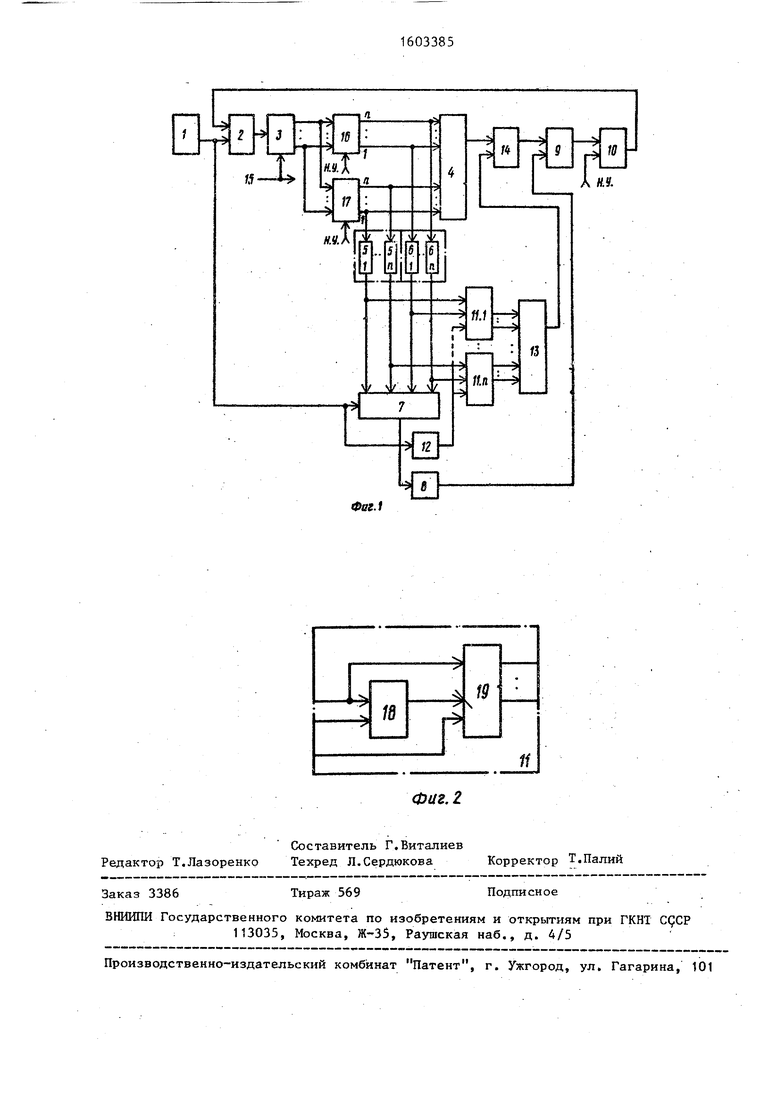

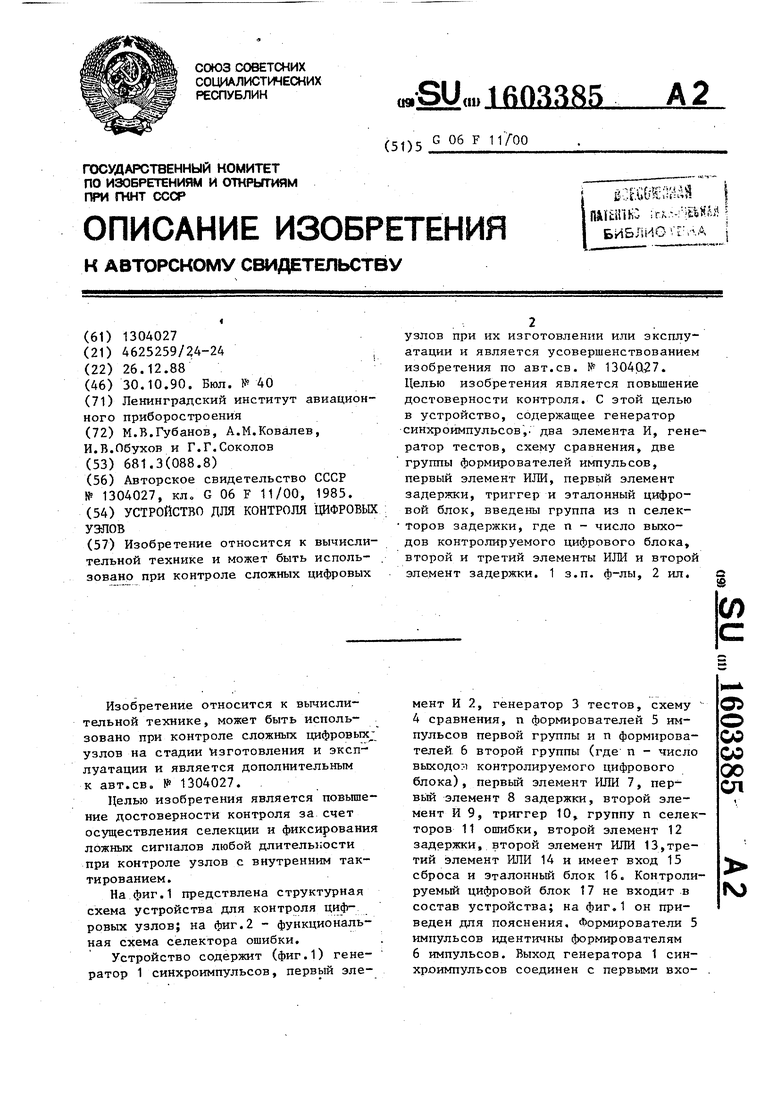

На фиг.1 предствлена структурная схема устройства для контроля цифровых узлов; на фиг.2 - функциональная схема селектора ошибки.

Устройство содержит (фиг.1) генератор 1 синхроимпульсов, первый элемент И 2, генератор 3 тестов, схему 4 сравнения, п формирователей 5 импульсов первой группы и п формирователей 6 второй группы (где п - число выходо:-) контролируемого цифрового блока), первый элемент ИЛИ 7, пер- вь1й элемент 8 задержки, второй элемент И 9, триггер 10, группу п селекторов 11 ошибки, второй элемент 12 задержки, второй элемент ИЛИ 13,третий элемент ИЛИ 14 и имеет вход 15 сброса и Эталонный блок 16. Контролируемый цифровой блок 17 не входит в состав устройства; на фиг.1 он приведен для пояснения. Формирователи 5 импульсов идентичны формирователям 6 импульсов. Выход генератора 1 синхроимпульсов соединен с первыми вхо- .

а о оо

00 00

ел

по

. дами элементов 2 и 7. Выход элемента 2 соединен с входом синхронизации генератора 3 тестов, выходы которого являются выходами устройства для подключения к информационным входам контролируемого цифрового блока 17 и соединены с информационными входами эталонного блока 16. Информационные входы устройства для подключения к выходам контролируемого цифрового блока 17 соединены с первой группой входов схемы А сравнения, а также с входами формирователей 5 импульсов первой группы, выходы которых соединены с входами первого элемента ИЛИ 7 с второго по (п+1)-й. Вторая группа входов схемы 4 сравнения .соединена с выходами эталонного блока 16, а также с входами формирователей 6 импульсов второй группы, выходы которых соединены с входами элемента 7 с (п+2)-го по (2п+1)-и соответственно. Выход элемента 7 соединен с входом элемента 8, Первые и вторые информационные входы селекторов 11 ошибки соединены с выходами-одноименных формирователей 5 и 6 импульсов первой и второй групп. Вход элемен- та 12 соединен с выходом генератора 1 синхроимпульсов. Выход второго элемента 12 задержки соединен с объединенными управляюп1ими входами селекторов 11 оршбки, выходы которых соединены с входами элемента 13. Выход элемента 13 соединен с первым входом элемента 14, подключенного в разрыв между выходом схемы 4 сравнения и первым входом элемента 9. Выход элемента 8 соединен с вторым входом элемента 9, выход которого соединен с единичным входом триггера 10, выход которого соединен с вторым входом элемента 2. Вход сброса генератора 3 тестов является входом 15 сброса устройства для подключения к входу начальной установки контролируемого цифрового блока 17, а также соединен с входом начальной установки эталонного блока 16 и триггера 10.

Селектор 11 ошибки (фиг.2) содержит элемент ИСКЛЮЧАКМЦЕЕ ИЛИ 18 и реверсивный счетчик 19, причем входы элемента 18 соединены с первым и вторым щиЬормационными входами селектора,

счетньй вход счетчика 19 соединен с выходом элемента 18,первь1й вход которого соединен также с входом направления счета счетчика 19, вход сброса

1603385

. д

д т 35 т 20 г 25 э ,Q с /ю в в з в н

и с л к з р да ющ ют 5 вх ре ст в си 55 де о ко вы тр

40

которого соединен с управляющим вхо- . дом селектора, выход счетчика 19 является выходом селектора.

Устройство работает-следующим образом.

Перед началом контроля блока 17 сигналом, поступающим на вход 15 сброса устройства, осуществляется ус- д тановка в исходное состояние генератора 3 тестов, триггера 10, контролируемого 17 и эталонного 16 блоков. Генератор 1 синхроимпульсов через открытый единичным уровнем с выхода 5 триггера 10 элемент 2 запускает генератор 3 тестов, инициируя выработку стимулирующих сигналов (воздействия) на каждый задающий синхроимпульс. Выработанное воздействие с выходов 0 генератора 3 тестов подается на одноименные входы эталонного 16 и контролируемого 17 блоков. Реакции блоков 16 и 17 на соответствующих одноименных выходах сравниваются в схеме 5 сравнения, результат сравнения через элемент 14 поступает на первый вход элемента 9. С целью опроса результата сравнения на второй вход элемента 9 с выхода генератора 1 Q синхроимпульсов через элемент 7 поступает задержанньй элементом 8 зада- /ющий синхроимпульс, причем временная величина задержки выбирается равной временному интервалу от появления задающего синхроимпульс до формиро- вания результата сравнения откликов на выходе схемы 4 сравнения.

Опрос- результатов сравнения производится при любом изменении состояния на любом из выходов контролируемого 17 или эталонного 16 блоков, в том числе и в интервале между задающими синхроимпульсами на внутренних тактах контролируемого блока 17. При изменении состояния на выходах блоков 16 и 17 в процессе выра- бо.тки отклика на выходах соответствующих формирователей 6 и 5 вырабатьгаа- ются импульсы, которые через элемент 7 и элемент 8 поступают на второй вход элемента 9, осу1цествляя опрос результата сравнения при изменении состояния блоков 16 и 17. При наличии в момент опроса результата сравнения сигнала ошибки, формируемого на выхо- 5 де схемы 4 сравнения при несравнении откликов на одноименных выходах блоков 16 и 17, на выходе элемента 9 вырабатывается сигнал, запускающий триггер 10, сигнал с выхода которого

0

поступает на вход элемента 2, запрещая прохождение задающих синхроимпульсов на вход генератора 3 тестов и останавливая тем работу устройств а о

В случае появления на выходе блока 17 ложного сигнала, имеющего длительность меньше временной величины задержки элемента 8, опрос результатов сравнения происходит в момент, когда ложный сигнал на выходе блока 17, а следовательно, и сигнал несравнения (ошибки) на выходе схемы 4 сравнения исчезнут. В связи с этим состояние на выходе элемента 9 не изменится, триггер 10 не запустится и не остановит работу устройства контроля, а ложный сигнал, свидетельствующий о неисправности контролируемого блока 17j таким образом, не обнаружится. С целью фиксирования ложных сигналов любой длительности в устройстве контроля используются п идентичных по исполнению и принципу работы селекторов 11 ошибки.

Перед опросом первого результата сравнения на объединенные управляющие входы селекторов 11 с выхода генератора 1 через элемент 12 задержки поступает задающий синхроимпульс, обнуляя содержимое счетчиков 19, входящих в состав селекторов 11 (фиг.2). Временная величина задержки элемента 12 выбирается меньшей величины задержки элемента 8 на время, необходимое для прохождения сигналов через элементы 13 и 14. Тем самым исключается влияние на результат контроля переходных процессов на выходах блоков 16 и 17, имеющих место до появления первого отклика из совокупности последовательных реакций на заданное входное воздействие.

В процессе выработки откликов (т. внутренних тактов) на первые и вторые информационные входы селекторов 11 поступают импульсы с выходов соответствующих пар одноименных формирователей 5 и 6 импульсов. Импульсы при этом воздействуют на первые и BTOpbie входы элементов 18, входящих в состав селекторов 11 (фиг.2).При . одновременном изменении состояния на Некоторой паре одноименных выходов блоков 16 и 17 импульсы с соответствующих формирователей 6 и 5 поступают на входы элемента 18 одновременно и не изменяют состояния высокого единичного уровня на выходе послед

5

0

него. Не изменяется и нулевое состояние счетчика 19, чей счетный вход возбуждается отрицательным перепадом логического уровня с выхода элемента 18.

При неодновременном появлении сиг. /lianoB отклика на одноименных выхс71ах блоков 16 и 17 (т.е. с задержкой относительно друг друга в пределах временного интервала, ограничиваемого величиной задержки элемента 8), а также при отсутствют необходимого изменения состояния или наличии ложного сигнала на выходе контролируемого . блока 17 реверсивным счетчиком 19 в процессе вьфаботки отклика осуществляется подсчет отрицательных перепадов логического уровня на выходе элемента 18. Отрицательные перепады при этом образуются в ответ на неодновременное поступление на входы элемента 18 импульсов с соответствующих одноименных формирователей 5 и 6 импульсов. Направление счета явля- ется непостоянным и меняется на противоположное в зависимости от того, с какого формирователя импульсов (5 или 6) поступает на входы элемента 18 „ импульс, вызываюпшй отрицательный перепад на выходе последнего, т.е, направление счета на приращение или уменьшение содержимого счетчика 19 задается соответственно по наличию или отсутствию сигнала с формирователя 5 импульсов, поступающего на вход направления счета счетчика 19. При этом естественная задержка прохождения сигнала через элемент 18 позволяет определить направление

5

5

0

счета до появления на счетном входе

счетчика. 19 отрицательного перепада логического уровня. Для обеспечения безотказной, правильной работы реверсивного счетчика 19 в устройст45 ве контроля необходимо, чтобы его время срабатывания было меньше дли-, тельности импульсов, вырабатываемых форми1ювателями 5 и 6.

Таким образом, счетчиками 19 се50 лекторов 11 ошибки производится подсчет сигналов откликов с соответствующих пар одноименных выходов эталонного 16 и контролируемого 17 блоков, но с приращением содержимо о

55 счетчиков 19 по сигналам откликов контролируемого блока 17 (т.е. импульсов с формирователей 5) и с уменьшением содержимого счетчиков 19 по сигналам откликов эталонного блока 16

(т.е. импульсов с соответствующих формирователей 6). Разрядность счетчика 19 определяется по возможному количеству импульсов ложной последовательности.

Если на момент опроса результатов сравнения число сигналов отклика с одноименных выходов блоков 16 и 17 не совпадает, то Ма выходах соответствующего селектора 11 ошибки {т.е. на одном или нескольких выходах счетчика 19) (фиксируется сигнал единичного уровня, свидетельствуюпщй о наличии ошибки. Сигнал ошибки через элементы 13 и 14 поступает на первый вход элемента 9, которьй с приходом на его второй вход импульса опроса результатов сравнения вырабатывает сигнал.

16033858

руется импульс, обладаюший длительностью, не большей длительности импульса, вырабатываемого формирователем 5 (6). Следовательно, лишь совместное использование в устройстве контроля схемы 4 сравнения и группы селекторов 11 ошибки обеспечивает фиксирование на выходе блока 17 ложных сигналов любой длительности (как одиночных,так и последовательностей им-s пульсов).

Формулаизобретения

10

15

30

ся нулевой уровень на выходе триггера 10 закрывает элемент 2 и останавливает работу устройства контроля. При остановке работы устройства делается вьшод о неисправности кон- тролируемого блока 17. При этом неисправность блока 17 определяется ошибками в формировании отклика нескольких видов. Если на момент опроса результата сравнения сигнал ошибки присутствует как на выходе элемента 13, так и на выходе схемы 4 сравнения, следовательно, на одном или нескольких выходах контролируемого блока 17 в процессе выработки отклика не произошло ожидаемого изменения уровня сигнала отклика или сформировалось ложное изменение состояния. Присутствие сигнала ошибки в момент опроса результатов лишь на выходе элемента 13 и отсутствие его на выходе схемы 4 сравнения свидетельствует о выработке на выходе блока 17 ло.жного сигнала с длительностью, меньшей временной величины задержки элемента 8, Не исключена ситуация, при которой вывод о сбое контролируемого блока 17 будет сделан лишь по сигналу ошибки с выхода схемы 4 сравнения, т.е. группа селекторов 11 ошиб-сп ки в отличие от схемы 4 сравнения может не обнаружить сбоя (ошибки)если вместо ожидае:мого изменения состояния в процессе выработки отклика на выторов ошибки, где п - число выходов контролируемого цифрового блока,второй и третий элементы ИЛИ и второй элемент задержки, вход которого соединен с выходом генератора синхроимпульсов , первый и второй информационные входы, управляющий вход и выход i-ro селектора ошибки группы подключены соответственно к выходу i-ro формирователя импульсов первой группы, выходу i-ro формировател импульсов второй группы, выходу второго элемента задержки и i-му входу второго элемента ИЛИ, а первьй и вто 35 Р° йходы и выход третьего элемента ИЛИ соединены соответственно с выходами второго элемента ИЛИ и схемы сравнения и первым входом второго элемента И, второй вход которого под ключен к выходу первого элемента задержки.

лектор ошибки группы содержит элемен 45 ИСКЛЮЧАЮЩЕЕ ИЛИ и реверсивный счетчик, вход направления счета, счетный вход, вход сброса и выход которого подключены соответственно к первому информационному входу селектора, выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, управляющему входу селектора и выходу селектора, а первый и второй входы элемента ИСКШОЧАИЯЦЕЕ ИЛИ являются соответственно первым и вторым информалектор ошибки группы содержи 45 ИСКЛЮЧАЮЩЕЕ ИЛИ и реверсивны чик, вход направления счета вход, вход сброса и выход ко подключены соответственно к информационному входу селект ходу элемента ИСКЛЮЧАЮЩЕЕ ИЛ равляющему входу селектора и селектора, а первый и второй элемента ИСКШОЧАИЯЦЕЕ ИЛИ явл ответственно первым и вторым

ходе контролирующего блока 17 сформи- ционными входами селектора.

торов ошибки, где п - число выходов контролируемого цифрового блока,второй и третий элементы ИЛИ и второй элемент задержки, вход которого соединен с выходом генератора синхроимпульсов , первый и второй информационные входы, управляющий вход и выход i-ro селектора ошибки группы подключены соответственно к выходу i-ro формирователя импульсов первой группы, выходу i-ro формирователя импульсов второй группы, выходу второго элемента задержки и i-му входу второго элемента ИЛИ, а первьй и вто- Р° йходы и выход третьего элемента ИЛИ соединены соответственно с выходами второго элемента ИЛИ и схемы сравнения и первым входом второго элемента И, второй вход которого подключен к выходу первого элемента задержки.

лектор ошибки группы содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и реверсивный счетчик, вход направления счета, счетный вход, вход сброса и выход которого подключены соответственно к первому информационному входу селектора, выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, управляющему входу селектора и выходу селектора, а первый и второй входы элемента ИСКШОЧАИЯЦЕЕ ИЛИ являются соответственно первым и вторым информационными входами селектора.

CkJcraBHTenb Г.Виталиев Редактор Т.Лазоренкр Техред Л.Сердюкова Корректор Т.Палий

Заказ 3386

Тираж 569

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ C(JCP 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Фиг, 2

Подписное

| Устройство для контроля цифровых узлов | 1985 |

|

SU1304027A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-10-30—Публикация

1988-12-26—Подача