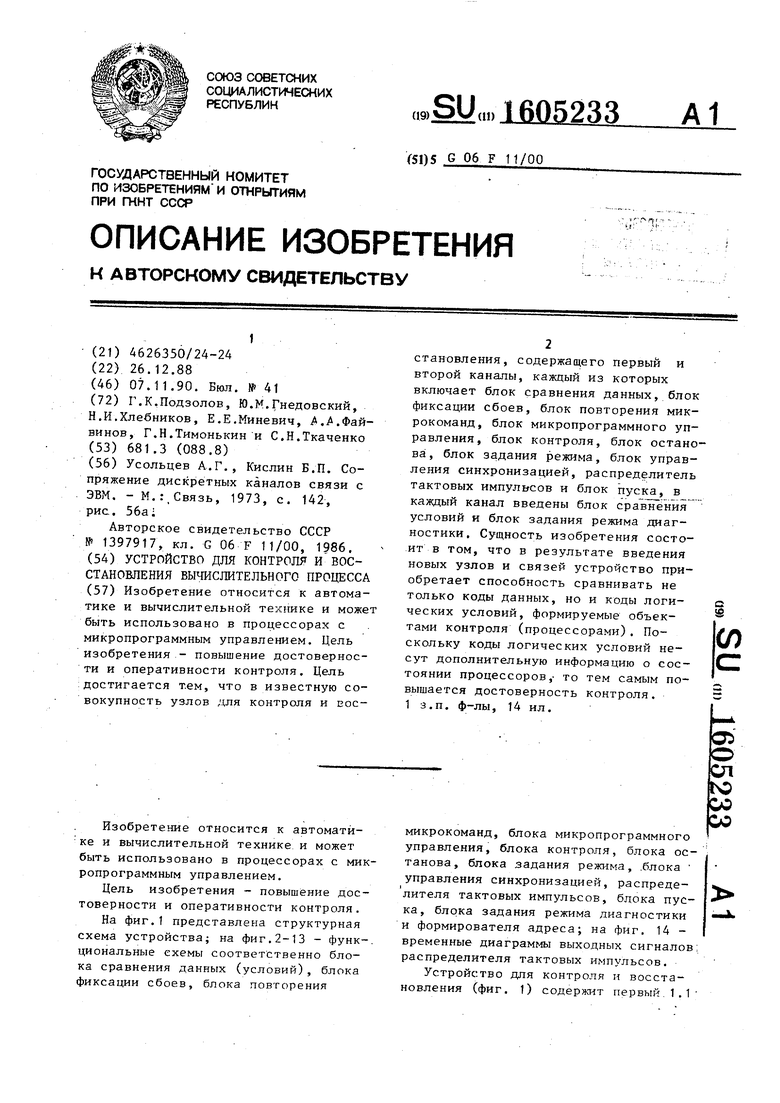

Изобретение относится к автоматике и вычислительной технике и может быть использовано в процессорах с микропрограммным управлением.

Цель изобретения - повышение достоверности и оперативности контроля.

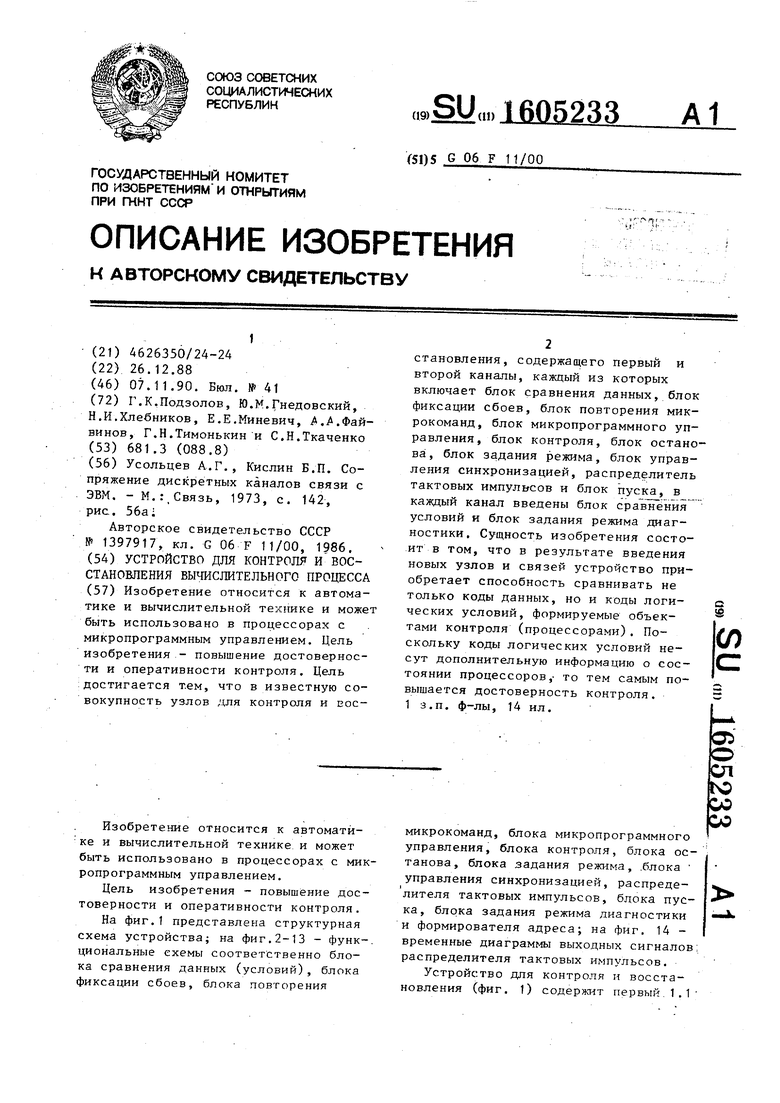

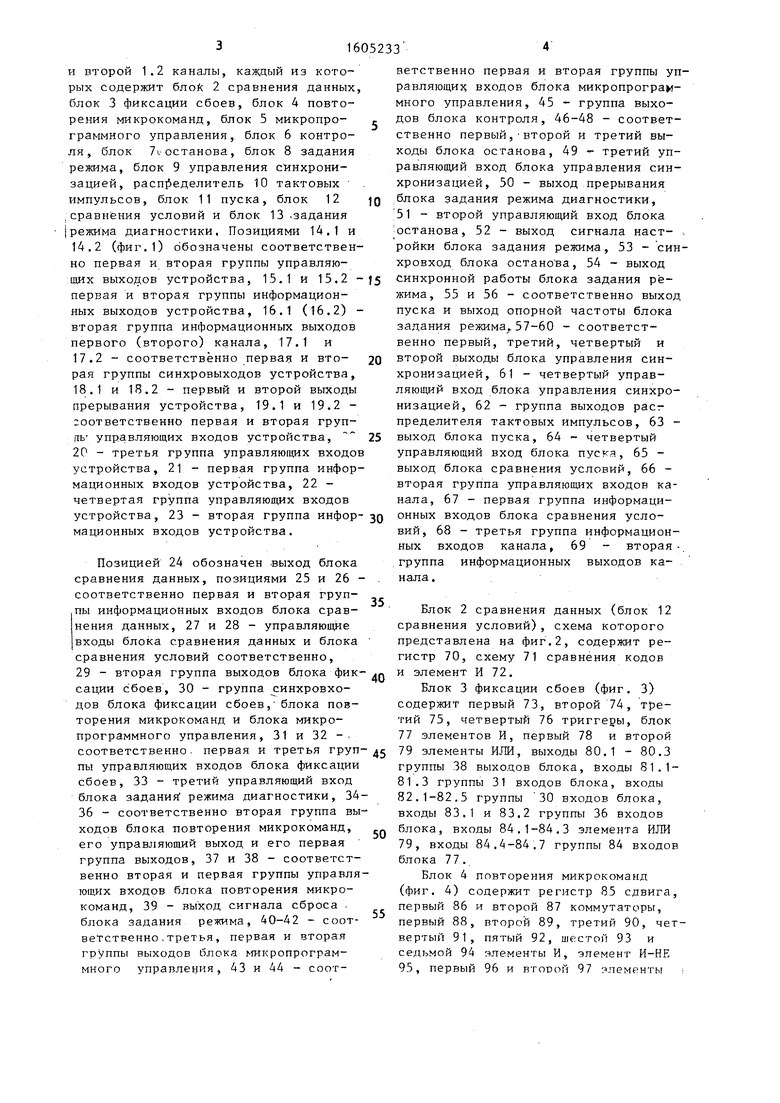

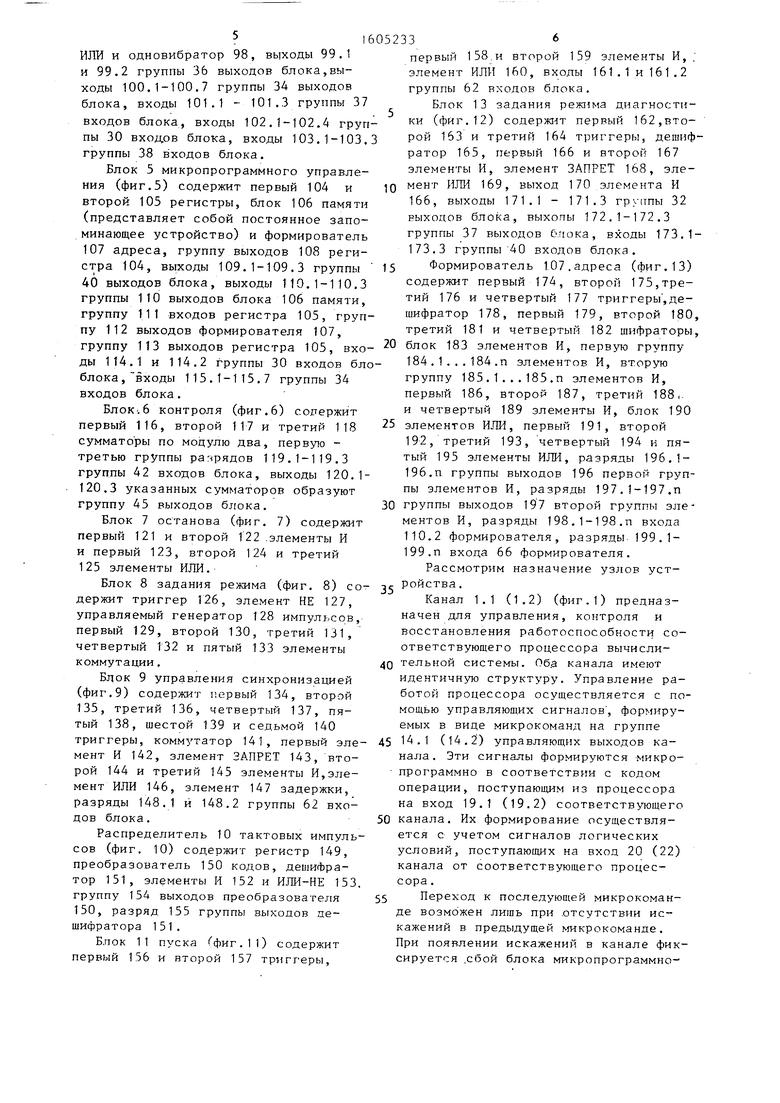

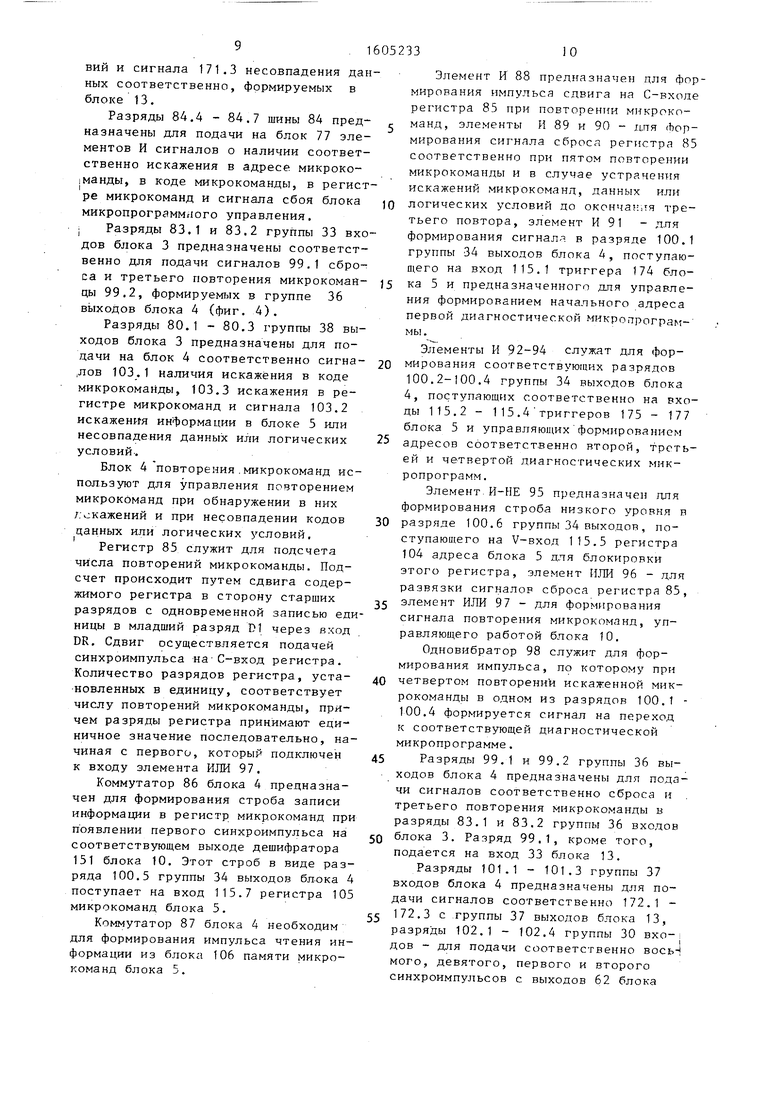

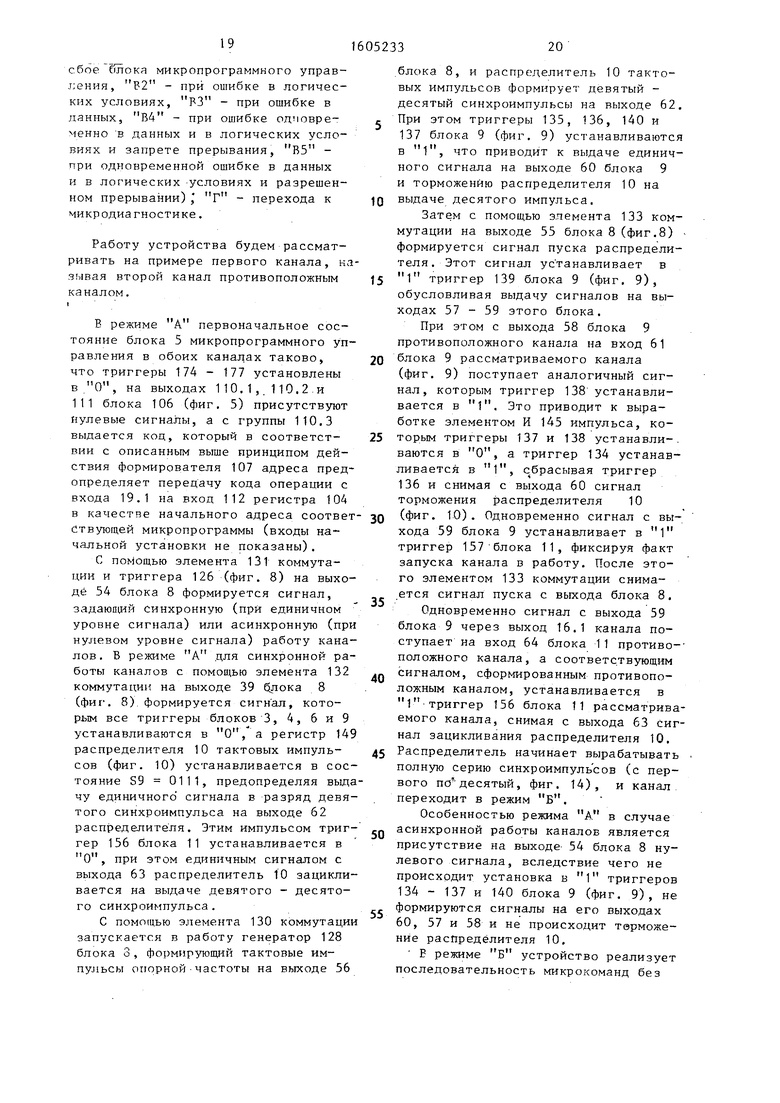

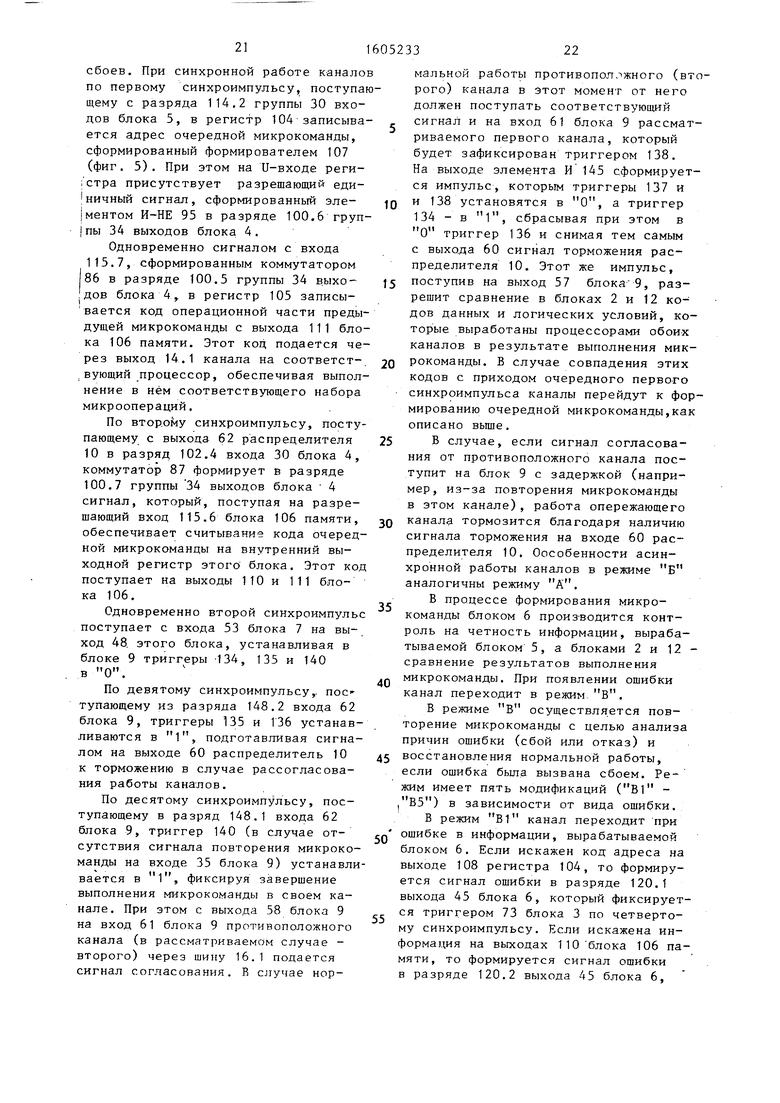

На фиг.1 представлена структурная схема устройства; на фиг.2-13 - функ-. циональные схемы соответственно блока сравнения данных (условий), блока фиксации сбоев, блока повторения

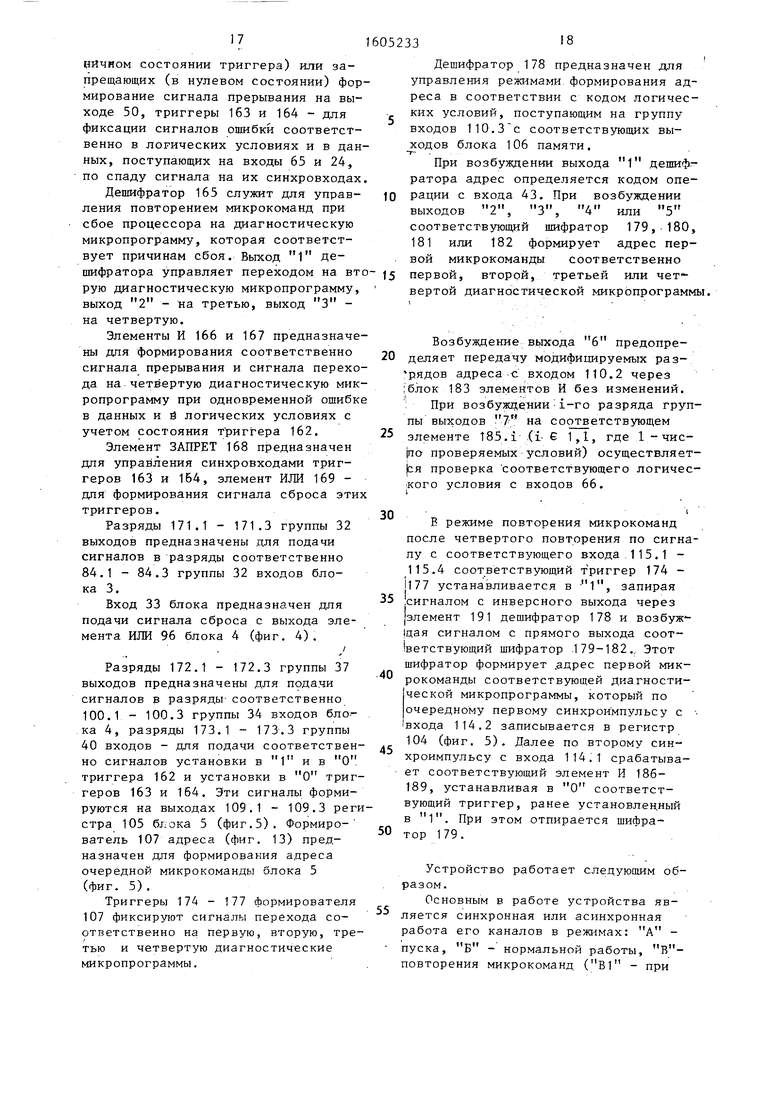

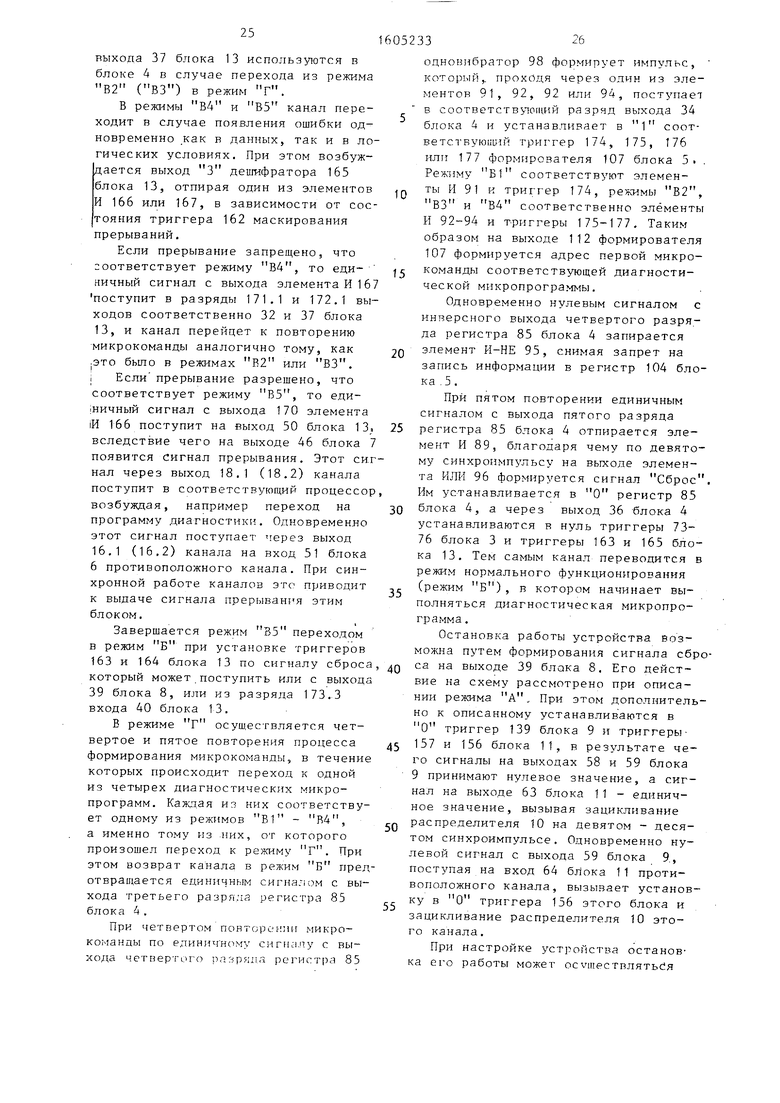

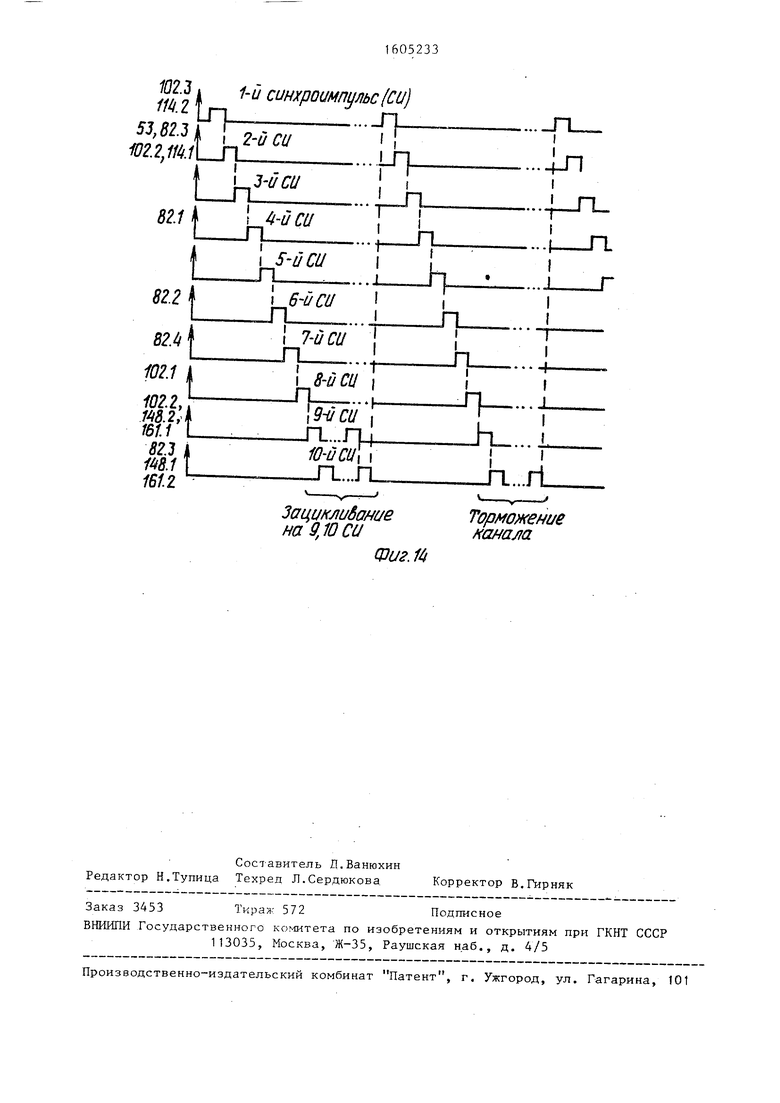

микрокоманд, блока микропрограммного управления, блока контроля, блока останова, блока задания режима, .блока управления синхронизацией, распределителя тактовых импульсов, блока пуска, блока задания режима диагностики и формирователя адреса; на фиг. 14 - временные диаграммы выходных сигналов; распределителя тактовых импульсов.

Устройство для контроля и восстановления (фиг. 1) содержит первый,1.1

о: о- ел

ГчЭ

с со

и второй 1.2 каналы, каждый из которых содержит бло#с 2 сравнения данных, блок 3 фиксации сбоев, блок 4 повторения микрокоманд, блок 5 микропро- граммного управления, блок 6 контроля, блок 7vостанова, блок 8 задания режима, блок 9 управления синхронизацией, распределитель 10 тактовых импульсов, блок 11 пуска, блок 12 ,сравнения условий и блок 13 .задания |режима диагностики, Позициями 14,1 и 14,2 (фиг.1) обозначены соответственно первая и вторая группы управляющих выходов устройства, 15.1 и 15.2 первая и вторая группы информационных выходов устройства, 16,1 (16,2) - вторая группа информационных выходов первого (второго) канала, 17.1 и 17.2 - соответственно первая и вто- рая группы синхровыходов устройства, 18,1 и 18.2 - первый и второй выходы прерывания устройства, 19.1 и 19.2 - соответственно первая и вторая груп- дь управляющих входов устройства, 20 - третья группа управляюпщх входов устройства, 21 - первая группа информационных входов устройства, 22 - четвертая группа управляющих входов устройства, 23 - вторая группа инфор мационных входов устройства.

Позицией 24 обозначен выход блока сравнения данных, позициями 25 и 26 - соответственно первая и вторая группы информационных входов блока сравнения данных, 27 и 28 - управляющие входы блока сравнения данных и блока сравнения условий соответственно, 29 - вторая группа выходов блока фик сации сбоев, 30 - группа синхровхо- дов блока фиксации сбоев, блока повторения микрокоманд и блока микропрограммного управления, 31 и 32 -- соответственно, первая и третья груп пы управляющих входов блока фиксации сбоев, 33 - третий управляющий вход блока задания; режима диагностики, 34 36 - соответственно вторая группа выходов блока повторения микрокоманд, его управляющий выход и его первая группа выходов, 37 и 38 - соответственно вторая и первая группы управляющих входов блока повторения микрокоманд, 39 - выход сигнала сброса . блока задания режима, 40-42 - соответственно .третья, первая и вторая группы выходов блока микропрограммного управления, 43 и 44 - соот

5 0 5 о

5

п .

5

ветственно первая и вторая группы управляющих входов блока микропрограммного управления, 45 - группа выходов блока контроля, 46-48 - соответственно первый,второй и третий выходы блока останова, 49 - третий управляющий вход блока управления синхронизацией, 50 - выход прерывания блока задания режима диагностики, 51 - второй управляющий вход блока останова, 52 - выход сигнала наст- , ройки блока задания режима, 53 - син- хровход блока остано ва, 54 - выход Синхронной работы блока задания режима, 55 и 56 - соответственно выход пуска и выход опорной частоты блока задания режима,. 57-60 - соответственно первый, третий, четвертый и второй выходы блока управления синхронизацией, 61 - четвертый управляющий вход блока управления синхронизацией, 62 - группа выходов расг пределителя тактовых импульсов, 63 - выход блока пуска, 64 - четвертый управляющий вход блока пуска, 65 - выход блока сравнения условий, 66 - вторая группа управляющих входов канала, 67 - первая группа информационных входов блока сравнения условий, 68 - третья группа информационных входов канала, 69 - вторая- группа информационных выходов канала .

Блок 2 сравнения данных (блок 12 сравнения условий), схема которого представлена на фиг,2, содержит регистр 70, схему 71 сравнения кодов и элемент И 72.

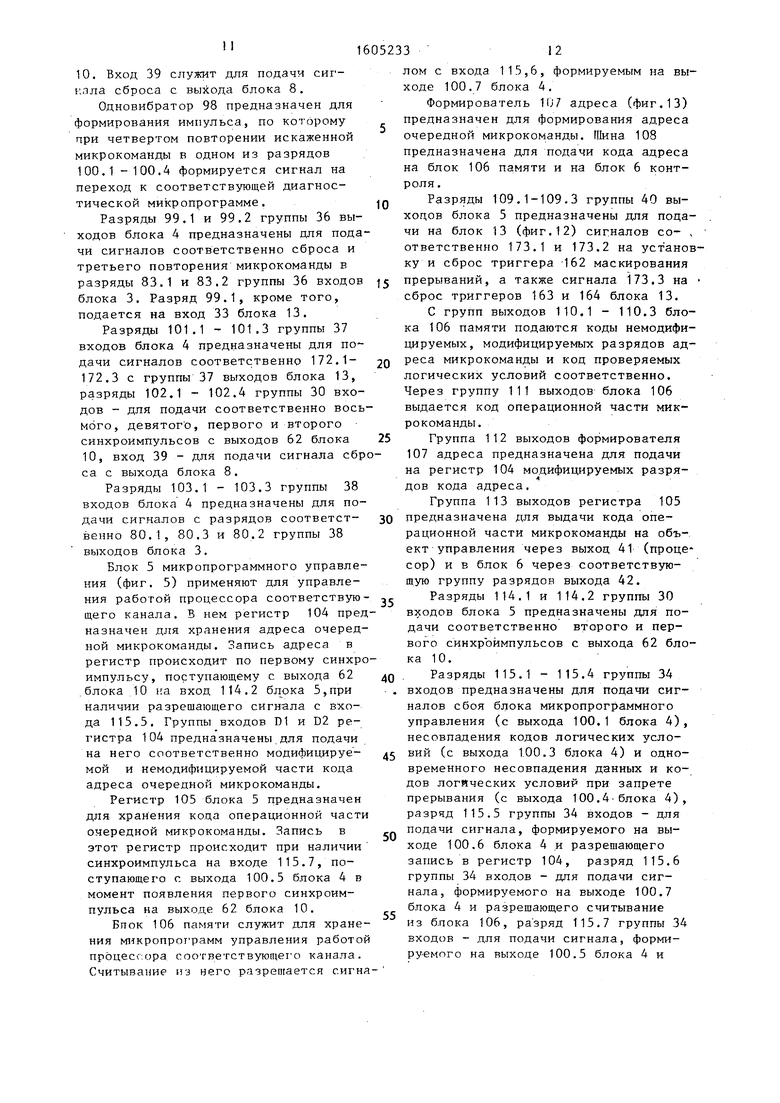

Блок 3 фиксации сбоев (фиг, 3) содержит первый 73, второй 74, третий 75, четвертый 76 триггеры, блок 77 элементов И, первый 78 и второй 79 элементы ИЛИ, выходы 80,1 - 80.3 группы 38 выхо.цов блока, входы 81.1- 81.3 группы 31 входов блока, входы 82.1-82.5 группы 30 входов блока, входы 83,1 и 83,2 группы 36 входов блока, входы 84,1-84.3 элемента ИЛИ 79, входы 84,4-84.7 группы 84 входов блока 77.

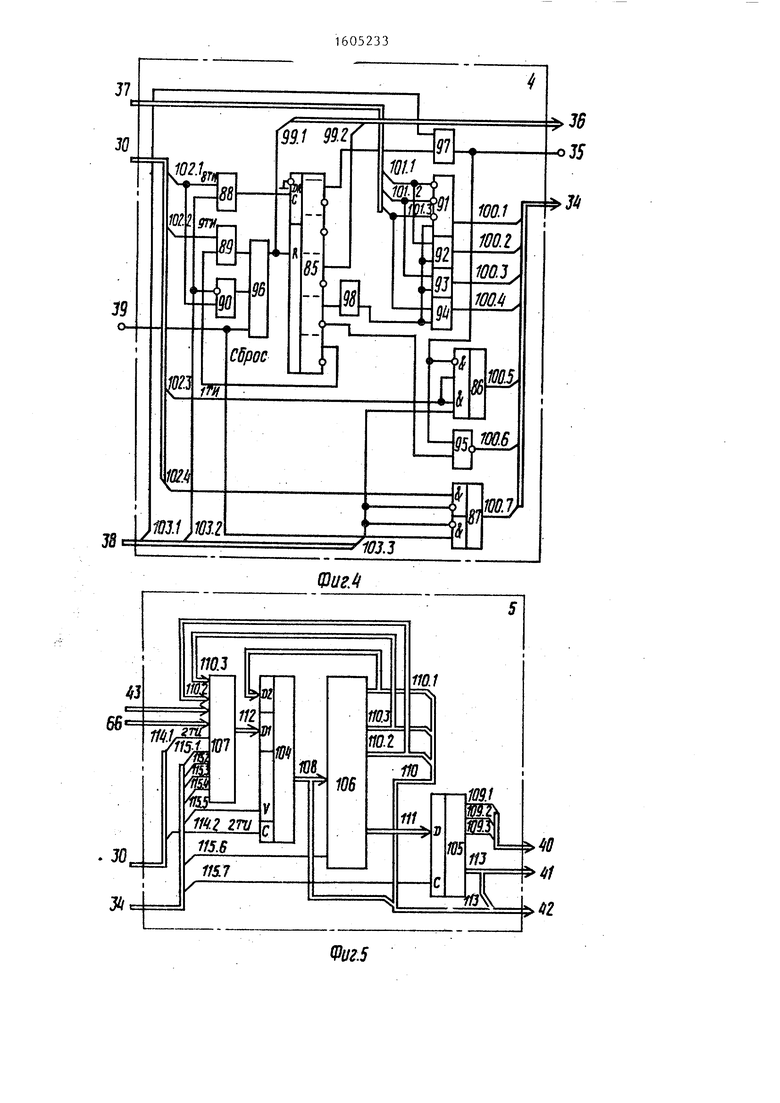

Блок 4 повторения микрокоманд (фиг, 4) содержит регистр 85 сдвига, первый 86 и второй 87 коммутаторы, первый 88, BTopoia 89, третий 90, четвертый 91, пятый 92, шестой 93 и седьмой 94 элементы И, элемент И-НЕ 95, первый 96 и ВТОРОЙ 97 элементы

ИЛИ и одновибратор 98, выходы 99.1 и 99,2 группы 36 выходов блока,выходы 100.1-100.7 группы 34 выходов блока, входы 101.1 - 101.3 группы 37 входов блока, входы 102.1-102.4 группы 30 входов блока, входы 103.1-103 группы 38 входов блока.

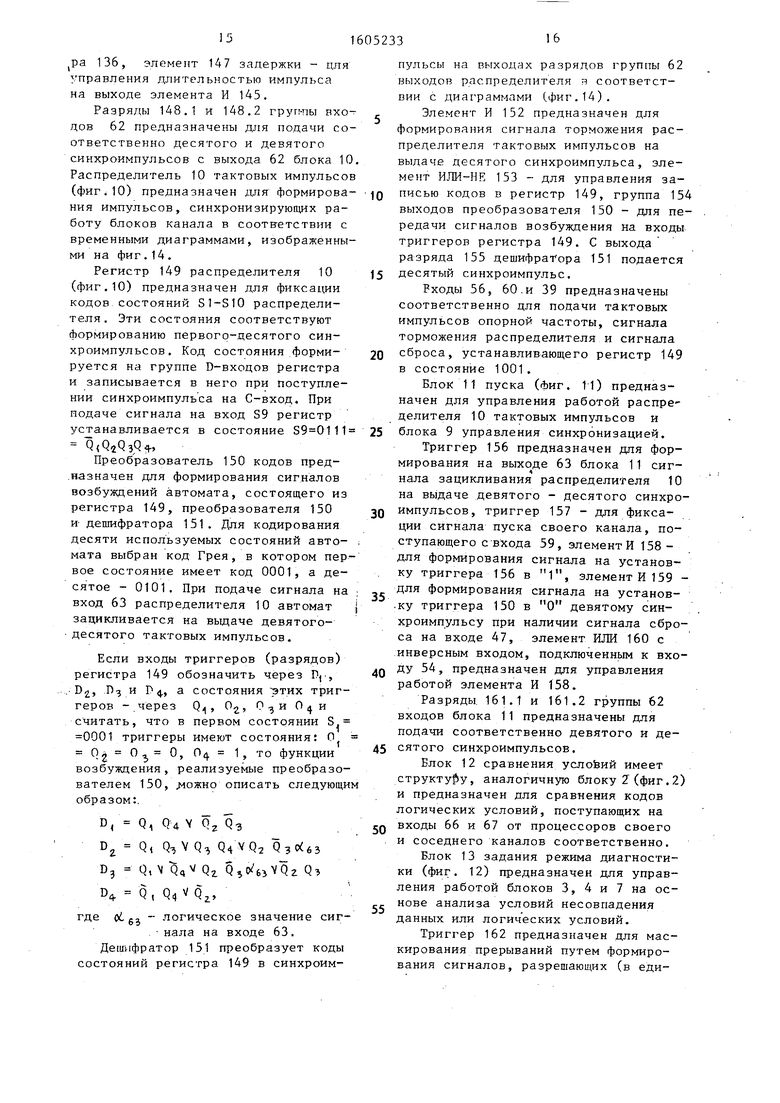

Блок 5 микропрограммного управления (фиг.5) содержит первый 104 и второй 105 регистры, блок 106 памяти (представляет собой постоянное запоминающее устройство) и формирователь 107 адреса, группу выходов 108 регистра 104, выходы 109.1-109.3 группы 40 выходов блока, выходы 110.1-110.3 группы 110 выходов блока 106 памяти, группу 111 входов регистра 105, группу 112 выходов формирователя 107, группу 113 выходов регистра 105, входы 114.1 и 114.2 группы 30 входов бл блока, входы 115.1-115.7 группы 34 входов блока.

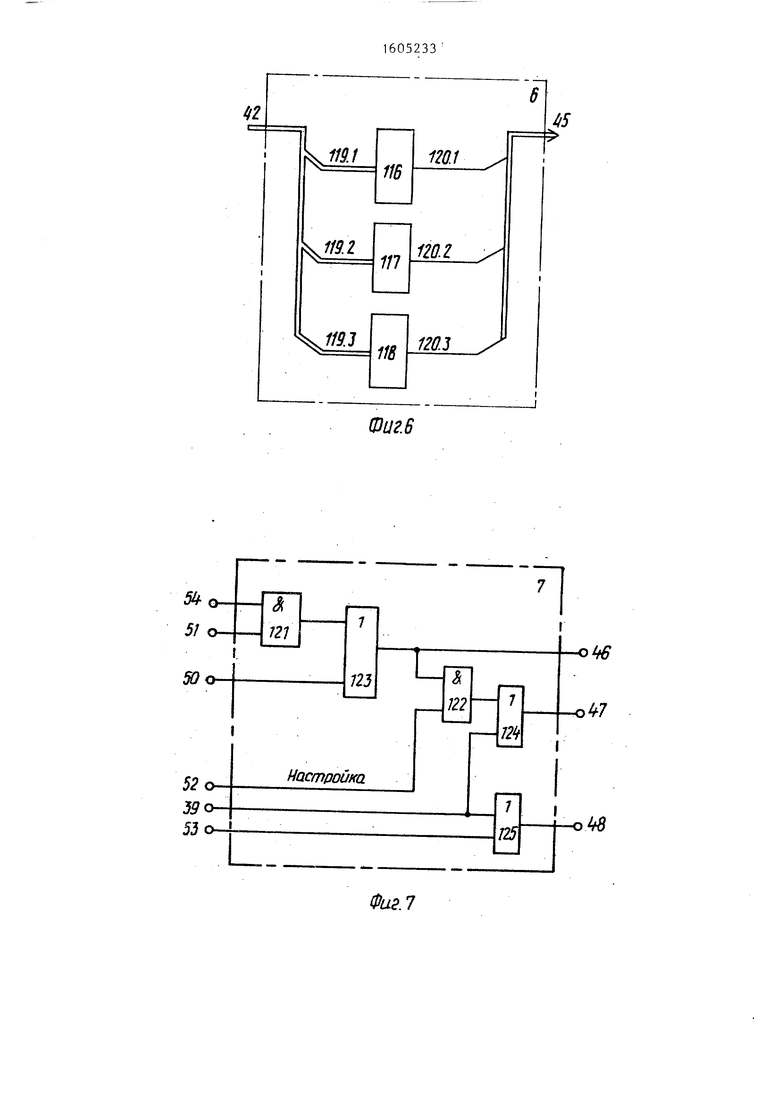

Блок-.6 контроля (фиг.6) содержит первый 116, второй 117 и третий 118 сумматоры по модулю два, первую - третью группы рагфядов 119.1-119.3 группы 42 входов блока, выходы 120.1 120.3 указанных сумматоров образуют группу 45 выходов блока.

Блок 7 останова (фиг. 7) содержит первый 121 и второй 122 .элементы И и первый 123, второй 124 и третий 125 элементы ИЛИ.

Блок 8 задания режима (фиг. 8) со- держит триггер 126, элемент НЕ 127, управляемый генератор 128 импульсов, первый 129, второй 130, третий 131, четвертый 132 и пятый 133 элементы коммутации.

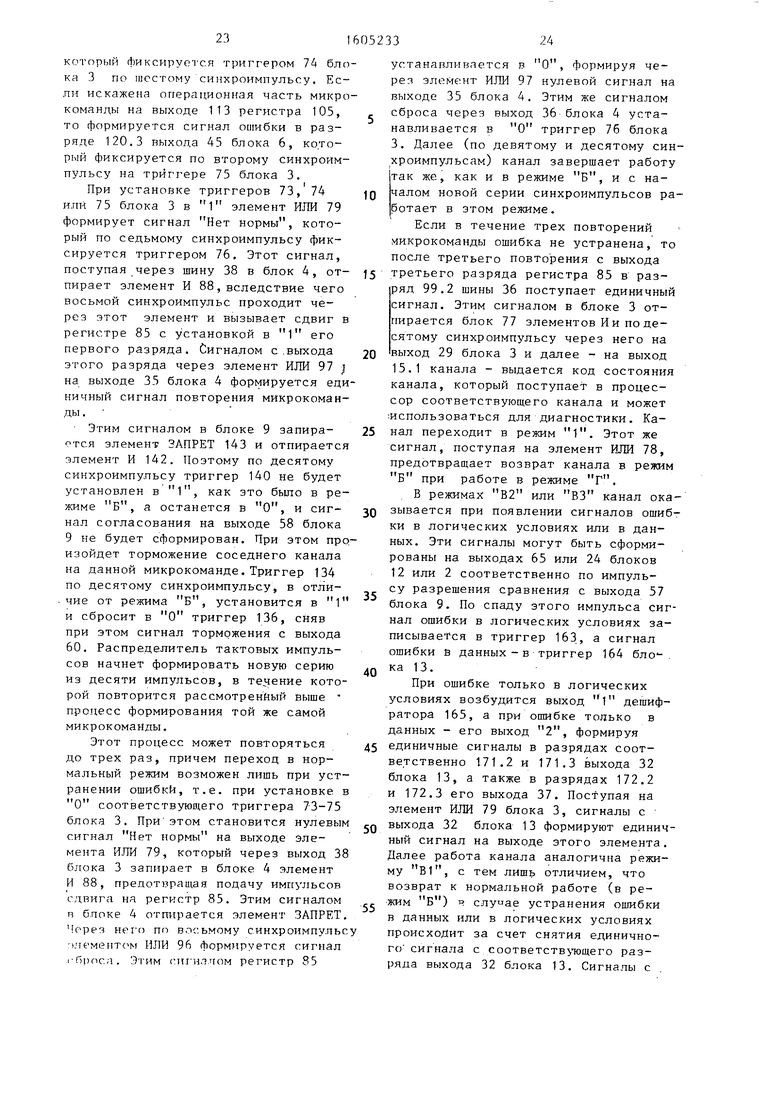

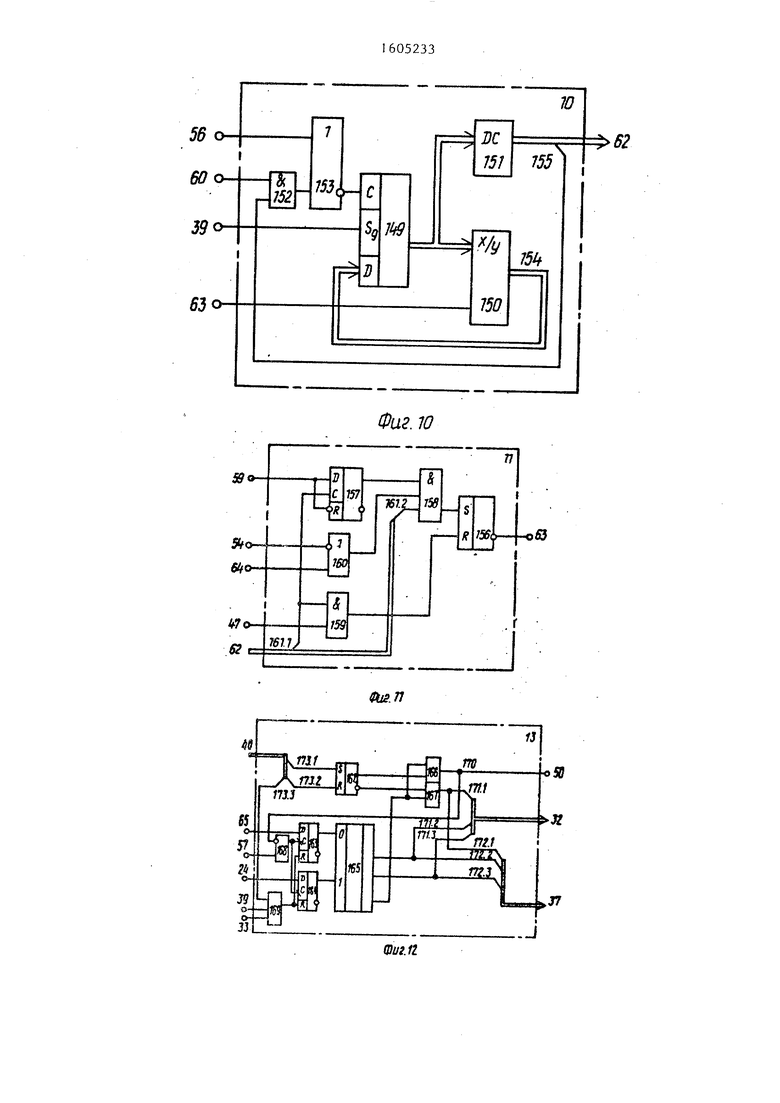

БЛОК 9 управления синхронизацией (фиг.9) содержит первый 134, второй 135, третий 136, четвертый 137, пятый 138, шестой 139 и седьмой 140 триггеры, коммутатор 141, первый элемент И 142, элемент ЗАПРЕТ 143, второй 144 и третий 145 элементы И,элемент ИЛИ 146, элемент 147 задержки, разряды 148.1 и 148.2 группы 62 входов блока.

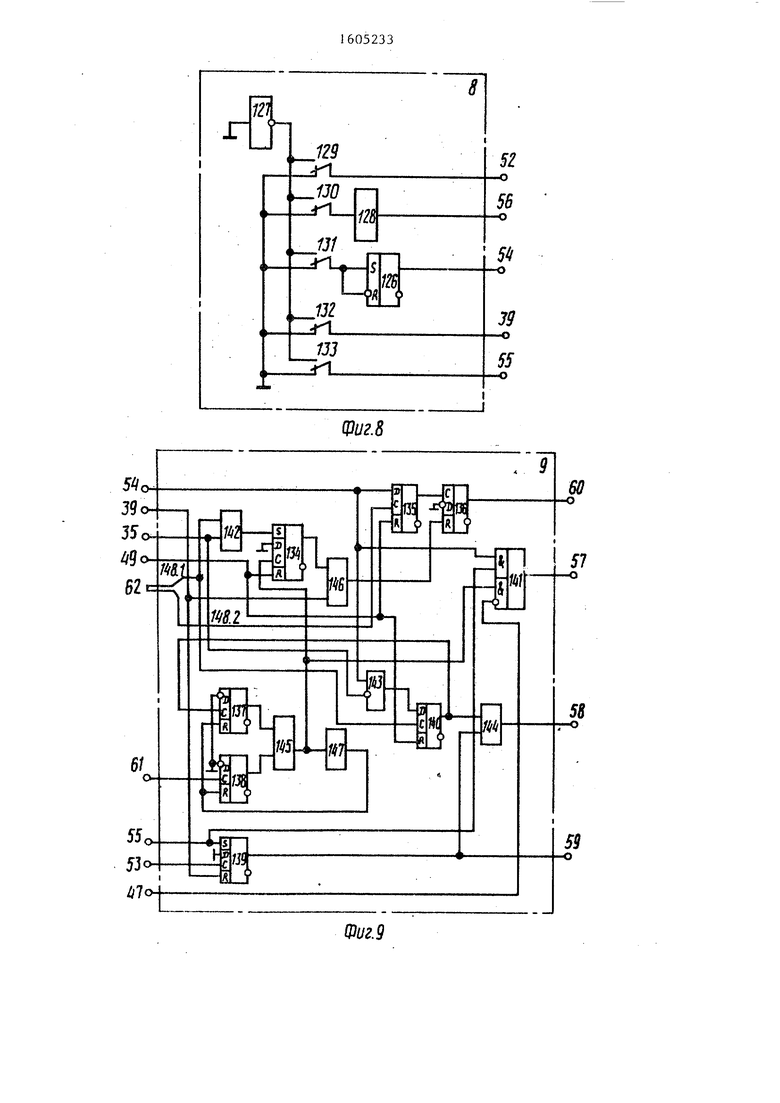

Распределитель 10 тактовых импульсов (фиг. 10) содержит регистр 149, преобразователь 150 кодов, дешифратор 151, элементы И 152 и ИЛИ-НЕ 153. группу 154 выходов преобразователя 150, разряд 155 группы выходов дешифратора 151.

Блок 11 пуска Гфиг.11) содержит первый 156 и второй 157 триггеры.

10

15

20

25

-

35

05233

первый

58,и второй 159 элементы И, ; элемент ИЛИ 160, входы 161.1 и 161.2 группы 62 входов блока.

Блок 13 задания режима диагностики (фиг.12) содержит первый 162,второй 163 и третий 164 триггеры, дешифратор 165, первый 166 и второй 167 элементы И, элемент ЗАПРЕТ 168, элемент ИЛИ 169, выход 170 элемента И 166, выходы 171.1 - 171.3 гру{1пы 32 выходов блока, выхопы 172.1-172.3 группы 37 выходов Олока, входы 173.1- 173.3 группы 40 входов блока.

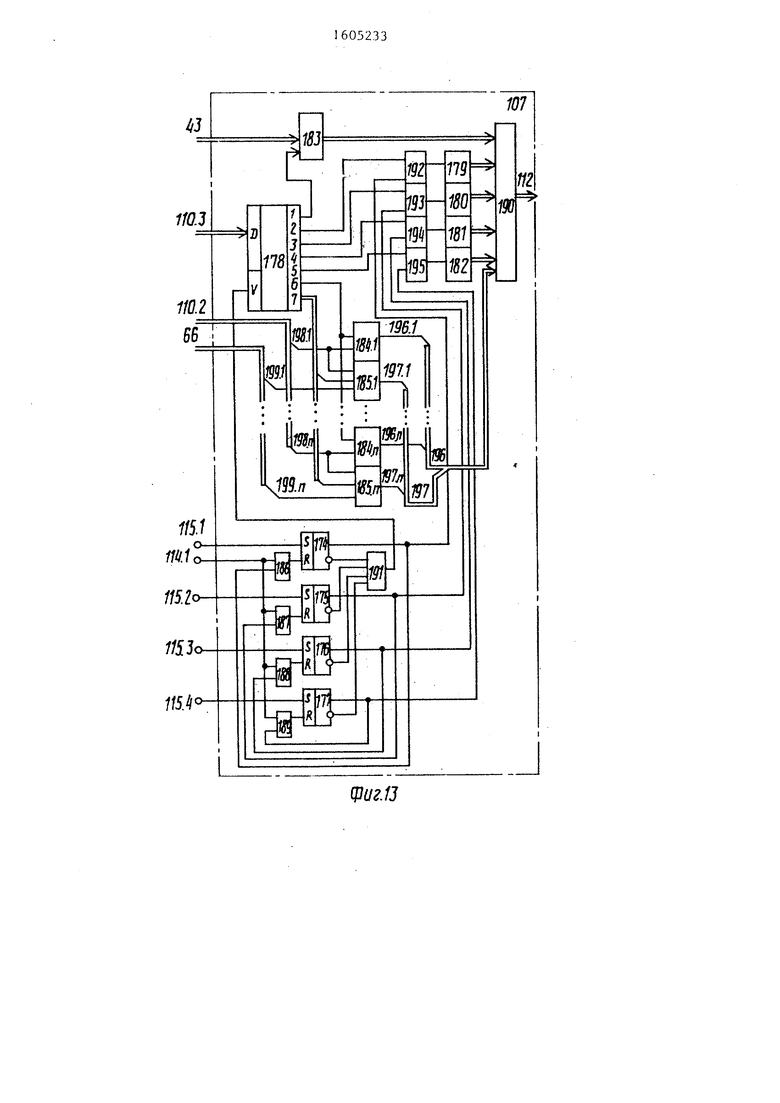

Формирователь 1.07.адреса (фиг. 13) содержит первый 174, второй 175,третий 176 и четвертый 177 триггеры ,де- шифратор 178, первый 179, второй 180, третий 181 и четвертый 182 шифраторы, блок 183 элементов И, первую группу 184 . 1 . . . 184.п элементов И, вторую группу 185.1...185.П элементов И, первый 186, второй 187, третий 188,. и четвертый 189 элементы И, блок 190 элементов ИЛИ, первый 191, BTopofi 192, третий 193, четвертый 194 и пятый 195 элементы ИЛИ, разряды 196.1- 196.п группы выходов 196 первой группы элементов И, разряды 197. 1-197.п группы выходов 197 второй группы эле ментов И, разряды 198,1-198.п входа 110.2 формирователя, разряды 199.1- 199.П входа 66 формирователя.

Рассмотрим назначение узлов устройства .

Канал 1.1 (1.2) (фиг.1) предназначен для управления, контроля и восстановления работоспособности соответствующего процессора вычисли- 40 тельной системы. Об.а канала имеют идентичную структуру. Управление работой процессора осушествляется с помощью управляющих сигналов , формируемых в виде микрокоманд на группе 45 14.1 (14.2) управляющих выходов канала. Эти сигналы формируются микро- программно в соответствии с кодом операции, поступающим из процессора на вход 19.1 (19.2) соответствующего канала. Их формирование осуществляется с учетом сигналов логических условий, поступающих на вход 20 (22) канала от соответствующего процессора .

Переход к последующей микрокоманде возможен лищь при .отсутствии искажений в предыдущей микрокоманде. Лри появлении искажений в канале фиксируется .сбой блока микропрограммно-30

50

55

го управления и микрсжоманда формируется повторно. Если после трехкратного повторения искажения не исчезают, то в канале фиксируется отказ блока-микропрограммного управления по данной микрокоманде, в результате чего на соответствующий процессор через выход 15.1 (15.2) выдается код состояния канала. При этом канал пе- реходит к реализации микропрограммы диагностики.

Работа каналов может осуществляться асинхронно или синхронно. При асинхронной работе каналы функциони- ругот независимо. При синхронной работе переход к следующей микрокоманде в каждом канале возможен лишь по окончании формирования соответствующей микрокоманды в другом канале . С целью синхронизации работы канал, окончив формирование микрокоманды без искажений, формирует в блоке 9 управления синхронизацией сигнал согласования, который через выход 16.1 (16.2) канала поступает на аналогичный блок соседнего канала. При отсутствии сигнала согласования от соседнего канала канал приостанавливает (тормозит) свою работу до прихода этого сигнала.

В случае синхронной работы, кроме того, в каждом канале при переходе к

следующей микрокоманде происходит

сравнение кодов логических условий (20 и 22) и кодов данных (21 и 23), сформированных процессорами в результате выполнения предьщущей микрокоманды. При несовпадении данных или логических условий канал )иксирует сбой процессора и аналогично описая- ному выше повторяет выдачу микрокоманды и сравнение ее результатов до трех раз, после чего в течение чет- вертого и пятого повторений вьщает на процессор код состояния канала и переходит к микродиагностике. При оцноврем енном несовпадении и данных, и логических условий работа канала зависит от состояния триггера маски- )ования. прерываний, находящегося в блоке 13 задания режима диагностики. Если прерывание запрещено, то канал работа, -f ,как и в предыдусаих случаях. Если оно разрешено, то на выходе 18.1 (1 8 . .1) канала формируется сигнал прорывания, а затем на выход 15. (15.2) подаетс:я кол, согтчзяния канала

g

5 0 5 О

5

Q 5

Блок 2 сравнения данных (фиг. 2) предназна-чен для сравнения кодов данных, поступающих на входы 25 и 26 от процессоров своего и Соседнего кана- пов соответственно. Сравнение происходит по приходу сигнала на вход 27, формируемого в случае нормального обмена сигналами согласования между каналами. При несовпадении данных на выходе 24 блока формируется сигнал ошибки в данных.

Блок 3 фиксации сбоев (фиг. 3) предназначен для фиксации причин искажения микрокоманды управления работой блока 4 повторения микрокоманд и выдачей на выход 29 кода состояния канала на выход 15.1 (15.2) канала. Этот код может использоваться процессором для диагностики и устранения последствий сбоев.

Триггеры 73 - 75 предназначены для фиксации искажения соответственно в адресе микрокоманды, в коде микрокоманды на выходе блока памяти микрокоманд и в коде микрокоманды на выходе регистра микрокоманд. Триггер 76 предназначен для фиксации наличия искажений указайньгх типов или наличия не- совпадения данных или логических условий с целью организации повторного формирования микрокоманды.

Входы 81.1 - 81.3 разрядов группы 31 входов блока 3 предназначены для подачи сигналов искажения соответственно в адресе микрокоманды, в коде микрокоманды и в регистре микрокоманд с выходов 120.1 - 120.3 блока 6 (фиг. 6).

Входы 82.1 - 82.5 разрядов группы 30 входов блока 3 предназначены для подачи соответственно четвертого,шестого, второго, седьмого и десятого синхроимпульсов с соответствующих выходов дешифратора 151 блока 10 (фиг. 10). Группа 32 входов блока 3 предназначена для подачи в этот блок сигналов несовпадения данных или логических условий с выхода блока 13. Шина 84 блока 3 предназначена для подачи на блок 77 элементов И сигналов состояния элементов канала.

Разряды 84.1 - 84.3 шины 84 предназначены для подачи на элемент ИЛИ 79 и блок 77 этементов блока 3 сигнала 171.1 одновременного несовпадения данных и логических условий при ра зрешенном прерывании, сигнала 171,2 несовпадения кодов логических уелоВИЙ и сигнала 171,3 несовпадения данных соответственно, формируемых в блоке 13.

Разряды 84.4 - 84.7 шины 84 предназначены для подачи на блок 77 элементов И сигналов о наличии соответственно искажения в адресе микроко- |Манды, в коде микрокоманды, в регистре микрокоманд и сигнала сбоя блока микропрограммного управления, i Разряды 83.1 и 83.2 группы 33 входов блока 3 предназначены соответственно для подачи сигналов 99.1 сбро20

первой диагностической микроггрограм- мы.

Элементы И 92-94 служат для форЭлемент И 88 предназначен для формирования импульса сдвига на С-входе регистра 85 при повторении микроко- 5 манд, элементы И 89 и 90 - для (hop- мирования сигнала сброса регистра 85 соответственно при пятом повторении . микрокоманды и в случае устранения искажений микрокоманд, данных или 10 логических условий до окончан;.тя третьего повтора, элемент И 91 - для формирования сигналя, в разряде 100.1 группы 34 выходов блока 4, поступаю- щего на вход 115.1 триггера 174 блоцы 99 г Z° ,5 ка 5 „ предназначенного для у„р„ле- Г(;: г., ф„р„„ро„ан„е„ начального адреса

Разряды 80.1 - 80.3 группы 38 выходов блока 3 предназначены для подачи на блок 4 соответственно сигна- ,лов 103.1 наличия искажения в коде микрокоманды, 103.3 искажения в регистре микрокоманд и сигнала 103.2 мскаженая информации в блоке 5 или несовпадения данных или логических условий..

Блок 4 повторения.микрокоманд используют для управления повторением микрокоманд при обнаружении в них /:скажений и при несовпадении кодов данных или логических условий.

Регистр 85 служит для подсчета числа повторений микрокоманды. Подсчет происходит путем сдвига содержимого регистра в сторону старших разрядов с одновременной записью единицы в младший разряд D1 через вход DR. Сдвиг осуществляется подачей синхроимпульса на-С-вход регистра. Количество разрядов регистра, установленных в единицу, соответствует числу повторений микрокоманды, причем разряды регистра принимают единичное значение последовательно, начиная с первого, который подключен к входу элемента ИЛИ 97.

Коммутатор 86 блока 4 предназначен для формирования строба записи информации в регистр микрокоманд при появлении первого синхроимпульса на соответствуюш,ем выходе дешифратора 151 блока 10. Этот строб в виде разряда 100.5 группы 34 выходов блока 4 поступает на вход 115.7 регистра 105 микрокоманд блока 5.

Коммутатор 87 блока 4 необходим для формирования импульса чтения информации из блока 106 памяти микрокоманд блока 5.

мирования соответствующих разрядов 100.2-100.4 группы 34 выходов блока 4, поступающих соответственно на входы 115.2 - 115.4 триггеров 175 - 177 блока 5 и управляющих формированием 5 адресов соответственно второй, третьей и четвертой диагностических микропрограмм.

Элемент.И-НЕ 95 предназначен для формирования строба низкого уровня в 30 разряде 100.6 группы 34 выходов, поступающего на V-вход 115.5 регистра 104 адреса блока 5 для блокировки этого регистра, элемент ИЛИ 96 - для развязки сигналов сброса регистра 85, 35 элемент ИЛИ 97 - для формирования сигнала повторения микрокоманд, управляющего работой блока 10.

Одновибратор 98 служит для формирования импульса, по которому при четвертом повторении искаженной микрокоманды в одном из разрядов 100.1 - 100.4 формируется сигнал на переход к соответствующей диагностической микропрограмме.

Разряды 99.1 и 99.2 группы 36 вы- ходов блока 4 предназначены для подачи сигналов соответственно сброса и третьего повторения микрокоманды в разряды 83.1 и 83.2 группы 36 входов 50 блока 3. Разряд 99.1, кроме того, подается на вход 33 блока 13.

Разряды 101.1 - 101.3 группы 37 входов блока 4 предназначены для подачи сигналов соответственно 172.1 - 172.3 с .группы 37 выходов блока 13, разряды 102.1 - 102.4 группы 30 входов - для подачи соответственно восьН мого, девятого, первого и второго синхроимпульсов с выходов 62 блока

40

45

55

20

первой диагностической микроггрограм- мы.

Элементы И 92-94 служат для фор,5 ка 5 „ предназначенного для у„р„ле- н„, ф„р„„ро„ан„е„ начального адреса

мирования соответствующих разрядов 100.2-100.4 группы 34 выходов блока 4, поступающих соответственно на входы 115.2 - 115.4 триггеров 175 - 177 блока 5 и управляющих формированием 5 адресов соответственно второй, третьей и четвертой диагностических микропрограмм.

Элемент.И-НЕ 95 предназначен для формирования строба низкого уровня в 30 разряде 100.6 группы 34 выходов, поступающего на V-вход 115.5 регистра 104 адреса блока 5 для блокировки этого регистра, элемент ИЛИ 96 - для развязки сигналов сброса регистра 85, 35 элемент ИЛИ 97 - для формирования сигнала повторения микрокоманд, управляющего работой блока 10.

Одновибратор 98 служит для формирования импульса, по которому при четвертом повторении искаженной микрокоманды в одном из разрядов 100.1 - 100.4 формируется сигнал на переход к соответствующей диагностической микропрограмме.

Разряды 99.1 и 99.2 группы 36 вы- ходов блока 4 предназначены для подачи сигналов соответственно сброса и третьего повторения микрокоманды в разряды 83.1 и 83.2 группы 36 входов 0 блока 3. Разряд 99.1, кроме того, подается на вход 33 блока 13.

Разряды 101.1 - 101.3 группы 37 входов блока 4 предназначены для подачи сигналов соответственно 172.1 - 172.3 с .группы 37 выходов блока 13, разряды 102.1 - 102.4 группы 30 входов - для подачи соответственно восьН мого, девятого, первого и второго синхроимпульсов с выходов 62 блока

0

5

5

t 1

10. Вход 39 служит для подачи сигнала сброса с выхода блока 8.

Одновибратор 98 предназначен для формирования импульса, по которому при четвертом повторении искаженной микрокоманды в одном из разрядов 100.1 -100.4 формируется сигнал на переход к соответствующей диагностической микропрограмме.

Разряды 99.1 и 99.2 группы 36 выходов блока 4 предназначены для подачи сигналов соответственно сброса и третьего повторения микрокоманды в разряды 83.1 и 83.2 группы 36 входов блока 3. Разряд 99.1, кроме того, подается на вход 33 блока 13.

Разряды 101.1 - 101.3 группы 37 входов блока 4 предназначены для подачи сигналов соответственно 172.1- 172.3 с группы 37 выходов блока 13, разряды 102.1 - 102.4 группы 30 входов - для подачи соответственно восьмого, девятого, первого и второго синхроимпульсов с выходов 62 блока 10, вход 39 - для подачи сигнала сбрса с выхода блока 8.

Разряды 103.1 - 103.3 группы 38 входов блока 4 предназначены для подачи сигналов с разрядов соответст- 1зенно 80.1, 80.3 и 80.2 группы 38 выходов блока 3.

Блок 5 микропрограммного управления (фиг. 5) применяют для управления работой процессора соответствующего канала. В нем регистр 104 предназначен для хранения адреса очередной микрокоманды. Запись адреса в регистр происходит по первому синхр

импульсу, поступающему с выхода 62 .блока 10 на вход 114.2 5,при наличии разрешающего сигнала с входа 115.5. Группы входов D1 и D2 регистра 104 предназначены для подачи на него соответственно модифицируемой и немодифицируемой части кода адреса очередной микрокоманды.

Регистр 105 блока 5 предназначен для хранения кода операционной част очередной микрокоманды. Запись в этот регистр происходит при наличии синхроимпульса на входе 115.7, поступающего с выхода 100.5 блока 4 в момент появления первого синхроимпульса на выходе 62 блока 10.

Блок 106 памяти служит для хранения микропрограмм управления работо процессора соответствующего канала. Считывание из него разрешается сигн

10

15

25оо20

йа60523312

лом с входа 115,6, формируемым на выходе 100.7 блока 4,

Формирователь 107 адреса (фиг.13) предназначен для формирования адреса очередной микрокоманды. Шина 108 предназначена для подачи кода адреса на блок 106 памяти и на блок 6 контроля.

Разряды 109.1-109.3 группы 40 выходов блока 5 предназначены для подачи на блок 13 (фиг.12) сигналов со- ответственно 173.1 и 173.2 на уст анов- ку и сброс триггера -162 маскирования прерываний, а также сигнала 173.3 на сброс триггеров 163 и 164 блока 13.

С групп выходов 110.1 - 110.3 блока 106 памяти подаются коды немодифицируемых, модифицируемых разрядов адреса микрокоманды и код проверяемых логических условий соответственно. Через группу 111 выходов блока 106 выдается код операционной части микрокоманды.

Группа 112 выходов формирователя 107 адреса предназначена для подачи на регистр 104 модифицируемых разрядов кода адреса.

Группа 113 выходов регистра 105 предназначена для выдачи кода операционной части микрокоманды на объект управления через выход 41 (проце- сор) и в блок 6 через соответствую- шую группу разрядов выхода 42.

Разряды 114.1 и 114.2 группы 30 входов блока 5 предназначены для подачи соответственно второго и первого синхроимпульсов с выхода 62 блока 10.

Разряды 115.1 - 115.4 группы 34 входов предназначены для подачи сигналов сбоя блока микропрограммного управления (с выхода 100.1 блока 4), несовпадения кодов логических условий (с выхода 1.00.3 блока 4) и одновременного несовпадения данных и кодов логических условий при запрете прерывания (с выхода 100.4-блока 4), разряд 115.5 группы 34 входов - для подачи сигнала, формируемого на выходе 100.6 блока 4 и разрешающего запись в регистр 104, разряд 115.6 группы 34 входов - для подачи сигнала, формируемого на выходе 100.7 блока 4 и разрешающего считывание из блока 106, разряд 115.7 группы 34 входов - для подачи сигнала, формируемого на выходе 100.5 блока 4 и

30

35

40

45

50

55

13

предназначенного для разрешения записи в регистр 105.

Блок 6 контроля (фиг. 6) предназначен для контроля на четность информации, поступающей из блока 5. Входящие в.него сумматоры 116 - 118 по модулю два предназначены для конроля на четность информации, поступающей через входы 119.1 - 119.3 соответственно из регистра 104, блока 106 памяти и регистра 105 блока (фиг.5). При четности информации сумматор формирует нулевой-сигнал, а при нечетности - единичный сигна свидетельствующий об искажении информации. Выходы разрядов 120.1- 120.3 предназначены дпя выдачи сигнала ошибки в разряды соответственно 81.1 - 81.3 группы 31 входов блока 3 (фиг. 3).

Блок 7 останова (фиг. 7) предназначен дпя формирования сигналов сбрса, останова и прерывания. Элемент И 121 блока 7 предназначен для формирования сигнала прерывания в своем канале при появлении на входе 51 блока 7 сигнала прерывания от соседнего канала и работает только при синхронной работе каналов.

Элемент И 122 предназначен для формирования сигнала останова в процессе настройки при появлении сигналов .прерывания в своем или соседнем канале на входах 50 или 51 соответственно (фиг. 7).

Элемент ИЛИ 123 предназначен для формирования сигнала прерывания на выходе 46 блока 7,

Элементы ИЛИ 124 и 125 служат для формирования сигналов сброса на соответствующих выходах 47 и 48 блока 7 .

; Блок 8 задания режима .(фиг. 8) предназначен для управления режимами работы устройства, триггер 126 - для задания синхронной работы каналов устройства (в единичном состоянии) с выхода 54, элемент НЕ 127 - для формирования единичного п отен- циала.

Генератор 128 предназначен для формирования импульсов опорной частоты на выходе 56 при наличии еди- .ничного сигнала на его управляющем входе. Элементы 129 и 130 коммутации используются для формирования сигнала настройки и сигнала включени генератора 128 соответственно, эле10

t5

20

25

05233,14

менты 131 - 133 коммутации - для формирования сигналов установки триггера 126 в единичное состояние, сиг- нала сброса на выходе 39 и сигнала пуска распределителя тактовых импульсов на выходе 55 соответственно.

Блок 9 управления синхронизацией (фиг.9) предназначен для координации работы блоков своего канала, а также работы каналов между собой.

Триггер 134 фиксирует сигнал о завершении формирования одноименных микрокоманд в обоих каналах, триггер 135 фиксирует синхронную (зависимую) работу каналов, триггер 136 предназначен для управления торможением работы распределителя 10, при котором последний зацикливается на выдаче десятого синхроимпульса.

Триггеры 137 и 138 предназначены для формирования сигнала формирования одноименных микрокоманд в обоих каналах устройства, триггер 139 - для фиксации факта пуска своего канала в работу, триггер 140 - для фиксации факта завершения формирования микрокоманды в своем канале.

Коммутатор 141 предназначен для формирования на выходе 57 блока 9 сигнала разрешения сравнения данных, сформированных процессорами обоих каналов в. результате выполнения одноименных .-микрокоманд.

Элемент И 142 служит для управления триггером 134. При- появлении на выходе 35 сигнала повторения микрокоманды элемент по десятому синхроимпульсу с входа 148.1 устанавливает триггер 1 34 в - 1.

Элемент ЗАПРЕТ 143 предназначен для управления триггером 140, разрешая его установку в 1 лишь при отсутствии на входе 35 сигнала повторения микрокоманды в случае синхронной работы каналов.

Элемент И 144 предназначен для формирования на выходе 58 блока 9 сигнала согласования, поступающего через группу 16.1 (16.2) выходов канала на вход 61 блока 9 противопо- ложного канала и свидетельствующего о завершении процесса формирования микрокоманды в своем канале.

Элемент И 145 предназначен для. формирования сигнала завершения формирования одноименных микрокоман.ц в обоих каналах, элемент ИЛИ 146 - для формирования сигнала сброса тригге30

35

0

5

0

5

ipa 136, элемент 147 задержки - цля управления длительностью импульса на выходе элемента И 145,

Разряды 148.1 и 148.2 груп-пы входов 62 предназначены для подачи соответственно десятого и девятого синхроимпульсов с выхода 62 блока 10 Распределитель 10 тактовых импульсов () предназначен для формирования импульсов, синхронизирующих работу блоков канала в соотнетствии с временными диаграммами, изображенными на фиг.14.

Регистр 149 распределителя 10 (фиг. 10) предназначен для фиксации кодов состояний S1-S10 распределителя. Эти состояния соответствуют формированию первогр-десятого синхроимпульсов. Код состояния формируется на группе D-входов регистра и записывается в него при поступлении синхроимпульса на С-вход. При подаче сигнала на вход S9 регистр устанавливается в состояние

QtQiQ Q.

Преобразователь 150 кодов пред- .назначен для формирования сигналов возбуждений автомата, состоящего из регистра 149, преобразователя 150 и- дешифратора 151. Для кодирования десяти используемых состояний авто- мата выбран код Грея, в котором первое состояние имеет код 0001, а десятое - 0101. При подаче сигнала на вход 63 распределителя 10 автомат зацикливается на выдаче девятого- десятого тактовых импульсов.

Если входы триггеров (разрядов) регистра 149 обозначить через D,,

D, Г)з Г 4- а геров - через

состояния тригQI, О

2

О и

О d и

считать, что в первом состоянии S. 0001 триггеры имеют состояния: О ,0, Oq. 1, то функции возбуткдения , реализуемые преобразователем 150, j«ioHHo описать следующим образом:.

D, Q, Q4 V Q Q3

D Q Q- Q Q4 VQ2 Рзо(бз D, Q,V Q,VQ Q,o 63VQ2 Q3 D Q, Q4 VQ,

где Oil. 65 логическое значение сиг нала на входе 63. Дешифратор 151 преобразует коды состояний регистра 149 в синхроим0

5

0

5

0

5

0

5

0

5

пульсы на выходах разрядов группы 62 выходов распределителя л соответствии с диаграммами (фиг.14).

Элемент И 152 предназначен для формирования сигнала торможения распределителя тактовых импульсов на выдаче десятого синхроимпульса, элемент ИЛИ-ИЕ 153 - для управления записью кодов в регистр 149, группа 154 выходов преобразователя 150 - для передачи сигналов возбуждения на входы триггеров регистра 149. С выхода разряда 155 дешифратора 151 подается десятый синхроимпульс.

Рходы 56, 60.и 39 предназначены соответственно для подачи тактовых импульсов опорной частоты, сигнала торможения распределителя и сигнала сброса, устанавливающего регистр 149 в состояние 1001.

Блок 11 пуска (фиг. 11) предназначен для управления работой распре делителя 10 тактовых импульсов и блока 9 управления синхронизацией.

Триггер 156 предназначен для формирования на выходе 63 блока 11 сигнала зацикливания распределителя 10 на выдаче девятого - десятого синхроимпульсов, триггер 157 - для фиксации сигнала пуска своего канала, поступающего с входа 59, элемент И 158- для формирования сигнала на установку триггера 156 в 1, элемент И 159 - для формирования сигнала на установ- .ку триггера 150 в О девятому синхроимпульсу при наличии сигнала сброса на входе 47, элемент ИЛИ 160 с инверсным входом, подключенным к входу 54, предназначен для управления работой элемента И 158.

Разряды 161.1 и 161.2 группы 62 входов блока 11 предназначены для подачи соответственно девятого и десятого синхроимпульсов.

Блок 12 сравнения услоЬий имеет структу у, аналогичную блоку Z (фиг. 2) и предназначен для сравнения кодов логических условий, поступающих на входы 66 и 67 от процессоров своего и соседнего каналов соответственно.

Блок 13 задания режима диагностики (фиг. 12) предназначен для управления работой блоков 3, 4 и 7 на основе анализа условий несовпадения данных или логических условий.

Триггер 162 предназначен для маскирования прерываний путем формирования сигналов, разрешающих (в едиНйчном состоянии триггера) или запрещающих (в нулевом состоянии) формирование сигнала прерывания на выходе 50, триггеры 163 и 164 - для фиксации сигналов ошибки соответственно в логических условиях и в данных, поступающих на входы 65 и 24, по спаду сигнала на их синхровходах. Дешифратор 165 служит для управления повторением микрокоманд при сбое процессора на диагностическую микропрограмму, которая соответствует причинам сбоя. Выход 1 де

Дешифратор 178 предназначен для управления режимами, формирования адреса в соответствии с кодом логических условий, поступающим на группу входов 110.3 с соответствующих выходов блока 106 памяти.

При возбуждении выхода 1 дешис х- ратора адрес определяется кодом операции с входа 43. При возбуждении выходов 2, 3, 4 или 5 соответствующий шифратор 179,-180, 181 или 182 формирует адрес первой микрокоманды соответственно

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухканальное устройство для контроля и восстановления процессорных систем | 1986 |

|

SU1397917A1 |

| Устройство для отладки вычислительной системы | 1986 |

|

SU1336015A1 |

| Микропрограммное устройство управления | 1989 |

|

SU1633402A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Конвейерная система для программного управления | 1989 |

|

SU1665340A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

Изобретение относится к области автоматики и вычислительной технике и может быть использовано в процессорах с микропрограммным управлением. Цель изобретения - повышение достоверности и оперативности контроля. Цель достигается тем, что в известную совокупность узлов для контроля и восстановления, содержащего первый и второй каналы, каждый из которых включает блок сравнения данных, блок фиксации сбоев, блок повторения микрокоманд, блок микропрограммного управления, блок контроля, блок останова, блок задания режима, блок управления синхронизацией, распределитель тактовых импульсов и блок пуска, в каждый канал введены блок сравнения условий и блок задания режима диагностики. Сущность изобретения состоит в том, что в результате введения новых узлов и связей устройство приобретает способность сравнивать не только коды данных, но и коды логических условий, формируемые объектами контроля (процессорами). Поскольку коды логических условий несут дополнительную информацию о состоянии процессоров, то тем самым повышается достоверность контроля. 1 з.п. ф-лы, 14 ил.

шифратора управляет переходом на вто- 5 первой, второй, третьей или чет- рую диагностическую микропрограмму, вертой диагностической микропрограммы, выход 2 - на третью, выход 3 -

на четвертую..

Элементы И 166 и 167 предназначе20

ны дпя формирования соответственно сигнала прерывания и сигнала перехода на четвертую диагностическую микропрограмму при одновременной ошибке в данных и и логических условиях с учетом состояния триггера 162.

Элемент ЗАПРЕТ 168 предназначен дпя управления синхровходами триггеров 163 и 164, элемент ИЛИ 169 - для формирования сигнала сброса этих триггеров.

Разряды 171.1 - 171.3 группы 32 выходов предназначены для подачи сигналов в разряды соответственно 84.1 - 84.3 группы 32 входов блока 3.

Вход 33 блока предназначен для подачи сигнала сброса с выхода элемента ИЛИ 96 блока 4 (фиг. 4).

/

f

Разряды 172.1 - 172.3 группы 37 выходов предназначены для п9Дачи сигналов в разряды-соответственно 100.1 - 100.3 группы 34 входов бло-- ка 4, разряды 173.1 - 173.3 группы 40 входов - дпя подачи соответственно сигналов установки в 1 и в О триггера 162 и установки в О трих- геров 163 и 164. Эти сигналы формируются на выходах 109.1 - 109.3 регистра 105 блока 5 (фиг.5). Формиро- ватель 107 адреса (фиг. 13) предназначен для формирования адреса очередной микрокоманды блока 5 (фиг. 5).

Триггеры 174 - 177 формирователя 107 фиксируют сигналы перехода соответственно на первую, вторую, третью и четвертую диагностические микропрограммы.

25

Возбужденив: выхода 6 предопределяет передачу модифицируемых раз- рядов адреса с входом 110.2 через блок 183 элементов И без изменений. ; При возбужденииi-ro разряда группы выходов 7 на соответствующем элементе 185.1 .(i- 6 1,1, где 1 - чис- |по проверяемых условий) осуществляет- |ся проверка соответствующего логичес- iKoro условия с входов 66.

30

35

40

45

50

55

В режиме повторения микрокоманд после четвертого повторения по сигналу с соответствующего входа. 115.1 - J15.4 соответствующий т риггер 174 - 1177 устанавливается в , запирая сигналом с инверсного выхода через {элемент 191 дешифратор 178 и возбуждая сигналом с прямого выхода соот- ветствующий шифратор .179-182., Этот шифратор формирует .адрес первой микрокоманды соответствующей диагностической микропрограммы, который по очередному первому синхроимпульсу с входа 114,2 записывается в регистр 104 (фиг, 5). Далее по второму синхроимпульсу с входа 114,1 срабатывает соответствующий элемент И 186- 189, устанавливая в О соответствующий триггер, ранее установленный в 1. При этом отпирается шифратор 179,

Устройство работает следуюощм образом.

Основным в работе устройства является синхронная или асинхронная работа его каналов в режимах: А - пуска, Б - нормальной работы, повторения микрокоманд (В1 - при

Возбужденив: выхода 6 предопределяет передачу модифицируемых раз- рядов адреса с входом 110.2 через блок 183 элементов И без изменений. ; При возбужденииi-ro разряда группы выходов 7 на соответствующем элементе 185.1 .(i- 6 1,1, где 1 - чис- |по проверяемых условий) осуществляет- |ся проверка соответствующего логичес- iKoro условия с входов 66.

В режиме повторения микрокоманд после четвертого повторения по сигналу с соответствующего входа. 115.1 - J15.4 соответствующий т риггер 174 - 1177 устанавливается в , запирая сигналом с инверсного выхода через {элемент 191 дешифратор 178 и возбуждая сигналом с прямого выхода соот- ветствующий шифратор .179-182., Этот шифратор формирует .адрес первой микрокоманды соответствующей диагностической микропрограммы, который по очередному первому синхроимпульсу с входа 114,2 записывается в регистр 104 (фиг, 5). Далее по второму синхроимпульсу с входа 114,1 срабатывает соответствующий элемент И 186- 189, устанавливая в О соответствующий триггер, ранее установленный в 1. При этом отпирается шифратор 179,

Устройство работает следуюощм образом.

Основным в работе устройства является синхронная или асинхронная работа его каналов в режимах: А - пуска, Б - нормальной работы, повторения микрокоманд (В1 - при

сбое блока микропрограммного управ- .пения, В2 - при ошибке в логических условиях, РЗ - при ошибке в данных, В4 - при ошибке одновременно В данных и в логических условиях и запрете прерывания, В5 - при одновременной ошибке в данных и в логических -условиях и разрешенном прерывании) , Г - перехода к микродиагностике.

Работу устройства будем рассматривать на примере первого канала, называя второй канал противоположным

каналом. I

В режиме А первоначальное состояние блока 5 микропрограммного управления в обоих каналах таково, что триггеры 174 - 177 установлены в О, на выходах 110.1,.110.2.и 111 блока 106 (фиг. 5) присутствуют нулевые сигналы, а с группы 110.3 выдается код, который в соответствии с описанньпхг выше принципом действия формирователя 107 адреса предопределяет передачу кода операции с входа 19.1 на вход 112 регистра 104 в качестве начального адреса соответствующей микропрограммы (входы начальной установки не показаны).

С помощью элемента 131 коммутации и триггера 126 (фиг. 8) на выходе 54 блока 8 формируется сигнал, зaдaюпl й синхронную (при единичном уровне сигнала) или асинхронную (при нулевом уровне сигнала) работу каналов. В режиме А для синхронной работы каналов с помощью элемента 132 коммутации на выходе 39 блока 8 (фиг-. 8) формируется сигн ал, которым все триггеры блоков 3, 4, 6 и 9 устана зливаются в О, а регистр 149 распределителя 10 тактовых импульсов (фиг. 10) устанавливается в состояние S9 0111, предопределяя выдачу единичного сигнала в разряд девятого синхроимпульса на выходе 62 распределителя. Этим импульсом триггер 156 блока 11 устанавливается в О, при этом единичным сигналом с выхода 63 распределитель 10 зацикливается на выдаче девятого - десятого синхроимпульса.

С помощью элемента 130 коммутации запускается в работу генератор 128 блока о, формирующей тактовые импульсы опорной - частоты на выходе 56

35

50

блока 8, и распределитель 10 тактовых импул.ьсов формирует девятый - десятый синхроимпульсы на выходе 62. с При этом триггеры 135, 136, 140 и 137 блока 9 (фиг. 9) устанавливаются в 1, что приводит к выдаче единичного сигнала на выходе 60 блока 9 и торможению распределителя 10 на

10 выдаче десятого импульса.

Затем с помощью элемента 133 коммутации на выходе 55 блока 8 (фиг.8) - формируется сигнал пуска распределителя. Этот сигнал устанавливает в

J5 1 триггер 139 блока 9 (фиг. 9), обусловливая выдачу сигналов на выходах 57 - 59 этого блока.

При этом с выхода 58 блока 9 противоположного канала на вход 61

20 блока 9 рассматриваемого канала

(фиг. 9) поступает аналогичный сигнал, которым триггер 138 устанавливается в 1. Это приводит к выработке элементом И 145 импульса, ко25 торым триггеры 137 и 138 устанавли-. ваются в О, а триггер 134 устанавливается в 1, отбрасывая триггер 136 и снимая с выхода 60 сигнал торможения распределителя 10

30 (фиг. 10). Одновременно сигнал с вы- хода 59 блока 9 устанавливает в 1 триггер 157 блока 11, фиксируя факт запуска канала в работу. После этого элементом 133 коммутации снима- .ется сигнал пуска с выхода блока 8. Одновременно сигнал с выхода 59 блока 9 через выход 16.1 канала поступает на вход 64 блока 11 противо-- положного канала, а соответствующим

дд сигналом, сформированным противоположным каналом, устанавливается в 1 -триггер 156 блока 11 рассматриваемого канала, снимая с выхода 63 сигнал зацикливания распределителя 10.

45 Распределитель начинает вырабатывать . полную серию синхроимпульсов (с первого по десятый, фиг. 14), и канал

. переходит в режим Б.

Особенностью режима А в случае асинхронной работы каналов является присутствие на выходе- 54 блока 8 нулевого сигнала, вследствие чего не происходит установка в 1 триггеров 134 - 137 и 140 блока 9 (фиг. 9), не формируются сигналы на его выходах 60, 57 и 58 и не происходит тврможе- ние распределителя 10.

В режиме Б устройство реализует последовательность микрокоманд без

55

21

сбоев. При синхронной работе канало по первому синхроимпульсу, поступащему с разряда 114.2 группы 30 входов блока 5, в регистр 104записывается адрес очередной микрокоманды, сформированный формирователем 107 (фиг. 5). При этом на U-входе реги- ;стра присутствует разрешающий еди- ничный сигнал, сформированный эле- |ментом И-НЕ 95 в разряде 100.6 груп Iпы 34 выходов блока 4.

Одновременно сигналом с входа 115.7, сформированным коммутатором 86 в разряде 100.5 группы 34 выходов блока 4, в регистр 105 записы- вается код операционной части предыдущей микрокоманды с выхода 111 блока 106 памяти. Этот код подается через выход 14.1 канала на соответст- ,вующий процессор, обеспечивая выполнение в нём соответствующего набора микроопераций.

По второму синхроимпульсу, поступающему с выхода 62 распределителя 10 в разряд 102.4 входа 30 блока 4, коммутатор 87 формирует в разряде 100.7 группы 34 выходов блока 4 сигнал, который, поступая на разрешающий вход 115.6 блока 106 памяти, обеспечивает считывание кода очередной микрокоманды на внутренний выходной регистр этого блока. Этот код поступает на выходы 110 и 111 блока 106.

Одновременно второй синхроимпульс поступает с входа 53 блока 7 на выход 48. этого блока, устанавливая в блоке 9 триггеры -134, 135 и 140 в О.

По девятому синхроимпульсу,, пос тупающему из разряда 148.2 входа 62 блока 9, триггеры 135 и 136 устанавливаются в 1, подготавливая сигналом на выходе 60 распределитель 10 к торможению в случае рассогласования работы каналов.

По десятому синхроимпульсу, поступающему в разряд 148.1 входа 62 блока 9, триггер 140 (в случае отсутствия сигнала повторения микрокоманды на входе 35 блока 9) устанавливается в 1 , фиксируя завершение выполнения микрокоманды в своем канале. При этом с выхода 58 блока 9 на вход 61 блока 9 противоположного канала (в рассматриваемом случае - второго) через 16.1 подается сигнал согласования. В случае нор

60523322

мальной работы противоположного (второго) канала в этот момент от него должен поступать соответствующий сигнал и на вход 61 блока 9 рассматриваемого первого канала, который будет зафиксирован триггером 138. На выходе элемента И 145 сформируется импульс, которым триггеры 137 и

15

20

25

30

50

55

10 и 138 установятся в О, а триггер 134 - в 1, сбрасывая при этом в О триггер 136 и снимая тем самым с выхода 60 сигнал торможения распределителя 10. Этот же импульс, поступив на выход 57 блока 9, разрешит сравнение в блоках 2 и 12 кодов данных и логических условий, которые выработаны процессорами обоих каналов в результате выполнения микрокоманды. В случае совпадения этих кодов с приходом очередного первого синхроимпульса каналы перейдут к формированию очередной микрокоманды,как описано вьш1е.

В случае, если сигнал согласования от противоположного канала поступит на блок 9 с задержкой (например, из-за повторения микрокоманды в этом канале), работа опережающего канала тормозится благодаря наличию сигнала торможения на входе 60 распределителя 10. Оособенности асинхронной работы каналов в режиме Б аналогичны режиму А.

В процессе формирования микрокоманды блоком 6 произ водится контроль на четность информации, вырабатываемой блоком 5, а блоками 2 и 12 - сравнение результатов выполнения микрокоманды. При появлении ошибки канал переходит в режим. В.

В режиме В осуществляется повторение микрокоманды с целью анализа причин ошибки (сбой или отказ) и восстановления нормальной работы, если ошибка была вызвана сбоем. Ре- жим имеет пять модификаций (В1 - | В5) в зависимости от вида ошибки. В режим В1 канал переходит при ошибке в информации, вырабатываемой блоком 6. Если искажен код адреса на выходе 108 регистра 104, то формируется сигнал ошибки в разряде 120.1 вых.ода 45 блока 6, который фиксируется триггером 73 блока 3 по четвертому синхроимпульсу. Если искажена информация на выходах 110 блока 106 памяти, то формируется сигнал ошибки в разряде 120.2 выхода 45 блока 6,

35

40

45

23

1605233

который фиксируется триггером 74 блока 3 по шестому синхроимпульсу. Если искажена операционная часть микрокоманды на выходе 113 регистра 105, то формируется сигнал ошибки в разряде 120.3 выхода 45 блока 6, который фиксируется по второму синхроимпульсу на триггере 75 блока 3.

При установке триггеров 73, 74 или 75 блока 3 в 1 элемент ИЛИ 79 формирует сигнал Нет нормы, который по седьмому синхроимпульсу фиксируется триггером 76. Этот сигнал, поступая через шину 38 в блок 4, отпирает элемент И 88,вследствие чего восьмой синхроимпульс проходит через этот элемент и вызывает сдвиг в регистре 85 с установкой в 1 его первого разряда. Сигналом с .выхода этого разряда через элемент ИЛИ 97 i на выходе 35 блока 4 формируется единичный сигнал повторения микрокоманды .

Этим сигналом в блоке 9 запирается элемент ЗАПРЕТ 143 и отпирается элемент И 142. Поэтому по десятому синхроимпульсу триггер 140 не будет установлен в 1, как это было в режиме Б, а останется в О, и сигнал согласования на выходе 58 блока 9 не будет сформирован. При этом произойдет торможение соседнего канала на данной микрокоманде.Триггер 134 по десятому синхроимпульсу, в отли- . чие от режима Б, установится в 1 и сбросит в О триггер 136, сНяв при этом сигнал торможения с выхода 60. Распределитель тактовых импульсов начнет формировать новую серию из десяти импульсов, в течение которой повторится рассмотренный выше - процесс формирования той же самой микрокоманды.

Этот процесс может повторяться до трех раз, причем переход в нормальный режим возможен лишь при устранении ошибки, т.е. при установке в О соответствукш;его триггера 73-75 блока 3. При этом становится нулевым сигнал Нет нормы на выходе элемента ИЛИ 79, который через выход 38 блока 3 запирает в блоке 4 элемент И 88, предотвращая подачу импульсов сдвига на регистр 85. Этим сигналом в блоке 4 отпирается элемент ЗАПРЕТ. Чррез него по восьмому синхроимпульс :)Jreмeнт( ИЛИ 96 формируется сигнал 1-Проса. Этим сиг нллом регистр 85

5233

24 О

0

5

0

5

0

5

0

устанавливается в О, формируя через элемент ИЛИ 97 нулевой сигнал на выходе 35 блока 4. Этим же сигналом сброса через выход 36 блока 4 устанавливается в О триггер 76 блока 3. Далее (по девятому и десятому синхроимпульсам) канал завершает работу так же, как и в режиме Б, и с началом новой серии синхроимпульсов работает в этом режиме.

Если в течение трех повторений микрокоманды ошибка не устранена, то после третьего повторения с выхода третьего разряда регистра 85 в разряд 99.2 шины 36 поступает единичный сигнал. Этим сигналом в блоке 3 отпирается блок 77 элементов И и по десятому синхроимпульсу через него на выход 29 блока 3 и далее - на выход 15.1 канала - выдается код состояния канала, который поступает в процессор соответствующего канала и может использоваться для диагностики. Канал переходит в режим 1. Этот же сигнал, поступая на элемент ИЛИ 78, предотвращает возврат канала в режим Б при работе в режиме Г.

В режимах В2 или ВЗ канал оказывается при появлении сигналов ошибки в логических условиях или в данных. Эти сигналы могут быть сформированы на выходах 65 или 24 блоков 12 или 2 соответственно по импульсу разрешения сравнения с выхода 57 блока 9. По спаду этого импульса сигнал ошибки в логических условиях записывается в триггер 163, а сигнал ошибки Ё данных - в триггер 164 блока 13.

При ошибке только в логических условиях возбудится выход 1 дешифратора 165, а при ошибке только в данных - его выход 2, формируя

единичные сигналы в разрядах соответственно 171.2 и 171.3 выхода 32 блока 13, а также в разрядах 172.2 и 172.3 его выхода 37. Поступая на элемент ИЛИ 79 блока 3, сигналы с выхода 32 блока 13 формируют единичный сигнал на выходе этого элемента. Далее работа канала аналогична режиму В1, с тем лишь отличием, что возврат к нормальной работе (в режим Б) ч случае устранения ошибки в данных или в логических условиях происходит за счет снятия единичного сигнала с соответствующего разряда выхода 32 блока 13. Сигналы с

25

выхода 37 блока 13 используются в блоке А в случае перехода из режима

/ ТТлоИЧПг

В/ (, BJ ; В режим Г .

В режимы В4 и В5 канал переходит в случае появления ошибки одновременно .как в данных, так и в логических условиях. При этом возбуждается выход 3 дешифратора 165 блока 13, отпирая один из элементов И 166 или 167, в зависимости от состояния триггера 162 маскирования прерываний.

Если прерывание запрещено, что соответствует режиму В4, то еди- ничный сигнал с выхода элемента И 167 поступит в разряды 171.1 и 172.1 выходов соответственно 32 и 37 блока 13, и канал перейдет к повторению микрокоманды аналогично тому, как |Это бьшо в режимах В2 или ВЗ. I Если прерывание разрешено, что соответствует режиму В5, то еди- 1НИЧНЫЙ сигнал с выхода 170 элемента 1И 166 поступит на выход 50 блока 13. вследствие чего на выходе 46 блока 7 появится сигнал прерывания. Этот сигнал через выход 18.1 (18.2) канала поступит в соответствующий продессор, возбуждая, например переход на программу диагностики. Одновременно этот сигнал поступает через выход 16.1 (16,2) канала на вход 51 блока 6 противоположного канала. При синхронной работе каналов это приводит к выдаче сигнала прерывания этим блоком.

Завершается режим В5 переходом в режим Б при установке триггеров

одновибратор 98 формирует импульс.

10

15

20

25

30

35

который,, прохбдя через один из эле ментов 91, 92, 92 или 94, поступае в соответствующий разряд выхода 34 блока 4 и устанавливает в 1 соот ветствующий триггер 174, 175, 176 или 177 формирователя 107 блока 5 Режиму В1 соответствуют элементы И 9 1 и триггер 174, режимы В2

tioofffTr /ti

cj и К4 соответственно элемент И 92-94 и триггеры 175-177, Таким образом на выходе 112 формировател 107 формируется адрес первой микро команды соответствующей диагностической микропрограммы.

Одновременно нулевым сигналом инверсного выхода четвертого разря да регистра 85 блока 4 запирается элемент И-НЕ 95, снимая запрет на запись информации в регистр 104 бл ка , 5 ,

При пятом повторении единичным сигналом с выхода пятого разряда регистра 85 блока 4 отпирается элемент И 89, благодаря чему по девято му синхроимпульсу на выходе элемента ИЛИ 96 формируется сигнал Сброс Им устанавливается в О регистр 85 блока 4, а через выход 36 блока 4 устанавливаются в нуль триггеры 73- 76 блока 3 и триггеры 163 и 165 бло ка 13, Тем самым канал переводится режим нормального функционирования (режим в), в котором начинает выполняться диагностическая микропрограмма.

Остановка работы устройства возможна путем формирования сигнала сб

- - - - 4 -t i-irJjJi i Ctiiri. O-J J d

IbJ и 164 блока 13 по сигналу сброса, Q са на выходе 39 блока 8. Его дейсткоторый может поступить или с выхода 39 блока 8, или из разряда 173.3 входа 40 блока 13.

В режиме Г осуществляется четвертое и пятое повторения процесса формирования микрокоманды, в течение которых происходит переход к одной из четырех диагностических микропрограмм. Каждая из них соответствует одному из режимов В1 - В4, а именно тому из них, от которого произошел переход к режиму Г. При этом возврат канала в режим Б предотвращается единичным сигна.-i.oM с выхода третьего разряда регистра 85 блока 4.

При четвертом noHTopef;iur микрокоманды по едини1;гн(1му cHrii;i,ny с выхода четвертого разряда регистра 85

вие на схему рассмотрено при описании режима А. При этом дополнител но к описанному устанавливаются в О триггер 139 блока 9 и триггеры- 45 157 и 156 блока 11, в результате чего сигналы на выходах 58 и 59 блока 9 принимают нулевое значение, а сигнал на выходе 63 блока 11 - единичное значение, вызывая зацикливание 5Q распределителя 10 на девятом - десятом синхроимпульсе. Одновременно нулевой сигнал с выхода 59 блока 9., поступая на вход 64 блока 11 противоположного канала, вызывает установ 2 ку в О триггера 156 этого блока и зацикливание распределителя 10 этого канала.

При настройке устройства остановка его работы может ос тествлятьс я

160523326

одновибратор 98 формирует импульс.

10

5

0

5

0

5

который,, прохбдя через один из элементов 91, 92, 92 или 94, поступает в соответствующий разряд выхода 34 блока 4 и устанавливает в 1 соответствующий триггер 174, 175, 176 или 177 формирователя 107 блока 5. Режиму В1 соответствуют элементы И 9 1 и триггер 174, режимы В2,

tioofffTr /ti

cj и К4 соответственно элементы И 92-94 и триггеры 175-177, Таким образом на выходе 112 формирователя 107 формируется адрес первой микрокоманды соответствующей диагностической микропрограммы.

Одновременно нулевым сигналом с инверсного выхода четвертого разряда регистра 85 блока 4 запирается элемент И-НЕ 95, снимая запрет на запись информации в регистр 104 блока , 5 ,

При пятом повторении единичным сигналом с выхода пятого разряда регистра 85 блока 4 отпирается элемент И 89, благодаря чему по девятому синхроимпульсу на выходе элемента ИЛИ 96 формируется сигнал Сброс, Им устанавливается в О регистр 85 блока 4, а через выход 36 блока 4 устанавливаются в нуль триггеры 73- 76 блока 3 и триггеры 163 и 165 блока 13, Тем самым канал переводится в режим нормального функционирования (режим в), в котором начинает выполняться диагностическая микропрограмма.

Остановка работы устройства возможна путем формирования сигнала сбро - - - 4 -t i-irJjJi i Ctiiri. O-J J d

Q са на выходе 39 блока 8. Его действие на схему рассмотрено при описании режима А. При этом дополнительно к описанному устанавливаются в О триггер 139 блока 9 и триггеры- 157 и 156 блока 11, в результате чего сигналы на выходах 58 и 59 блока 9 принимают нулевое значение, а сигнал на выходе 63 блока 11 - единичное значение, вызывая зацикливание распределителя 10 на девятом - десятом синхроимпульсе. Одновременно нулевой сигнал с выхода 59 блока 9., поступая на вход 64 блока 11 противоположного канала, вызывает установ- ку в О триггера 156 этого блока и зацикливание распределителя 10 этого канала.

При настройке устройства остановка его работы может ос тествлятьс я

дополнительно в случае появления сигнала прерывания на входе 50 блока 7. Лпя этого с помощью элемента 129 коммутации блока 8 на выходе 52 блока формируется сигнал, отпирающий элемент И 122 блока 7 и разрешающий выдачу сигнала прерывания на выход 47 блока 7 в качестве сигнала сброса.

Формула изобретения

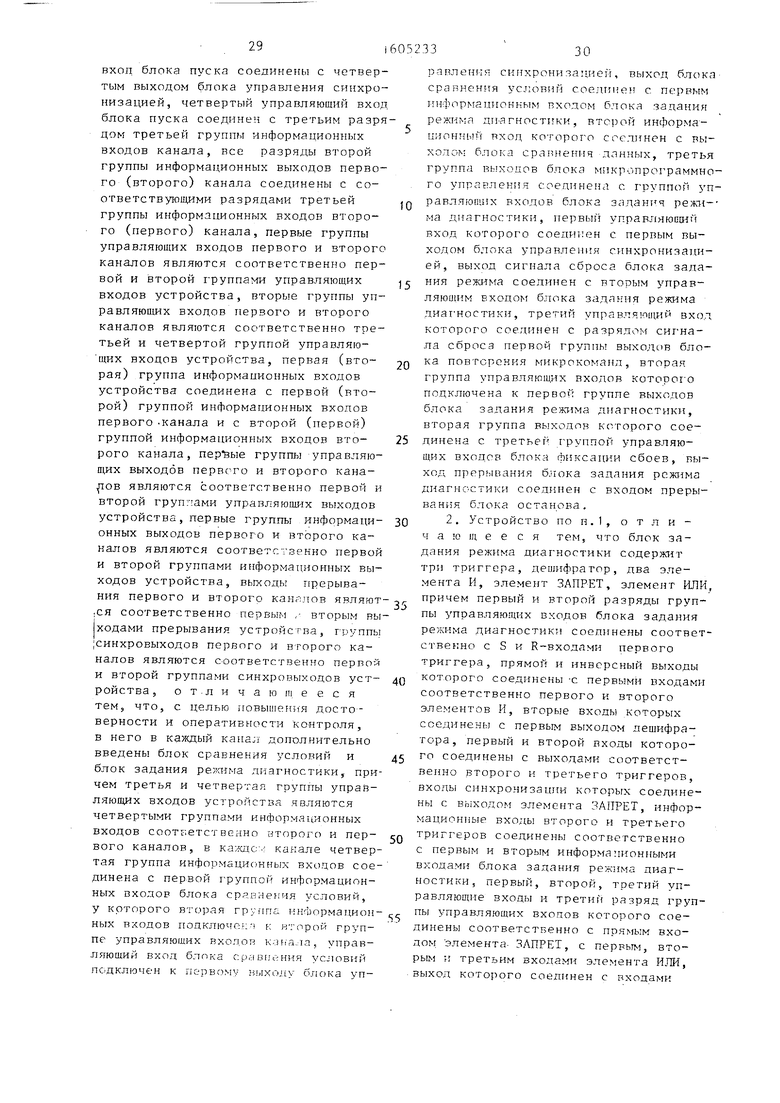

блока повторения микрокоманд соединен с выходом сигнала блока зацания режима, yпpaвляюnI й выход блока пов торения микрокоманд соединен с входом повторения микрокоманды блока управления синхронизацией, выход сигнала настройки блока задания режима соединен с входом настройки блока останова, выход сигнала сброса блока задания режима соединен с входами сброса распределителя тактовых импульсов, блока управления синхронизацией и блока останова, выход пуска блока задания режима соединен с первым информационным входом блока управления синхронизацией, выход опорной частоты блока задания режима соединен с входом опорной частоты распределителя так- ,товых импульсов, выход синхронной работы блока задания режима соединен с первыми управляющими входами блока останова, блока управления синхронизацией и блока пуска, первая и вторая группы информационных входов канала соединены соответственно с первой и второй группами информационных входов блока сравнения данных управляющий вход которого подключен к первому выходу блока управления синхронизацией, второй выход которого соединен с первым управляющим входом распределителя такто в ых импульсов, второй управляющий вход блока останова соединен с первым разрядом третьей группы информационных входов канала, первый выход блока останова соединен с выходом прерывания канала и с первым разрядом второй группы информационных выходов канала, второй выход блока останова 1 соединен с вторыми управляющими вхо- 1дами блока управления синхр онизацией и блока-пуска, третий выход блока останова соединен с третьим управляющим, входом блока управления синхронизацией, четвертый управляющий вход которого соединен с вторым разрядом третьей группы информационных входов :канала, пятый управляющий вход блока управления синхронизацией соединен с выходом блока пуска и вторым управляю дим входом распределителя тактовых импульсов, третий выход блока управления синхронизацией соедине с вторым разрядом второй группы информационных выходов канала, третий разряд которой и третий управляющий

29

вход блока пуска соединены с четвертым выходом блока управления синхронизацией, четвертый управляющий вхо блока пуска соединен с третьим разрдом третьей группы информационпых входов канапа, все разряды второй группы информационных выходов первого (второго) канала соединены с со- ответствую1дими разрядами третьей группы информационных входов второго (первого) канала, первые группы управляющих входов первого и второго каналов являются соответственно первой и второй группами управляющих входов устройства, вторые группы управляющих входов первого и второго каналов являются соответственно третьей и четвертой группой управляю- щих входов устройства, первая (вто- рая) группа информационных входов устройства соединена с первой (второй) группой информационных входов первого .канала и с второй (первой) группой информационных входов вто- рого канала, пер вые группы управляющих выходов первого и второго кана- (IOB являются соответственно первой и второй группами управляющих выходов устройства, первые группы информаци- онных выходов первого и второго каналов являются соответственно первой и второй группами информационных выходов устройства, выходы прерывания первого и второго каналов являют ся соответственно первым , вторым выходами прерывания устройства, группы ;синхровыходов первого и второго каналов являются соответственно первой и второй группами синхровыходов уст- ройства, о т-л и ч а ю ш е е с я тем, что, с целью повыше ци-я достоверности и оперативности контроля, в него в каждый канал дополнительно введены блок сравнения условий и блок задания диагностики, причем третья и четвертая группы управляющих входов устройства являются четвертыми группами информационных входов соотг.етствеино нторого и пер- вого каналов, в каящс :: канале четвертая группа информационных входов соединена с первой группой информационных входов блока ср и неиия условий, у которого вторая группа информационных входов подключен ) к второй rpvn- пе управляющих входов кзиа.:-1а, управляющий вход блока ср.-:1В1 йния условий подключен к первому выходу блока уп

«пс 2о 25 ЗО г 4045 п

60523330

ракления синхронизацией, выход блока сравнения условий соед1 иен с первым инфopмaпиoнны входом блока задания режима ди-а гностики, второй информационный вход которого соединен с выходом блока сравнения данных, третья группа выходов блока микропрограммного упрлрдения соединена с группой управляющих входов блока заданг я режи-- ма диагностики, первый управляюпщй вход которого соединен с первым выходом блока управления синхронизацией, выход сигнала сброса блока задания режима соединен с вторым управляющим входом блока задания режима диат ностики, третий управляющий вход которого соединен с разрядом сигнала сброса первой группы выхо,дс В блока повторения микрокоманд, вторая группа управляющих входов которог о подключена к первой группе выходов блока задания режима диагностики, вторая группа выходов которого соединена с третьей г руппой управляющих входов блока фиксации сбоев, выход прерывания блока задания режима диагностики соединен с входом прерывания блока останова,

5

сброса второго и третьего триггеров, выход первого элемещ а И соединен с инверсным входом элемента ЗАПРЕТ и является выходом прерывания блока задания режима диагностики, первая

и вторая группы выходов которого образованы вторым и третьим выходами дешифратора и выходом второго элемента И.

30

31

Ш

801

7J

St. Ы4

т.с

7

и

36

т

W

э

75

j({ о

Фиг.1

38

Н7

19

П

-ЕЦВ

жю

.

25

Фиг.

30

J

fiZ

ш

14

1Ш

5 5/

т

Настройка

I

L.

5

т

1П

т

Фцг.б

т

7

12h

Г25

Фиг.7

Щиг.8

iilo

se

W

о4705

161Г

ззи

Фиг. 10

т

3

75

fX(

oSJ

..J

Л

3at4UKjnj6aweТорможение

на С

Фиг. 11{

| Усольцев А.Г., Кислин Б.П | |||

| Сопряжение дискретных каналов связи с ЭВМ | |||

| - М.:,Связь, 1973, с | |||

| Рогульчатое веретено | 1922 |

|

SU142A1 |

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-11-07—Публикация

1988-12-26—Подача