;

(Л

JW

контроля на четность, блок 8 останова, блок 9 задания режима, распределитель 11 тактовых импульсов, блок 12 пуска, введен второй канал 2 и в каждый канал дополнительно введены блок 3 сравнения данных, блок 4 фиксации сбоев, блок 5 повторения микрокоманд 5 и блок 10 управления синхронизацией В результате введения новых узлов и связей конструкция двухканального устройства лля контроля и восстановления процессорных систем обеспечивает контроль информации, обнаружение сбоя (отказа) и организует повторение микрокоманды, а в случае необходимости переход на микропрограмму диагностики отказа. Кроме того, обеспечивается согласование и взаимосинхронизация работы каналов устройства в составе двухканального комплекса, достигается расширение области применения устройства. 1 з.п. ф-лы, 13 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и восстановления вычислительного процесса | 1988 |

|

SU1605233A1 |

| Устройство для отладки вычислительной системы | 1986 |

|

SU1336015A1 |

| Устройство для синхронизации вычислительной системы | 1985 |

|

SU1684785A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Конвейерная система для программного управления | 1989 |

|

SU1665340A1 |

| Устройство управления микропроцессором | 1983 |

|

SU1156072A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1381506A1 |

| Устройство для программного управления и контроля | 1985 |

|

SU1280574A1 |

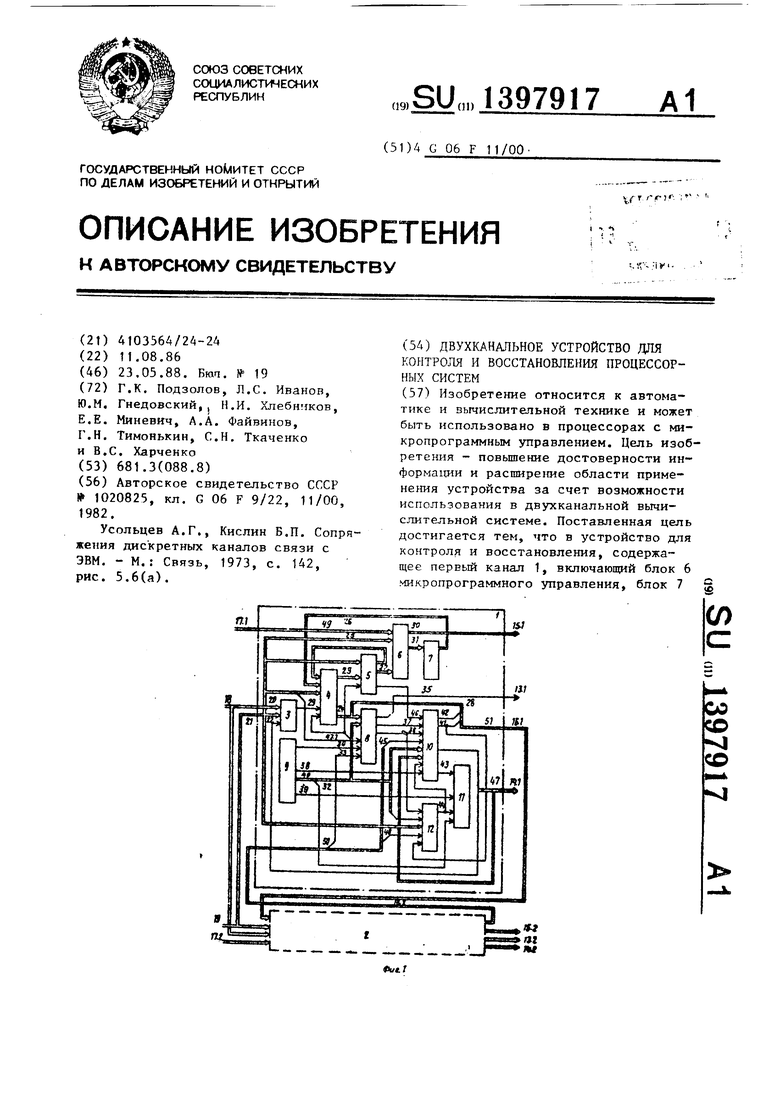

Изобретение относится к автоматике и вычислительной технике и может быть использовано в процессорах с микропрограммным управлением. Цель изобретения - повышение достоверности информации и расширезше области применения устройства за счет возможности использования в двухканальной вычислительной системе. Поставленная цель достигается тем, что в устройство для контроля и восстановления, содержащее первый канал 1, включающий блок 6 микропрограммного управления, блок 7 о

Изобретение относится к автоматике и вычислительной технике и может быть использовано в процессорах с микропрограммным управлением.

Цель изобретения - повышение достоверности контроля и расширение области применения устройства за счет возможности использования в двухка- нальной вычис;штельной системе.

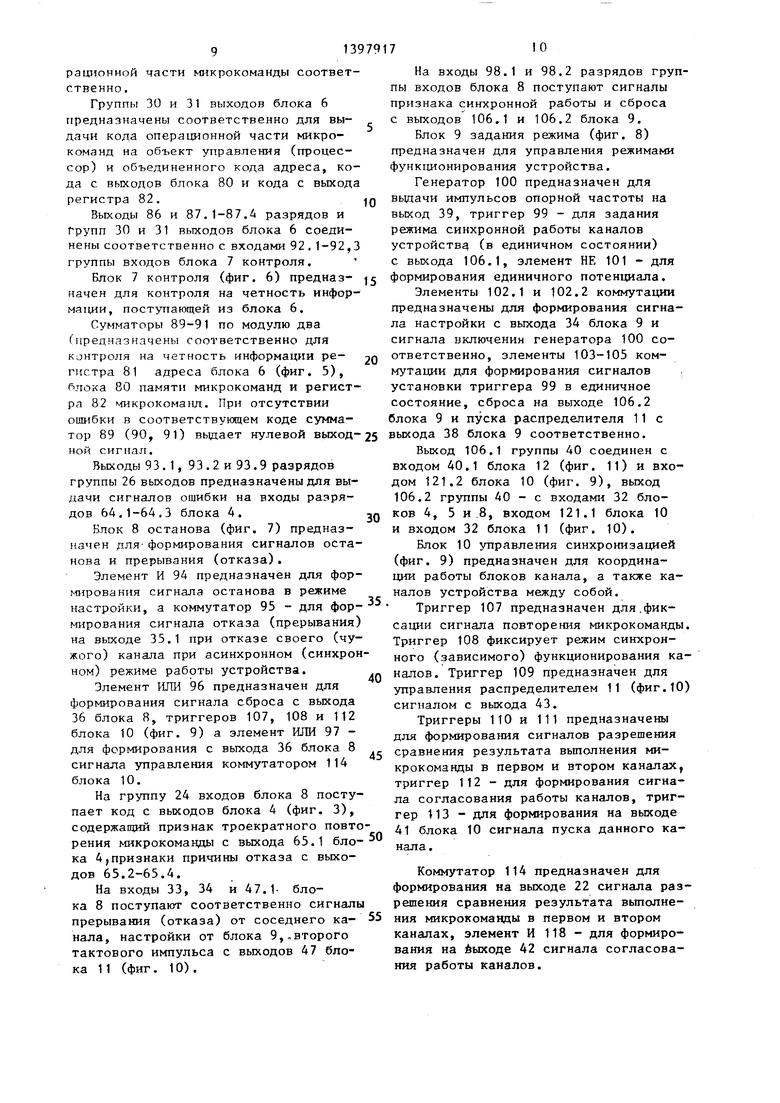

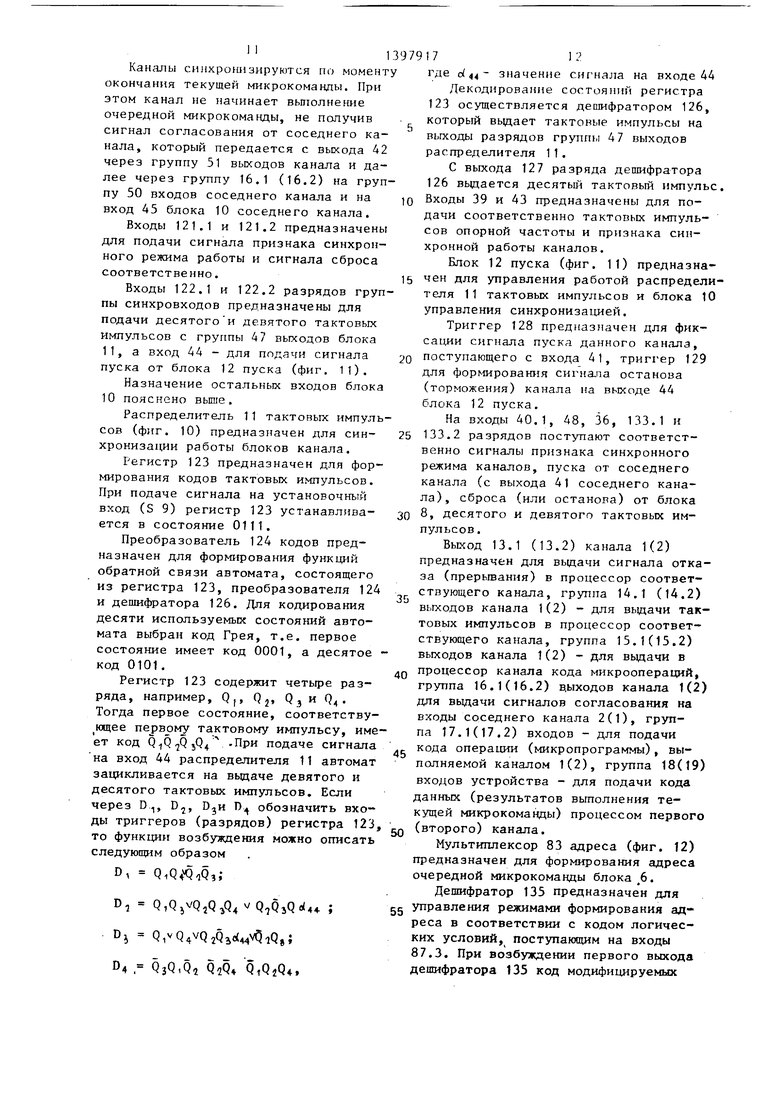

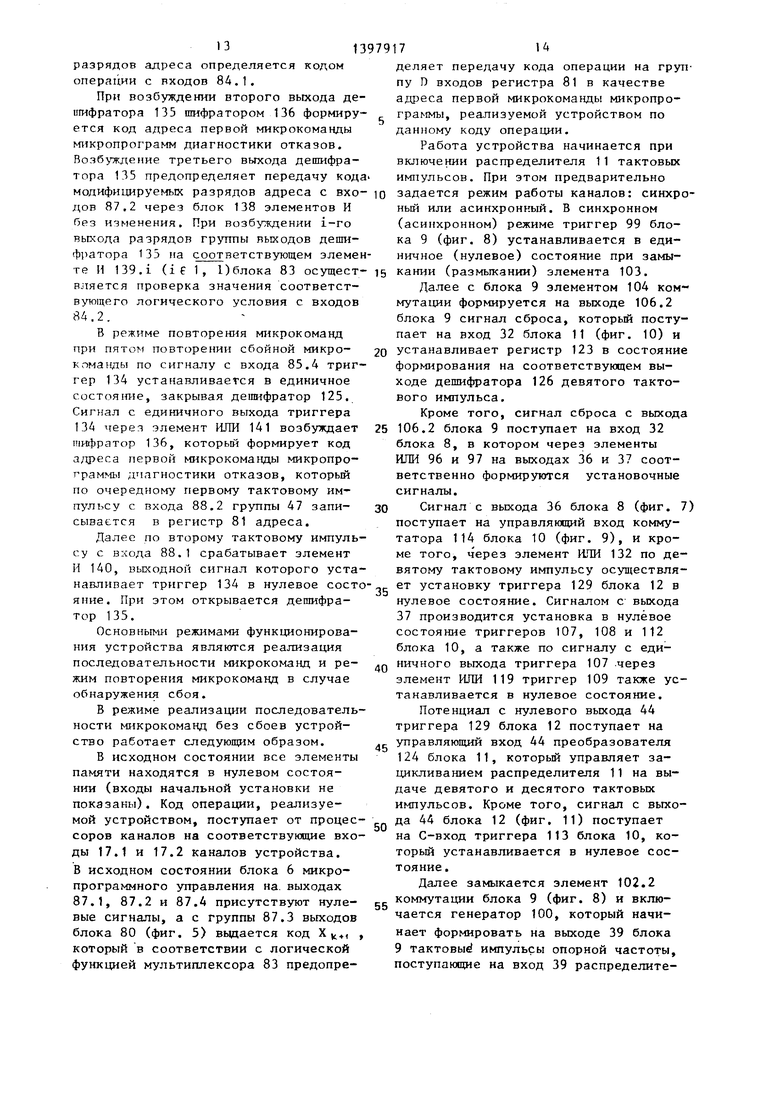

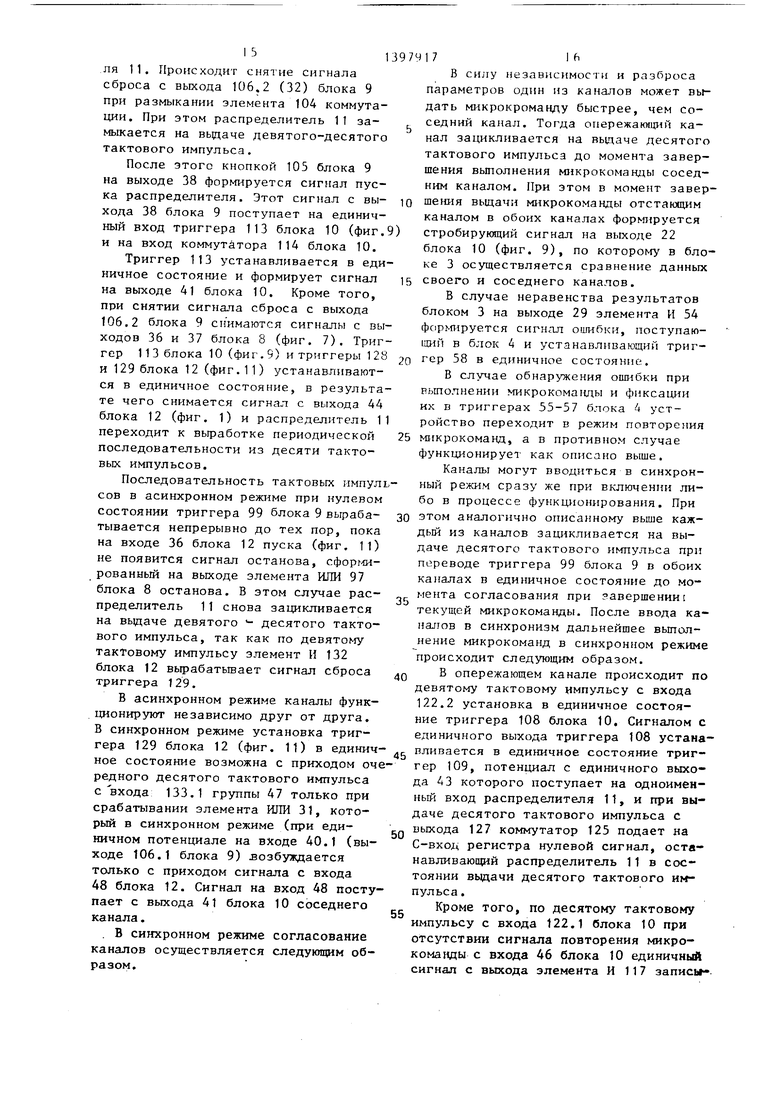

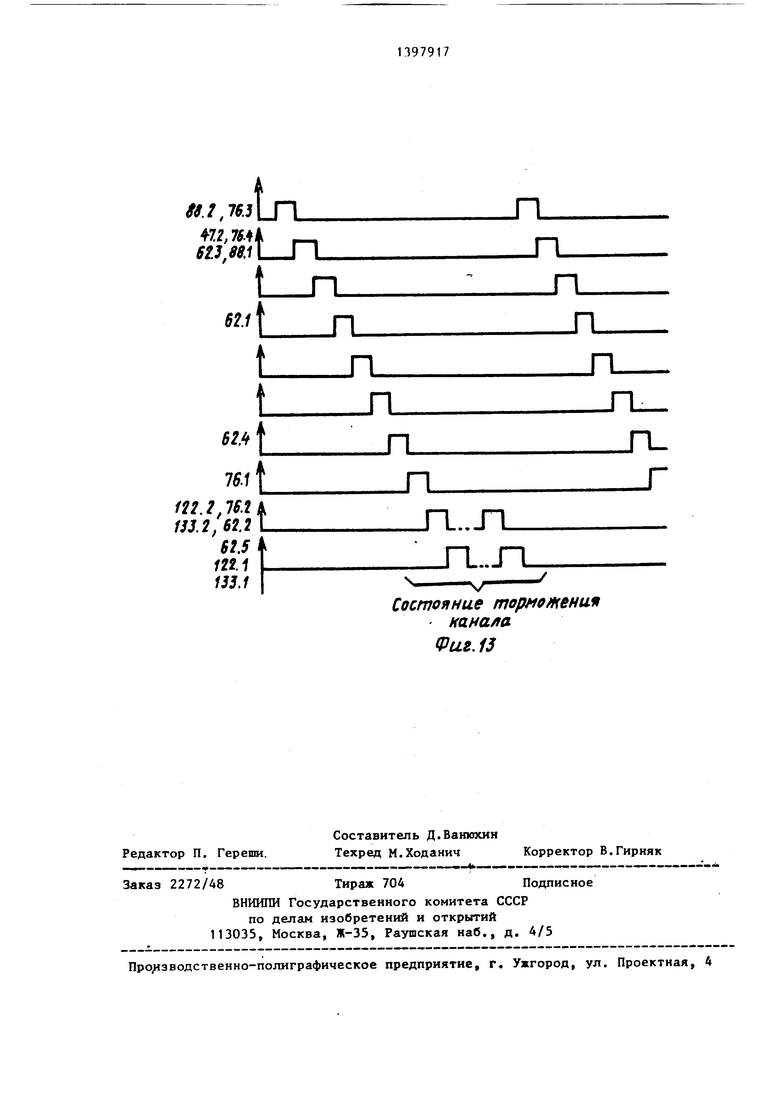

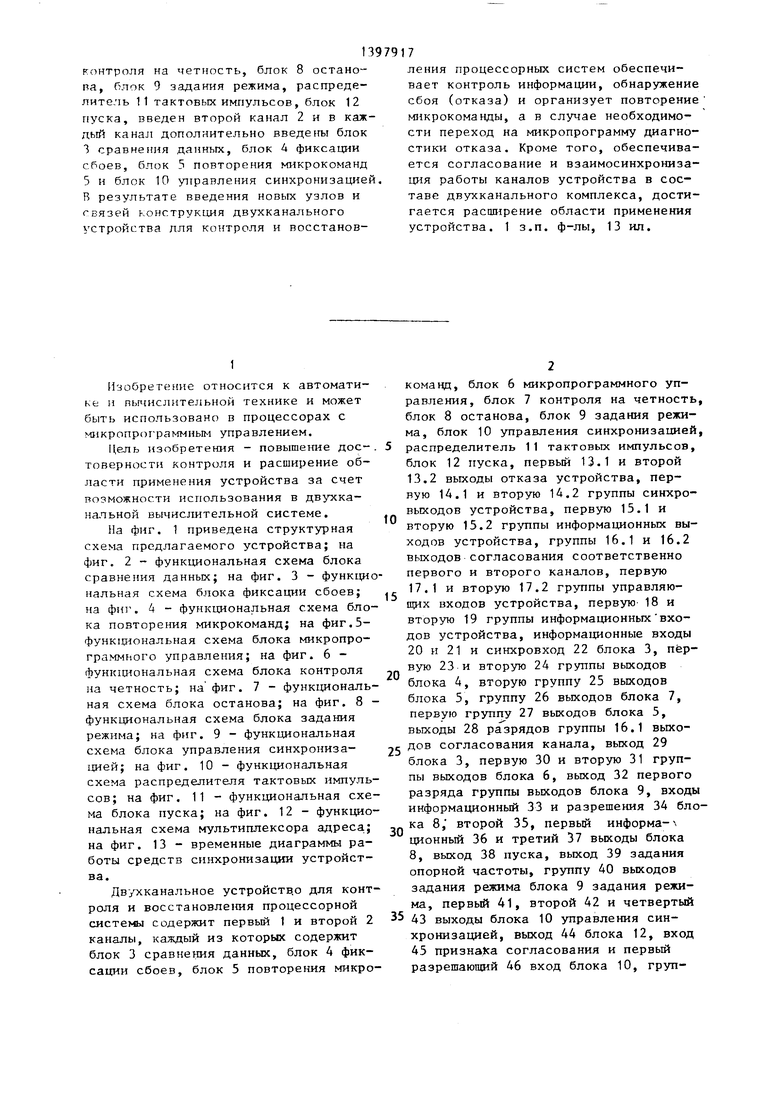

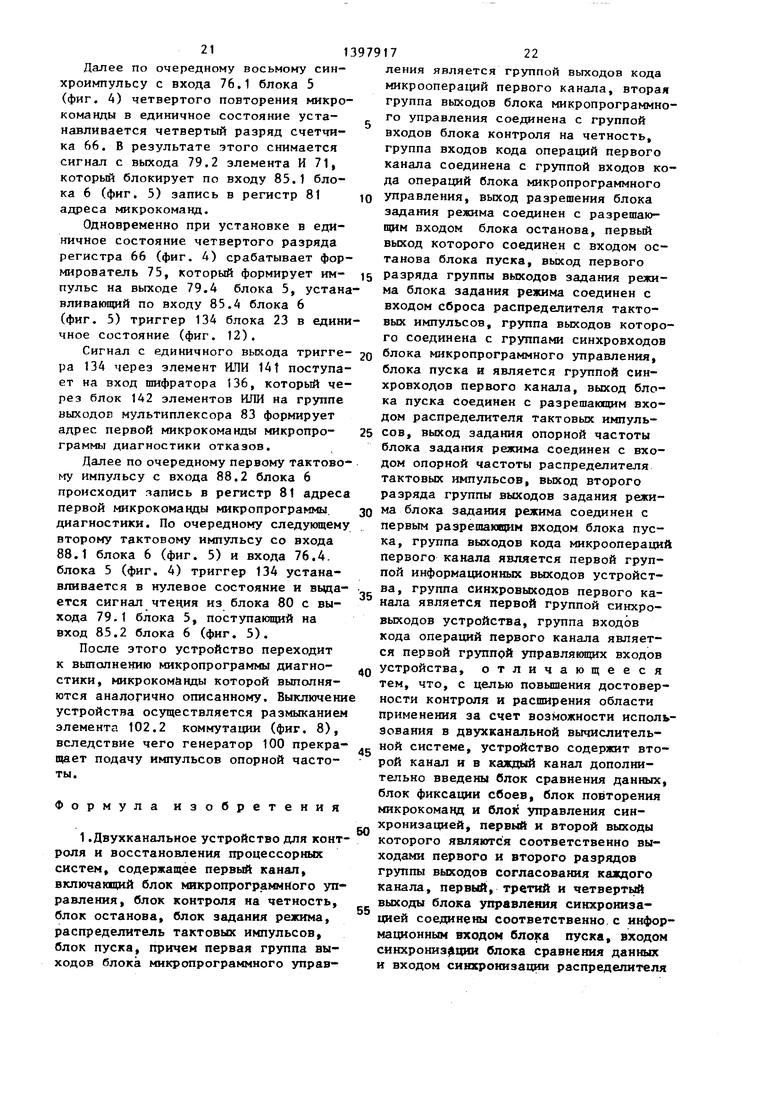

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг, 2 - функциональная схема блока сравнения данных; на фиг. 3 - функгц о нальная схема блока фиксации сбоев; на фиг. 4 - функциональная схема блока повторения микрокоманд; на фиг.5- функгщональная схема блока микропрограммного управления; на фиг. 6 - функш-юнальная схема блока контроля на четность; на фиг. 7 - функциональная схема блока останова; на фиг. 8 - функциональная схема блока задания режима; на фиг. 9 - функциональная схема блока управления синхронизацией; на фиг. 10 - функциональная схема распределителя тактовых импульсов; на фиг. 11 - функциональная схема блока пуска; на фиг. 12 - функциональная схема мультиплексора адреса.; на фиг. 13 - временные диаграммы работы средств синхронизации устройства.

Двухканальное устройство для контроля и восстановления процессорной систе в 1 содержит первый 1 и второй 2 каналы, каждый из которых содержит блок 3 сравнения данных, блок 4 фиксации сбоев, блок 5 повторения микро

5

0

5

0

5

команд, блок 6 микропрограммного управления, блок 7 контроля на четность, блок 8 останова, блок 9 задания режима, блок 10 управления синхронизацией, распределитель 11 тактовых импульсов, блок 12 пуска, первый 13.1 и второй 13.2 выходы отказа устройства, первую 14.1 и вторую 14.2 группы синхро- выходов устройства, первую 15.1 и вторую 15.2 группы информационных выходов устройства, группы 16.1 и 16.2 выходов согласования соответственно первого и второго каналов, первую 17.1 и вторую 17.2 группы управляющих входов устройства, первую 18 и вторую 19 группы информационных входов устройства, информационные входы 20 и 21 и синхровход 22 блока 3, первую 23 и вторую 24 группы выходов блока 4, вторую группу 25 выходов блока 5, группу 26 выходов блока 7, первую группу 27 выходов блока 5, выходы 28 разрядов группы 16.1 выходов согласования канала, выход 29 блока 3, первую 30 и вторую 31 группы выходов блока 6, выход 32 первого разряда группы выходов блока 9, входы информационный 33 и разрешения 34 блока 8, второй 35, первый инфopмa- ционный 36 и третий 37 выходы блока 8, выход 38 пуска, выход 39 задания опорной частоты, группу 40 выходов задания режима блока 9 задания режима, первый 41, второй 42 и четвертый 43 выходы блока 10 управления синхронизацией, выход 44 блока 12, вход 45 признака согласования и первый разрешающий 46 вход блока 10, группу 47 выходов распределителя П, второй разрешающий вход 48 блока 12, группу 49 входов кода операций, группу 50 входов согласования канала и группу 51 выходов согласования канала .

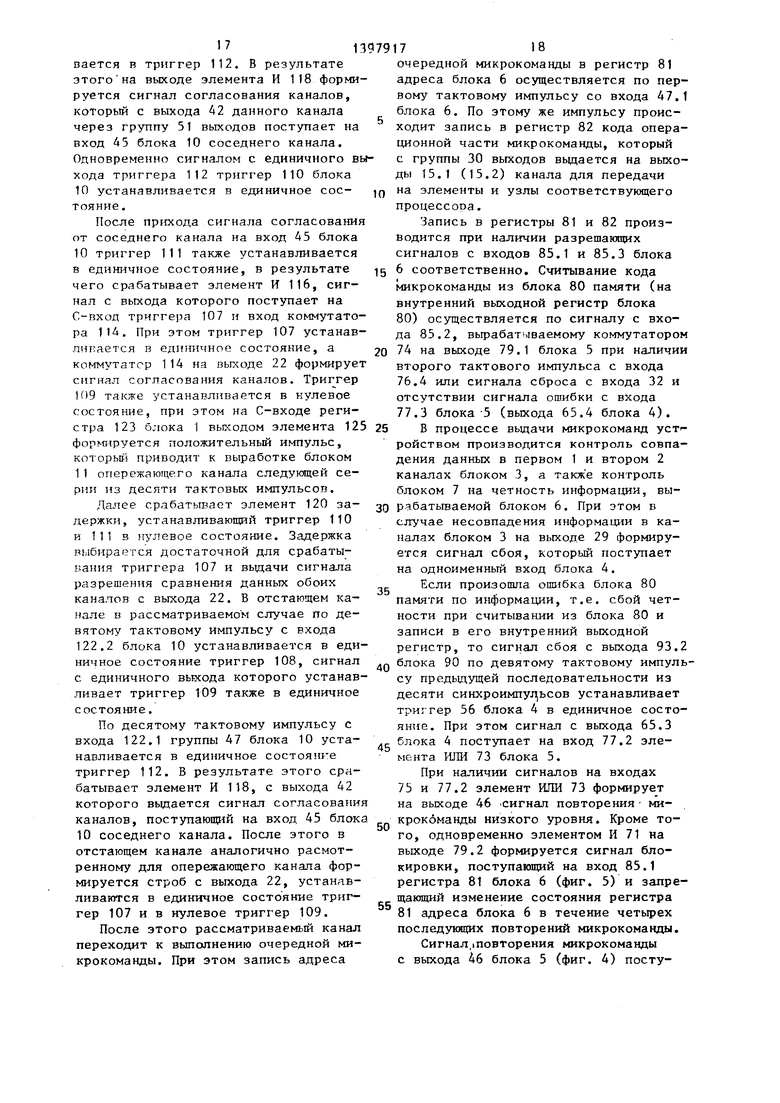

Блок 3 сравнения данных (фиг. 2) содержит регистр 52, схему 53 сравнения и элемент Н 54.

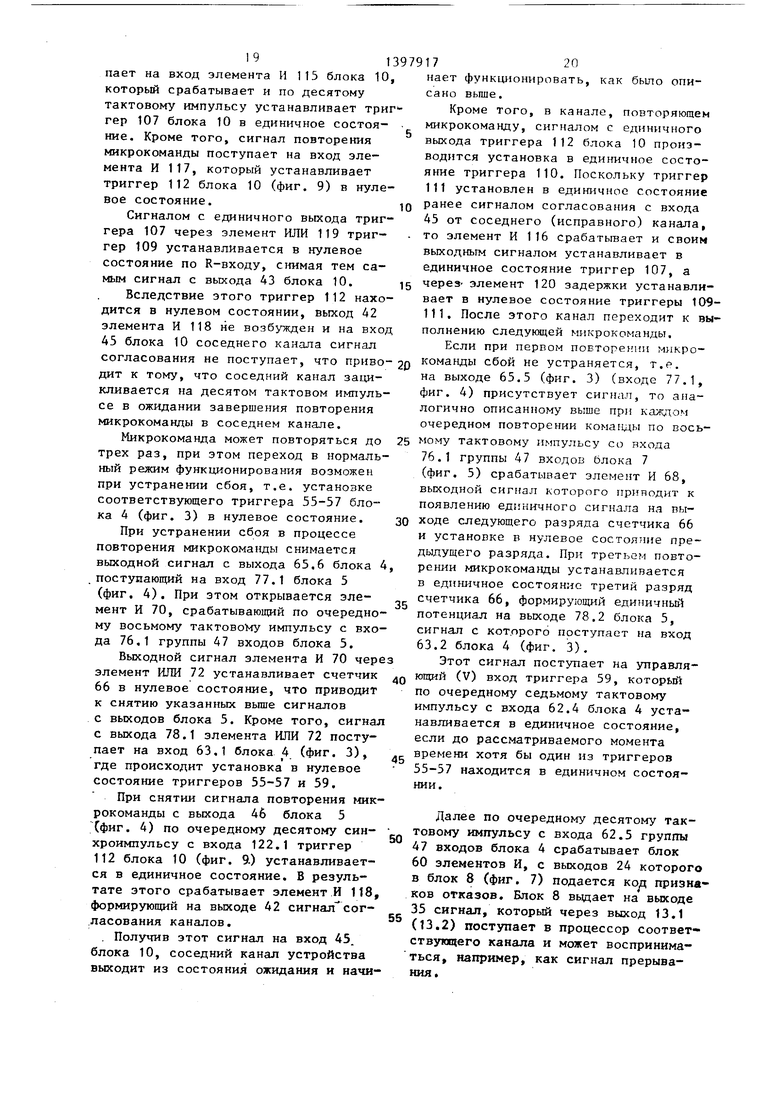

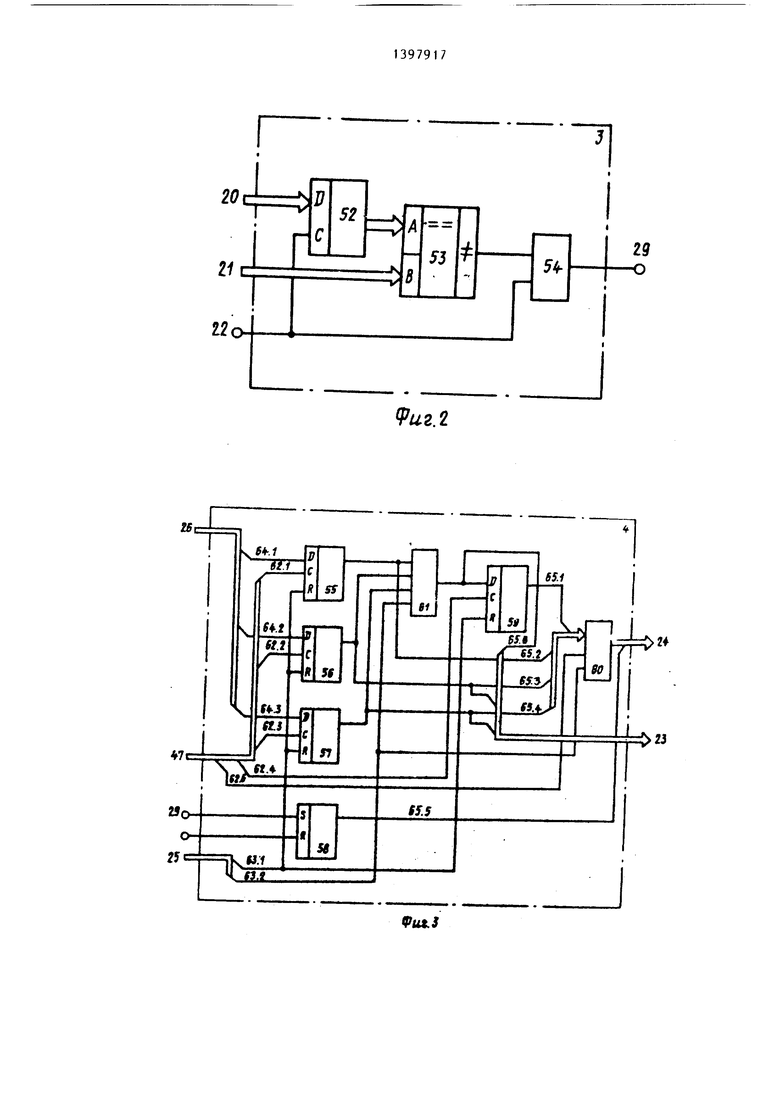

Блок 4 фиксации сбоев (фиг, 3) содержит первый 55, второй 56, третий 57, четвертый 58 и пятый 59 триггеры, группу 60 элементов И, элемент ИЛИ 6 входы 62.1-62.5 разрядов группы син- хровходов блока 4, входы 63.1 и 63,2 разрядов группы.входов установки блока 4, входы 64.1-64.3 разрядов группы информационных входов блока 4, третьи входы 65,1-65,4 соответственно с первого по четвертый элементов И группы 60, выходы 65.5 и 65,6 первых разрядов соответственно второй и первой групп выходов блока 4.

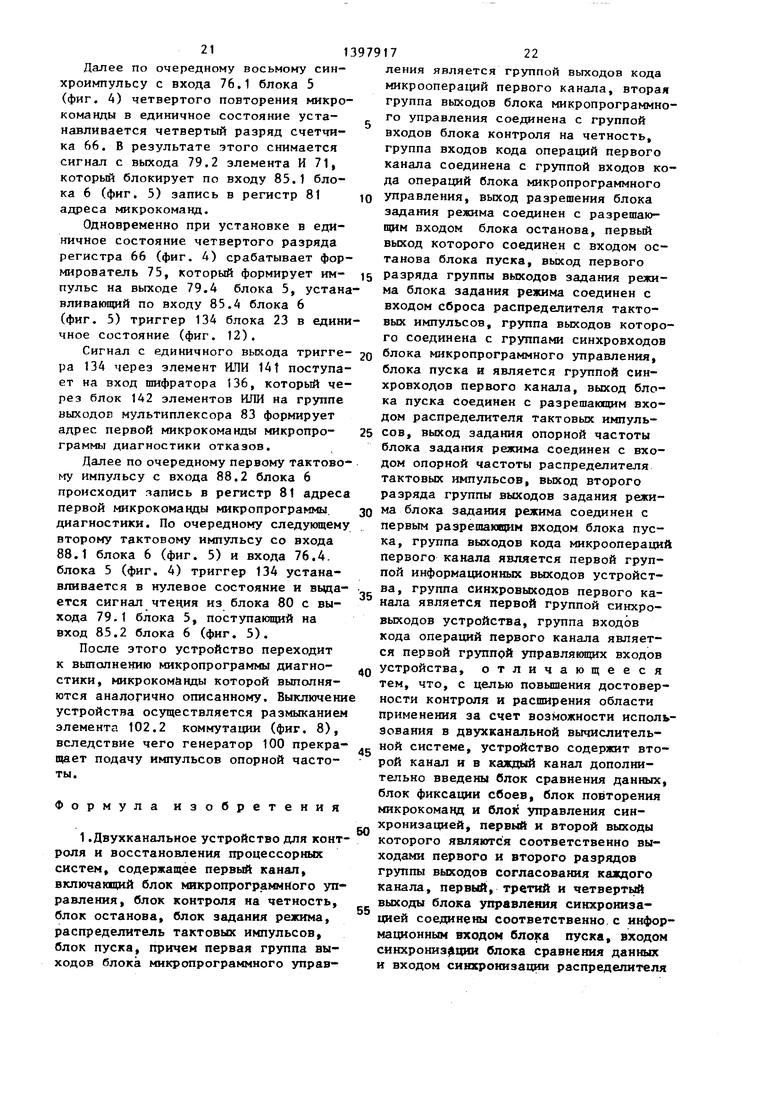

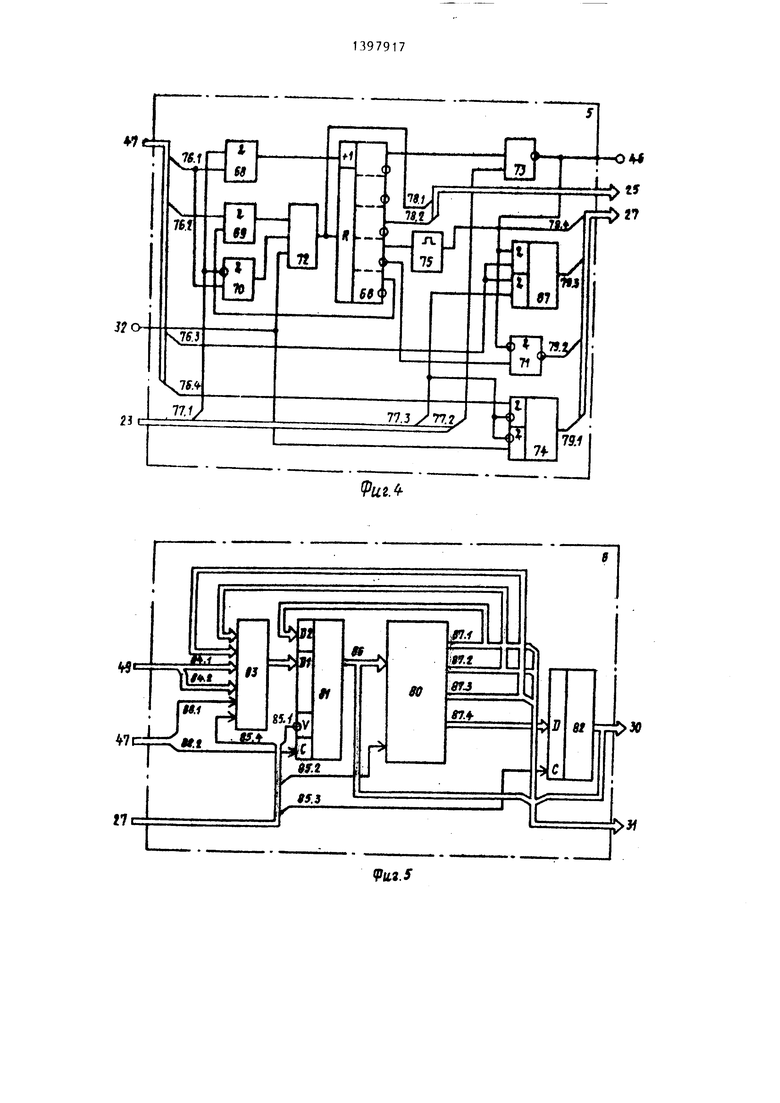

Блок 5 повторения микрокоманд (фиг. 4) содержит счетчик 66, первый коммутатор 67, первый 68, второй , третий 70 и четвертьш 71 элементы И, первьш 72 и второй 73 элементы гШИ, второй коммутатор 74,формирователь 75 импульсов, входы 76.1-76.4 разрядов группы синхровходов блока 5, входы 77.1-77.3 разрядов группы информационных входов блока 5, выходы 78.1 и 78.2 разрядов группы 25 выходов блока 5, выходы 79.1-79.4 разрядов группы 27 выходов блока 5 повторения микрокоманд.

Блок 6 микропрограммного управле

ния (фиг. 5) содержит блок 80 памяти микропрограмм, регистр 81 адреса, регистр 82 микрокоманд, мультиплексор 83 адреса, входы разрядов кода .операции 84.1 и логических условий 84.2 группы входов кода операций блока 6, входы 85.1-85.4 и первого - четвертого разрядов соответственно группы управляющих входов блока 6, группу 86 выходов регистра 81, группы 87.1-87.4 выходов блока 80, первый 88.1 и второй 88.2 входы разрядов группы синхровходов блока 6.

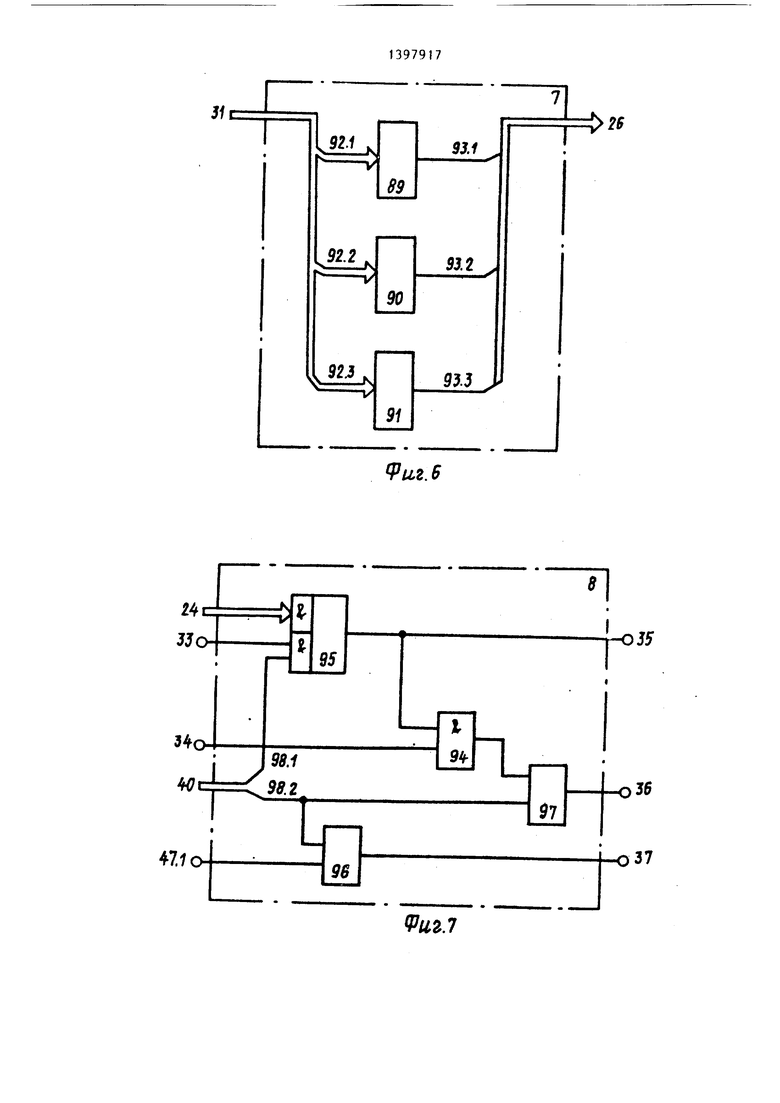

Блок 7 контроля на четность (фиг. 6) содержит первый 89, второй 90 и третий 91 сут маторы по модулю два, первую 92,1, вторуй 92.2 w третью 92.3 группы разрядов группы входов блока 7, выходы 93.1-93.3 пер

Q

5 о

5 Q

5

0

0

В(1Гп-трг:Т1.е го разрядов соотнетстпс и- но группы выходов блока 7,

Блок 8 останова (фиг, 7) содержит элемент И 94, коммутатор 95, перпьп 96 и второй 97 элементы И ТИ, входы 98.1 и 98,2 разрядов группы разрешающих входов блока 8.

Блок 9 задания режима (фиг, 8) содержит триггер 99 пуска, генератор 100 импульсов, элемент НЕ 101, элементы (кнопки) 102.1, 102,2 и 103- 105 коммутации, выходы 106,1 и 106.2 разрядов группы 40 выходов блока 9.

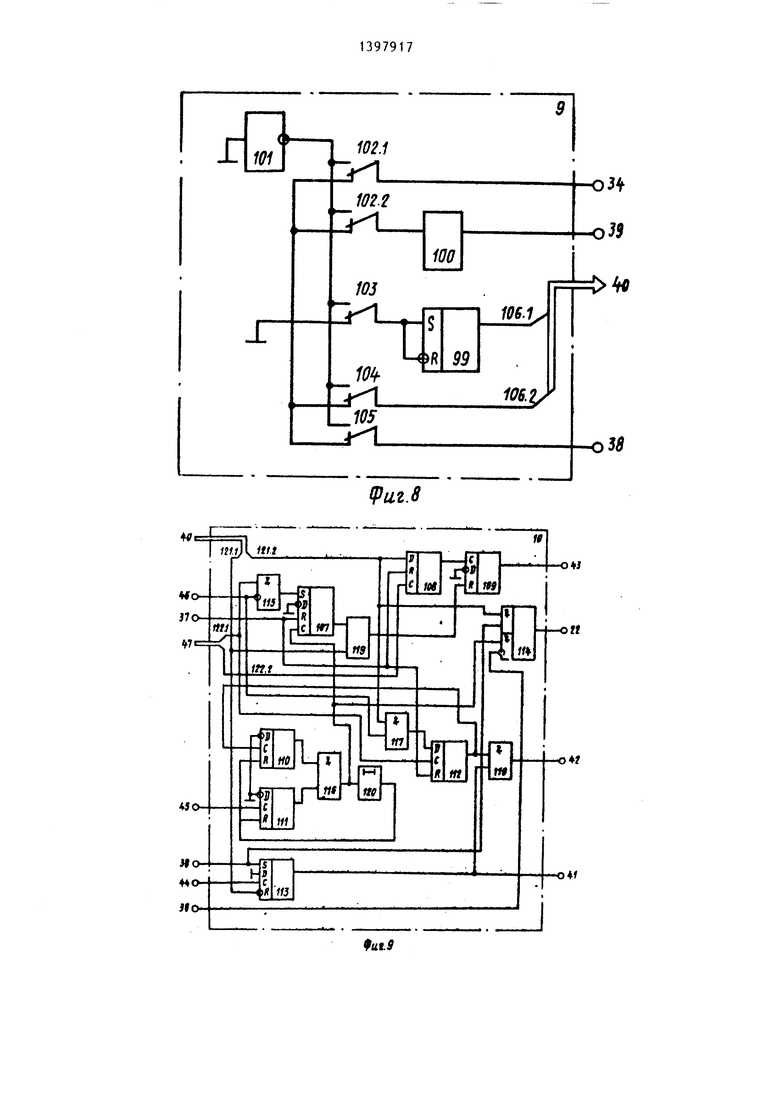

Блок 10 управления синхронизацией (фиг. 9) содержит первый 107, второй 108, третий 109, четвертьш 110, пятый 111, шестой 112 и седьмой 113 триггеры, коммутатор 114, псрпый 115 второй 116, третий 117 и чстпертьй 118 элементы И, элемент 1LTH 119 и элемент 120 задержки, вхо,.ы 121,1 и 121,2 разрядов группы разрешаюпц1х входов блока 10, входы 122.1 и 122,2 разрядов группы синхровходов блока 10.

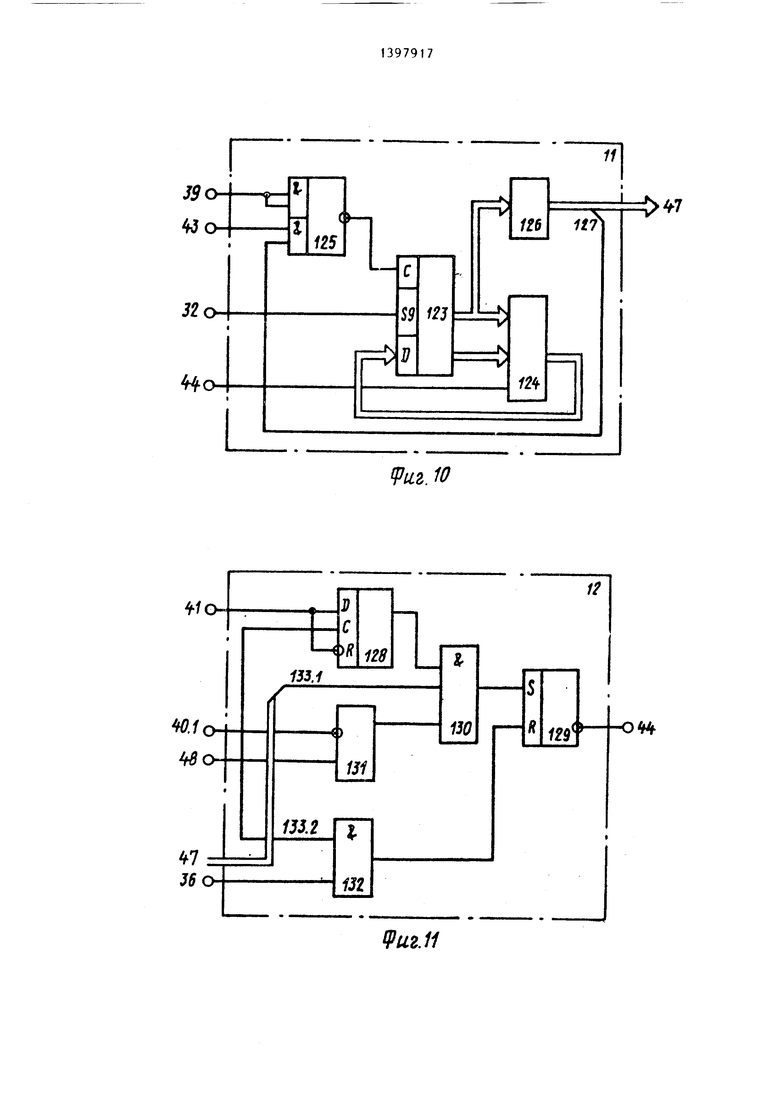

Распределитель 11 тактовых импульсов (фиг, 10) содержит регистр 123, преобразователь 124 кодов, коммутатор 125 и дешифратор 126, выход 127 десятого разряда группы 47 выходов распределителя 1 1 ,

Блок 12 пуска (фиг. 11) содержит первьш 128 и второй 129 триггеры, первый элемент И 130, элемент ilTH 131, второй элемент И 132, входы 133.1-133.2 разрядов группы синхровходов блока 12.

Мультиплексор 83 адреса (фиг. 12) содержит триггер 134, дешифратор 135, шифратор 136, первый 137, второй 138 и третий 139 блоки элементов И, элементы И 140, и ИЛИ 141 и блок 142 элементов ИЛИ.

Канал 1(2) предназначен для управления, контроля и восстановления работоспособности соответствующего процессора вычислительной системы. Каналь 1 и 2 имеют идентичную структуру .

Устройство предназначено для исправления одиночных сбоев в работе процессора, а также для организации вькода на микропрограмму обработки ошибок в случае отказа процессора, т.е. невосстановления его после повторного выполнения сбойной микрокоманды.

В случае одиночного сбоя организуется повторение микрокоманды и в

случае исчезновения сбоя продолжается выполнение икpoпpoгpaммь,

Сбои, которые не могут быть ликвидированы путем повторения микроко- , фиксируются как сигналы ошибки в триггерах блока 4 фиксации сбоев

Влок 3 сравнения данных предназначен для сравнения кодов данных, по- ступаюш,их на входы 20 и 21 блока 3 от пропессора одноименного и соседнего каналов соответственно.

Сравнение осуществляется в конце выполнения каждой микрокоманды при поступлении сигнала на вход 22 блока 3 в случае нормального обмена синхро- сигнала№1 согласования между обоими кяпллают. При несравнетп данных своего и соседнего каналоч схемой 53 вырлбатывается соответствующий сигнал, который через элемент И 54 поступает на в.1ход 29 для записи в триггер 58 блока 4.

Влок 4 фиксации сбоев предназначен для фиксации причины сбоя и формирования управляющих сигналов в блок 8 останова с 24 выходов и в блок 5 повторения микрокоманд (фиг.4) с группы 23 выходов.

Трттггепы 55-58 предназначены соот- вотстБРнно для фиксации сбоев в адресе микрокоманд, коде микрокоманды на выкоде блока памяти микрокоманд, регистра микрокоманд и ошибки даиньЕх процессоров каналов. Триггер 59 предназначен для фиксации факта обнару- сбоя одного из указанных типов.

Входы 64.1-64.3 разрядов группы

тьего повторения микрокоманды с выхода 78.2 блока 5.

Сброс триггеров 55-57 и 59 осуществляется по сигналу сброса, который формируется либо при нажатии кнопки 104 блока 9 и поступает на вход элемента ИЛИ 72, либо при пятом повторении микрокоманды, или при пропада10 НИИ сигнала сбоя на выходе элемента ИЛИ 61 блока 4, поступающего через группу выходов 23 на вход элемента И 70 блока 5. Сброс триггера 58 происходит по сигналу сброса от кнопки

15 104 блока 9 (фиг. 8), поступающему через выход блока 9 на нулевой вход триггера 58 блока 4,

Кроме того, триггеры 55-57 устанавливаются в кулевое состояние по

20 соответствующим синхросигналам с

входов 62.1-62.4 в случае снятия сигналов отказа с входов 64.1-64.3 группы информационных входов блока 4. Триггер 59 срабатывает по седьмо25 му синхроимпульсу с входа 62.4 при наличии признака сбоя на выходе элемента HJBi 61.

Ecjni при трехкратном повторении 30 признаки отказов не сняты, то по де- сятомл синхроимпульсу с входа 62.5 при наличии признака третьей микрокоманды с входа 63.2 признаки (код) сбоев с выходов 65.1-65.4 через груп- 35 пу 60 элементов И передаются на группу 24 выходов блока 4, являющуюся группой входов блока 8 (фиг. 7), в котором формируется код признаков сбоев и обобщенный сигнал сбоя. Код информафюнных входов блока 4 предназ-40 признаков сбоев может интерп{зетиро- начены для подачи сигналов сбоя в ад- ваться процессором, например, как

ресе микрокоманды, коде микрокоманды регистра микрокоманд соответственно с выходов 93,1-93.3 блока 7 (фиг. 6).

Входы 62.1-62.5 разрядов группы синхровходов (фиг. 3) предназначень для подачи соответственно четвертого, шестого, второго, седьмого и десятого синхроимпульсов с соответствующих выходов дешифратора 126 блока 11 (фиг. 10).

Информационный вход блока 4 предназначен для подачи сигнала несравнения данных своего и соседнего процессора с выхода 29 блока 3.

Входы 63.1 и 63.2 разрядов группы входов установки предназначены соот- ветственно для подачи сигналов сброса с выходов 78.1 блока 5 и признака третьего повторения микрокоманды с выхода 78.2 блока 5.

Сброс триггеров 55-57 и 59 осуществляется по сигналу сброса, который формируется либо при нажатии кнопки 104 блока 9 и поступает на вход элемента ИЛИ 72, либо при пятом повторении микрокоманды, или при пропадаНИИ сигнала сбоя на выходе элемента ИЛИ 61 блока 4, поступающего через группу выходов 23 на вход элемента И 70 блока 5. Сброс триггера 58 происходит по сигналу сброса от кнопки

104 блока 9 (фиг. 8), поступающему через выход блока 9 на нулевой вход триггера 58 блока 4,

Кроме того, триггеры 55-57 устанавливаются в кулевое состояние по

соответствующим синхросигналам с

входов 62.1-62.4 в случае снятия сигналов отказа с входов 64.1-64.3 группы информационных входов блока 4. Триггер 59 срабатывает по седьмому синхроимпульсу с входа 62.4 при наличии признака сбоя на выходе элемента HJBi 61.

адрсс программы (микропрограммы) диагностики отказов, а сигнал сбоя - как сигна-ч прерывания при отказе.

Таким образом, при одиночных сбоях блок 4 инициирует трехкратное повторение микрокоманды, а в случае постоянного отказа (если за время по- вторе ния микрокоманды признаки отказов не сняты) происходит выдача в процессор кода признаков сбоев и сигнала прерывания. При этом процессор может перейти на программу диагностики отказов.

Кроме того, выходы 65.6, 65.3 и 65.4 через группу 23 выходов соединены соответственно с входами 77.1- 77.3 групЛы входов блока 5 повторения микрокоманд.

713

Сигналы с выходов 65.6, 65.3 и 65.4 разрядов используются в блоке 5 в качестве сигналов управления счетным входом (входом сброса) счетчика 66 (фиг. 4) через элемент И 68 (И 70 и ИЛИ 72), формирования сигнала повторения микрокоманды элементов ИЛИ 7 и сигналов управления записью в регистр 82 (фиг. 5) микрокоманд через коммутатор 67 блока 5 и считывания информации из блока 80 через коммутатор 74 блока 5.

Блок 5 повторения микрокоманд предназначен для управления повторе- нием микрокоманд при сбое.

Счетчик 66 предназначен для подсчета числа повторений микрокоманды при сбое и осуп1ествляет счет в унитарном коде, причем номер разряда счетчика 66, в котором записана единица, однозначно соответствует числу повторений микрокоманды в рассматриваемый момент времени. Разряды счетчика принимают единичное значение по- гледовательно, начиная с первого, который подключен к входу элемента ИЛИ 73.

Коммутатор 67 блока 5 предназначен для формирования строба записи с выхода 79.3 в регистр 82 микрокоманд блока 6 (фиг. 5).

Элемент И 68 предназначен для фор- мирования счетного импульса на вход +1 счетчика 66 в режиме повторения микрокоманд, элементы И 69 и 70 - для формирования сигнала сброса счетчика 66 по окончании режима повторения микрокоманд и в случае устранения сбоя соответственно, элемент И 71 - для формирования строба низкого уровня дл блокировки регистра 81 адреса блока 6 (фиг. 5), элемент ИЛИ 72 - для формирования сигнала сброса счетчика 66, элемент И 73 - для формирования строб низкого уровня, управляющего режимами работы блока 10 (фиг. 9) управления синхронизацией.

Коммутатор 74 предназначен для формирования импульса разрешения чте- ния из блока 80 памяти микрокоманд.

Входы 76.1-76.4 разрядов предназначены для подачи восьмого, девятого, первого и второго тактовых импульсов с выходов 47 блока 11.

Входы 77.1-77.3 разрядов предназначены для подачи сигналов сбоя с выходов 65.6, 65.3 и 65..4 блока 4 соот- ветств.енно.

ю

5

20 25

30

35 0 45

п

5

178

Выходы 78.1 и 78.2 разрядов группы 25 выходов блока 5 соединены соответственно с входами 63.1 и 63.2 разрядов группы 25 входов блока 4.

Выходы разрядов 79.1-79.4 соединены соответственно с входами 85.2, 85.1, 85.3 и 85.4 разрядов блока 6.

Блок 6 ьшкропрограммного управления (фиг. 5) предназначен для управления работой процессора данного канала, в состав которого входит устройство.

Блок 80 памяти предназначен для хранения микропрограмм управления работой процессора канала. Считывание из блока 80 разрешается при наличии сигнала с входа 85.2, поступающего с выхода 79.1 блока 5 (фиг. 4). Регистр 81 предназначен для хранения адреса очередной микрокоманды. Запись в регистр 81 осуществляется по первому синхроимпульсу, поступающему на вход 47.1 блока 6 с выхода блока 11 (фиг. 10), при наличии разрешающего сигнала с входа 85.1, который поступает с выхода 79.2 блока 5 (фиг. 4).

На группу входов D1(D2) регистра 81 поступает модифицируемая (немодифицируемая) часть кода адреса очередной микрокоманды. Регистр 82 предназначен для хранения кода операционной части очередной микрокомавды. Запись в этот регистр производится при наличии синхроимпульса с входа 85.3, который поступает с выхода 79.3 блока 5,

Мультиплексор 83 адреса (фиг. 12) предназначен для формирования адреса очередной микрокоманды.

Входы разрядов 88.1 и 88.2 предназначены для подачи второго и первого тактовых импульсов соответственно. При подаче сигнала на вход 85.4 блока 6 (фиг. 5) с выхода 79.4 блока 5 мультиплексор 83 формирует на своей группе выходов код адреса первой микрокоманды диагностики отказов.

Сигнал на вход 85.4 поступает при отработке четвертого повторения сбойной микрокоманды. Разряды 84.1 и 84.2 группы 49 входов блока 6 предназначены для подачи кода операции и кода логических условий соответственно.

С выходов 87.1-87.4 разрядов блока 80 выдаются коды немодифицируемых модифицируемых разрядов микрокоманды, проверяемых логических условий и one

рационной части микрокоманды соответственно ,

Группы 30 и 31 выходов блока 6 предназначены соответственно для выдачи кода операционной части микрокоманд на объект управления (процессор) и объединенного кода адреса, кода с выходов блока 80 и кода с выхода регистра 82.

Выходы 86 и 87.1-87.4 разрядов и Групп 30 и 31 выходов блока 6 соединены соответственно с входами 92 , 1-92,3 группы входов блока 7 контроля.

Блок 7 контроля (фиг. 6) предназ- качен для контроля на четность инфорMaii iH, поступающей из блока 6.

Сумматоры 89-91 по модулю два fпредназначены соответственно для контроля на четность информации ре- гпстра 81 адреса блока 6 (фиг. 5), блока 80 памяти микрокоманд и регистра 82 микрокоманд. При отсутствии ошибки в соответствующем коде сумма-

тор 89 (90, 91) вьщает нулевой выход-25 выхода 38 блока 9 соответственно.

30

ной сигнал.

Выходы 93.1, 93.2и93.9 разрядов группы 26 выходов предназначены для выдачи сигналов ошибки на входы разрядов 64.1-64.3 блока 4.

Елок 8 останова (фиг. 7) предназначен для- формирования сигналов останова и прерывания (отказа).

Элемент И 94 предназначен для формирования сигнала останова в режиме настройки, а коммутатор 95 - для фор- мирования сигнала отказа (прерывания) на выходе 35.1 при отказе своего (чужого) канала при асинхронном (синхронном) режиме работы устройства.

Элемент ИЛИ 96 предназначен для формирования сигнала сброса с выхода 36 блока 8, триггеров 107, 108 и 112 блока 10 (фиг. 9) а элемент ИЖ 97 - для формирования с выхода 36 блока 8 сигнала управления коммутатором 114 блока 10.

На группу 24 входов блока 8 поступает код с выходов блока 4 (фиг. 3), содержапщй признак троекратного повторения микрокоманды с выхода 65.1 бло- ка 4Jпризнаки причины отказа с выходов 65.2-65.4.

На входы 33, 34 и 47.1- блока 8 поступают соответственно сигналы

40

45

Выход 106.1 группы 40 соединен с входом 40.1 блока 12 (фиг. 11) и вх дом 121.2 блока 10 (фиг. 9), выход 106.2 группы 40 - с входами 32 блоков 4, 5 и В, входом 121.1 блока 10 и входом 32 блока 11 (фиг. 10).

Блок 10 управления синхронизацие (фиг. 9) предназначен для координации работы блоков канала, а также к налов устройства между собой.

Триггер 107 предназначен для.фик сации сигнала повторения микрокоман Триггер 108 фиксирует режим синхрон ного (зависимого) функционирования налов. Триггер 109 предназначен для управления распределителем 11 (фиг. сигналом с выхода 43.

Триггеры 110 и 111 предназначены для формирования сигналов разрешени сравнения результата вьшолнения микрокоманды в первом и втором канала триггер 112 - для формирования сигн ла согласования работы каналов, три гер ИЗ - для формирования на выход 41 блока 10 сигнала пуска данного к нала.

Коммутатор 114 предназначен для формирования на выходе 22 сигнала р решения сравнения результата вьшолн

прерывания (отказа) от соседнего ка- 55 ния микрокоманды в первом и втором

нала, настройки от блока 9,,второго тактового импульса с выходов 47 блока 11 (фиг. 10).

0

5

0

На входы 98.1 и 98.2 разрядов группы входов блока 8 поступают сигналы признака синхронной работы и сброса с выходов 106.1 и 106.2 блока 9.

Блок 9 задания режима (фиг. 8) предназначен для управления режимами функционирования устройства.

Генератор 100 предназначен для вьщачи импульсов опорной частоты на выход 39, триггер 99 - для задания режима синхронной работы каналов устройству (в единичном состоянии) с выхода 106.1, элемент НЕ 101 - для формирования единичного потенциала.

Элементы 102.1 и 102.2 коммутации предназначены для формирования сигнала настройки с выхода 34 блока 9 и сигнала включения генератора 100 соответственно, элементы 103-105 коммутации для формирования сигналов установки триггера 99 в единичное состояние, сброса на выходе 106.2 блока 9 и пуска распределителя 11 с

0

0

5

Выход 106.1 группы 40 соединен с входом 40.1 блока 12 (фиг. 11) и входом 121.2 блока 10 (фиг. 9), выход 106.2 группы 40 - с входами 32 блоков 4, 5 и В, входом 121.1 блока 10 и входом 32 блока 11 (фиг. 10).

Блок 10 управления синхронизацией (фиг. 9) предназначен для координации работы блоков канала, а также каналов устройства между собой.

Триггер 107 предназначен для.фиксации сигнала повторения микрокоманды. Триггер 108 фиксирует режим синхронного (зависимого) функционирования каналов. Триггер 109 предназначен для управления распределителем 11 (фиг.10) сигналом с выхода 43.

Триггеры 110 и 111 предназначены для формирования сигналов разрешения сравнения результата вьшолнения микрокоманды в первом и втором каналах, триггер 112 - для формирования сигнала согласования работы каналов, триггер ИЗ - для формирования на выходе 41 блока 10 сигнала пуска данного канала.

Коммутатор 114 предназначен для формирования на выходе 22 сигнала разрешения сравнения результата вьшолнеканалах, элемент И 118 - для формирования на ёыходе 42 сигнала согласования работы каналов.

Каналы синхронизируются по моменту окончания текущей микрокоманды. При этом канал не начинает выполнение очередной микрокоманды, не получив сигнал согласования от соседнего канала, который передается с выхода 42 через группу 51 выходов канала и далее через группу 16.1 (16.2) на группу 50 входов соседнего канала и на вход 45 блока 10 соседнего канала.

Входы 121.1 и 121.2 предназначены для подачи сигнала признака синхронного режима работы и сигнала сброса соответственно.

Входы 122.1 и 122.2 разрядов группы синхровходов предназначены для подачи десятого и девятого тактовых импульсов с группы 47 выходов блока 11, а вход 44 - для подачи сигнала пуска от блока 12 пуска (фиг. 11).

Назначение остальных входов блока 10 пояснено выше.

Распределитель 11 тактовых импульсов (фиг. 10) предназначен для синхронизации работы блоков канала.

Регистр 123 предназначен для формирования кодов тактовых импульсов. При подаче сигнала на установочный вход (S 9) регистр 123 устанавливается в состояние 0111.

Преобразователь 124 кодов предназначен для фортфования функций обратной связи автомата, состоящего из регистра 123, преобразователя 124 и дешифратора 126. Для кодирования есяти используемых состояний автомата выбран код Грея, т.е. первое состояние имеет код 0001, а десятое - код 0101.

Регистр 123 содержит четьфе разяда, например, Q,, Qj, Q , и Q . Тогда первое состояние, соответству- ющее первому тактовому импульсу, имет код -При подаче сигнала а вход 44 распределителя 11 автомат ацикливается на вьщаче девятого и есятого тактовых импульсов. Если

через D-, D

7

ОдИ Dj обозначить входы триггеров (разрядов) регистра 123, то функции возбуждения можно описать следующим образом

D, ,;

D,

Da

QiQi QjQjQ Q,QjQei44 ;

QlVQ4VQjQjO(44VQiQj;

o

5

0

5

0

0

5

где с/44 - значение сигнала на входе 44

Декодирование состоя)1ий регистра 123 осуществляется дешифратором 126, который вьщает тактовые импульсы на выходы разрядов группы 47 выходов распределителя 11.

С выхода 127 разряда дещифратора 126 вьщается десятьш тактовый импульс. Входы 39 и 43 предназначены для подачи соответственно тактовых импульсов опорной частоты и признака синхронной работы каналов.

Блок 12 пуска (фиг. 11) предназначен для управления работой распределителя 11 тактовых импульсов и блока 10 управления синхронизацией.

Триггер 128 предназначен для фиксации сигнала пуска данного канала, поступающего с входа 41, триггер 129 для формирования сигнала останова (торможения) канала на выходе 44 блока 12 пуска.

На входы 40.1, 48, 36, 133.1 и 133.2 разрядов поступают соответственно сигналы признака синхронного режима каналов, пуска от соседнего канала (с выхода 41 соседнего канала), сброса (или останова) от блока 8, десятого и девятого тактовых импульсов .

Выход 13.1 (13.2) канала 1(2) предназначен для вьщачи сигнала отказа (прерьшания) в процессор соответствующего канала, группа 14.1 (14.2) выходов канала 1(2) - для вьвдачи тактовых импульсов в процессор соответствующего канала, группа 15.1(15.2) выходов канала 1(2) - для выдачи в процессор канала кода микроопераций, группа 16.1(16.2) выходов канала 1(2) для выдачи сигналов согласования на входы соседнего канала 2(1), группа 17.1(17.2) входов - для подачи кода операции (микропрограммы), выполняемой каналом 1(2), группа 18(19) входов устройства - для подачи кода данных (результатов вьшолнения текущей микрокоманды) процессом первого (второго) канала.

Мультиплексор 83 адреса (фиг. 12) предназначен для формирования адреса очередной микрокоманды блока Ь.

Дешифратор 135 предназначен для е зт равления режимами формирования адреса в соответствии с кодом логических условий, поступающим на входы 87.3. При возбуждении первого выхода дешифратора 135 код модифицируемых

0

13139

разрядов адреса определяется кодом операции с входов 84.1.

При возбуждении второго выхода дешифратора 135 шифратором 136 формируется код адреса первой микрокоманды микропрограмм диагностики отказов. Возбуждение третьего выхода дешифратора 135 предопределяет передачу кода

модифицируемых разрядов адреса с вхо- ю задается режим работы каналов: синхродов 87.2 через блок 138 элементов И без изменения. При возбуткдении i-ro выхода разрядов группы выходов дешифратора 135 на соответствующем элементе Н 139.1 (ie 1, 1)блока 83 осущест- 15 кании (размыкании) элемента 103. вляется проверка значения соответствующего логического условия с входов 84. 2.

В режиме повторения микрокоманд при пятом повторении сбойной микрокоманды по сигналу с входа 85.4 триггер 134 устанавливается в единичное состояroie, закрывая дешифратор 125. Сигнал с единичного выхода триггера 134 через элемент ИЛИ 141 возбуждает шифратор 136, который формирует код адреса первой микрокоманды микропрограммы диагностики отказов, который по очередному первому тактовому импульсу с входа 88.2 группы 47 записывается в регистр 81 адреса.

Далее по второму тактовому импульсу с входа 88.1 срабатывает элемент И 140, выходной сигнал которого устанавливает триггер 134 в нулевое состояние. При этом открывается дешифратор 135.

Основными режимами функционирования устройства являются реализация последовательности микрокоманд и режим повторения микрокоманд в случае обнаружения сбоя.

В режиме реализации последовательности микрокоманд без сбоев устройство работает следующим образом.

В исходном состоянии все элементы памяти находятся в нулевом состоянии (входы начальной установки не показаны). Код операции, реализуемой устройством, поступает от процессоров каналов на соответствующие входы 17.1 и 17.2 каналов устройства. В исходном состоянии блока 6 микропрограммного управления на. выходах 87.1, 87.2 и 87.А присутствуют нулевые сигналы, а с группы 87.3 выходов блока 80 (фиг. 5) вьщается код X j,+, , который в соответствии с логической функцией мультиплексора 83 предопреДалее с блока 9 элементом 104 мутации формируется на выходе 106 блока 9 сигнал сброса, который по пает на вход 32 блока 11 (фиг. 10

20 устанавливает регистр 123 в состо формирования на соответствующем в ходе дешифратора 126 девятого так вого импульса.

Кроме того, сигнал сброса с вы

25 106.2 блока 9 поступает на вход 3 блока 8, в котором через элементы ИЛИ 96 и 97 на выходах 36 и 37 со ветственно формируются установоч сигналы.

30 Сигнал с выхода 36 блока 8 (фи поступает на управляющий вход ком татора 114 блока 10 (фиг. 9), и к ме того, через элемент ПТИ 132 по вятому тактовому импульсу осущест

-с ет установку триггера 129 блока 1 нулевое состояние. Сигналом с вых 37 производится установка в нулев состояние триггеров 107, 108 и 11 блока 10, а также по сигналу с ед ничного выхода триггера 107 .через элемент ИЛИ 119 триггер 109 также танавливается в нулевое состояние

Потенциал с нулевого выхода 44 триггера 129 блока 12 поступает н управляющий вход 44 преобразовате 124 блока 11, который управляет з цикливанием распределителя 11 на даче девятого и десятого тактовых импульсов. Кроме того, сигнал с в да 44 блока 12 (фиг. 11) поступае на С-вход триггера 113 блока 10, торый устанавливается в нулевое с тояние.

Далее замыкается элемент 102.2 коммутации блока 9 (фиг. 8) и вкл чается генератор 100, который нач нает формировать на выходе 39 бло 9 тактовый импульсы опорной часто поступающие на вход 39 распредели

40

45

50

55

14

деляет передачу кода операции на группу D входов регистра 81 в качестве адреса первой микрокоманды микропрограммы, реализуемой устройством по данному коду операции.

Работа устройства начинается при включении распределителя 11 тактовых импульсов. При этом предварительно

ный или асинхронный. В синхронном (асинхронном) режиме триггер 99 блока 9 (фиг. 8) устанавливается в единичное (нулевое) состояние при замыкании (размыкании) элемента 103.

Далее с блока 9 элементом 104 коммутации формируется на выходе 106.2 блока 9 сигнал сброса, который поступает на вход 32 блока 11 (фиг. 10) и

устанавливает регистр 123 в состояние формирования на соответствующем выходе дешифратора 126 девятого тактового импульса.

Кроме того, сигнал сброса с выхода

Сигнал с выхода 36 блока 8 (фиг. 7) поступает на управляющий вход коммутатора 114 блока 10 (фиг. 9), и кроме того, через элемент ПТИ 132 по девятому тактовому импульсу осуществляет установку триггера 129 блока 12 в нулевое состояние. Сигналом с выхода 37 производится установка в нулевое состояние триггеров 107, 108 и 112 блока 10, а также по сигналу с единичного выхода триггера 107 .через элемент ИЛИ 119 триггер 109 также устанавливается в нулевое состояние.

Потенциал с нулевого выхода 44 триггера 129 блока 12 поступает на управляющий вход 44 преобразователя 124 блока 11, который управляет зацикливанием распределителя 11 на выдаче девятого и десятого тактовых импульсов. Кроме того, сигнал с выхода 44 блока 12 (фиг. 11) поступает на С-вход триггера 113 блока 10, который устанавливается в нулевое состояние.

Далее замыкается элемент 102.2 коммутации блока 9 (фиг. 8) и включается генератор 100, который начинает формировать на выходе 39 блока 9 тактовый импульсы опорной частоты, поступающие на вход 39 распределите

ля 11. Происходит снятие сигнала сброса с выхода 106.2 (32) блока 9 при размыкании элемента 104 коммутации. При этом распределитель П замыкается на вьщаче девятого-десятого тактового импульса.

После этого кнопкой 105 блока 9 на выходе 38 формируется сигнал пуска распределителя. Этот сигнал с вы- хода 38 блока 9 поступает на единичный вход триггера 113 блока 10 (фиг.9 и на вход коммутатора 114 блока 10.

Триггер 113 устанавливается в единичное состояние и формирует сигнал на выходе 41 блока 10. Кроме того, при снятии сигнала сброса с выхода 106.2 блока 9 снимаются сигналы с выходов 36 и 37 блока 8 (фиг. 7). Триггер 11 3 блока 10 (фиг. 9) и триггеры 1 28 и 129 блока 12 (фиг.11) устанавливаются в единичное состояние, в результате чего снимается сигнал с выхода 44 блока 12 (фиг. 1) и распределитель 1 переходит к вьфаботке периодической последовательности из десяти тактовых импульсов.

Последовательность тактовых импульсов в асинхронном режиме при нулевом состоянии триггера 99 блока 9 выраба- тывается непрерывно до тех пор, пока на входе 36 блока 12 пуска (фиг. 11) не появится сигнал останова, рованный на выходе элемента ИЛИ 97 блока 8 останова. В этом случае распределитель 11 снова зацикливается на вьдаче девятого - десятого тактового импульса, так как по девятому тактовому импульсу элемент И 132 блока 12 вырабатьшает сигнал сброса триггера 129.

В асинхронном режиме каналы функционируют независимо друг от друга, В синхронном режиме установка триггера 129 блока 12 (фиг. 11) в единичное состояние возможна с приходом очередного десятого тактового импульса с входа 133.1 группы 47 только при срабатывании элемента ИЛИ 31, который в синхронном режиме (при единичном потенциале на входе 40.1 (выходе 106.1 блока 9) возбуждается только с приходом сигнала с входа 48 блока 12. Сигнал на вход 48 поступает с выхода 41 блока 10 соседнего канала.

. В синхронном режиме согласование каналов осуществляется следующим образом.

5 0 5

о Q

5

5

0

5

В силу независимости и разброса параметров один из каналов может выдать микрокроманду быстрее, чем соседний канал. Тогда ог1ережаю ций канал зацикливается на вьдаче десятого тактового импульса до момента завершения вьтолнения микрокоманды соседним каналом. При этом в момент завершения вьдачи микрокоманды отстающим каналом в обоих каналах формируется стробирующий сигнал на выходе 22 блока 10 (фиг. 9), по которому в блоке 3 осуществляется сравнение данных своего и соседнего каналов.

В случае неравенства результатов блоком 3 на выходе 29 элемента И 54 формируется сигнал ошибки, поступающий в блок 4 и устанавливающий триггер 58 в единичное состояние.

В случае обнаружения ошибки при выполнении микрокоманды и фиксации их в триггерах 55-57 блока 4 устройство переходит в режим повторения микрокоманд а в противном случае функционирует как описано выше.

Каналы могут вводиться в синхронный режим сразу же при включении либо в процессе функционирования. При этом аналогично описанному выше каждый из каналов зацикливается на выдаче десятого тактового импульса при шзреводе триггера 99 блока 9 в обоих каналах в единичное состояние до момента согласования при завершении текущей микрокоманды. После ввода каналов в синхронизм дальнейшее вьтол- нение микрокоманд в синхронном режиме происходит следующим образом.

В опережающем канале происходит по девятому тактовому импульсу с входа 122.2 установка в единичное состояние триггера 108 блока 10. Сигналом с единичного выхода триггера 108 устанавливается в единичное состояние триггер 109, потенциал с единичного вько- да A3 которого поступает на одноименный вход распределителя 11, и при выдаче десятого тактового импульса с выхода 127 коммутатор 125 подает на С-вход регистра нулевой сигнал, останавливающий распределитель 11 в состоянии вьщачи десятого тактового импульса.

Кроме того, по десятому тактовоку импульсу с входа 122.1 блока 10 при отсутствии сигнала повторения микрокоманды с входа 46 блока 10 единичный сигнал с выхода элемента И 117 запись 1713

Бается в триггер 112. В результате этого на выходе элемента И 118 формируется сигнал согласования каналов, который с выхода 42 данного канала через группу 51 выходов поступает на вход 45 блока 10 соседнего канала. Одновременно сигналом с единичного выхода триггера 112 триггер 110 блока 10 устанавливается в единичное сое- тояние.

После прихода сигнала согласования от соседнего канала на вход 45 блока

10триггер 111 также устанавливается

в единичное состояние, в результате чего срабатывает элемент И 116, сигнал с выхода которого поступает на С-вход тригге1за 107 и вход коммутатора 114. При этом триггер 107 устанавливается в единичное состояние, а коммутатор 114 на выходе 22 формирует сигнал согласования каналов. Триггер 109 также устанавливается в нулевое состояние, при этом на С-входе регистра 123 блока 1 выходом элемента 125 формфуется положительный импульс, KOTopbrfi приводит к выработке блоком

11опережающего канала следующей серии из десяти тактовых импульсов.

Далее срабатывает элемент 120 за- держки, устанавливающий триггер 110 и 111 в тгулевое состояние. Задержка выбирается достаточной для срабатывания триггера 107 и вьщачи сигнала разрешения сравнения данных обоих каналов с вьгхода 22. В отстающем канале в рассматриваемом случае по девятому тактовому импульсу с входа 122.2 блока 10 устанавливается в единичное состояние триггер 108, сигнал с единичного выхода которого устанавливает триггер 109 также в единргчное состояние.

По десятому тактовому импульсу с входа 122,1 группы 47 блока 10 устанавливается в единичное состояние триггер 112. В результате этого срабатывает элемент И 118, с выхода 42 которого выдается сигнал согласования каналов, поступающий на вход 45 блока 10 соседнего канала. После этого в отстающем канале аналогично расмот- ренному для опережающего канала формируется строб с выхода 22, устанавливаются в единичное состояние триггер 107 и в нулевое триггер 109.

После этого рассматриваемый канал переходит к выполнению очередной микрокоманды. При этом запись адреса

5 о 5

о

5

5

5

1718

очередной микрокоманды в регистр 81 адреса блока 6 осуществляется по первому тактовому импульсу со входа 47,1 блока 6. По этому же импульсу происходит запись в регистр 82 кода операционной части микрокоманды, который с группы 30 выходов выдается на выходы 15.1 (15.2) канала для передачи на элементы и узлы соответствующего процессора.

Запись в регистры 81 и 82 производится при наличии разрешающих сигналов с входов 85.1 и 85.3 блока 6 соответственно. Считывание кода микрокоманды из блока 80 памяти (на внутренний выходной регистр блока 80) осуществляется по сигналу с входа 85.2, вырабатываемому ком гутатором

74на выходе 79.1 блока 5 при наличии второго тактового импульса с входа 76.4 или сигнала сброса с входа 32 и отсутствии сигнала ошибки с входа 77.3 блока-5 (выхода 65.4 блока 4).

В процессе выдачи микрокоманд уст ройством производится контроль совпадения данных в первом 1 и втором 2 каналах блоком 3, а такж е контроль блоком 7 на четность информадаи, вы- рабатьгоаемой блоком 6. При этом в случае несовпадения информации в каналах блоком 3 на вьгходе 29 формируется сигнал сбоя, который поступает на одноименный вход блока 4.

Если произошла ошибка блока 80 памяти по информации, т.е. сбой четности при считывании из блока 80 и записи в его внутренний выходной регистр, то сигнал сбоя с выхода 93.2 блока 90 по девятому тактовому импульсу предыдущей последовательности из десяти синхроимпу/ ьсов устанавливает триггер 56 блока 4 в единичное состояние. При этом сигнал с выхода 65.3 блока 4 поступает на вход 77.2 элемента ИЛИ 73 блока 5.

При наличии сигналов на входах

75и 77.2 элемент ИЛИ 73 формирует на выходе 46 Сигнал повторения микрокоманды низкого уровня. Кроме того, одновременно элементом И 71 на вькоде 79.2 формируется сигнал блокировки, поступающий на вход 85.1 регистра 81 блока 6 (фиг, 5) и запрещающий изменение состояния регистра 81 адреса блока 6 в течение четьфех последукнцих повторений микрокоманды.

Сигнал,(Повторения микрокоманды с выхода 4б блока 5 (фиг. 4) посту19139791720

15 блока 10, нает функционировать, как было описано выше.

Кроме того, в канале, повторяющем микрокоманду, сигналом с единичного выхода триггера 112 блока 10 производится установка в единичное состояние триггера 110. Поскольку триггер 111 установлен в единичное состояние ранее сигналом согласования с входа 45 от соседнего (исправного) канала, . то элемент И 116 срабатывает и своим выходным сигналом устанавливает в единичное состояние триггер 107, а 15 через- элемент 120 задержки устанавливает в нулевое состояние триггеры 10S- Ill. После этого канал переходит к выполнению следующей микрокоманды.

Если при первом noBTopefrini микро- согласования не поступает, что приво-20 команды сбой не устраняется, т.е. дит к тому, что соседний капал заци- на выходе 65.5 (фиг. 3) (входе 77.1,

фиг. 4) присутствует сигнал, то аналогично описанному выше при каж;1;ом очередном повторении команды по вось- 25 мому тактовому импульсу со входа 76.1 группы 47 входов блока 7 (фиг. 5) срабатывает элемент И 68, выходной сигнал которого принодит к появлению единичного сигнала на вы- 30 ходе следующего разряда счетчика 66 и установке в нулевое состояние пре- дьщущего разряда. При третьем повторении микрокомавды устанавливается в единичное состояние третий разряд счетчика 66, формирующий единичный

мент И 70, срабатывающий по очередно-- « му восьмому тактовому импульсу с входа 76.1 группы 47 входов блока 5.

Выходной сигнал элемента И 70 через

элемент ИЛИ 72 устанавливает счетчик Q ющий (V) вход триггера 59, которьп 66 в нулевое состояние, что приводит по очередному седьмому тактовому к снятию указанных выше сигналов с выходов блока 5. Кроме того, сигнал с выхода 78.1 элемента ИЛИ 72 поступает на вход 63.1 блока 4 (фиг. 3), где происходит установка в нулевое состояние триггеров 55-57 и 59.

При снятии сигнала повторения микрокоманды с выхода 46 блока 5 (фиг. 4) по очередному десятому синхроимпульсу с входа 122,1 триггер 112 блока 10 (фиг. 9.) устанавливается в единичное состояние. В результате этого срабатывает элемент И 118, формирующий на выходе 42 сигнал согласования каналов.

пает на вход элемента И который срабатывает и по десятому тактовому импульсу устанавливает триггер 107 блока Ю в единичное состояние. Кроме того, сигнал повторения микрокоманды поступает на вход элемента И 117, который устанавливает триггер 112 блока 10 (фиг. 9) в нулевое состояние.1Q

Сигналом с единичного выхода триггера 107 через элемент ИЛИ 119 триггер 109 устанавливается в нулевое состояние по R-входу, снимая тем самым сигнал с выхода 43 блока 10.

Вследствие этого триггер 112 находится в нулевом состоянии, выход 42 элемента И 118 не возбужден и на вход 45 блока 10 соседнего канала сигнал

кливается па десятом тактовом импульсе в ожидании завершения повторения микрокоманды в соседнем канале.

Микрокоманда может повторяться до трех раз, при этом переход в нормальный режим функционирования возможен при устранении сбоя, т.е. установке соответствующего триггера 55-57 блока 4 (фиг. 3) в нулевое состояние.

При устранении сбоя в процессе повторения микрокомавды снимается выходной сигнал с выхода 65.6 блока 4, .поступающий на вход 77.1 блока 5 (фиг, 4), При этом открывается эле45

потенциал на выходе 78.2 блока 5, сигнал с которого поступает на вход 63.2 блока 4 (фиг. 3).

Этот сигнал поступает на управляимпульсу с входа 62.4 блока 4 устанавливается в единичное состояние, если до рассматриваемого момента времени хотя бы один из триггеров 55-57 находится в единичном состоянии.

50

55

Далее по очередному десятому тактовому импульсу с входа 62,5 группы 47 входов блока 4 срабатывает блок 60 элементов И, с выходов 24 которого в блок 8 (фиг, 7) подается код признаков отказов. Блок 8 выдает на выходе 35 сигнал, который через выход 13,1 (13,2) поступает в процессор соответствующего канала и может воспринима ться, например, как сигнал прерывания.

Получив этот сигнал на вход 45. блока 10, соседний канал устройства выходит из состояния ожидания и начи- « потенциал на выходе 78.2 блока 5, сигнал с которого поступает на вход 63.2 блока 4 (фиг. 3).

Этот сигнал поступает на управляющий (V) вход триггера 59, которьп по очередному седьмому тактовому

импульсу с входа 62.4 блока 4 устанавливается в единичное состояние, если до рассматриваемого момента времени хотя бы один из триггеров 55-57 находится в единичном состоянии.

Далее по очередному десятому тактовому импульсу с входа 62,5 группы 47 входов блока 4 срабатывает блок 60 элементов И, с выходов 24 которого в блок 8 (фиг, 7) подается код признаков отказов. Блок 8 выдает на выходе 35 сигнал, который через выход 13,1 (13,2) поступает в процессор соответствующего канала и может воспринима ться, например, как сигнал прерывания.

Далее по очередному BocbMoffy синхроимпульсу с входа 76.1 блока 5 (фиг. 4) четвертого повторения микрокоманды в единичное состояние устанавливается четвертый разряд счетчика 66. В результате этого снимается сигнал с выхода 79.2 элемента И 71, который блокирует по входу 85.1 блока 6 (фиг. 5) запись в регистр 81 адреса микрокоманд.

Одновременно при установке в единичное состояние четвертого разряда регистра 66 (фиг. А) срабатывает формирователь 75, который формирует импульс на выходе 79.4 блока 5, устанавливающий по входу 85.4 блока 6 (фиг. 5) триггер 134 блока 23 в едини15 разряда группы выходов задания режи ма блока задания режима соединен с входом сброса распределителя тактовых импульсов, группа выходов котор го соединена с группами синхровходо

чное состояние (фиг. 12).

Сигнал с единичного выхода тригге- 2Q блока микропрограммного управления, ра 134 через элемент ИЛИ 14Т поступа- блока пуска и является группой син- ет на вход шифратора 136, который через блок 142 элементов ИЛИ на группе выходов мультиплексора 83 формирует адрес первой микрокоманды микропрограммы диагностики отказов.

Далее по очередному первому тактовому импульсу с входа 88.2 блока 6 происходит запись в регистр 81 адреса первой микрокоманды микропрограммы, диагностики. По очередному следующему второму тактовому импульсу со входа 88.1 блока 6 (фиг. 5) и входа 76.4. блока 5 (фиг. 4) триггер 134 устанавливается в нулевое состояние и выдается сигнал чтения из блока 80 с выхода 79,1 блока 3, поступающий на вход 85.2 блока 6 (фиг. 5).

хровходов первого канала, выход бло ка пуска соединен с разрешающим вхо дом распределителя тактовых импуль25 сов, выход задания опорной частоты блока задания режима соединен с вхо дом опорной частоты распределителя тактовых импульсов, выход второго разряда группы выходов задания режи

30 ма блока задания режима соединен с первым разрешаняцим входом блока пус ка, группа выходов кода микроопераци первого канала является первой груп пой информационных выходов устройства, группа синхровыходов первого ка нала является первой группой синхровыходов устройства, группа входов кода операций первого канала является первой группой управляющих входов

35

После этого устройство переходит к вьшалнению микропрограммы диагностики, микрокоманды которой выполняются аналогично описанному. Выключение устройства осуществляется размыканием элемента 102.2 коммутации (фиг. 8),

вследствие чего генератор 100 прекра- . ной системе, устройство содержит втощает подачу импульсов опорной частоты.

Формула изобретения

55

ления является группой выходов кода микроопера1Ц1Й первого канала, вторая группа выходов блока микропрограммно- го управления соединена с группой входов блока контроля на четность, группа входов кода операций первого канала соединена с группой входов кода операций блока микропрограммного

управления, выход разрешения блока задания режима соединен с разрешающим входом блока останова, первый выход которого соединен с входом останова блока пуска, выход первого

разряда группы выходов задания режима блока задания режима соединен с входом сброса распределителя тактовых импульсов, группа выходов которого соединена с группами синхровходов

блока микропрограммного управления, блока пуска и является группой син-

хровходов первого канала, выход блока пуска соединен с разрешающим входом распределителя тактовых импульсов, выход задания опорной частоты блока задания режима соединен с входом опорной частоты распределителя тактовых импульсов, выход второго разряда группы выходов задания режима блока задания режима соединен с первым разрешаняцим входом блока пуска, группа выходов кода микроопераций первого канала является первой группой информационных выходов устройства, группа синхровыходов первого канала является первой группой синхровыходов устройства, группа входов кода операций первого канала является первой группой управляющих входов

устройства, отличающееся тем, что, с целью повышения достоверности контроля и расширения области применения за счет возможности использования в двухканальной вычислитель

рой канал и в каждый канал дополнительно введены блок сравнения данных, блок фиксации сбоев, блок повторения микрокоманд и блок утфавления син- - хронизацией, первый и второй выходы которого являются соответственно выходами первого и второго разрядов группы выходов согласования каждого канала, первый, третий и четвертый выходы блока управления синхронизацией соединены соответственно.с информационным входом блока пуска, входом синхронизации блока сравнения данньвс и входом сишсронизации распределителя

5

тактовых имттульсов, группа выхоцов которого соединена с группами сннхро- входов блока управления синхронизацией, блока фиксации сбоев и блока повторения микрокоманд, выход которого и первая и вторая группы вькодов соединены соответственно с первым разрешающим входом блока управления синхронизацией, группой управляющих входов микропрограммного управления и группой входов сброса блока фиксации сбоев,первая и вторая группЪ выходов которого соединены соответственно с группой инфор мационных входов блока повторения микрокоманд и группой информационных входов блока останова, вторая группа выходов блока фиксации сбоев образует выходы разрядов групиы выходов согласования каждого канала, группа выходов блока контроля на четность соединена с группой информа1Д1онных входов блока фиксации сбоев, выход блока сравнения данных соединен с информационным входом блока фиксации сбоев, выход первого разряда группы выходов распределителя тактовых импульсов соединен с синхровходом блока останова, второй выход которого является выходом отказа каждого канала, первый и третий выходы блока останова соединены соответственно с вторым разрешакицим входом и входом сбросу блока управления синхронизацией, выход пуска блока задания режима Соединен с входом признака пуска блока управления синхронизацией, выход первого разряда группы выходов задания режима блока задания соединен с входами сброса блока фиксации сбоев и блока повторения микрокоманд, первая и вторая группы входов данных каждого канала соединены соответственно с первой и второй группами информационных входов блока сравнения данных, входы первого, второго, третьего разрядов группы входов согласования каждого канала соединены соответственно с информационным входом блока останова, входом признака согласования блока управления синхронизацией и вторым разрешающим входом блока пуска, группа выходов задания . режима блока задания режима соединена с группами разрешающих входов блоков останова и управления синхронизацией, выход блока пуска соединен с третьим разрешающим входом блока управления синхронизацией, выходы отказа перво-

0

5

0

0

5

0

5

5

го и второго каналов япляются первым и вторым выходами отказа устройства соответственно, группа выходов согласования первого (второго) канала соединена с группой входов согласования второго (первого) канала, группа выходов кода микроопера1Щй и группа синхровмходов аторого канала являются соответственно группой информационных и второй группой синхровьтходов устройства, первая (вторая гр Т1па информационных входов устройства соединена с первой (второй) группой входов данных первого канала и второй (первой) группой входов данных второго канала, вторая группа управляющих входов устройства гооттшена с группой входов кода оперяпиГ) второго канала, причем блок фиксац; и сбоеч содержит с первого по пятый триггеры, группу злементов И и элемрт;т №11 , информационные с псргого по третий триггеров образуют информационную группу входов блока фиксащш сбоев, S- R-пходы четвертгт., триггера являются соответственно информагшон- ным входом и входом сброса блока фиксации сбоев, синхровходы с первого по третий триггеров, сич. пятого триггера и первые входы элементов И группы обрл зуют группу синхровхо доп блока фиксации сбоев, входы сброса с первого по третий трнгтеров и пятого триггера, первый вход элемента КГГИ и вторые входы элементов И группы образуют группу входов сброса блока фиксащ и сбоев, вьгходы элемента ИЛИ, второго и третьего триггеров образуют первую группу выходов блока фиксации сбоев, в 1ходы первого второго, третьего и пятого триггеров соединены с третьими входами соответственно первого, второго, третьего и четвертого злементов И группы, выходы которых и выход четвертого триггера образуют вторую группу выходов блока фиксации сбоев, выходы с первого по третий триггеров соединены соответственно с второго по четвертый входами элемента ИЛИ, выход которого соединен с информационным входом пятого триггера, причем блок повторения микрокоманд содержит счетчик, первый и второй коммутаторы,с первого по четвертый элементы И, первьгй и вто- рой элементы ИЛИ и формирователь импульсов, выходы первого, второго и третьего элементов И соединены соот2513

ветстпенно со счетным входом счетчк- ка, с первым и вторым входами первого элемента ИЛИ, выход которого соединен с входом сброса счетчика, первые входы первого н второго элементов И, прямой вход третьего элемента И, управляюишй вход перво о коммутатора и перпьш. ннформа1шоннын вход второго коммутатора образуют группу синхро- входов блока повторения микрокоманд, вход сброса которого подключен к третьему входу первого элемента ИЛИ и зторому информационному входу второго коммутатора, второй вход перво- го элеме1 та И, инверсный вход третьего элемента И, первый вход второго элемента ИЛИ, уп15авляющлй вход второ- г о тсоммутатора и первый информагщонны вход ;1{-рВ(ЗГо коммутатора образуют группу информационных входов блока П1)нгсре тия микрокомавд, инверсный , второго элемента ИЛИ соединен с BTopciM информационным входом первого коммутатора, инверсным входом чет- зертпго элемента И и является выходом блока повторения микрокоманд, выход первого разряда счетчика соединен с вторым входом второго элемента ШШ, зглход первого элемента ИЛИ и выход второго разряда счетчика образуют BTopyFo группу выходов блока повторения микрокоманд, выходы формироват.е- ля импульсов, первого и второго коммутаторов и инверсный выход четвертого элемента И образуют первую группу выходов блока повторения микрокоманд, прямой и инверсный выходы третьего разряда и выход четвертого разряда счетчика соединены соответственно с входом формирователя импульсов, прямым входом четвертого элемента И и вторым входом второго элемента И.

Q д 0 J5 g ,.

35

0

5

1726

четвертым выходом блока управления синхронизагщей, выход первого элемента И соединен с S-входом первого триггера, выход второго элемента И соединен с С-входом первого триггера, с первым информационным входом коммутатора и через элемент задержки с R-входами четвертого и пятого три:- геров, выходы четвертого и пятого триггеров соединены соответственно с первым и вторым входами второго элемента И, прямой вход первого элемента И, С-вход шестого триггера и С-вход второго триггера образуют группу синхровходов блока управления синхронизацией, вход сброса которого подключен к R-входу шестого триггера, первый разрешаюпщй вход блока управления синхронизацией подклю тен к инверсному входу первого элемента И и первому входу третьего элемента И, D-вход второго триггера, первый управляющий вход коммутатора, второй вход третьего элемента И, второй вход элемента ИЛИ и R-вход седьмого триггера образуют группу разрешающих входов блока управления синхронизацией, вход признака пуска которого подключен к S-вхо- ду седьмого триггера и второму информационному входу коммутатора, второй управляющий вход которого является вторым разрешающим входом блока управления синхронизацией, третий разре- шакндий вход которого подключен к С-входу седьмого триггера,D-вход первого триггера, D-вход третьего триггера, D-входы четвертого и пятого триггеров и D-вход седьмого триггера подключены к шине нулевого потент ала, выход третьего элемента И соединен с D-входом шестого триггера, выход которого соединен с С-входом четвертого триггера и первым входом четвертого элемента И, выход которого является вторым выходом блока управления синхронизацией, выход седьмого триггера соединен с вторым входом четвертого элемента И и является первым выходом блока управления синхронизацией, третий выход которого подключен к выходу коммутатора, вход признака согласования блока управления синхронизацией подключен к С-входу пятого триггера, выход второго триггера соединен с С-входом третьего триггера.

1

.2

иг.

Jfc

92:3

Риг.б

Уигл

4tfi

иг.В

19

/о

.j -С -()/

15S.1

Шо о

)

7

J60Vaz. 10

ш

I

т

т

--он

131

132

fPuz.11

fPii2.f2

Состояние тормотени нана/га

Фиг. 15

| Микропрограммное устройство управления | 1982 |

|

SU1020825A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Усольцев А.Г., Кислин Б.П | |||

| Сопряжения дискретных каналов связи с ЭВМ | |||

| - М.: Связь, 1973, с | |||

| Рогульчатое веретено | 1922 |

|

SU142A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-05-23—Публикация

1986-08-11—Подача