,.изобретение относится к автоматике и вычислительной технике и может быть использовано для управления специализированным устройством, р Мотающим в реальном масштабе времени, или в качестве контроллера АСУ iех- нологическими процессами, обеспечивающего управление по сигналам от датчиков в штатном и аварийном режимах.

Цель изобретения - расширение области применения за счет реализации возможности лтлнза комплекса логических условий и повышение быстродействия устройства.

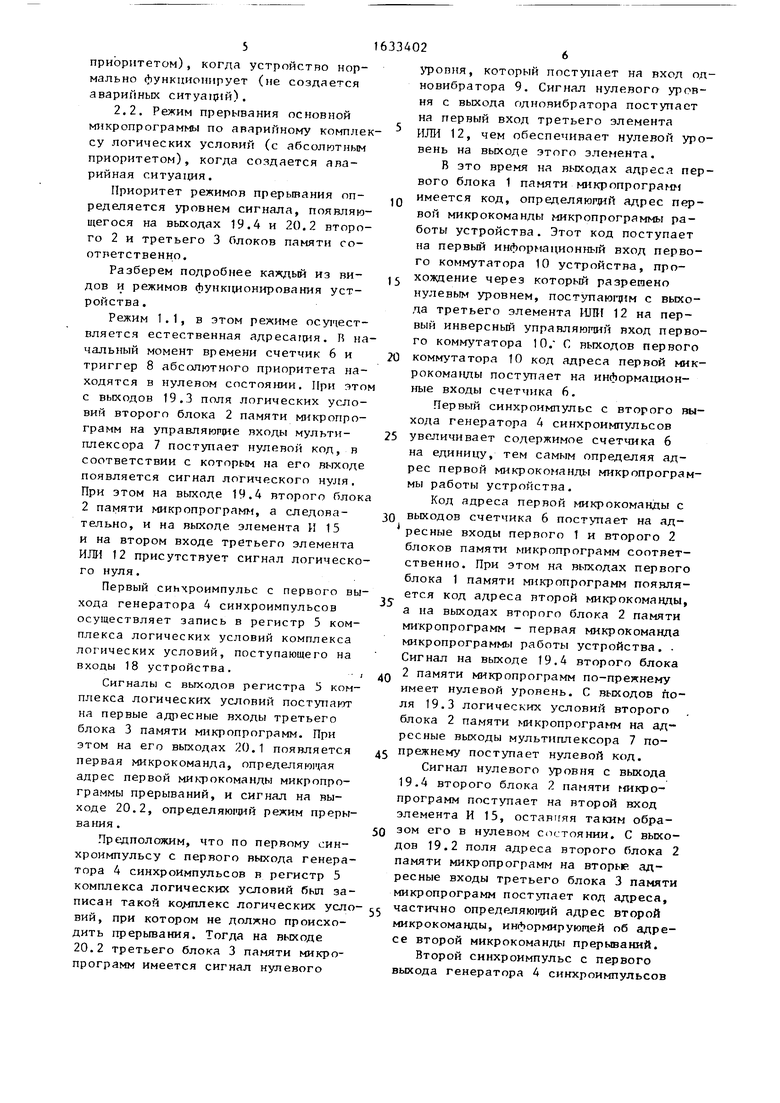

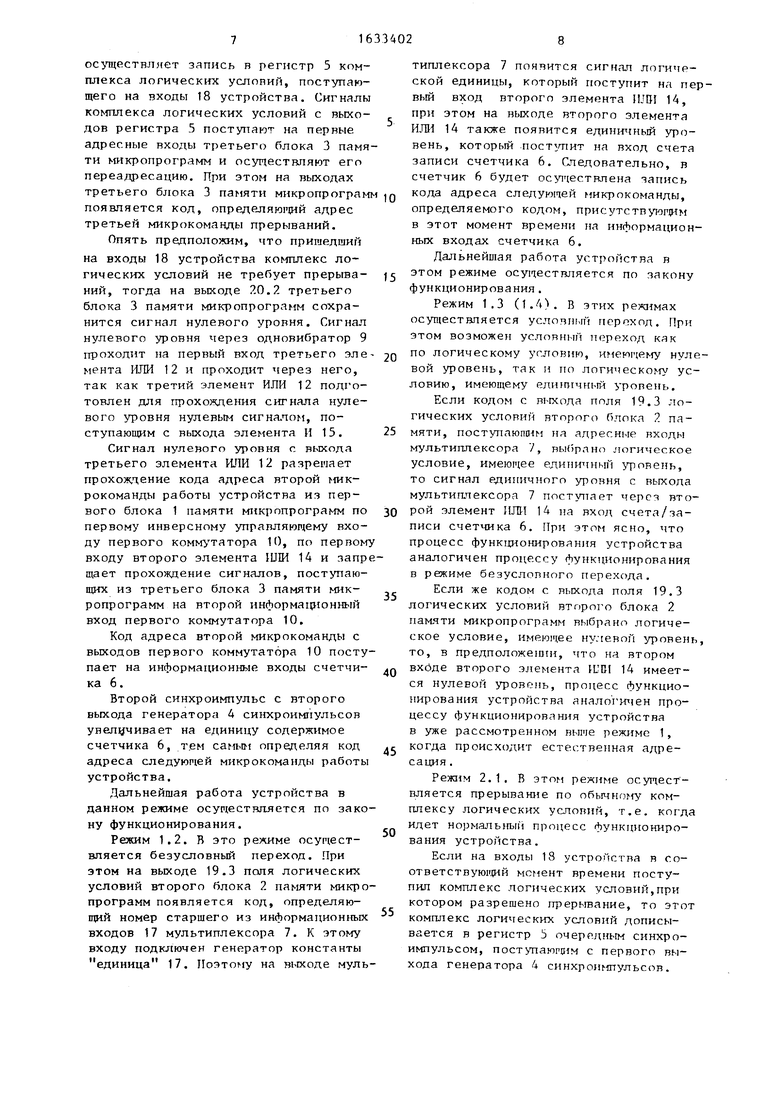

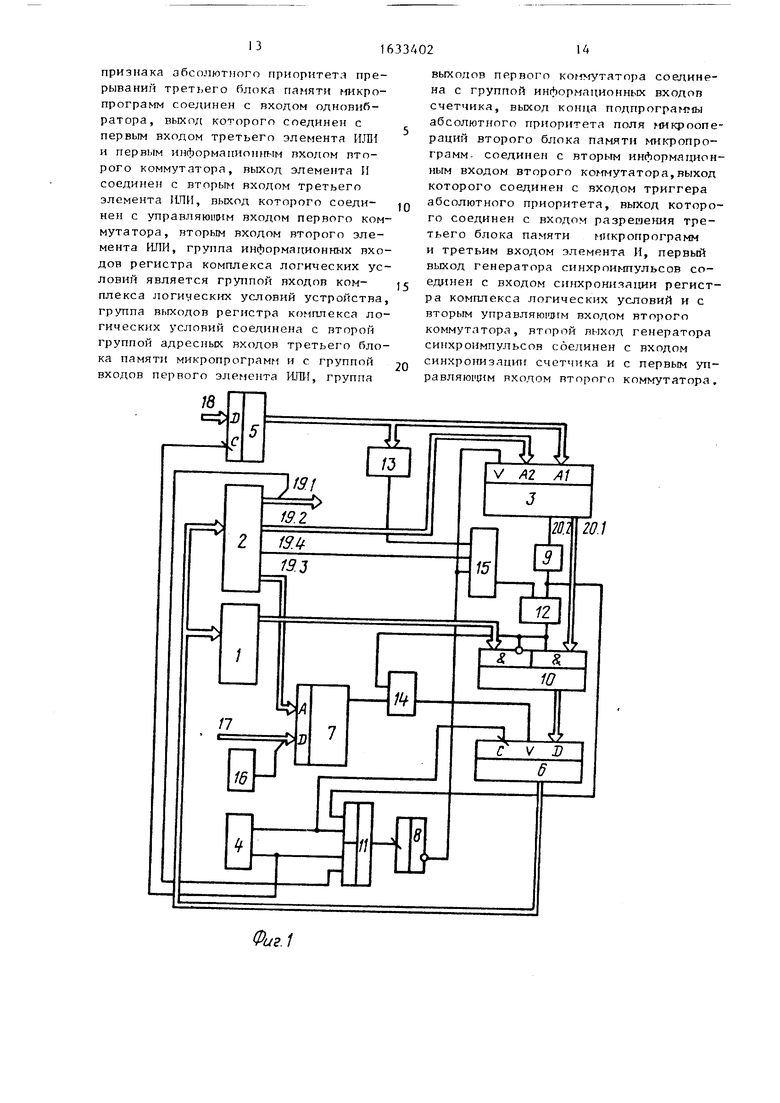

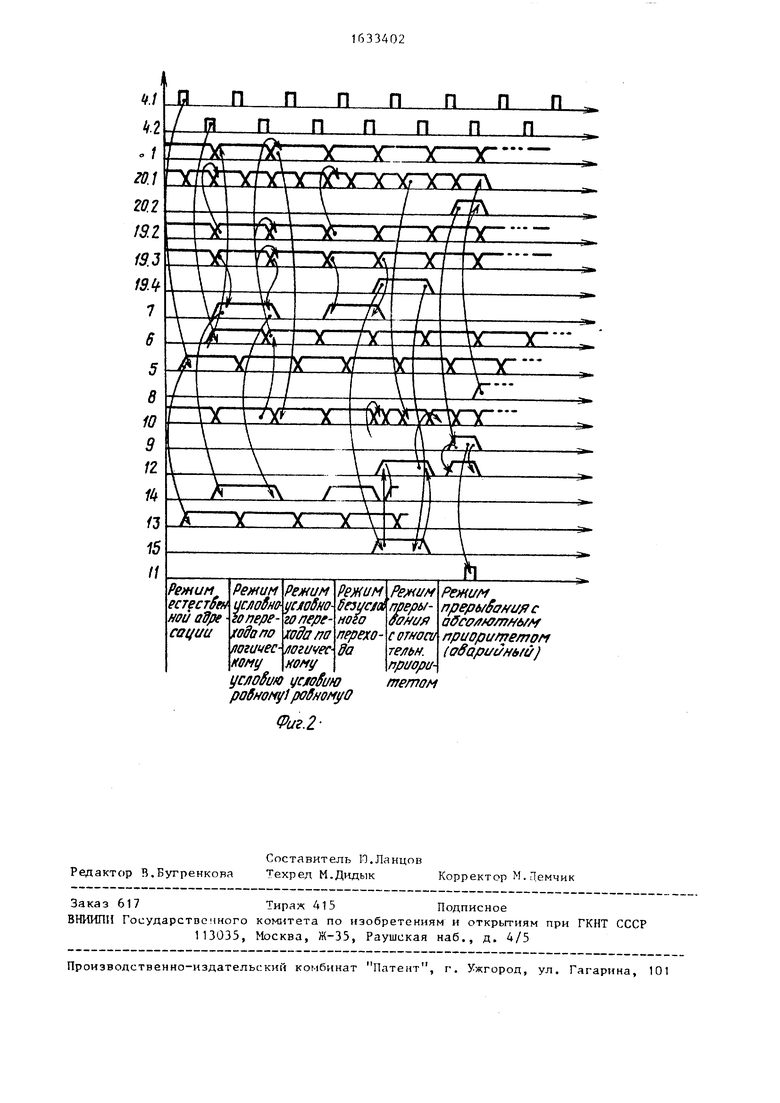

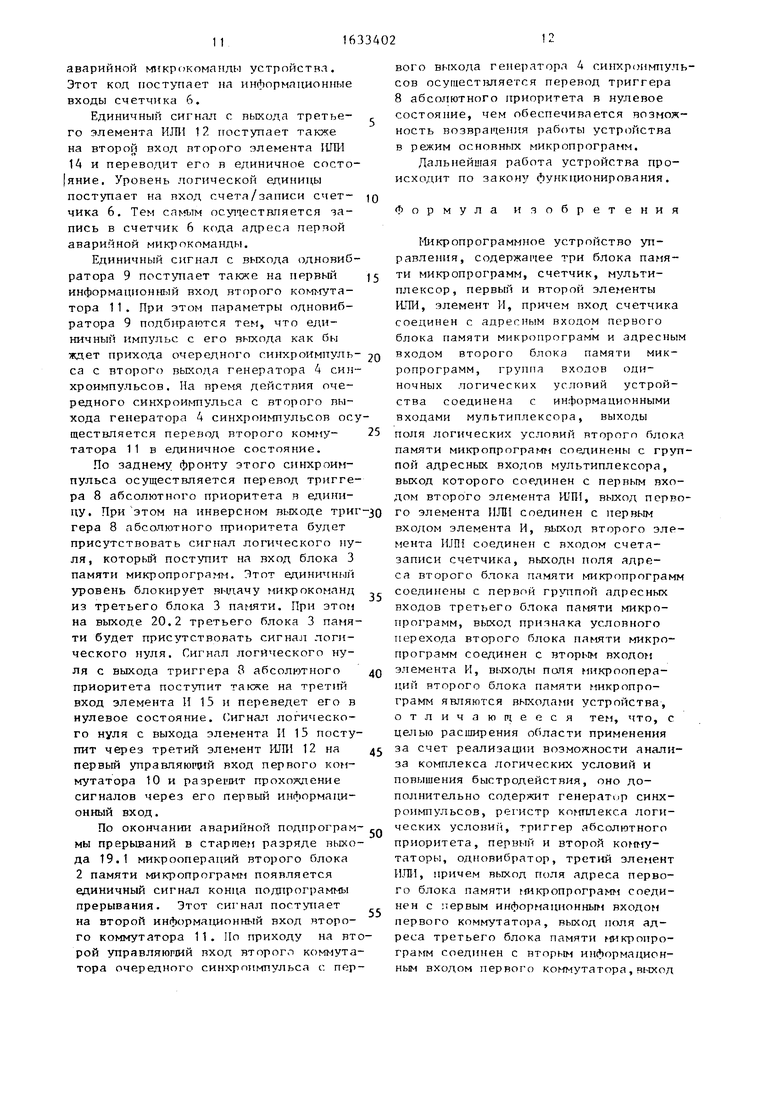

На фиг.1 представлена Лункциональ- ная схема устройства; на Лиг.2 - временная диаграмма Лункционирования устройства.

Устройство (Лиг.1) содержит пер- вый-третим 1-3 блоки памяти микропрограмм, генератор 4 синхроимпульсов, регистр 5 комплекса логически условий, счетчик 6, мультиплексор 7, триггер 8 абсолютного приоритета, одно- вибратор 9, первым 10 и второй 11 коммутаторы, элементы ИЛИ 12-14, элемент И 15, генератор константы единица 16, группу 1/ входов одиночных

съ со

со

Is3

логических условий, группу 18 входов 1 комплекса логических условий.

Кроме этого, блок 2 памяти имеет выходы поля 19.1 микроопераций поля 19.2 адреса, поля 19.3 логических условий и признака 19.4 условного перехода, а блок 3 памяти - выходы поля 20.1 адреса и признака 20.2 абсолютного приоритета.

Блок 1 памяти служит для хранения и выдачи информации об адресах основных микропрограмм, а также об адресах подпрограмм, обеспечивающих работу микропрограммного устройства управления в аварийном режиме.

Блок 2 памяти предназначен для хранения и выдачи микропрограмм, обеспечивающих работу микропрограммного устройства управления в режиме основных программ и в режиме подпрограмм прерываний.

Блок 3 памяти предназначен для хра нения и выдачи адресов подпрограмм прерываний, обладающих относительным приоритетом. Считвание информации из блока 3 памяти разрешена только при наличии единичного сигнала на входе V.

Генератор 4 синхроимпульсов служит для синхронизации работы функциональных элементов, входящих в устройство.

Регистр 5 комплекса логических условий предназначен для приема, хранения и выдачи значений комплекса логических условий, поступающего на входы 18 микропрограммного устройства управления. Сигналы на его выходах определяют часть адреса микрокоманды, хранящейся в третьем блоке 3 памяти.

м

Счетчик 6 служит для переадресации в- соответствующие моменты времени или при соответствующих условиях первого и второго блоков 1 и 2 памяти соответственно.

Мультиплексор 7 служит для коммутации на первый вход второго элемента ИЛИ 14 одного из входов логических условий устройства ИЛИ 17 выхода генератора константы единица 16.

Мультиплексор 7 реализует следующую логическую функцию

Cf- D0-A,- A,... AmVD, x

гп

х А.

Aft...Amv.. .VT)h A , А2...А

где D и А ; - сигналы на информационных и адресных (управляк г(нх) входах мультиплексора,

С,

i 1,n, j 1,п.

Триггер 8 абсолютного приоритета, одновибратор 9, первый коммутатор 10, JQ второй коммутатор 11, третий элемент

ИЛИ 12, первый элемент ИЛИ 13, второй . элемент ИЛИ 14, элемент И 15 предназначены для управления режимами работы устройства.

15 Генератор константы единица 16 служит для организации работы устройства в режиме безусловного перехода. Принцип работы микропрограммного устройства управления заключается п 20 следующем.

Имеется два микрорежима работ.. 1. Работа микропрограммного устройства управления по выполнению непрерываемых микропрограмм. 25 2. Работа микропрограммного уст- роства управления по выполнению прерываемых микропрограмм.

Каждый из видов работ имеет свои режимы.

3Q Рассмотрим режимы для первого макрорежима :

1.1.Режим естественной адресации, когда переадресация счетчика 6 осуществляется импульсными сигналами, приходящими на вход С(-Н) счетчика

6 от генератора 4 синхроимпульсов.

1.2.Режим безусловного перехода, когда переадресация счетчика 6 осуие- ствляется при поступлении единичного сигнала на вход счета/записи счетчика 6 с выхода второго элемента ИЛИ 14.

1„3. Режим условного перехода по нулевому логическому условию, когда дс переадресация счетчика 6 осуществляется по приходу на его вход счета/за- писи сигнала нулевого уровня, синхросигналом с второго выхода генератора 4 синхроимпульсов.

1.4. Режим условного перехода по единичному логическому условию,когда переадресация счетчика 6 осуществляется по приходу единичного уровня на вход счета/записи.

Для второго макрорежима работ существуют следующие режимы:

2.К Режим прерывания основной мик- микропрограммы по обычному комплексу логических, условий (с относительным

35

40

50

55

5

приоритетом), когда устройство нормально функционирует (не создается аварийных ситуаций).

2.2. Режим прерывания основной микропрограммы по аварийному комплесу логических условий (с абсолютным приоритетом), когда создается аварийная ситуация.

Приоритет режимов прерывания определяется уровнем сигнала, появляющегося на выходах 19.4 и 20.2 второго 2 и третьего 3 блоков памяти соответственно.

Разберем подробнее каждый из видов и режимов функционирования устройства .

Режим 1.1, в этом режиме осуществляется естественная адресация. R нчальный момент времени счетчик 6 и триггер 8 абсолютного приоритета находятся в нулевом состоянии. При эт с выходов 19.3 поля логических условий второго блока 2 памяти микропрограмм на управляющие входы мультиплексора 7 поступает нулевой код, в соответствии с которым на его выход появляется сигнал логического нуля. При этом на выходе 19.4 второго бло 2 памяти микропрограмм, а следовательно, и на выходе элемента И 15 и на втором входе третьего элемента ИЛИ 12 присутствует сигнал логическго нуля.

Первый синхроимпульс с первого выхода генератора 4 синхроимпульсов осуществляет запись в регистр 5 комплекса логических условий комплекса логических условий, поступающего на входы 18 устройства.-

Сигналы с выходов регистра 5 комплекса логических условий поступают на первые адресные входы третьего блока 3 памяти микропрограмм. При этом на его выходах 20.1 появляется первая микрокоманда, определяющая адрес первой микрокоманды микропрограммы прерываний, и сигнал на выходе 20.2, определяющий режим прерывания .

Предположим, что по первому синхроимпульсу с первого выхода генератора 4 синхроимпульсов в регистр 5 комплекса логических условий был эа

0

5

0

5

уропня, который поступает на вход од- новибратора 9. Сигнал нулевого уровня с выхода однояибратора поступает на первый вход третьего элемента ИЛИ 12, чем обеспечивает нулевой уровень на выходе этого элемента.

В это время на выходах адреса первого блока 1 памяти микропрограмм имеется код, определяющий адрес первой микрокоманды микропрограммы работы устройства. Этот код поступает на первый информационный вход первого коммутатора 10 устройства, прохождение через который разрешено нулевым уровнем, поступающим с выхода третьего элемента ИЛИ 12 на первый инверсный управляющий вход первого коммутатора 10. С выходов первого коммутатора 10 код адреса первой микрокоманды поступает на информационные входы счетчика 6.

Первый синхроимпульс с второго выхода генератора 4 синхроимпульсов увеличивает содержимое счетчика 6 на единицу, тем самым определяя адрес первой микрокоманды микропрограммы работы устройства.

Код адреса первой микрокоманды с выходов счетчика 6 поступает на адресные входы первого 1 и второго 2 блоков памяти микропрограмм соответственно. При этом на выходах первого блока 1 памяти микропрограмм появляется код адреса второй микрокоманды, а на выходах второго блока 2 памяти микропрограмм - первая микрокоманда микропрограммы работы устройства. . Сигнал на выходе 19.4 второго блока 2 памяти микропрограмм по-прежнему имеет нулевой уровень. С выходов поля 19.3 логических условий второго блока 2 памяти микропрограмм на адресные выходы мультиплексора 7 по- 5 прежнему поступает нулевой код.

Сигнал нулевого уровня с выхода 19.4 второго блока 2 памяти микропрограмм поступает на второй вход элемента И 15, оставляя таким образом его в нулевом состоянии. С выходов 19.2 поля адреса второго блока 2 памяти микропрограмм на вторые, адресные входы третьего блока 3 памяти микропрограмм поступает код адреса,

0

j

5

0

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Микропрограммное устройство управления с динамической памятью | 1985 |

|

SU1260954A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134936A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1259262A1 |

| Устройство для программного управления и контроля | 1985 |

|

SU1280574A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1270772A1 |

| Многоканальная микропрограммная управляющая система | 1985 |

|

SU1280628A1 |

| Процессор | 1983 |

|

SU1213485A1 |

Изобретение относится к автоматике и вычислительнон технике и может быть использовано для управления специализированным устройством, работающим в реапыюм масштабе времени, или в качестве контроллера ACV технологическими процессами, обеспечивающего управление по сигналам от датчиков в штатном и аварийном режимах. Цель изобретения - расширение области применения за счет реализации возможности анализа комплекса логических условий и повышение быстродействия устройства на основе обеспечения возможности совместного хранения и реализации в одном устройстве как подпрограмм, обладающих относитетышм приоритетом, так и подпрограмм, об- ладакнчих абсолютным приоритетом, со- ответствуклчих обработке аварийных ситуаций. Микропрограммное устройство содержит три блока памяти микропрограмм, счетчик, мультиплексор, элементы ИЛИ, И, генератор синхроимпульсов, регистр комплекса логических условий, триггер абсолютного приоритета, два коммутатора, генератор константы единица, одновибратор.2 ил. с $ ел

писан такой комплекс логических уело- ее частично определяющий адрес второй

вий, при котором не должно происходить прерывания. Тогда на выходе 20.2 третьего блока 3 памяти микропрограмм имеется сигнал нулевого

микрокоманды, информирующей об адре се второй микрокоманды прерываний. Второй синхроимпульс с первого выхода генератора 4 синхроимпульсов

микрокоманды, информирующей об адресе второй микрокоманды прерываний. Второй синхроимпульс с первого выхода генератора 4 синхроимпульсов

осуществляет запись в регистр 5 комплекса логических условий, поступающего на входы 18 устройства. Сигналы комплекса логических условий с выходов регистра 5 поступают на первые адресные входы третьего блока 3 памяти микропрограмм и осуществляют его переадресацию. При этом на выходах третьего блока 3 памяти микропрограм появляется код, определяющий адрес третьей микрокоманды прерываний.

Опять предположим, что пришедший на входы 18 устройства комплекс логических условий не требует прерыва- ний, тогда на выходе 20.2 третьего блока 3 памяти микропрограмм сохранится сигнал нулевого уровня. Сигнал нулевого уровня через одновибратор 9 проходит на первый вход третьего эле мента ИЛИ 12 и проходит через него, так как третий элемент ИЛИ 12 подготовлен для прохождения сигнала нулевого уровня нулевым сигналом, поступающим с выхода элемента И 15.

Сигнал нулевого уровня с выхода третьего элемента ИЛИ 12 разрешает прохождение кода адреса второй микрокоманды работы устройства из первого блока 1 памяти микропрограмм по первому инверсному управляющему входу первого коммутатора 10, по первом входу второго элемента ИЛИ 14 и запрщает прохождение сигналов, поступающих из третьего блока 3 памяти мик- ропрограмм на второй информационный вход первого коммутатора 10.

Код адреса второй микрокоманды с выходов первого коммутатора 10 поступает на информационные входы счетчи- ка 6.

Второй синхроимпульс с второго выхода генератора 4 синхроимпульсов увеличивает на единицу содержимое счетчика 6, тем самым определяя код адреса следующей микрокоманды работы устройства.

Дальнейшая работа устройства в данном режиме осуществляется по закону функционирования.

Режим 1.2. В это режиме осуществляется безусловный переход. При этом на выходе 19.3 поля логических условий второго блока 2 памяти микропрограмм появляется код, определяющий номер старшего из информационных входов 17 мультиплексора 7. К этому входу подключен генератор константы единица 17. Поэтому на выходе муль

5

5 0

0

Q

г

5

типлексора 7 появится сигнал логической единицы, который поступит на первый вход второго элемента ИЛИ 14, при этом на выходе второго элемента ИЛИ 14 также появится единичный уровень, который поступит на вход счета записи счетчика 6. Следовательно, в счетчик 6 будет осуществлена запись кода адреса следующей микрокоманды, определяемого кодом, присутствующим в этот момент времени на информационных входах счетчика 6.

Дальнейшая работа устройства в этом режиме осуществляется по закону функционирования.

Режим 1.3 (1.4. В этих режимах осуществляется условный переход. При этом возможен условный переход как по логическому условию, имеющему нулевой уровень, так и по логическому условию, имеющему единичный уровень.

Если кодом с выхода поля 19.3 логических условий второго блока 2 памяти, поступаюгдам на адресные входы мультиплексора 7, выбрано логическое условие, имеющее единичный уровень, то сигнал единичного уровня с выхода мультиплексора 7 поступает через второй элемент ИЛИ 14 на вход счета/записи счетчика 6. При этом ясно, что процесс функционирования устройства аналогичен процессу функционирования в режиме безусловного перехода.

Если же кодом с выхода поля 19.3 логических условий второго блока 2 памяти микропрограмм выбрано логическое условие, имеющее нулевой уровень, то, в предположешш, что на втором входе второго элемента ИЛИ 14 имеется нулевой уровень, процесс функционирования устройства аналогичен процессу функционирования устройства в уже рассмотренном выше режиме 1, когда происходит естественная адресация .

Режим 2.1. В этом режиме осуществляется прерывание по обычному комплексу логических условий, т.е. когда идет нормальный процесс функционирования устройства.

Если на входы 18 устройства в соответствующий момент времени поступил комплекс логических условий,при котором разрешено прерывание, то этот комплекс логических условий дописывается в регистр Ь очередным синхроимпульсом, поступающая с первого выхода генератора 4 синхроимпульсов.

Комплекс логических условий с выходов регистра 5 поступает на первые адресные входы третьего блока 3 памяти микропрограмм и осуществляет его пе- реадресацию.

При этом на выходе 19.4 второго блока 2 памяти микропрограмм присутствует сигнал логической единицы. Комплекс логических условий, разре- шающих прерывание, не может быть нулевым. Поэтому, поступая на входы первого элемента ИЛИ 13, сигналы комплекса логических условий переводят его в единичное состояние. Единичные сигналы с выхода первого элемента ИЛИ 13 и выхода 19.4 второго блока 2 памяти микропрограмм поступают на входы элемента И 15 и переводят его в единичное состояние. Единичный сигнал с выхода элемента И 15 поступает через третий элемент ИЛИ 12 на второй управляющий вход первого коммутатора 10, тем самым разрешая прохождение через него кода, определяю- щего адрес микрокоманды прерывания по обычному комплексу логических условий, поступающему с выходов третьего блока 3 памяти микропрограмм.

Код адреса первой микрокоманды прерывания по обычному комплексу логических условий поступает на информационные входы счетчика 6.

Единичный сигнал с выхода третьего элемента ИЛИ 13 поступает на первый управляющий вход первого коммутатора 10. тем самым запрещая прохождение через него кода, определяющего адрес микрокоманды, основной микропрограммы из первого блока 1 памяти микропрограмм.

Единичный сигнал с выхода третьего элемента ИЛИ 13 поступает на второй вход второго элемента ИЛИ 14, про проходит через него и поступает на вход счета/записи счетчика 6. При этом в счетчик 6 записывается информация о коде адреса первой микрокоманды прерываний, которая t выходов счетчика 6 поступит на адресные входы первого и второго блоков 1 и / памяти соответственно.

После перехода устройства в новое состояние возможны два случая.

В первом случае возобновление работы устройства после прерывания осуществляется с места программы, принадлежащего такому ее участку, где также разрешено прерывание. Тогда при на

JQ 2Q 25

о

.

г

5

0

личии необходимого комплекса логических условий на входах 18 устройства осуществляется переход в новое место программы. Если новое место программы также принадлежит ее участку, где разрешено прерывание, процесс перехода продолжается до тех пор, пока устройство не перейдет в состояние, соответствующее участку программы, где прерывание запрещено.

Во втором случае возобновление работы устройства осуществляется с места программы, принадлежащего к такому ее участку, где прерывание запрещено или отсутствуют условия прерывания. В этом случае с указанного места программы продолжается обычная работа устройства.

Режим 2.2. В этом режиме осуществляется прерывание микропрограммы по аварийному комплексу логических условий. При этом адреса аварийных микропрограмм записываются в первый блок 1 памяти микропрограмм.

В этом режиме устройство работает следующим образом. Аварийный комплекс логических условий поступает на входы 18 устройства. По очередному синхроимпульсу, поступающему на С- вход регистра 5 комплекса логических условий с первого выхода генератора 4 синхроимпульсов .комплекс логических условий записывается в регистр 5.С выхода регистра 5 сигналы комплекса логических услочий поступают на первые адресные входы третьего блока 3 памяти микропрограмм, при этом переадресуя его для обработки устройством аварийной подпрограммы. При этом на выходе 20.2 третьего блока 3 памяти микропрограмм будет присутствовать сигнал логической единицы. Это значит, что выполнение этой микрокоманды обладает абсолютным приоритетом по отношению ко всем другим видам микрокоманд. Единичный сигнал с выхода 20.2 третьего блока 3 памяти микропрограмм поступает через одновиоратор 9 на первый вход третьего элемента IDB-I 12 и переводит его в единичное состояние. Единичный уровень с выхода третьего элемента ИЛИ 12 разрешает по - второму управляющее входу первого коммутатора 10 прохождение сигналов через второй информационный вход первого коммутатора 10. Следовательно, на выходах первого коммутатора 10 будет присутствовать код адреса первой

аварийной микрокоманды устройства. Этот код поступает на информационные входы счетчика 6.

Единичный сигнал с ныхода третье- го элемента ИЛИ 12 поступает также на второй вход второго элемента ИЛИ 14 и переводит его в единичное состо- |яние. Уровень логической единицы поступает на вход счета/записи счет- чика 6. Тем самым осуществляется запись в счетчик 6 кода адреса первой аварийной микрокоманды.

Единичный сигнал с выхода одновиб- ратора 9 поступает также на первый информационный вход второго коммутатора 11 . При этом параметры одновиб- ратора 9 подбираются тем, что единичный импульс с его выхода как бы ждет прихода очередного синхроимпульса с второго выхода генератора 4 синхроимпульсов. На время действия очередного синхроимпульса с второго выхода генератора 4 синхроимпульсов осу ществляется перевод второго коммутатора 11 в единичное состояние.

По заднему фронту этого синхроимпульса осуществляется перевод триггера 8 абсолютного приоритета в единицу. При этом на инверсном выходе триг гера 8 абсолютного приоритета будет присутствовать сигнал логического нуля, который поступит на вход блока 3 памяти микропрограмм. Этот единичный уровень блокирует выдачу микрокоманд из третьего блока 3 памяти. При этом на выходе 20.2 третьего блока 3 памяти будет присутствовать сигнал логического нуля. Сигнал логического нуля с выхода триггера 8 абсолютного приоритета поступит также на третий вход элемента И 15 и переведет его в нулевое состояние. Сигнал логического нуля с выхода элемента И 15 поступит через третий элемент ИЛИ 12 на первый управляющий вход первого коммутатора 10 и разрешит прохождение сигналов через его первый информационный вход.

По окончании аварийной подпрограммы прерываний в старшем разряде выхода 19.1 микроопераций второго блока 2 памяти микропрограмм появляется единичный сигнал конца подпрограммы прерывания. Этот сигнал поступает на второй информационный вход второго коммутатора 11. По приходу на второй управляющий вход второго коммутатора очередного синхроимпульса с пер

0

5

5

о

5

0

5

0

5

вого выхода генератора 4 синхроимпульсов осуществляется перевод триггера 8 абсолютного приоритета в нулевое состояние, чем обеспечивается возможность возвращения работы устройства в режим основных микропрограмм.

Дальнейшая работа устройства происходит по закону функционирования.

Формула изобретения

Микропрограммное устройство управления, содержащее три блока памяти микропрограмм, счетчик, мультиплексор, первый и второй элементы ИЛИ, элемент И, причем вход счетчика соединен с адресным входом первого блока памяти микропрограмм и адресным входом второго блока памяти микропрограмм, группа входов одиночных логических условий устройства соединена с информационными входами мультиплексора, выходы поля логических условий второго блока памяти микропрограмм соединены с группой адресных входов мультиплексора, выход которого соединен с первым входом второго элемента ИЛИ, выход первого элемента ИЛИ соединен с первым входом элемента И, выход второго элемента ИЛИ соединен с входом счета- записи счетчика, выходы поля адреса второго блока памяти микропрограмм соединены с первой группой адресных входов третьего блока памяти микропрограмм, выход признака условного перехода второго блока памяти микропрограмм соединен с вторым входом элемента И, выходы поля микроопераций второго блока памяти микропрограмм являются выходами устройства, отличающееся тем, что, с целью расширения области применения за счет реализации возможности анализа комплекса логических условий и повышения быстродействия, оно дополнительно содержит генератор синхроимпульсов, регистр комплекса логических условий, триггер абсолютного приоритета, первый и второй коммутаторы, одновибратор, третий элемент ИЛИ, причем выход поля адреса первого блока памяти микропрограмм соединен с первым информационным входом первого коммутатора, выход поля адреса третьего блока памяти микропрограмм соединен с вторым информационным входом первого коммутатора,выход

признака абсолютного приоритета прерывании третьего блока памяти микропрограмм соединен с входом одновиб- ратора, выход которого соединен с первым входом третьего элемента ИЛИ и первым информационным входом второго коммутатора, выход элемента II соединен с вторым входом третьего элемента ИЛИ, выход которого соеди- ней с управляющим входом первого коммутатора, вторым входом второго элемента ИЛИ, группа информационных входов регистра комплекса логических условий является группой входов ком- плекса логиуеских условий устройства, группа выходов регистра комплекса логических условий соединена с второй группой адресных входов третьего блока памяти микропрограмм и с группой входов первого элемента ИЛИ, группа

выходов первого коммутатора соединена с группой информационных входов счетчика, выход конца подпрограммы абсолютного приоритета поля микроопераций второго блока памяти микропрограмм- соединен с вторым информационным входом второго коммутатора,выход которого соединен с входом триггера абсолютного приоритета, выход которого соединен с входом разрешения третьего блока памяти микропрограмм и третьим входом элемента И, первый выход генератора синхроимпульсов соединен с входом синхронизации регистра комплекса логических условий и с вторым управляющим входом второго коммутатора, второй выход генератора синхроимпульсов соединен с входом синхронизации счетчика и с первым управляющим входом второго коммутатора.

If.}

услойиа ycjioSifH) робному родномуО

Риг.2ПCL

тельн. приоритетом

прерывания с а&с0/гнгтнб/м приоритетом (аварийный)

| Устройство для программного управления | 1982 |

|

SU1057927A1 |

| С, 05 В 19/18, 1984 | |||

| Микропрограммное устройство управления | 1985 |

|

SU1322281A1 |

| С Oh F , 198/. | |||

Авторы

Даты

1991-03-07—Публикация

1989-03-30—Подача