Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах помехоустойчивого хранения информации.

Целью изобретения является повышение стойкости ячейки к ионизирующим излучениям.

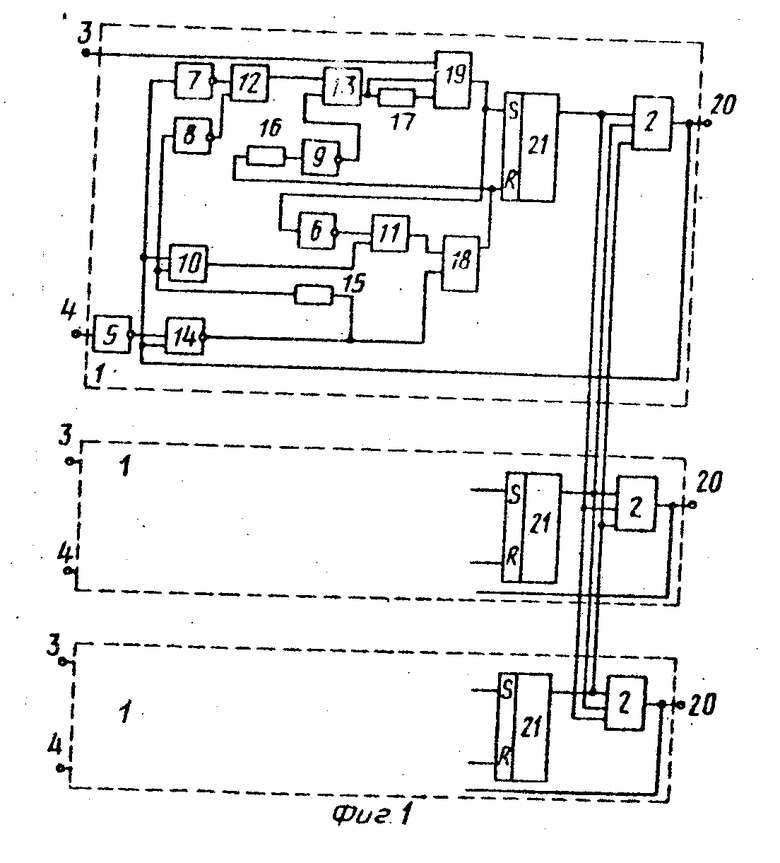

На фиг. 1 представлена электрическая схема резервированной ячейки памяти; на фиг. 2 эпюры работы ячейки в различных режимах.

Резервированная ячейка памяти содержит три разряда 1, каждый из которых состоит из мажоритарного элемента 2, входа 3 установки, входа 4 сброса, пяти элементов НЕ 5-9, четырех элементов И 10-13, элемента И-НЕ 14, трех элементов 15-17 задержки, двух элементов ИЛИ 18, 19, выхода 20, триггера 21.

Резервированная ячейка памяти работает следующим образом.

В режиме хранения на входы 3 и 4 подаются низкие уровни, соответствующие отсутствию управляющих сигналов. При этом триггер 21 находится в нулевом или единичном состоянии. В нулевом состоянии на входах триггеров 21 и выходах 20 удерживается низкий потенциал, а в единичном высокий. Установка резервированной ячейки памяти в нулевое состояние производится подачей импульса положительной полярности на входы 4 установки в нулевое состояние. Это импульс, поступая хотя бы в двух разрядах 1 через первый элемент НЕ 5, элемент И-НЕ 14 и элемент ИЛИ 18 на вход сброса триггера 21, переключает их в нулевое состояние. При этом по большинству входов мажоритарные элементы 2 оказываются в нулевом состоянии. В результате низкий уровень с выходов мажоритарных элементов 2 поступает на выходы 20 и входы элементов И-НЕ 14, которые принудительно формируют на входах сброса триггеров 21 всех разрядов 1 высокие уровни, сохраняющиеся и после снятия импульса с входов 4. Принудительные высокие уровни на входах сброса триггеров 21 всех разрядов 1 исключают переключение триггеров 21 в единичное состояние помехами, действующими на их входах установки.

Установка резервированной ячейки памяти в единичное состояние производится подачей импульса положительной полярности на вход 3. Этот импульс поступает на входы установки триггеров 21 и переводит их в единичное состояние независимо от присутствия высокого уровня на их входах сброса, так как вход установки имеет приоритет. При этом по большинству входов в единичном состоянии. В результате высокий уровень с выходов мажоритарных элементов 2 поступает на выходы 20 и входы элементов И-НЕ 14, снимая принудительный высокий уровень с входов сброса триггеров 21. В случае, если триггеры 21 находились в нулевом состоянии и под действием ионизирующего излучения произошло переключение триггеров 21 всех разрядов 1 в единичное состояние, в начальный момент на выходе первого элемента И 10 сформируется импульс высокого уровня, так как на выходе элемента 15 задержки будет время задержки сигнала высокого уровня, так как на выходе элемента И-НЕ 14 поддерживается принудительный высокий уровень, и на другой вход первого элемента И 10 будет подаваться сигнал высокого уровня с выхода мажоритарного элемента 2. Сигнал высокого уровня с первого элемента И 10 подается на вход второго элемента И 11, на другой вход которого подается сигнал высокого уровня со второго элемента НЕ 6, таким образом на выходе второго элемента И 11 сформируется сигнал высокого уровня, который через элемент ИЛИ 18 подается на вход сброса триггера 21 и переводит его в нулевое состояние, после чего на выходе элемента И-НЕ 14 будет сформирован принудительный сигнал высокого уровня. При этом время задержки выбирается меньше длительности входного импульса. В режиме хранения, когда триггеры 21 находятся в единичном состоянии на выходе второго элемента И 11 сигнал будет иметь низкий уровень, так как на выходе первого элемента И 10 будет сигнал низкого уровня.

При установке ячейки памяти в единичное состояние, при действии импульса положительной полярности на входе 3 низкий уровень сигнала на выходе второго элемента И 11 обусловлен низким уровнем сигнала на выходе второго элемента НЕ 6.

В случае, если триггеры 21 находились в единичном состоянии и под действием ионизирующего излучения произошло переключение в нулевое состояние, то в начальный момент, определяемый временем задержки элементов 15, 16, на входах элементов НЕ 7, 8, 9 будет низкий уровень сигнала, что позволит получить на их выходах, а следовательно, и на входах третьего и четвертого элементов И 12, 13 сигнал высокого уровня, который через второй элемент ИЛИ 19 будет подан на вход установки триггера 21, что переведет его в единичное состояние.

По истечении времени задержки элемента 15 на его выходе появится импульс высокого уровня, с учетом того, что на втором входе первого элемента И 10 будет тоже импульс высокого уровня, на вход второго элемента И 11 будет подан сигнал высокого уровня. В это же время на выходе третьего элемента задержки 17 будет импульс высокого уровня, который будет через второй элемент ИЛИ 19 подан на приоритетный вход установки триггера 21 и через второй элемент НЕ 6 на вход второго элемента И 11, что обеспечит отсутствие сигнала высокого уровня на входе сброса и переключение в нулевое состояние.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕЗЕРВИРОВАННАЯ ЯЧЕЙКА ПАМЯТИ | 1988 |

|

SU1540565A1 |

| РЕЗЕРВИРОВАННАЯ ЯЧЕЙКА ПАМЯТИ | 1990 |

|

RU2072567C1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Устройство для вывода информации | 1991 |

|

SU1833857A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Резервированный счетчик импульсов | 1982 |

|

SU1023663A1 |

| Резервированный счетчик импульсов | 1985 |

|

SU1314449A1 |

| Многоканальный резервированный генератор | 1989 |

|

SU1699028A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Резервированный счетчик импульсов | 1981 |

|

SU982197A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах помехоустойчивого хранения информации. Целью изобретения является повышение стойкости ячейки к ионизирующим излучениям. Поставленная цель достигается тем, что ячейка содержит в каждом разряде 1 элементы НЕ 7, 8, 9, элементы И 12, 13, элементы 16, 17 задержки, второй элемент ИЛИ 19 с соответствующими связями. Стойкость к ионизирующим излучениям повышается за счет невозможности самопроизвольного переключения триггера 1 из единичного состояния в нулевое, так как при этом с помощью элементов задержки 16 и 17, элементов НЕ 7,8,9 элементов И 12, 13 через элемент ИЛИ 19 на вход установки триггера 21 подается сигнал высокого уровня. 2 ил.

Резервированная ячейка памяти по авт. св. N 1540565, отличающаяся тем, что, с целью повышения стойкости ячейки к ионизирующим излучениям, она содержит в каждом разряде третий, четвертый и пятый элементы НЕ, третий и четвертый элементы И, второй и третий элементы задержки, второй элемент ИЛИ, первый вход которого является входом установки соответствующего разряда ячейки, а выход соединен с входом установки триггера, вход сброса которого соединен с входом второго элемента задержки, выход которого соединен с входом пятого инвертора, выход которого соединен с первым входом четвертого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ и входом третьего элемента задержки, выход которого соединен с третьим входом второго элемента ИЛИ, входы третьего и четвертого элементов НЕ соединены с вторым и первым входами первого элемента И соответственно, а выходы с первым и вторыми входами третьего элемента И соответственно, выход которого соединен с вторым входом четвертого элемента И.

| РЕЗЕРВИРОВАННАЯ ЯЧЕЙКА ПАМЯТИ | 1988 |

|

SU1540565A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1996-12-27—Публикация

1989-04-11—Подача