Изобретение относится к вычислительной технике и может быть.использовано для накопления и вывода достоверной .информации во внешние устройства.

Целью изобретения является повышение достоверности выводимой информации путем резервирования информационных каналов, сравнением в процессе хранения информации каналов между собой и регенерации ее во всех каналах по принципу большинства.

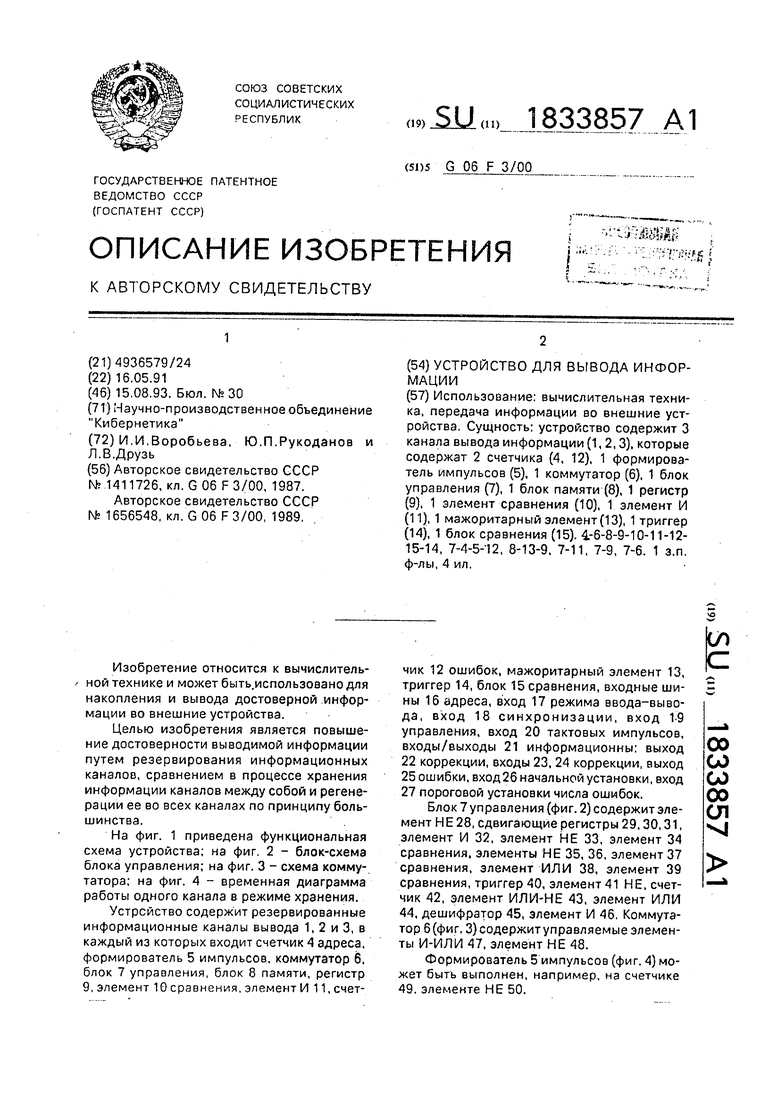

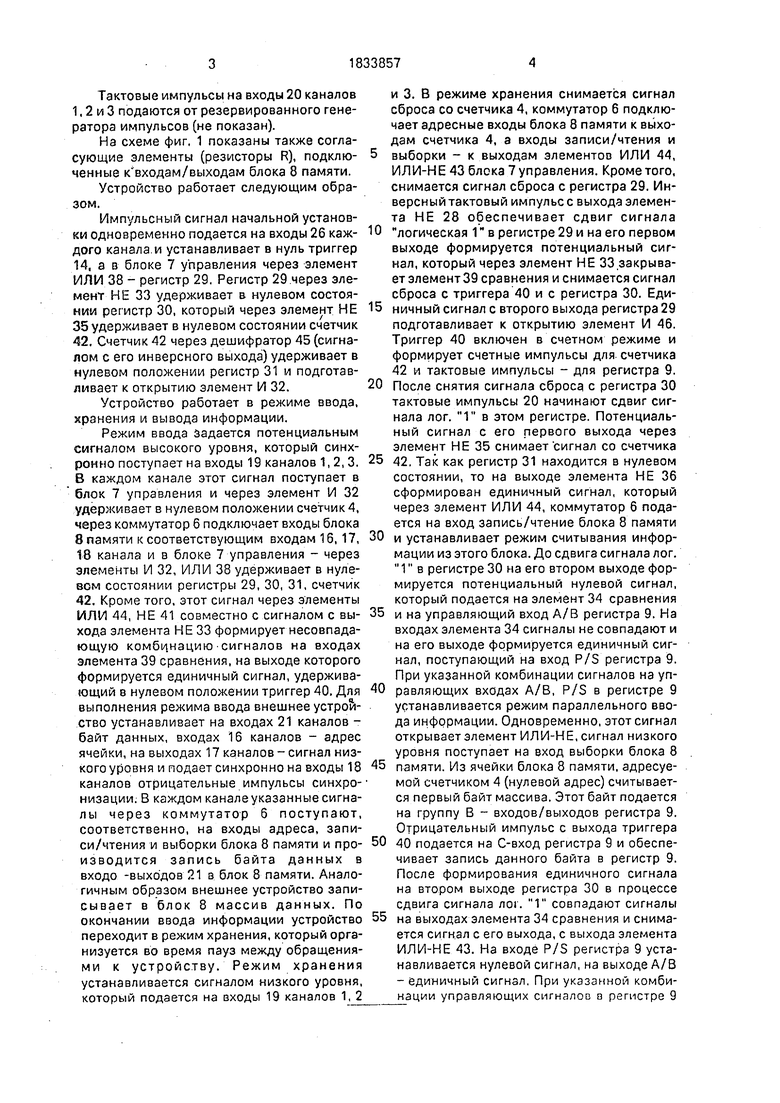

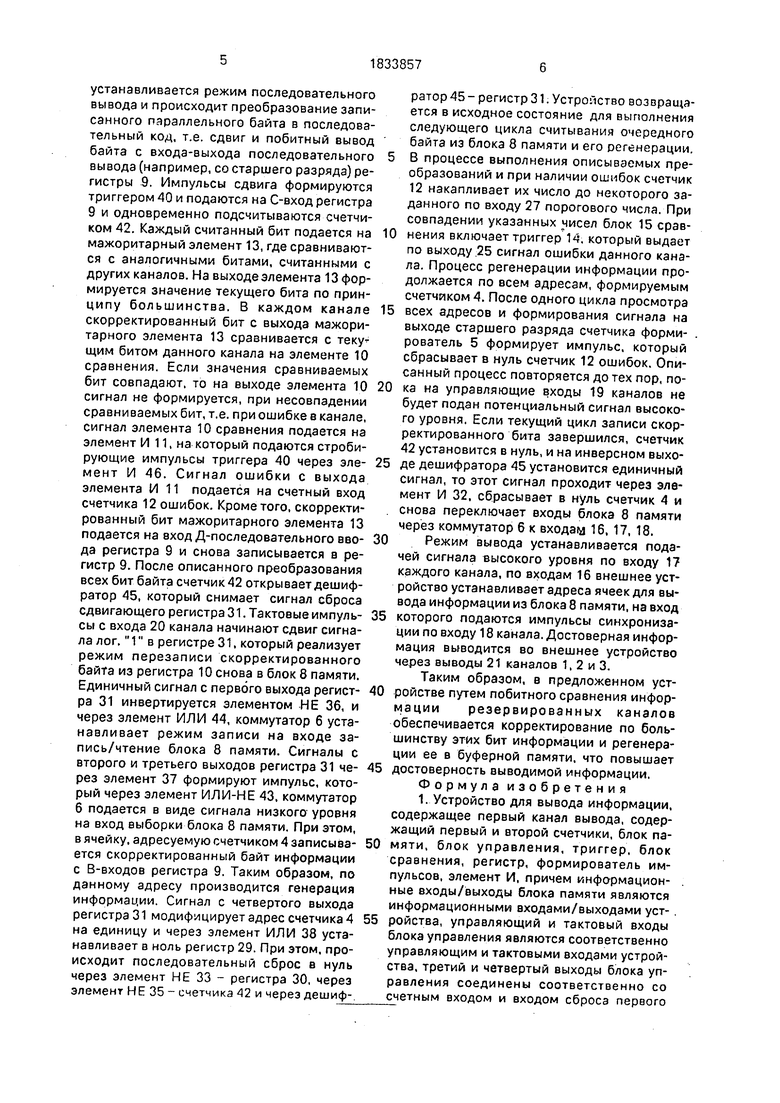

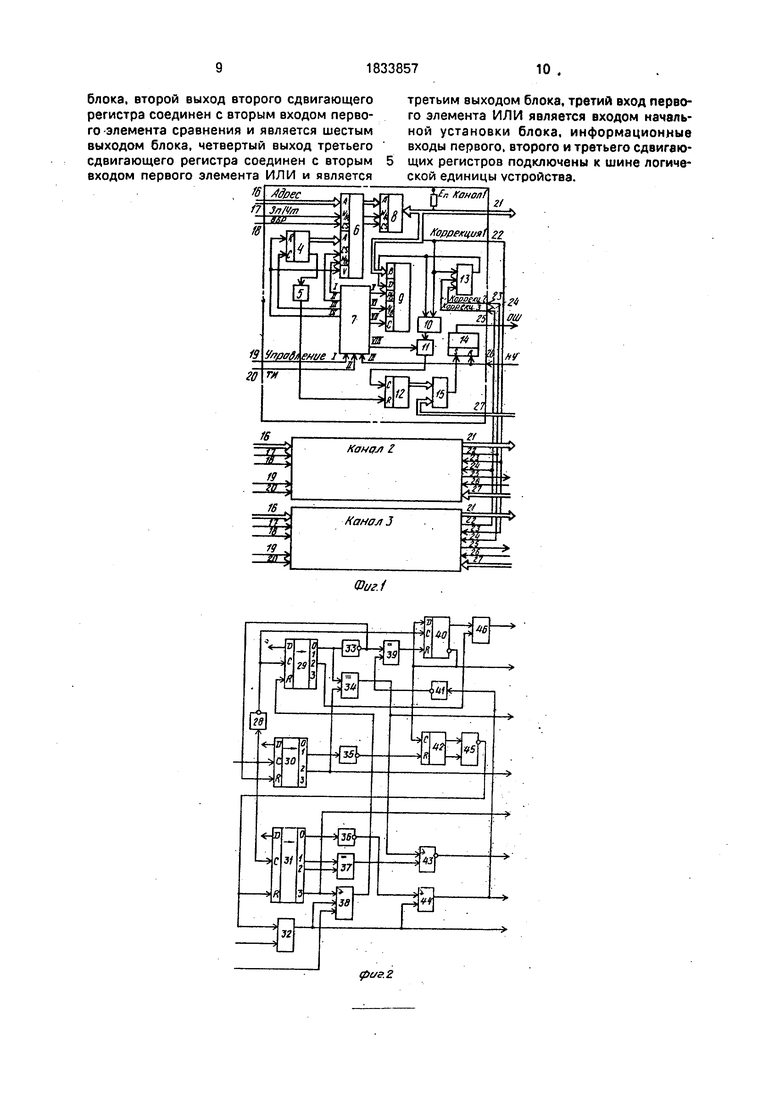

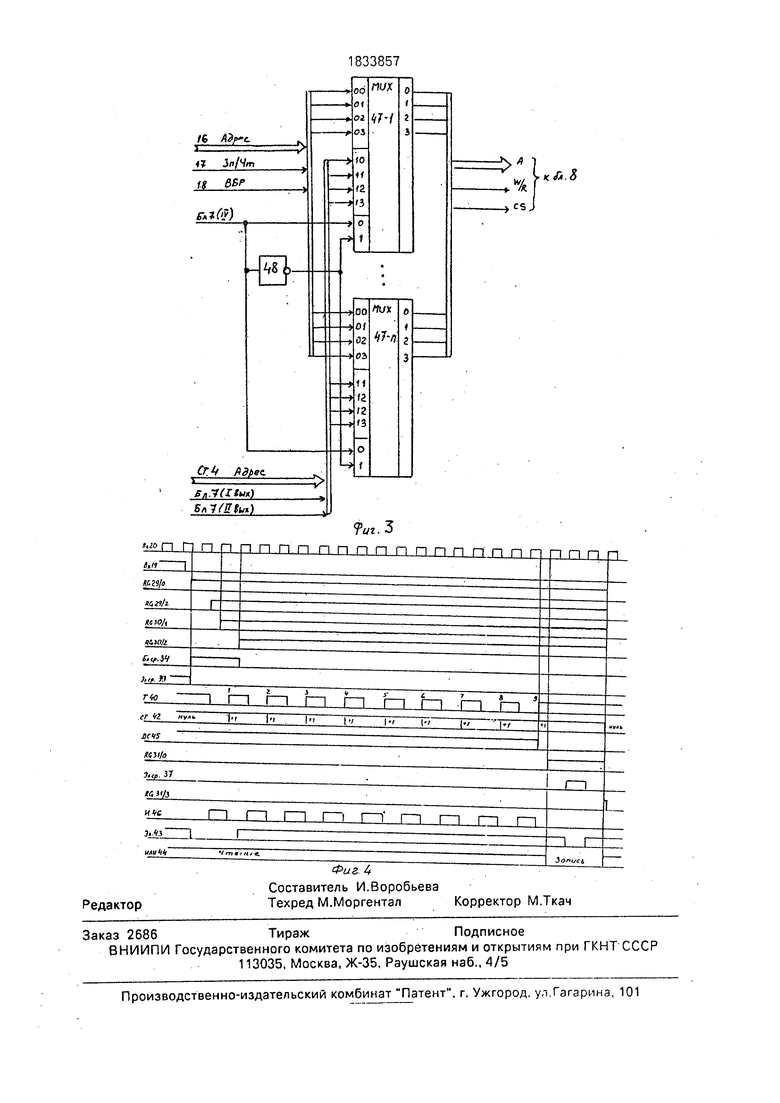

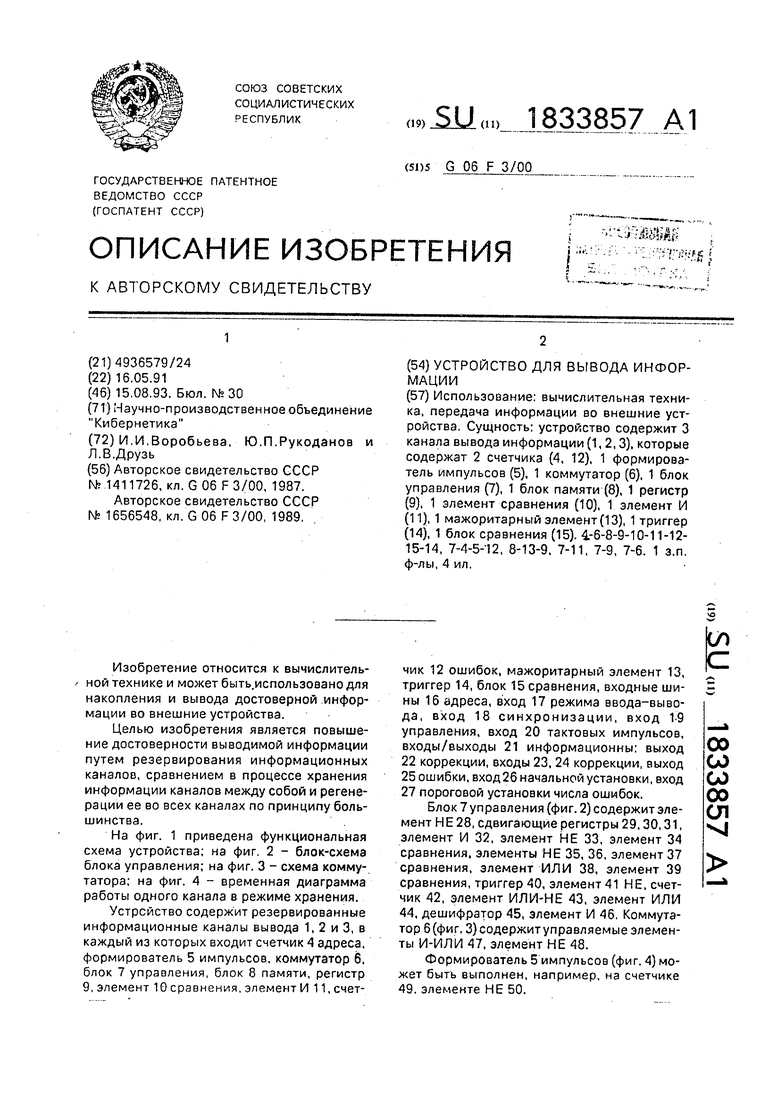

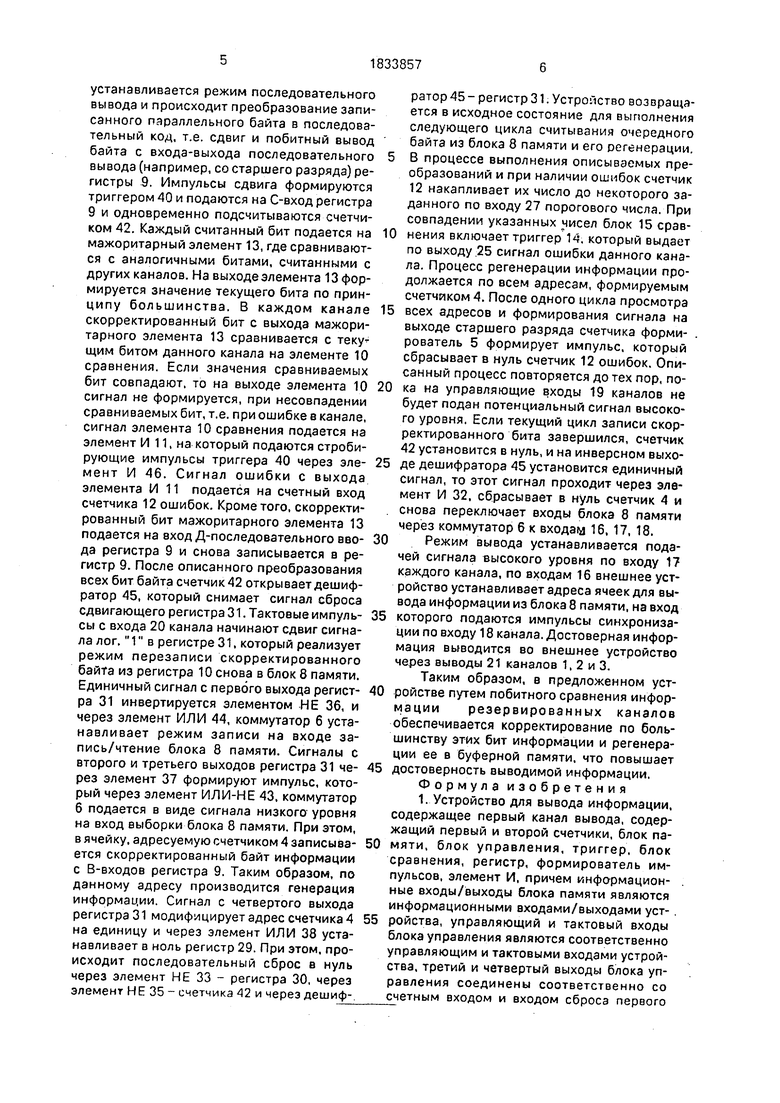

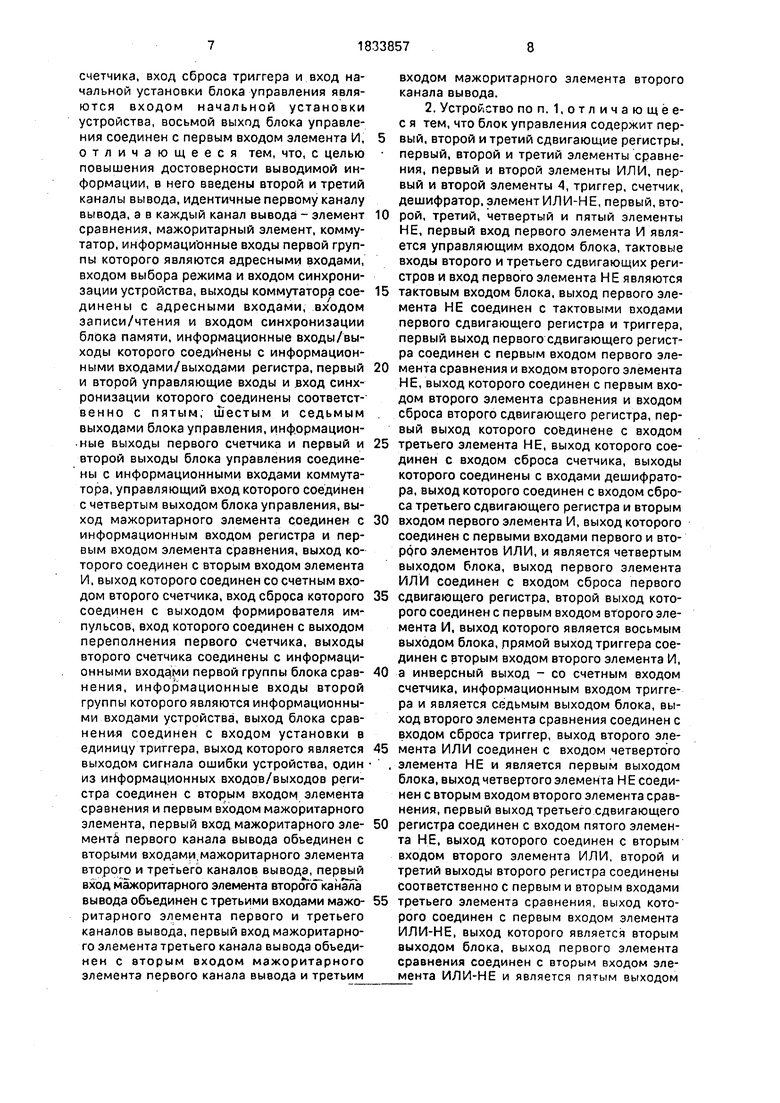

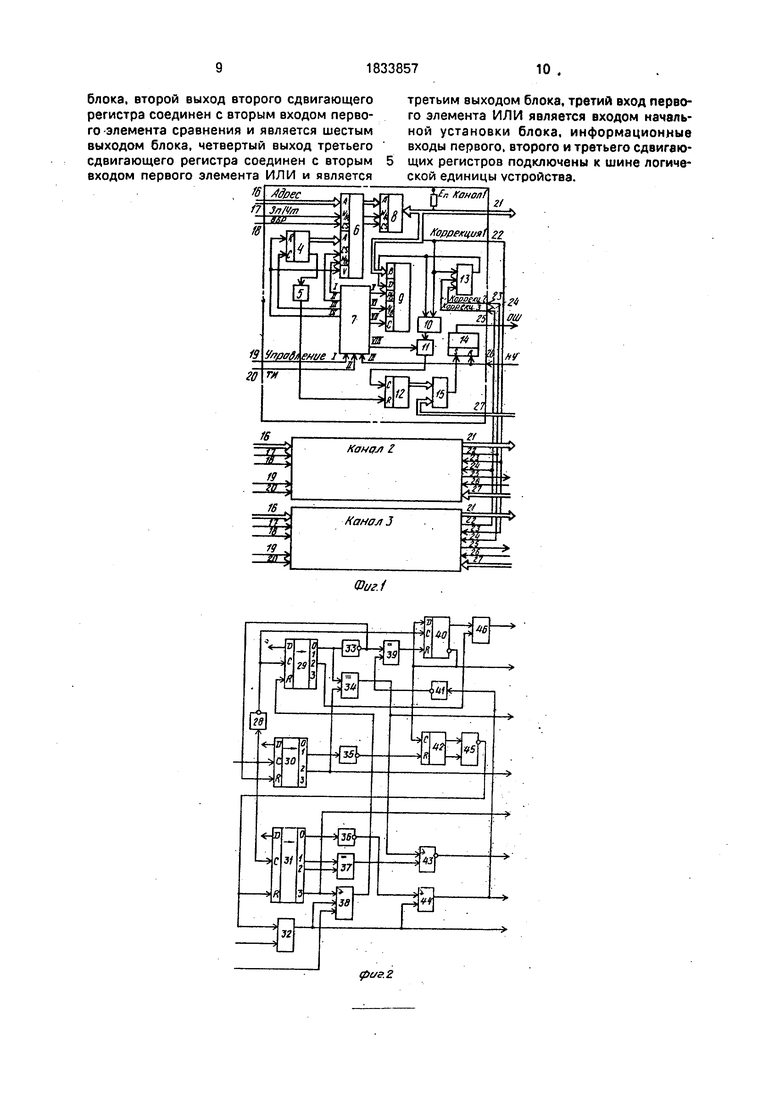

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - блок-схема блока управления; на фиг. 3 - схема коммутатора; на фиг. 4 - временная диаграмма работы одного канала в режиме хранения.

Устройство содержит резервированные информационные каналы вывода 1, 2 и 3, в каждый из которых входит счетчик 4 адреса, формирователь 5 импульсов, коммутатор 6, блок 7 управления, блок 8 памяти, регистр 9, элемент 10 с равнения, элемент И 11, счетчик 12 ошибок, мажоритарный элемент 13, триггер 14, блок 15 сравнения, входные шины 16 адреса, вход 17 режима ввода-вывода, вход 18 синхронизации, вход 19 управления, вход 20 тактовых импульсов, входы/выходы 21 информационны: выход 22 коррекции, входы 23, 24 коррекции, выход 25 ошибки, вход 26 начальной установки, вход 27 пороговой установки числа ошибок.

Блок 7управления (фиг. 2) содержит элемент Н Е 28, сдвигающие регистры 29,30,31, элемент И 32, элемент НЕ 33, элемент 34 сравнения, элементы НЕ 35, 36, элемент 37 сравнения, элемент ИЛИ 38, элемент 39 сравнения, триггер 40, элемент 41 НЕ, счетчик 42, элемент ИЛИ-НЕ 43, элемент ИЛИ 44, дешифратор 45, элемент И 46. Коммутатор 6 (фиг, 3) содержит управляемые элементы И-ИЛИ 47, элемент НЕ 48.

Формирователь 5 импульсов (фиг. 4) может быть выполнен, например, на счетчике 49. элементе НЕ 50.

00

с

00 СО

со

00

ел VI

Тактовые импульсы на входы 20 каналов 1,2 и 3 подаются от резервированного генератора импульсов (не показан).

На схеме фиг, 1 показаны также согласующие элементы (резисторы R), подключенные к входам/выходам блока 8 памяти. Устройство работает следующим образом.

Импульсный сигнал начальной установки одновременно подается на входы 26 каждого канала.и устанавливает в нуль триггер 14, а в блоке 7 управления через элемент ИЛИ 38 - регистр 29. Регистр 29 .через элемент НЕ 33 удерживает в нулевом состоянии регистр 30, который через элемент НЕ 35 удерживает в нулевом состоянии счетчик 42. Счетчик 42 через дешифратор 45 (сигналом с его инверсного выхода) удерживает в нулевом положении регистр 31 и подготавливает к открытию элемент И 32.

Устройство работает в режиме ввода, хранения и вывода информации.

Режим ввода задается потенциальным сигналом высокого уровня, который синхронно поступает на входы 19 каналов 1,2,3. В каждом канале этот сигнал поступает в блок 7 управления и через элемент И 32 удерживает в нулевом положении счетчик 4, через коммутатор 6 подключает входы блока 8 памяти к соответствующим входам 16, 17, 18 канала и в блоке 7 управления - через элементы И 32, ИЛИ 38 удерживает в нулевом состоянии регистры 29, 30, 31, счетчик 42. Кроме того, этот сигнал через элементы ИЛИ 44, НЕ 41 совместно с сигналом с выхода элемента НЕ 33 формирует несовпадающую комбинацию-сигналов на входах элемента 39 сравнения, на выходе которого формируется единичный сигнал, удерживающий в нулевом положении триггер 40. Для выполнения режима ввода внешнее устройство устанавливает на входах 21 каналов - байт данных, входах 16 каналов - адрес ячейки, на выходах 17 каналов - сигнал низкого уровня и подает синхронно на входы 18 каналов отрицательные импульсы синхронизации. В каждом канале указанные сигналы через коммутатор 6 поступают, соответственно, на входы адреса, записи/чтения и выборки блока 8 памяти и производится запись байта данных в входо -выходов 21 в блок 8 памяти. Аналогичным образом внешнее устройство записывает в блок 8 массив данных. По окончании ввода информации устройство переходит в режим хранения, который организуется во время пауз между обращениями к устройству. Режим хранения устанавливается сигналом низкого уровня, который подается на входы 19 каналов 1, 2

и 3. В режиме хранения снимается сигнал сброса со счетчика 4, коммутатор 6 подключает адресные входы блока 8 памяти к выходам счетчика 4, а входы записи/чтения и

выборки - к выходам элементов ИЛИ 44, ИЛИ-НЕ 43 блока 7 управления. Кроме того, снимается сигнал сброса с регистра 29. Инверсный тактовый импульс с выхода элемента НЕ 28 обеспечивает сдвиг сигнала

0 логическая 1 в регистре 29 и на его первом выходе формируется потенциальный сигнал, который через элемент НЕ 33 закрывает элементЗЭ сравнения и снимается сигнал сброса с триггера 40 и с регистра 30. Еди5 ничный сигнал с второго выхода регистра 29 подготавливает к открытию элемент И 46. Триггер 40 включен в счетном режиме и формирует счетные импульсы для счетчика 42 и тактовые импульсы - для регистра 9.

0 После снятия сигнала сброса с регистра 30 тактовые импульсы 20 начинают сдвиг сигнала лог. 1 в этом регистре. Потенциальный сигнал с его первого выхода через элемент НЕ 35 снимает сигнал со счетчика

5 42. Так как регистр 31 находится в нулевом состоянии, то на выходе элемента НЕ 36 сформирован единичный сигнал, который через элемент ИЛИ 44, коммутатор 6 подается на вход запись/чтение блока 8 памяти

0 и устанавливает режим считывания информации из этого блока. До сдвига сигнала лог. 1 в регистре 30 на его втором выходе формируется потенциальный нулевой сигнал, который подается на элемент 34 сравнения

5 и на управляющий вход А/В регистра 9. На входах элемента 34 сигналы не совпадают и на его выходе формируется единичный сигнал, поступающий на вход P/S регистра 9. При указанной комбинации сигналов на уп0 равляющих входах А/В, P/S в регистре 9 устанавливается режим параллельного ввода информации. Одновременно, этот сигнал открывает элемент ИЛИ-НЕ, сигнал низкого уровня поступает на вход выборки блока 8

5 памяти. Из ячейки блока 8 памяти, адресуемой счетчиком 4 (нулевой адрес) считывается первый байт массива. Этот байт подается на группу В - входов/выходов регистра 9. Отрицательный импульс с выхода триггера

0 40 подается на С-вход регистра 9 и обеспечивает запись данного байта в регистр 9. После формирования единичного сигнала на втором выходе регистра 30 в процессе сдвига сигнала лог. 1 совпадают сигналы

5 на выходах элемента 34 сравнения и снимается сигнал с его выхода, с выхода элемента ИЛИ-НЕ 43. На входе P/S регистра 9 устанавливается нулевой сигнал, на выходе А/В - единичный сигнал, При указанной комби- нации управляющих сигналов в регистре 9

устанавливается режим последовательного вывода и происходит преобразование записанного параллельного байта в последовательный код, т.е. сдвиг и побитный вывод байта с входа-выхода последовательного вывода (например, со старшего разряда) регистры 9. Импульсы сдвига формируются триггером 40 и подаются на С-вход регистра 9 и одновременно подсчитываются счетчиком 42. Каждый считанный бит подается на мажоритарный элемент 13, где сравниваются с аналогичными битами, считанными с других каналов. На выходе элемента 13 формируется значение текущего бита по принципу большинства. В каждом канале скорректированный бит с выхода мажоритарного элемента 13 сравнивается с текущим битом данного канала на элементе 10 сравнения. Если значения сравниваемых бит совпадают, то на выходе элемента 10 сигнал не формируется, при несовпадении сравниваемых бит, т.е. при ошибке в канале, сигнал элемента 10 сравнения подается на элемент И 11, на который подаются строби- рующие импульсы триггера 40 через элемент И 46. Сигнал ошибки с выхода элемента И 11 подается на счетный вход счетчика 12 ошибок. Кроме того, скорректированный бит мажоритарного элемента 13 подается на вход Д-последовательного ввода регистра 9 и снова записывается в регистр 9. После описанного преобразования всех бит байта счетчик 42 открывает дешифратор 45, который снимает сигнал сброса сдвигающего регистра 31. Тактовые импульсы с входа 20 канала начинают сдвиг сигнала лог. 1 в регистре 31, который реализует режим перезаписи скорректированного байта из регистра 10 снова в блок 8 памяти. Единичный сигнал с первого выхода регистра 31 инвертируется элементом НЕ 36, и через элемент ИЛИ 44, коммутатор 6 устанавливает режим записи на входе запись/чтение блока 8 памяти. Сигналы с второго и третьего выходов регистра 31 через элемент 37 формируют импульс, который через элемент ИЛИ-НЕ 43, коммутатор б подается в виде сигнала низкого уровня на вход выборки блока 8 памяти. При этом, в ячейку, адресуемую счетчиком 4 записывается скорректированный байт информации с В-входов регистра 9. Таким образом, по данному адресу производится генерация информации. Сигнал с четвертого выхода регистра 31 модифицирует адрес счетчика 4 на единицу и через элемент ИЛИ 38 устанавливает в ноль регистр 29. При этом, происходит последовательный сброс в нуль через элемент НЕ 33 - регистра 30, через элемент НЕ 35 - счетчика 42 и через дешиф-.

ратор 45 - регистр 31. Устройство возвращается в исходное состояние для выполнения следующего цикла считывания очередного байта из блока 8 памяти и его регенерации. 5 В процессе выполнения описываемых преобразований и при наличии ошибок счетчик 12 накапливает их число до некоторого заданного по входу 27 порогового числа. При совпадении указанных чисел блок 15 срав0 нения включает триггер 14. который выдает по выходу .25 сигнал ошибки данного канала. Процесс регенерации информации продолжается по всем адресам, формируемым счетчиком 4. После одного цикла просмотра

5 всех адресов и формирования сигнала на выходе старшего разряда счетчика формирователь 5 формирует импульс, который сбрасывает в нуль счетчик 12 ошибок. Описанный процесс повторяется до тех пор, по0 ка на управляющие входы 19 каналов не будет подан потенциальный сигнал высокого уровня. Если текущий цикл записи скорректированного бита завершился, счетчик 42 установится в нуль, и на инверсном выхо5 де дешифратора 45 установится единичный сигнал, то этот сигнал проходит через элемент И 32, сбрасывает в нуль счетчик 4 и снова переключает входы блока 8 памяти через коммутатор 6 к входам. 16, 17, 18.

0 Режим вывода устанавливается подачей сигнала высокого уровня по входу 17 каждого канала, по входам 16 внешнее устройство устанавливает адреса ячеек для вывода информации из блока 8 памяти, на вход

5 которого подаются импульсы синхронизации по входу 18 канала. Достоверная информация выводится во внешнее устройство через выводы 21 каналов 1, 2 и 3.

Таким образом, в предложенном уст0 ройстве путем побитного сравнения инфор- мации резервированных каналов обеспечивается корректирование по большинству этих бит информации и регенерации ее в буферной памяти, что повышает

5 достоверность выводимой информации. Формула изобретения 1. Устройство для вывода информации, содержащее первый канал вывода, содержащий первый и второй счетчики, блок па0 мяти, блок управления, триггер, блок сравнения, регистр, формирователь импульсов, элемент И, причем инфармацион- . ные входы/выходы блока памяти являются информационными входами/выходами уст-.

5 ройства, управляющий и тактовый входы блока управления являются соответственно управляющим и тактовыми входами устройства, третий и четвертый выходы блока управления соединены соответственно со счетным входом и входом сброса первого

счетчика, вход сброса триггера и вход начальной установки блока управления являются входом начальной установки устройства, восьмой выход блока управления соединен с первым входом элемента И, отличающееся тем, что, с целью повышения достоверности выводимой информации, в него введены второй и третий каналы вывода, идентичные первому каналу вывода, а в каждый канал вывода - элемент сравнения, мажоритарный элемент, коммутатор, информационные входы первой группы которого являются адресными входами, входом выбора режима и входом синхронизации устройства, выходы коммутатора сое- динены с адресными входами, входом записи/чтения и входом синхронизации блока памяти, информационные входы/выходы которого соединены с информационными входами/выходами регистра, первый и второй управляющие входы и вход синхронизации которого соединены соответственно с пятым, шестым и седьмым выходами блока управления, информацион- . ные выходы первого счетчика и первый и второй выходы блока управления соединены с информационными входами коммутатора, управляющий вход которого соединен с четвертым выходом блока управления, выход мажоритарного элемента соединен с информационным входом регистра и первым входом элемента сравнения, выход которого соединен с вторым входом элемента И, выход которого соединен со счетным входом второго счетчика, вход сброса которого соединен с выходом формирователя импульсов, вход которого соединен с выходом переполнения первого счетчика, выходы второго счетчика соединены с информационными входами первой группы блока срав- нения, информационные входы второй группы которого являются информационными входами устройства, выход блока сравнения соединен с входом установки в единицу триггера, выход которого является выходом сигнала ошибки устройства, один из информационных входов/выходов регистра соединен с вторым входом элемента сравнения и первым входом мажоритарного элемента, первый вход мажоритарного эле- мента первого канала вывода объединен с вторыми входами,мажоритарного элемента второго и третьего каналов вывода, первый вход мажоритарного элемента второпГканала вывода объединен с третьими входами мажо- ритарного элемента первого и третьего каналов вывода, первый вход мажоритарного элемента третьего канала вывода объединен с вторым входом мажоритарного элемента первого канала вывода и третьим

входом мажоритарного элемента второго канала вывода.

2. Устройство поп. 1,отличающёе- с я тем, что блок управления содержит первый, второй и третий сдвигающие регистры, первый, второй и третий элементы сравнения, первый и второй элементы ИЛИ, первый и второй элементы 4, триггер, счетчик, дешифратор, элементИЛИ-НЕ, первый, второй, третий, четвертый и пятый элементы НЕ, первый вход первого элемента И является управляющим входом блока, тактовые входы второго и третьего сдвигающих регистров и вход первого элемента НЕ являются тактовым входом блока, выход первого элемента НЕ соединен с тактовыми сходами первого сдвигающего регистра и триггера, первый выход первого сдвигающего регистра соединен с первым входом первого элемента сравнения и входом второго элемента НЕ, выход которого соединен с первым входом второго элемента сравнения и входом сброса второго сдвигающего регистра, первый выход которого соединене с входом третьего элемента НЕ, выход которого соединен с входом сброса счетчика, выходы которого соединены с входами дешифратора, выход которого соединен с входом сброса третьего сдвигающего регистра и вторым входом первого элемента И, выход которого соединен с первыми входами первого и второго элементов ИЛИ, и является четвертым выходом блока, выход первого элемента ИЛИ соединен с входом сброса первого сдвигающего регистра, второй выход которого соединен с первым входом второго элемента И, выход которого является восьмым выходом блока, прямой выход триггера соединен с вторым входом второго элемента И, а инверсный выход - со счетным входом счетчика, информационным входом триггера и является седьмым выходом блока, выход второго элемента сравнения соединен с входом сброса триггер, выход второго элемента ИЛИ соединен с входом четвертого элемента НЕ и является первым выходом блока, выход четвертого элемента НЕ соединен с вторым входом второго элемента сравнения, первый выход третьего сдвигающего регистра соединен с входом пятого элемента НЕ, выход которого соединен с вторым входом второго элемента ИЛИ, второй и третий выходы второго регистра соединены Соответственно с первым и вторым входами третьего элемента сравнения, выход которого соединен с первым входом элемента ИЛИ-НЕ, выход которого является вторым выходом блока, выход первого элемента сравнения соединен с вторым входом элемента ИЛИ-НЕ и является пятым выходом

блока, второй выход второго сдвигающеготретьим выходом блока, третий вход перво- регистра соединен с вторым входом перво-го элемента ИЛИ является входом началfaro элемента сравнения и является шестымной установки блока, информационные выходом блока, четвертый выход третьеговходы первого, второго и третьего сдвигаю- сдвигающего регистра соединен с вторым5 щих регистров подключены к шине логичевходом первого элемента ИЛИ и является ской единицы устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для вывода информации | 1989 |

|

SU1732349A1 |

| Устройство для двунаправленной передачи информации | 1991 |

|

SU1784987A1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Устройство для индикации | 1990 |

|

SU1795511A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Устройство для приема информации | 1988 |

|

SU1552216A1 |

| Устройство для управления ленточным перфоратором | 1990 |

|

SU1837333A1 |

| Устройство для коррекции ошибок внешней памяти | 1989 |

|

SU1662011A1 |

Использование: вычислительная техника, передача информации во внешние устройства, Сущность: устройство содержит 3 канала вывода информации (1, 2,3), которые содержат 2 счетчика (4, 12), 1 формирователь импульсов (5), 1 коммутатор (6), 1 блок управления (7), 1 блок памяти (8), 1 регистр

рс/е.2

fc/i.3

| Устройство для ввода информации | 1987 |

|

SU1411726A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вывода информации | 1989 |

|

SU1656548A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-08-15—Публикация

1991-05-16—Подача