Изс

бретение относится к цифровой вычислительной технике и может быть зовано в цифровых вычислит ел ь- стемах высокой производитель-

ИСПОЛ1 НЫХ CI

ности,

nej:b изобретения - сок ращение оборудования параллельного потокового проце4сора,

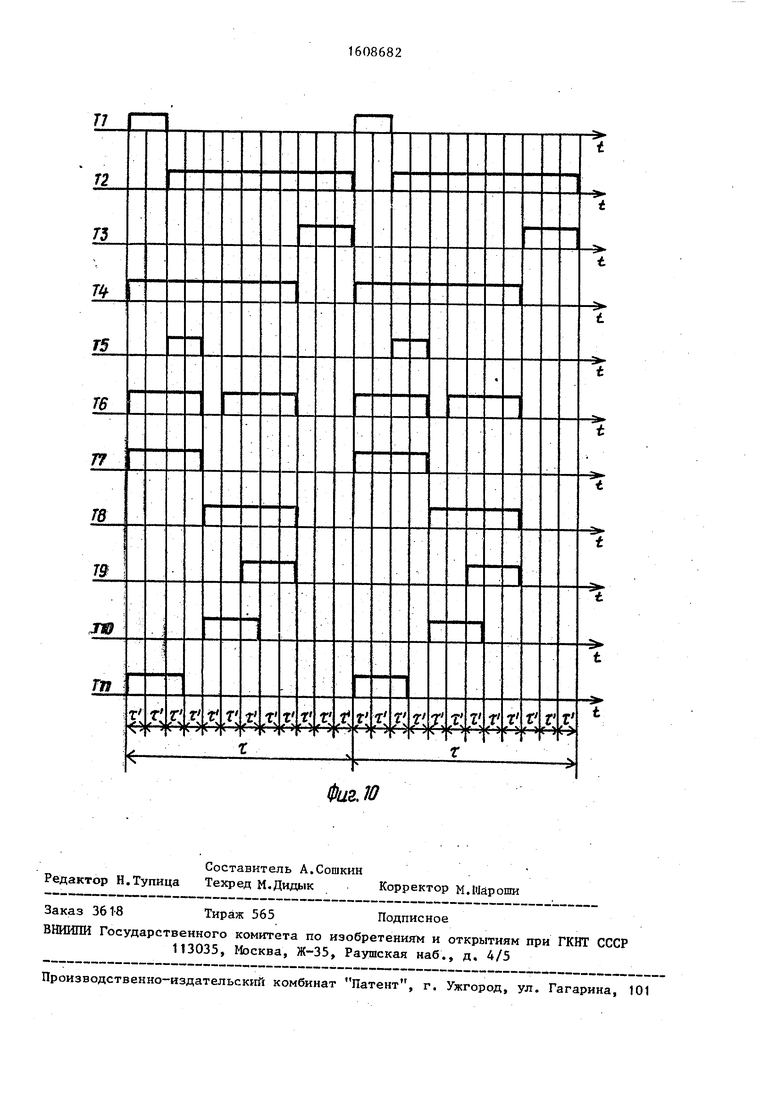

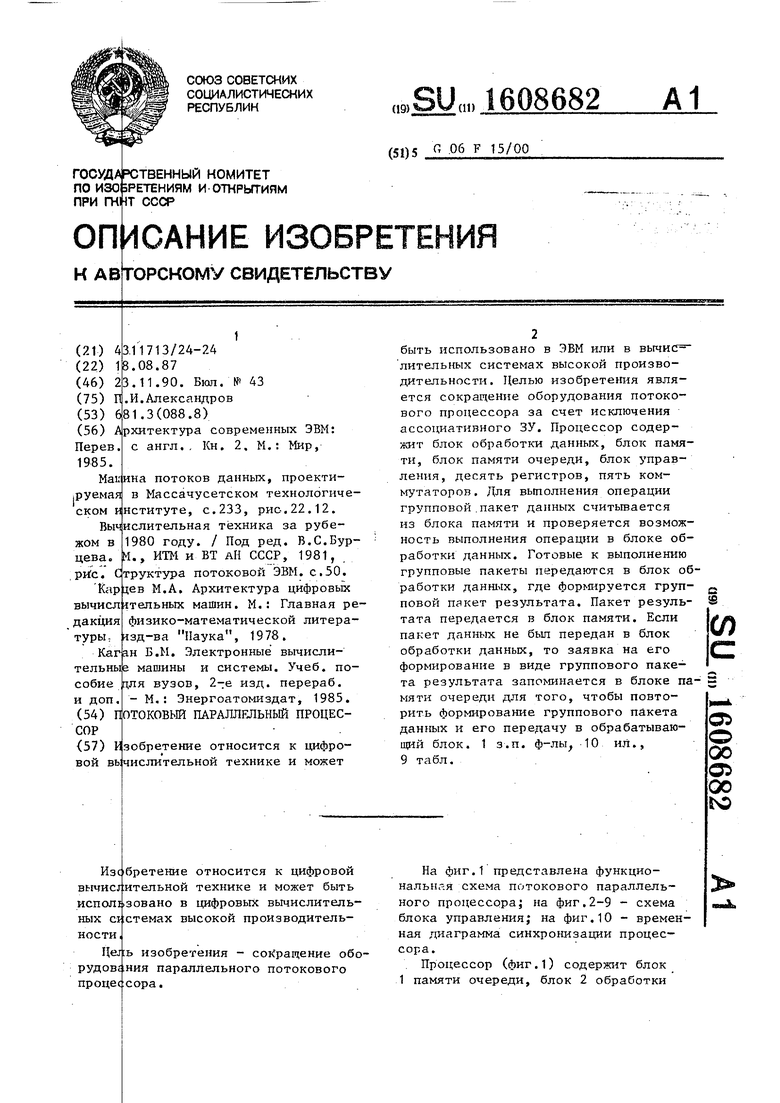

На фиг.1 представлена функциональная схема потокового параллельного процессора; на фиг.2-9 - схема блока управления, на фиг. 10 - временная диаграмма синхронизации процессора.

Процессор (фиг.1) содержит блок 1 памяти очереди, блок 2 обработки

данных, блок 3 памяти, блок 4 управления, первый регистр 5, с первого 6 по третий 8 коммутаторы, с второго 9 по седьмой 14 регистры, блок 15 пакета результата, блок 16 пакета адреса, блок 17 адреса, четвертый 18 и пятый 19 коммутаторы, с восьмого 20 по десятый 22 регистры, блок 23 пакета данных, блок 24 пакета адреса.

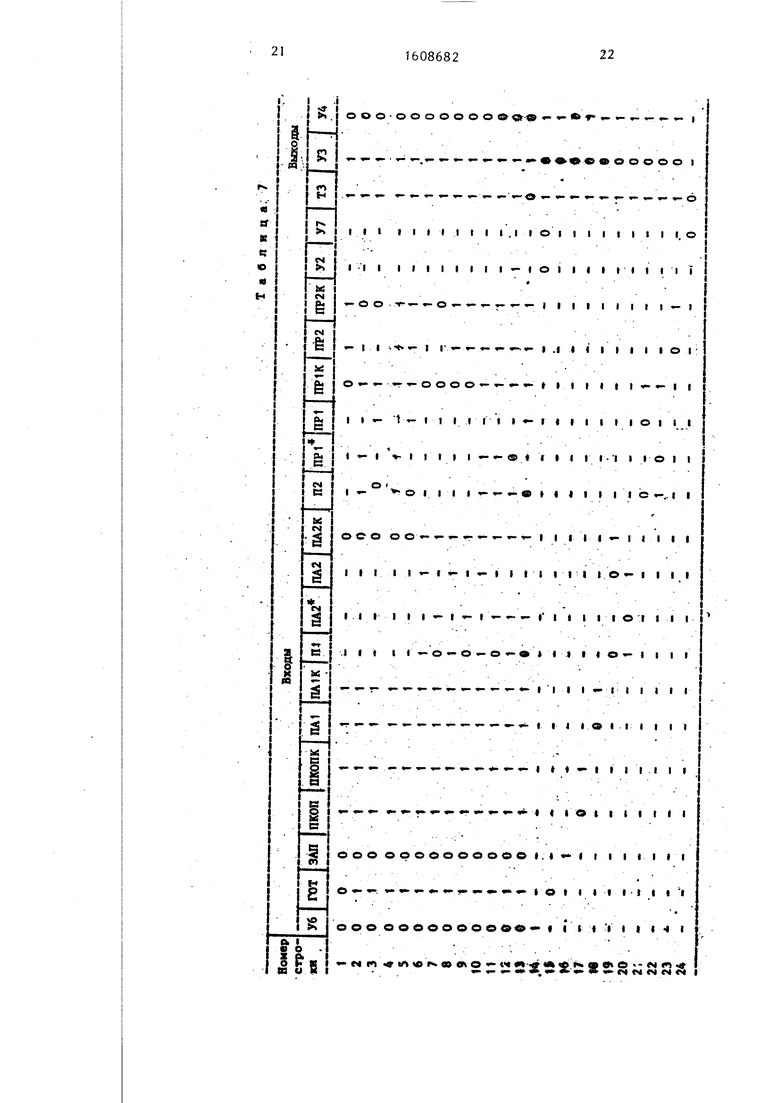

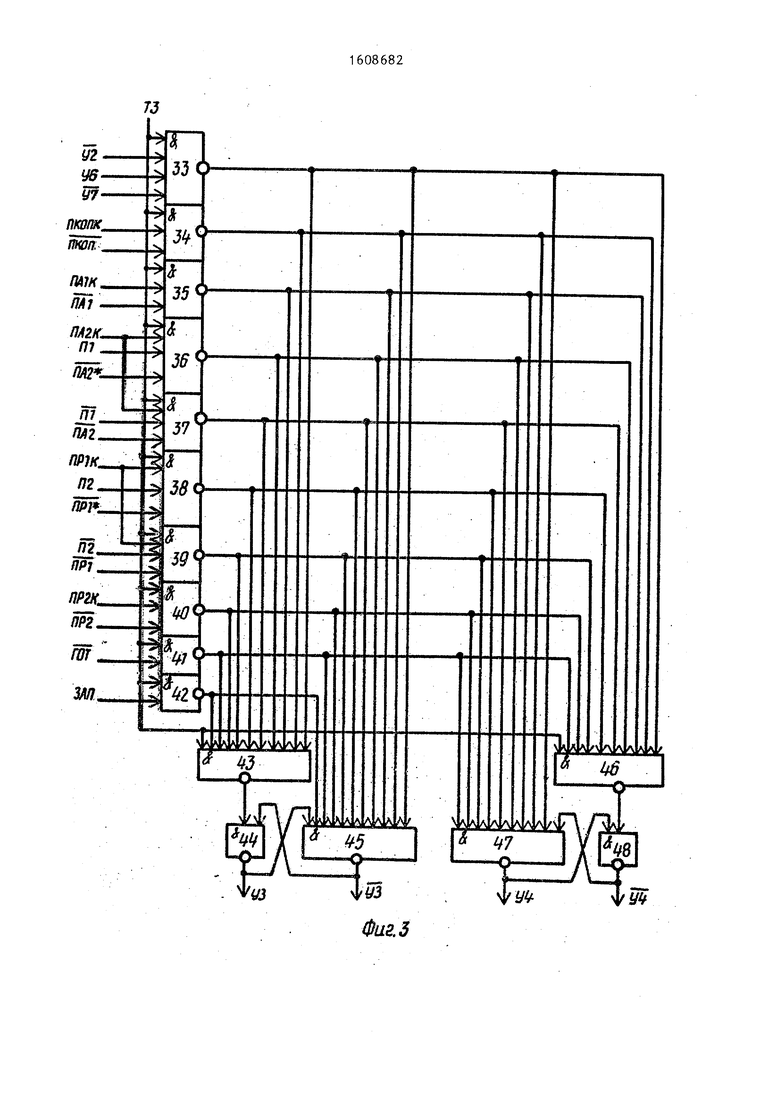

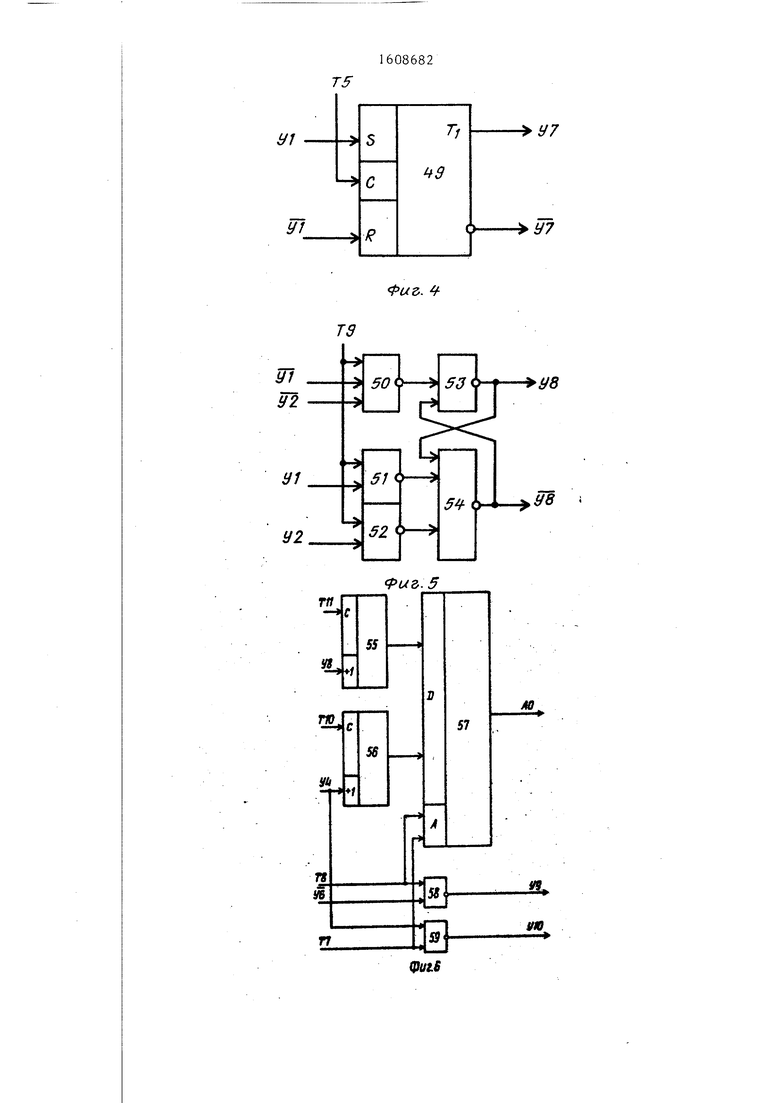

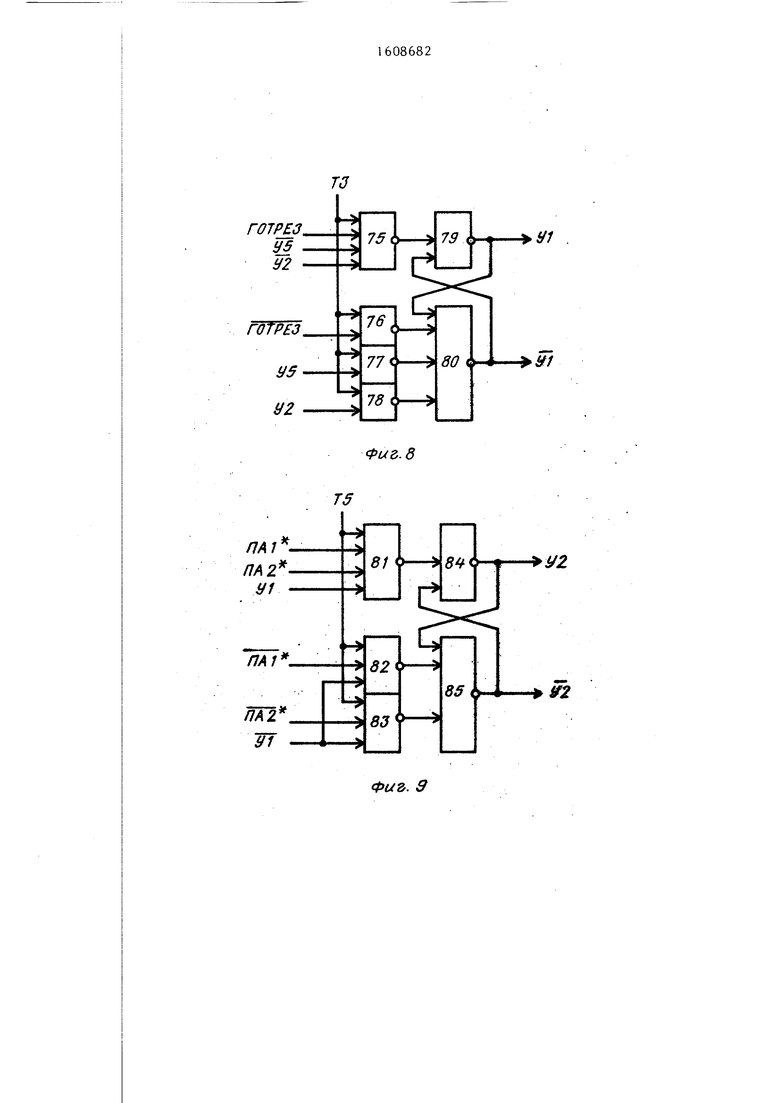

Блок 4 управления (фиг,2) содержит с первого 25 по седьмой 31 узлы управления и шину 32 входов синхронизации, при этом третий узел 27 управления блока управления содержит (фиг.З) с двенадцатого 33 по двадцать седьмой 48 элементы И-НЕ, пятый уэел управления (фиг.4) содержит первый триггер 49, шестой узел управления (фиг.5) содержит элементы И-НЕ с двад цать восьмого 50 по тридцать второй 54, седьмой узел управления (фиг,6) содержит первый 55 и второй 56 К-раЗ- рядные суммирующие счетчики, коммук приему информации (ГОТ 1), в данном (п+1) такте принята в регистры 20-22 новая информация из блока 3 (ЗАП О) или из блока 1, когда очередь пакетов не пуста (У2 У6 У7 О). Если в данном (п+1) такте не было передачи группового пакета данных в блок 2, то запрос на его формирование заносится на конец очереди в форме группового пакета результата в блоке очереди пакетов переносчиков по сигналу У4 1, кроме случая, если в данном такте была запись пакета результата в блок 3 (строка 16, табл.7).

Сигнал У7, сформированный в пятом узле по Т5 в п-м такте, как указано в табл.8, сохраняет в следующем (п+1) такте значение сигнала У1.

Сигнал У8 1, сформированный по Т9 в шестом узле в п-м такте (табл.9), указывает в (п+1) такте,чт в п-м такте работы устройства был

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения микропроцессора с системной шиной | 1990 |

|

SU1837299A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| МОДУЛЬ ДЛЯ ОРГАНИЗАЦИИ ОБМЕНА СООБЩЕНИЯМИ | 2007 |

|

RU2359320C2 |

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

| Потоковый параллельный процессор | 1989 |

|

SU1691845A1 |

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ LDPC-КОДОВ | 2013 |

|

RU2549134C1 |

| Система для сопряжения терминалов с вычислительной машиной | 1987 |

|

SU1529232A1 |

| УСТРОЙСТВО МНОГОКОМПОНЕНТНОЙ ДИАГНОСТИКИ СЕРДЕЧНОЙ ДЕЯТЕЛЬНОСТИ ЧЕЛОВЕКА ПО ПУЛЬСУ | 2005 |

|

RU2308876C2 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в ЭВМ или в вычислительных системах высокой производительности. Целью изобретения является сокращение оборудования потокового процессора. За счет исключения ассоциативного ЗУ. Процессор содержит блок обработки данных, блок памяти, блок памяти очереди, блок управления, десять регистров, пять коммутаторов. Для выполнения операции групповой пакет данных считывается из блока памяти, и проверяется возможность выполнения операции в блоке обработки данных. Готовые к выполнению групповые пакеты передаются в блок обработки данных, где формируется групповой пакет результата. Пакет результата передается в блок памяти. Если пакет данных не был передан в блок обработки данных, то заявка на его формирование в виде группового пакета результата запоминается в блоке памяти очереди, для того чтобы повторить формирование группового пакета данных и его передачу в обрабатывающий блок. 1 з.п. ф-лы, 10 ил., 9 табл.

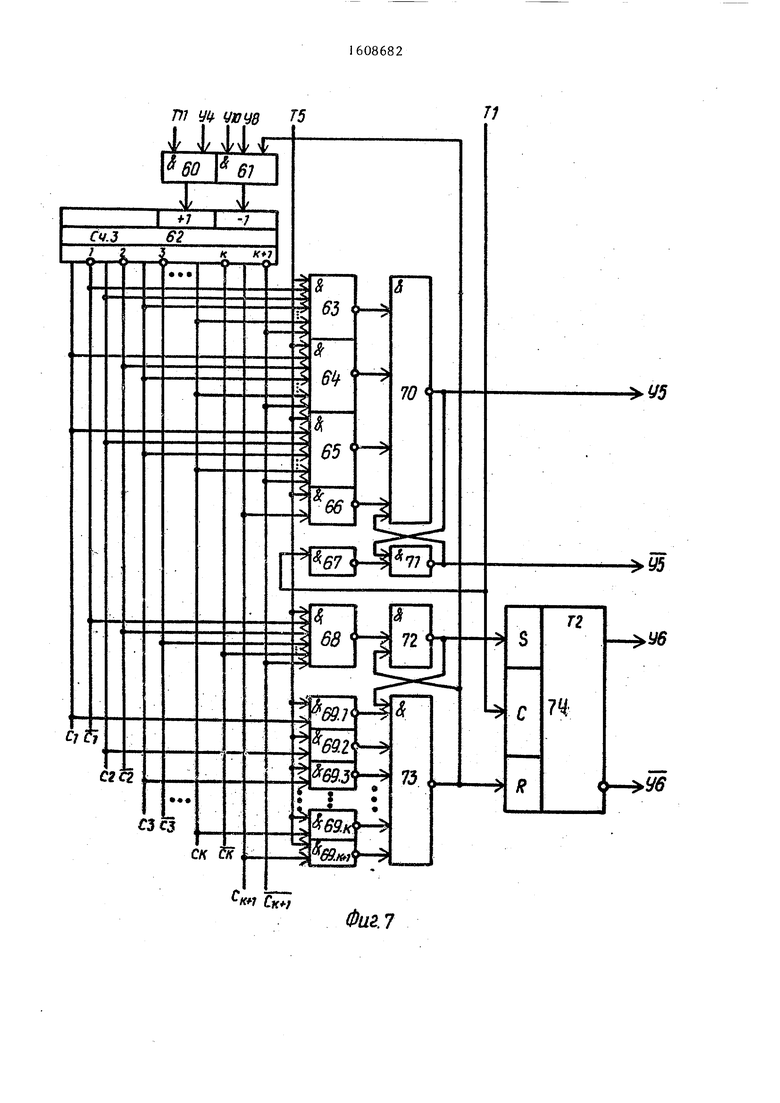

татор 57, тридцать третий 58 и трид- 25 принят групповой пакет результата из

цать четвёртый 59 элементы И-НЕ, чет- вертый узел управления (фиг,7) содержит первый 60 и второй 61 элементы И, реверсивный (К+1)-разрядный третий счетчик 62, с тридцать седьмого jg 63 по сороковой 66 элементы И-НЕ, элемент НЕ 67, сорок первый элемент И-НЕ 68, элементы И-НЕ 69.1-69,К+1, тридцать пятый 70, тридцать шестой

блока 1 очереди пакетов переносчиков.

Обращение к блоку 1 производится два раза за такт работы устройства по тактовому импульсу Т6 для записи и считывания согласно У9 и У10 (управляющие входы записи и считывания блока 1 являются инверсными),

При наличии в блоке 11 очереди

71, сорок второй 72, сорок третий 73 пакетов на выходе коммутатора 57 элементы И-НЕ, второй триггер 74, формируется в каждом такте работы первый узел управления (фиг,8) со- . устройства адрес обращения (АО) к держит с первого 75 по шестой 80 эле- блоку 1 для считывания информации из менты И-НЕ, второй узел управления (фиг.9) содержит с седьмого 81 по дО одиннадцатый 85 элементы И-НЕ,

Рассмотрим некоторые особенности формирования управляющих сигналов,

Управляю1ч 1 е сигналы УЗ и У4 формируются в блоке 3 в п-м такте по так- 45 товому импульсу ТЗ, как указано в табл.8, и в следующем (п+1) такте управляют передачей информации из регистров 20-22 в блок 2 или блок 1.

начала очереди и сопровождается сигналом

У9 У6 ЛТ8,

адрес обращения (АО) к блоку 1 для записи в конце очереди сопровоадает- ся сигналом

У10 У4 М8

У10 У4 Д Т7,

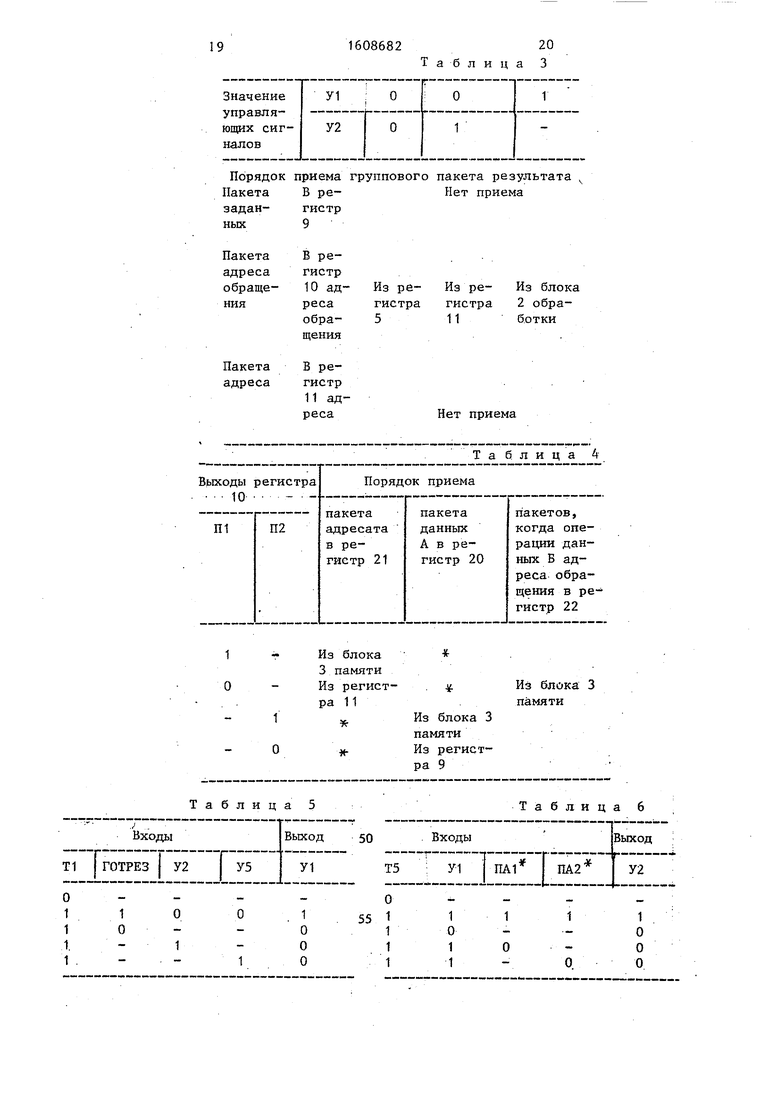

Сигнал УЗ - 1 разрешает передачу группового пакета данных в блок 2, если выполнены условия: состав группового пакета соответствует заданному (строки 1-27, табл.7), при этом учитывается,. с какого направления принимаются пакеты данных А и адреса (строки 2, 3 и 7, 8, табл.7) в соответствии с признаками П1 и П2 из пакета, адреса обращения; блок 2 готов

пакетов на выходе коммутатора 57 формируется в каждом такте работы устройства адрес обращения (АО) к блоку 1 для считывания информации из

начала очереди и сопровождается сигналом

У9 У6 ЛТ8,

адрес обращения (АО) к блоку 1 для записи в конце очереди сопровоадает- ся сигналом

У10 У4 М8

45

50

У10 У4 Д Т7,

На выходах первого счетчика фор- ьируется текурщй адрес первой ячейки, из которой в п-м такте будет считывание по У9 О группового пакета результата и передача его в регистр 5 по Т9, Если в предьщущем (п-1) такте была передача группового пакета данных из регистра 5 в регистры

5-:ri08682

9-11 его обработки в этом такте,

то в I синхрс чика личен

-м такте по Т11, поданному на HH3Hpyroi flift вход первого счет- 5, адрес считывания будет увена единицу по сигналу У8 1

II 1Г

поданному на суммирующий вход первого счетчика. Таким образом, считывание в п-м такте будет производиться из следующей ячейки блока 1, которая первой в очереди.

Если сформированный в (п-1) так повой пакет данных в п-м так- будет передан в блок 2,.то зате ГР:

те не

явка фа его формирование будет занесенс

блоке

выхода

В конец очереди пакетов в 1 по адресу,сформированному на X второго с етчика в п-м такте. Если в п-м такте не было передачи ин(юрмации в блок 1, то в следующем (ii+1) такте запись будет произво- дитьсг в ту не ячейку. Если в п-м такте бьи то в ;

МУ СИ1

счетный вход второго счетчика, по

а передача информации в блок 1, том же п-м такте по управляюще- налу У4 1, поданному на

такто на СИ чика,

единитАу, указывая первую свободную

ячейку тон).

ДЛ5 полив

формщ

II 4 11

пакете У5

ому импульсу Т10, поданному хронизирующий вход второго сч адрес записи увеличится на

блока 1 (конец очереди пакеисключения возможности пере- ия очереди пакетов в блоке 1 уется зшравляющий сигнал У5

запрещающий прием групповых iB результатов из блока 2. При 1 осуществляется прследовапакетедится в бло1 ков, I осуще

ВЫПОЛ

тельн1 й перебор заявок из очереди IB в блоке 1, пока не освобо- достаточное количество ячеек

:е 1 очереди пакетов переносчитакте работы коммутатора може твляться запись в очередь не- :енной заявки из регистров 12 - роме того, в этом же такте ра- I регистры 9-11 может быть при- упповой пакет результата, кото жет быть рассмотрен как еще

мaкcи ryм две заявки. Таким образом, до ПО}вления сигнала У5 1, чтобы .исключить возможность потери ин- форма1;ии, надо иметь не менее трех свобо;;Ных ячеек в блоке 1. Это условие выражается формулой

У5 CMI V(C,,, Л С, Л С,,., Л

...ЛС-г С,) V (С, А ,.,Л...

ЛС,) V (С

kti

С ; АС J, , л

...ЛС уЛ С,).

где.С; - значение j-ro разряда третьего счетчика. Значение сигнала У5 формируется в каждом такте работы коммутатора по Т5 (по Т1 устанавливается значение У5 О).

Значение третьего счетчика указывает количество занятых ячеек блока 1. При передаче информации регистров 12 - 14 в блок 1 (У4 1) на выходе элемента И 60 и по Т11 формируется импульс, подаваемый на суммирующий вход реверсивного третьего счетчика. При приеме информации в регистр 5 из бло--- ка (У8 1) на выходе элемента И 61 и по Т10 формируется импульс, подаваемый на вычитающий вход реверсивного третьего счетчика. Если очередь пакетов в блоке 1 пуста (значение третьего счетчика равно О), то на вы

25

ходе элемента И-ПЕ 73 формируется сигнал О, подаваемый на вход элемента И 61 и запрещающий дальнейшее вычитание из третьего счетчика. Значение сигналов на выходах элементов И-НЕ, задержанные на один такт по

Т1, формируют управляющий-сигнал У6, запрещающем обработку запросов считанных из пустой очереди пакетов в блоке 1 (строка 14, табл.7). Таким образом, сигнал У6, задержанный на

один такт, формируется в соответ- ствии с формулой

0

5

0

5

У6 С,

с„

Y с, V ...VCk V с.,

1 V г

Необходимость задержки формирования сигнала У6 вызвана тем, что обработка заявки, передача сформированного пакета данных в блок 2 производится в следующем (п+1) такте работы устройства.

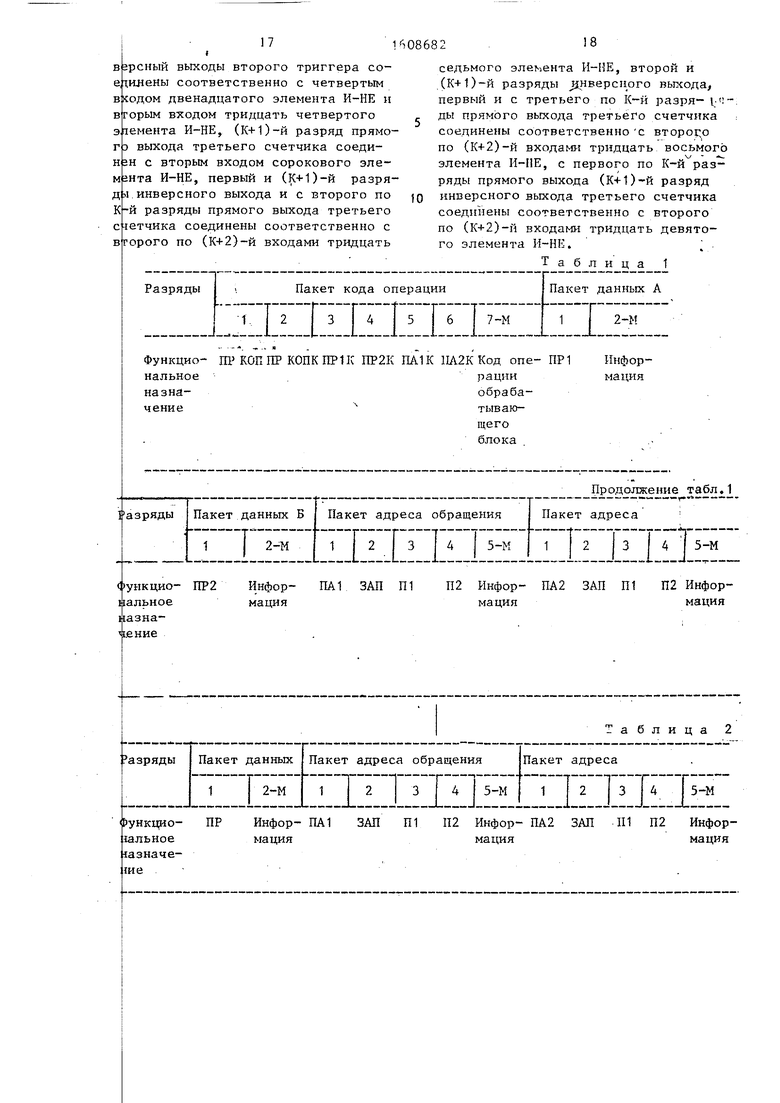

Блок 15 (17) предназначен для приема по Т1 и для хранения М-разряд- ного пакета результата (пакета адреса) ,содержит М одинаковых схем.Функционирование схемы поясняет табл.3.

Блок 16 предназначен для приема Т1 и хранения М-разрядного пакета адреса обращения и содержит М одинаковых схем. Функционирование схемы также поясняет табл.3.

Блок 23 содержит М одинаковых схемо Но тактовому импульсу ТЗ блок принимает и хранит в течение такта значение разряда адреса, как указано в табЛо 4.

Блок 24 содержит М одинаковых схем. Функционирование блока также поясняет табл.4. По тактовому им- ,пульсу ТЗ осуществляется прием и хрнение в течение такта значения разряда пакета- адреса.

Регистр 22 содержит ЗМ одинаковь схем для приема по ТЗ, хранения в тчение такта ЗМ разрядов пакетов кода операции, данных Б и адреса обращения. Функционирование регистра поясняется табл.4.

Регистр 5 содержит ЗМ одинаковых схем, идентичных схемам регистра 10

Обработка и передача информации в процессоре осуществляется в форме М-разрядных пакетов данных, адресов кода операции, которые при обмене между блоками процессора объединяют в групповые пакеты данных и результатов.

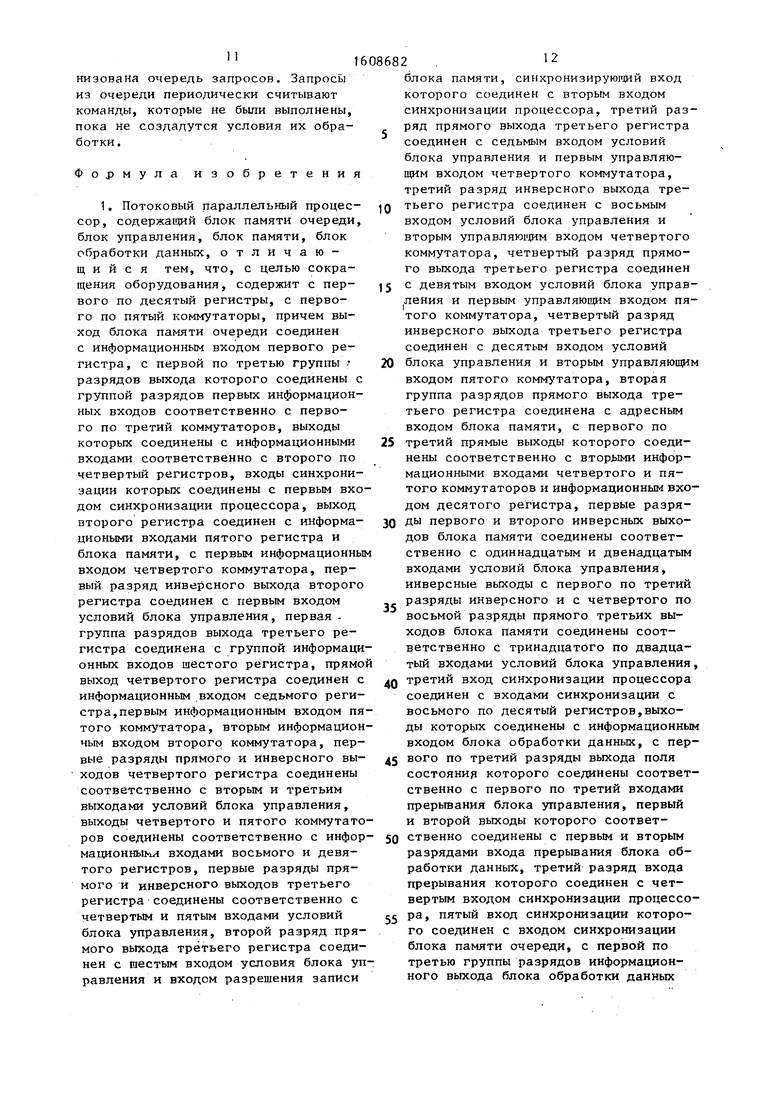

Состав группового пакета данных приведен в табл.1, а группового пакета результатов - в табл.2.В табл.1 и 2 обозначены через ПР УКОП, ПР 1 ПР 2, ПА 1, ПА 2, ПР - признаки наличия информации в соответствующих пакетах, через НПОПК, ПР1К, ПР2К, ПА1К, ПА2К - признаки разрещения участка соответствующих пакетов в операции обрабатывающего блока, указанной в коде операции. Признак ЗАП 1 указывает на необходимость записи пакета результата в блок памяти по данному адресу. Признак П1 О разрешает передачу пакета результата из регистра 9 в регистр 20 Признак П2 разрешает передачу пакета адреса из регистра 11. в регистр

Блок 2 обработки данных вьтолня- ет операции над пакетами данных и адресов согласно коду операции из пакета кода операции. Если блок обработки данных готов принять для обработки очередной групповой пакет данных, то он формирует признак го- т овности ГОТ 1 (иначе ГОТ О Если на выходах блока 2 сформирован результат выполнения операции в виде группового пакета результата, то формируется признак ГОТ РЕЗ 1 (иначе ГОТ РЕЗ О). Примером реализации блока 2 может служить известный процессор.

Блок.очереди пакетов переносчико выполнен в виде буферного запоминающего устройства емкостью ju ЗМ-разря ных слов, где m должно быть боль

0

5

0

5

8682

0

5

0

5

0

5

8

ше максимального количества выполняемых параллельно ветвей программ, чтобы исключить возможность переполнения. Примером реализации может служить известное запоминающее устройство.

Блок 3 памяти предна значен для хранения программ и данных. При этом по адресу запоминающего устройства считывается 5 М-разрядный групповой пакет данных и записывается М-разрядный пакет данных из группового пакета результата. Примером реализации может служить известное запоминающее устройство..

Особенностью функционирования предлагаемого процессора является то,что программа представляется в виде направленного графа, узлами которого являются команды, а дуги указывают порядок выполнения команд. Из каяздо- го узла выходит не более двух дуг,так как в составе группового пакета результата есть два адреса для обращения к памяти (табл.2). По дугам на входы узла в виде групповых пакетов результатов поступают данные, сопровождаемые признаком активизации команды (признак ЗАП из группового пакета результата, табл.2). При ЗАП 1 данные записываются в блок 3 памяти по адресу, указанному в групповом пакете результата (табл.2). Команды и данные хранятся в блоке 3 памяти. При поступлении по одной из ветвей на вход узла признака активации команды (ЗАП О)) эта команда считывается из блока 1 памяти в виде пакета переносчика данных (табл.1) и поступает в блок 2, в котором осуществляется обработка данных, и на выходе блока 2 формируется групповой пакет результата. В случае, если активизированной оказалась команда, для которой еще нет всех данных, либо блок 2 не готов к обработке очередной ко14анды, групповой пакет результата, вызвавший активизацию данной команды, запоминается в виде запроса на считьтание в блоке 1 памяти очереди. Такие запросы хранятся в блоке 1 в виде очереди. Первый запрос из очереди при возникновении паузы в вычислительном процессе активизирует свою команду, которая считывается из блока 3 и передается в блок 2 для выполнения, и запрос вычеркивается из очереди. Если выполнение

команды невозможно, запрос возвращается в конец очереди.

В данном процессоре возможна непосредственная передача данных нз груп- пово: о пакета результата в групповой

паке в бл быст тить грам В

данных, исключая их запись ж 3, что позволяет увеличить )одействие процессора и сокра- объем памяти, занимаемый про10Й.

казздом такте работы процессор

формируется на выходах регистров 9 - 11 по Т1 групповой пакет результата, который по Т9 переписывается в реги- стры 12-14, по Т2 в блок 3 записываются данные с выхода регистра 9 по адре(;у, содержащемуся в регистре 10, ::ибо по ТЗ формируется групповой пакет данных на выходах регист

ров те ПС обра( то зг 14 ш 1 по

nOCTJ

BI

пульс

г J

скогс такт.

0-22, который в следующем так- i Т4 передается в блок 2 для отки, либо если это невозможно ,прос с выходов регистров 12 - |Ступает в конец очереди блока Т6, а первый из очереди запрос пает в регистр 5 по Т9. еменные диаграммы тактовых им- ов представлены на фиг.10, где время задержки одного логиче- элемента, С - длительность работы устройства.

табл.3 и 4 поясняется соответственно порядок формирования групповых, пакетов результата в регистрах 9-11 и данных в регистрах 20-22.

BJ;OK 4, содержащий узлы 25-30, формирующий сигналы У1-У8, и узел уп- равле;ния, формирующий сигналы У9 и У10 i; адрес обращения к блоку 1 (АО) построены исходя из задачи получения максимального быстродействия.

П(рвый узел (фиг.8) 25 управления формирует сигнал У1 по ТЗ в п-м такте и в следующем (п+1) такте управляет первым, вторым и третьим коммутаторами. Сигнал У1 1 пропускает с вьп:одов блока 2 групповой пакет результата, если на выходах блока 2 сформировался групповой пакет ре- (признак ГОТРЕЗ - 1), в блоки 1 есть свободные ячейки (У5 - О) и если в составе принятого ранее группбвого пакета результата не

было

пакета адреса или пакета адреса

обрацения. Иначе формируется У1 О.

r

10

0

5

0

5

0

5

0

5

Работу схемы формирования У1 поясняет табл.5, а работу второго узла 26 .управления (фиг.9) поясняет табл.6.

Сигнал У1, сформированный по Т5 в п-м такте, управляет передачей пакета адреса из регистра 11 в регистр 10 через второй коммутатор 7. Это ito- зволяет для одного группового пакета результата сформировать две заявки на считывание групповых пакетов данных из блока 3, что необходимо для организации разветвлений программ, вьшолняюгщх на потоковом параллельном процессоре. Сигнал У2 1, если в составе принятого из блока 2 группового пакета результата есть два пакета адреса (признаки ПА1 ПА2 1), иначе У2 О (табл.6). При этом сигнал У2 1, сформированный в п-м такте, указывает, что принятый в этом такте из блока 2 групповой пакет результата содержит две заявки на обращение к блоку 3, кото- рые будут обрабатываться в п-м и (п+1) тактах. Поэтому в (п+1) такте в регистры 9-11 прием нового группового пакета результата из блока 2 запрещен, а организовывается передача пакета адреса из регистра 11 в регистр 1. При этом две заявки могут содержать только групповой пакет результата, принятый из блока 2, когда У1 1 (строка 2, табл.6). Групповой пакет, принятый в регистры 9-11 из блока 1, рассматривается как одна заявка.

Потоковый параллельный процессор содержит блоки обработки данных, па- кяти, памяти очереди и управления, регистры и коммутаторы.

Программа для процессора составляется в виде направленного графа, узлаш которого являются команды, а дуги указывают направления передачи данных и управления от каждой команды к следуюгцим за ней командам. Команды и данные в виде пакетов хранятся в блоке памяти и передаются в обрабатываюгчий блок для выполнения операции, результатом которой является пакет результата, имеющий информацию о- том, чуда передать данные и какие следующие команды считывать из блока памяти для выполнения, В случае, если команда не может быть вьтолнена, запрос на ее выполнение в виде пакета результата запоминается в блоке памяти очереди, где орга

ниэована очередь запросов. Запрось из очереди периодически считывают команды, которые не были выполнены, пока не создадутся условия их обработки.

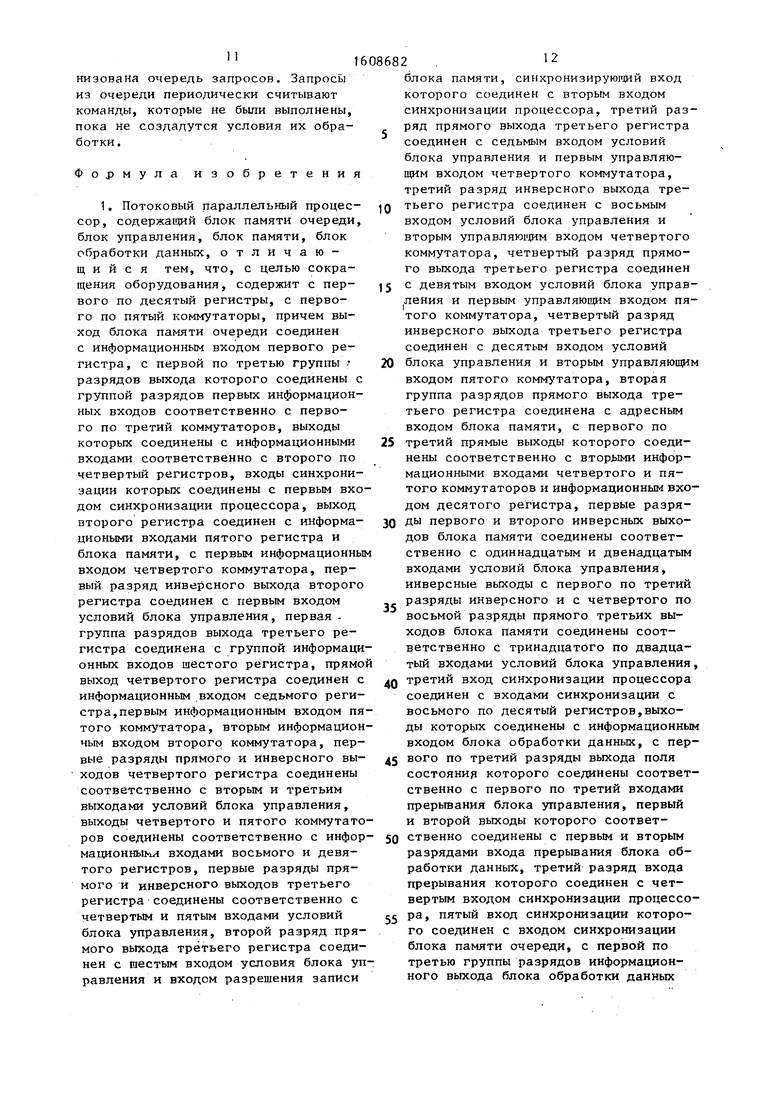

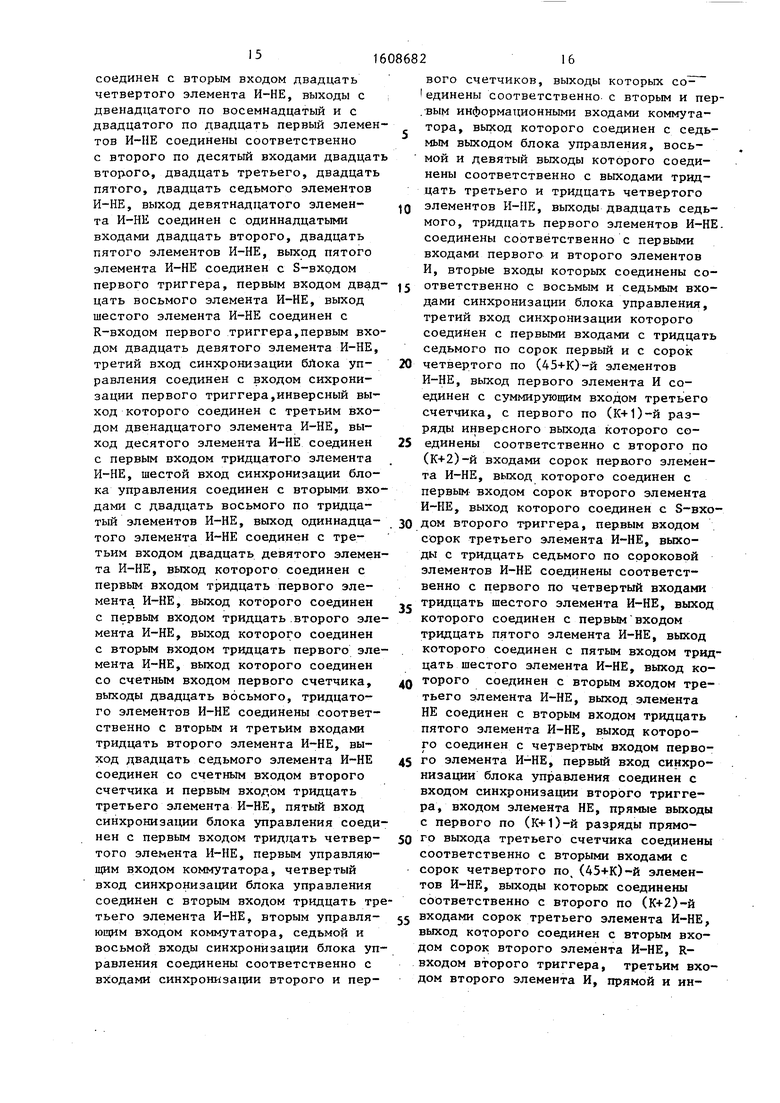

Формула изобретения

1608682

12

5 О 5 0 5

5

0

блока памяти, синхронизируюгиий вход которого соединен с вторым входом синхронизации процессора, третий разряд прямого выхода третьего регистра соединен с седьмым входом условий блока управления и первым управляющим входом четвертого коммутатора, третий разряд инверсного выхода третьего регистра соединен с восьмым входом условий блока управления и вторым управляю1чим входом четвертого коммутатора, четвертый разряд прямого вьгхода третьего регистра соединен с девятым входом условий блока управления и первым управляющим входом пятого коммутатора, четвертый разряд инверсного выхода третьего регистра соединен с десятым входом условий блока управления и вторым управляющим входом пятого коммутатора, вторая группа разрядов прямого выхода третьего регистра соединена с адресным входом блока памяти, с первого по третий прямые выходы которого соединены соответственно с вторыми информационными входами четвертого и пятого коммутаторов и информационным входом десятого регистра, первые разряды первого и второго инверсных выходов блока памяти соединены соответственно с одиннадцатым и двенадцатым входами условий блока управления, инверсные выходы с первого по третий разряды инверсного и с четвертого по восьмой разряды прямого третьих выходов блока памяти соединены соответственно с тринадцатого по двадцатый входами условий блока управления, третий вход синхронизации процессора соединен с входами синхронизации с восьмого по десятый регистров,выходы которых соединены с информационным входом блока обработки данных, с первого по третий разряды выхода поля состояния которого соединены соответственно с первого по третий входами прерьгаания блока управления, первый и второй выходы которого соответственно соединены с первым и вторым разрядами входа прерывания блока обработки данных, третий разряд входа прерывания которого соединен с четвертым входом синхронизации процессора, пятый вход синхронизации которого соединен с входом синхронизации блока памяти очереди, с первой по третью группы разрядов информационного выхода блока обработки данных

соединены соответственно с группой разрядов второго информационного входа первого коммутатора, группой разрядов третьего информационного входа второго коммутатора, группой разрядов второго информационного входа третьего коммутатора, с первого по восьмой входы синхронизации блока управления соединены соответственно с первьм, третьим, шестым, седьмым, восьмью, девятым, десятым и одиннадцатым входами синхронизации процессора, восьмой вход синхронизации которого соединен с входом синхронизации с Еторого по четвертый регистров, вьходы которых соединены с информационным входом блока памяти очереди, девятый вход синхронизации процессора соединен с входом синхронизации первого регистра, с третьего по пять и выходы блока управления со- единень соответственно с первого по третий управяющими входами с первого по третий коммутаторов, с шестого по девятый выходы блока управления соединены соответственно с четвертым управляющим входом второго коммутатора, входом адреса блока памяти опереди, первым, вторым входами управления записью-чтением блока памяти огередн,

0

5

0

5

вход синхронизации блока управления ; соединен с вторыми входами с седьмо го по девятый элементов И-НЕ, с второго по пятый входы условий блока управления соединены соответственно с третьими входами седьмого и восьмого элементов И-ПЕ, четвертыми входами седьмого и третьим входом десятого элементов И-НЕ, выход седьмого элемента И-НЕ соединен с первым входом десятого элемента И-НЕ, выход кото- рого соединен с первыь входом одиннадцатого элемента И-НЕ и вторым вхо- дом четвертого элемента И-НЕ, выходы восьмого и девятого элементов И-НЕ соединены соответственно с вторым ; и третьим входами одиннадцатого эле-i мента И-НЕ, выход.которого соединен с вторым входом десятого и первым входом двенадцатого элементов И-НЕ, первые входы с тринадцатого по девят- надцатьп элементов И-НЕ соединены соответственно с шестнадцатого по двадцатый входами условий, первым входом лрерьшания и шестьй входом уровней блока управления, восемнадцатый и девятнадцатый входы условий которого соединены соответственно с вторыми входами двадцатого и двадцать первого элементов И-НЕ, вторые входы с двенадцатого по девятнадцатый, третья входы двадцатого и двадцать первого элементов И-НЕ, первые входы двадцать второго и двадцать третьего элементов И-НЕ соединены с вторым входом синхронизации блока управления, первый и второй входы условий которого соединены соответственно с третьими входами шестнадцатого и пятнадцатого элементов И-НЕ, с седьмого по один- надцатьй входы условий блока управления соединены соответственно с четвертыми входами пятнадцатого, двадцатого, шестнадцатого, двадцать первого элементов И-НЕ, выход двадцать второго элемента И-НЕ соединен с первым входом двадцать четвертого элемента И-НЕ, выход которого соединен с вторым выходом блока з равления ц первым входом двадцать пятого элемента И-НЕ, выход двадцать третьего элемента И-НЕ соединен с первым входом двадцать шестого элемента И-НЕ, выход которого соединен с первым вхо- дом двадцать седьмого элемента И-НЕ, выход которого соединен с вторым входом двадцать шестого элемента И-НЕ, . выход двадцать пятого элемента И-НЕ

0

5

0

5

0

51

соединен с вторым входом двадцать четвертого элемента И-НЕ, выходы с двенадцатого по восемнадцатый и с двадцатого по двадцать первый элементов И-НЕ соединены соответственно с второго по десятый входами двадцат второго, двадцать третьего, двадцать пятого, двадцать седьмого элементов И-НЕ, выход девятнадцатого элемен- та И-НЕ соединен с одиннадцатыми входами двадцать второго, двадцать пятого элементов И-НЕ, выход пятого элемента И-НЕ соединен с 8-входом первого триггера, первым входом двадцать восьмого элемента И-НЕ, выход шестого элемента И-НЕ соединен с R-входом первого триггера,первым входом двадцать девятого элемента И-НЕ, третий вход синхронизации бЛока управления соединен с входом сихрони- зации первого триггера,инверсный выход которого соединен с третьим входом двенадцатого элемента И-НЕ, выход десятого элемента И-НЕ соединен с первым входом тридцатого элемента И-НЕ, шестой вход синхронизации блока управления соединен с вторыми входами с двадцать восьмого по тридцатый элементов И-НЕ, выход одиннадцатого элемента И-НЕ соединен с третьим входом двадцать девятого элемента И-НЕ, выход которого соединен с первым входом тридцать первого элемента. И-НЕ, выход которого соединен с первым входом тридцать .второго элемента И-НЕ, выход которого соединен с вторым входом тридцать первого элемента И-НЕ, выход которого соединен со счетным входом первого счетчика, выходы двадцать восьмого, тридцатого элементов И-НЕ соединены соответственно с вторым и третьим входами тридцать второго элемента И-НЕ, выход двадцать седьмого элемента И-НЕ соединен со счетным входом второго счетчика и первым входом тридцать третьего элемента И-НЕ, пятый вход синхронизации блока управления соединен с первым входом тридцать четвертого элемента И-НЕ, первым управляющим входом коммутатора, четвертый вход синхронизации блока управления соединен с вторым входом тридцать тртьего элемента И-НЕ, вторым управляющим входом коммутатора, седьмой и восьмой входы синхронизации блока управления соединены соответственно с входами синхронизатщи второго и пер

16

вого счетчиков, выходы которых со единены соответственно с вторым и первым информационньпчи входами коммутатора, выход которого соединен с седьмым выходом блока управления, восьмой и девятый вькоды которого соединены соответственно с выходами тридцать третьего и тридцать четвертого элементов И-НЕ, выходы двадцать седь

соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с восьмым и седьмым входами синхронизации блока управления, третий вход синхронизации которого соединен с первыми входами с тридцать седьмого по сорок первый и с сорок четвертого по ()-й элементов И-НЕ, выход первого элемента И соединен с суммирующим входом третьего счетчика, с первого по (К+1)-й разряды инверсного которого соединены соответственно с второго по (К+2)-й входами сорок первого элемента И-НЕ, выход которого соединен с первым входом сорок второго элемента И-НЕ, выход которого соединен с S-вхо- дом второго триггера, первым входом сорок третьего элемента И-НЕ, выходы с тридцать седьмого по сороковой элементов И-НЕ соединены соответственно с первого по четвертый входами

тридцать шестого элемента И-НЕ, выход которого соединен с первым входом тридцать пятого элемента И-НЕ, выход которого соединен с пятым входом тридцать шестого элемента И-НЕ, выход которого соединен с вторым входом третьего элемента И-НЕ, выход элемента НЕ соединен с вторым входом тридцать пятого элемента И-НЕ, выход которого соединен с четвертым входом первого элемента И-НЕ, первый вход синхронизации блока управления соединен с входом синхронизации второго триггера, входом элемента НЕ, прямые выходы с первого по (К+1)-й разряды прямого выхода третьего счетчика соединены соответственно с вторыми входами с сорок четвертого по, (45+К)-й элементов И-НЕ, выходы которых соединены соответственно с второго по (К+2)-й

входами сорок третьего элемента И-НЕ, ыход которого соединен с вторым вхоом сорок второго элемента И-НЕ, R- ходом второго триггера, третьим вхоом второго элемента И, прямой и инвзрсный выходы второго триггера соединены соответственно с четвертым в кодом двенадцатого элемента И-НЕ и вторым входом тридцать четвертого 1емента И-НЕ, (К+1)-й разряд прямо- э выхода третьего счетчика соеди- 2Н с вторым входом сорокового элемента И-НЕ, первый и (К+1)-й разряда инверсного выхода и с второго по К-и разряды прямого выхода третьего летчика соединены соответственно с второго по (К+2)-й входами тридцать

назна-обрабачение тывающегоблока

(; ункцио- ПР2 Инфор- IIA1 ЗАП П1 П2 Инфор- ПА2 ЗАП П1 П2 Инфор- иальноемациямациямация

назна-,

чение.

Функциональное1азначе- ше

ПР Инфор- ПА1 ЗАП П1 П2 Инфор- I1A2 ЗАП III П2 Информациямациямация

седьмого элемента И-1Ш, второй и (К+1)-й разряды jjHBepcH oro выхода, первый и с третьего по разря- i. ;- ды прямого выхода третьего счетчика соединены соответственно с второг,о по (К+2)-й входами тридцать восьмого элемента И-НЕ, с первого по К-й разряды прямого выхода (К+1)-й разряд инверсного выхода третьего счетчика соединены соответственно с второго по (К+2)-й входами тридцать девятого элемента И-НЕ. .

Таблица 1

Таблица 2

Порядок приема группового пакета результата Пакета В ре-Нет приема

задан- гистр ных 9

В регистр11 адреса

Таблица 5

1 О

О

1

1 О

о

о

Нет приема

Таблица 4

Таблица 6

о

5 1

1

1

1

1 О

1

1

1 о

о

1 о о о

У

У7

У2 .у

УЗ У9 УЮ

У1

У1

я if

TI

Фиг.

f/8

.5

JS

т yij. 5

jLxl vl

w

Фиг. 7

У5

У6

Фиг. 9

| Архитектура современных ЭВМ: Перев | |||

| с англ. | |||

| Кн | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| М.: Мир, 1985 | |||

| Мафна потоков данных, проекти- ,руемая в Массачусетском технологическом институте, с | |||

| Крутильный аппарат | 1922 |

|

SU233A1 |

| Машина для добывания торфа и т.п. | 1922 |

|

SU22A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| / Под ред | |||

| В.С.Бурцева | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Структура потоковой ЭВМ | |||

| Устройство для выпрямления многофазного тока | 1923 |

|

SU50A1 |

| Кар дев М.А | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| М.: Главная редакция туры: физико-математической литера- зд-ва Паука, 1978 | |||

| Каган Б.М | |||

| Электронные вычислительны собие и доп, | |||

Авторы

Даты

1990-11-23—Публикация

1987-08-18—Подача