/V

СЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с абонентами | 1987 |

|

SU1575191A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 2013 |

|

RU2547216C1 |

| Устройство для сопряжения периферийных устройств с ЭВМ | 1987 |

|

SU1425699A1 |

| СИСТЕМА ИНДИКАЦИИ ЛЕТАТЕЛЬНОГО АППАРАТА | 2001 |

|

RU2206872C2 |

| НАВИГАЦИОННЫЙ КОМПЛЕКС ЛЕТАТЕЛЬНОГО АППАРАТА | 2000 |

|

RU2170409C1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1478222A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Управляющая вычислительная система | 1986 |

|

SU1451711A1 |

| Устройство для сопряжения процессоров | 1990 |

|

SU1807495A1 |

Изобретение относится к вычислительной технике. Целью изобретения является расширение области применения путем обеспечения работы устройства в качестве внешнего энергонезависимого запоминающего устройства, энергонезависимого оперативного запоминающего устройства или энергонезависимого постоянного запоминающего устройства. Устройство содержит блок памяти 1, блок управления 2, дешифратор номера страницы 4, блок сопряжения 6, подключенный к магистрали ЭВМ 7, блок коммутации 8, элементы односторонней проводимости 9 - 11, резервный источник питания 12. Изобретение позволяет уменьшить номенклатуру устройств, подключаемых к ЭВМ, а также переставлять платы запоминающих устройств из одного конструктивного места в другое без потери информации. 2 ил., 2 табл.

О5 О 00

4

05

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам.

Целью изобретения является расширение области применения устройства за счет обеспечения работы устройства в качестве внешнего энергонезависимого запоминающего устройства, энергонезависимого оперативного запоминающего устройства и энергонезависимого постоянного запоминающего устройства.

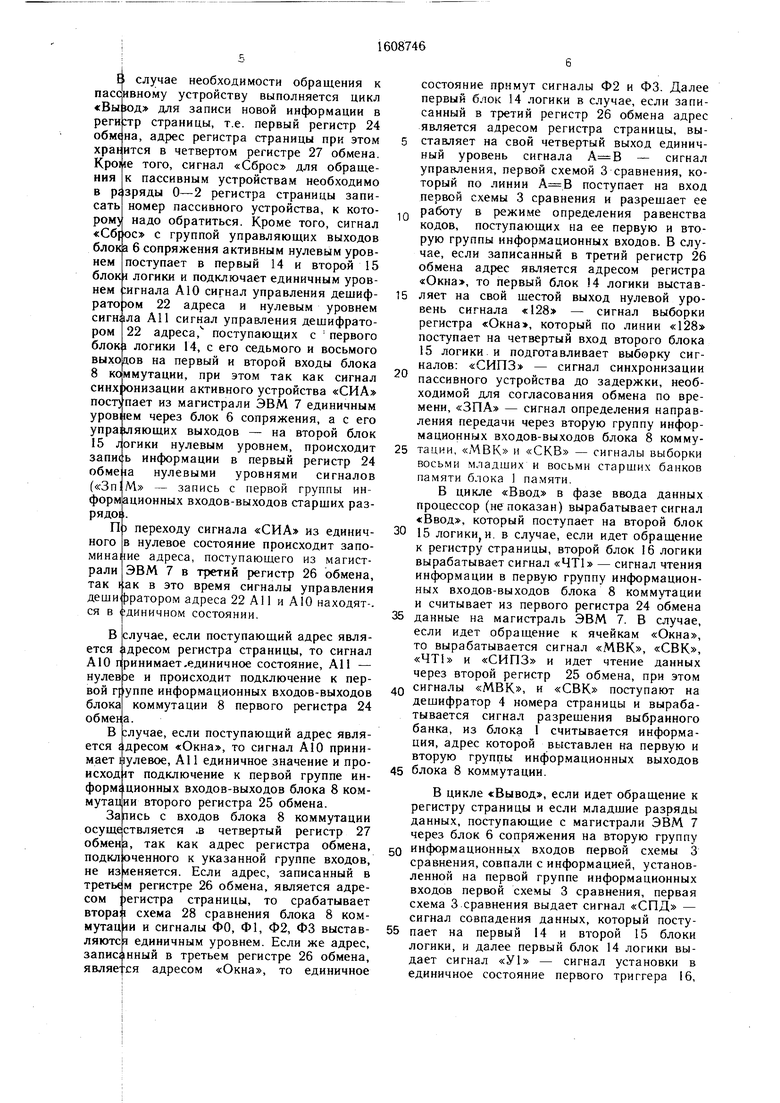

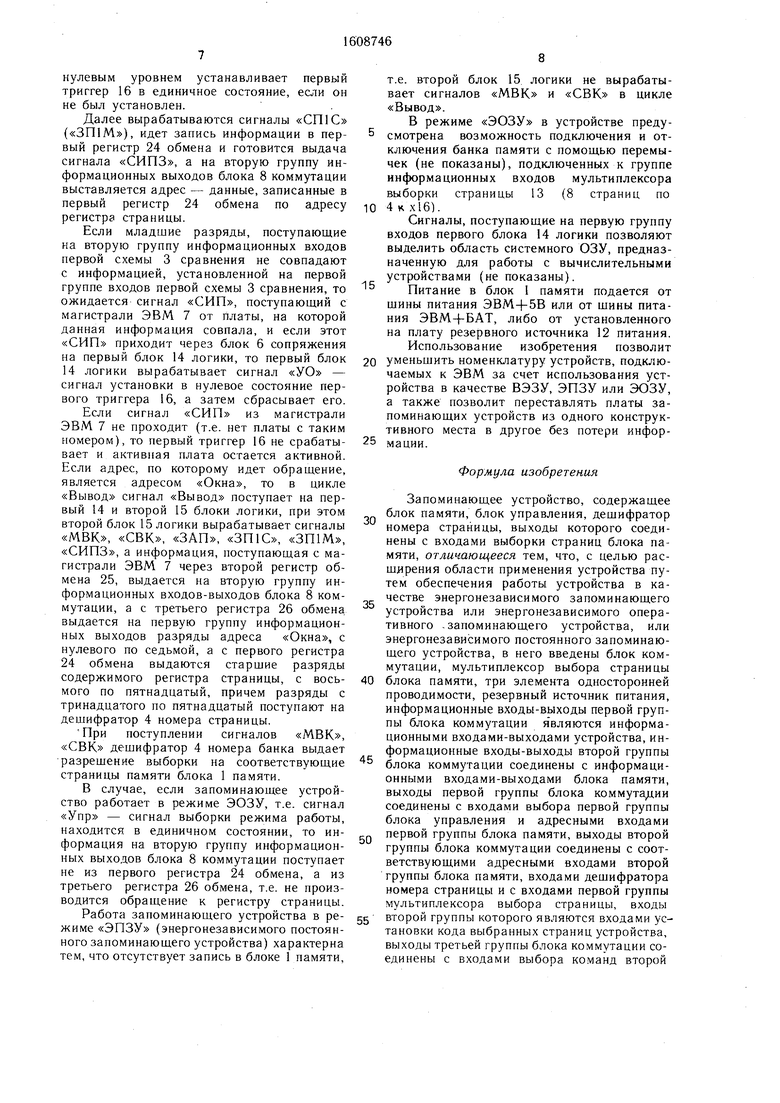

На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - структурная схема блока коммутации.

Запоминающее устройство содержит блок 1 памяти, блок 2 управления, первую схему 3 сравнения, дешифратор 4 номера страницы, формирователь 5 и блок 6 сопряжения, группа информационных входов которого подсоединена к магистрали ЭВМ 7, блок 8 коммутации, первый 9, второй 10 и третий 11 элементы односторонней проводимости, резервный источник 12 питания, мультиплексор 13 выборки страницы.

Блок 2 управления содержит первый 14 и второй 15 блоки логики, первый 16 и второй 17 триггеры, первую схему 3 сравнения, формирователь 5 и элемент 18 задержки.

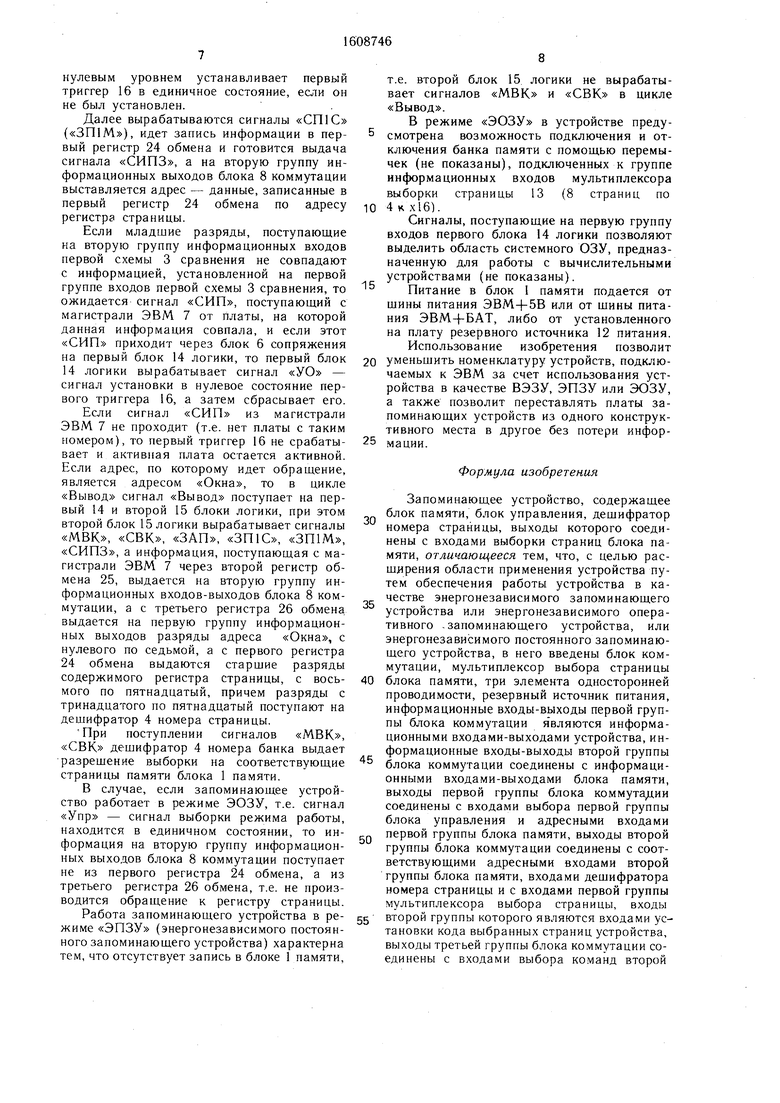

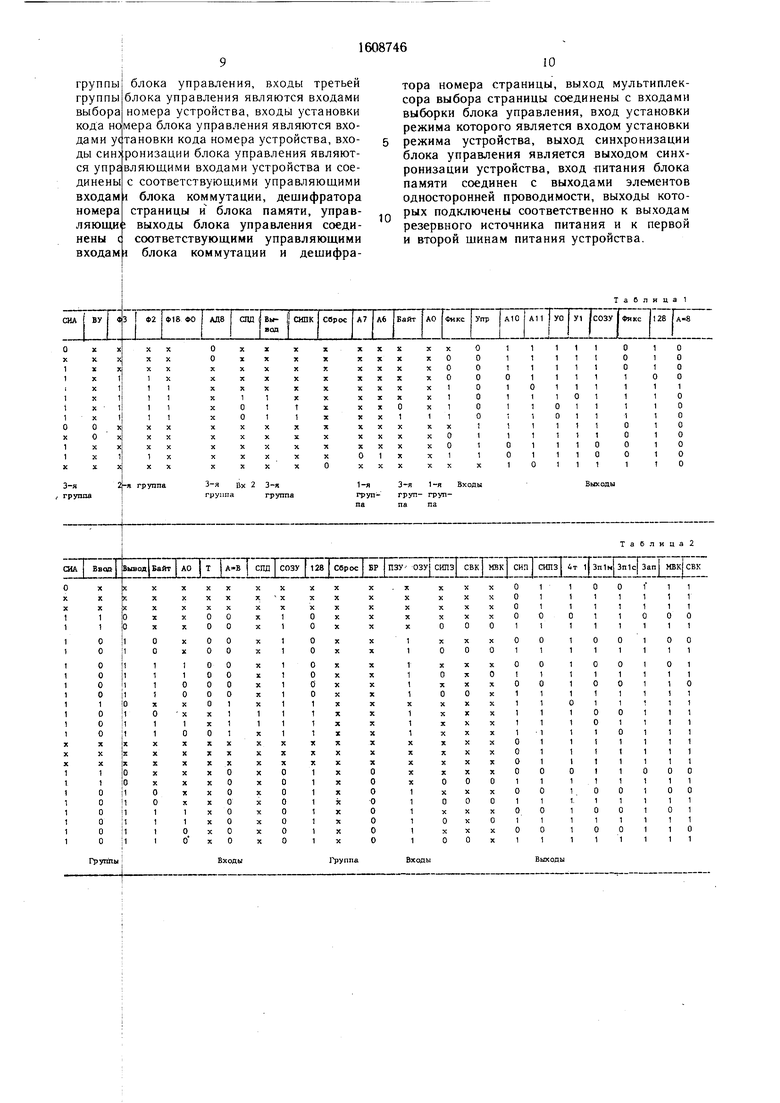

Алгоритм функционирования первого 14 и второго 15 блоков логики приведен в табл. 1 и 2 соответственно, где X - любое значение сигнала.

Элемент 18 задержки содержит четвертый элемент 19 односторонней проводимости, накопительный элемент 20 и ограничительный элемент 21.

Блок 8 коммутации содержит дешиф-. ратор 22 адреса, мультиплексор 23 каналов, первый 24, второй 25, третий 26 и четвертый 27 регистры обмена, вторую схему 28 сравнения и блок 29 приема-выдачи данных, входами-выходами которого являются двунаправленные каналы 1-4 блока 8 коммутации.

Блок 8 коммутации может быть выполнен на базе микросхемы К1802ВВ1. Первый 14 и второй 15 блоки логики могут быть выполнены на базе микросхем К155РЕЗ. Блок памяти выполнен на базе микросхем памяти статического типа К 537РУЗА. Магистраль ЭВМ 7 представляет собой унифицированную систему связей и сигналов между процессором (не показан) и подключенными к нему устройствами.

В первом режиме работы запоминающее устройство функционирует как внешнее энергонезависимое запоминающее устройство (ВЭЗУ) с информационной емкостью, определяемой количеством устройств (плат), подключенных к магистрали ЭВМ 7. На одной плате может быть размешен объем памяти до 64 кбайт, т.е. при установке восьми устройств максимальная информационная емкость составляет 512 кбайт.

Во втором режиме работы устройство функционирует, как энергонезависимое оперативное запоминающее устройство (ЭОЗУ) с максимальной информационной емкостью 56 Кбайт. При работе в режиме ВЭЗУ устройством реализован метод базового регистра и «окна. Одновременно . на магистрали ЭВМ 7 может находиться число устройств ВЭЗУ, определяемое числом

Q информационных разрядов, отведенных для определения номера устройства (платы), каждое из которых имеет один и тот же адрес базового регистра и «окна размером 128 16-разрядных ячеек, расположенных в адресном пространстве в области внешних

5 устройств. Адрес базового регистра и «окна задаются перемычками на плате (не показаны).

Адрес ячейки ВЭЗУ формируется из но0 мера платы (младшие разряды содержимого базового регистра) восьми старших разрядов содержимого базового регистра и восьми младщих разрядов адреса ячейки «окна. Номер платы задается перемычками на плате (не показаны). Таким образом,

5 сформированный адрес ячейки ВЭЗУ содержит 16+Т разрядов, где Т - число разрядов, отведенное для передачи кода номера платы, что позволяет при и установке восьми плат иметь объем ВЭЗУ 512 кбайт. При включении питания блок питания (не показано) выставляет сигнал «КПост - постоянное напряжение в норме единичным уровнем, который поступает с магистрали ЭВМ 7 .в блок 6 сопряжения и далее по линии «Пост также единичным уровнем на вход формирователя 5 и на управляющий вход дещифратора 4 номера банка и подготавливает его работу. Затем процессор выставляет на магистраль ЭВМ 7 сигнал «Сброс - сигнал начальной установки активным нулевым уровнем, который через

0 блок 6 сопряжения по линии «Сброс поступает на динамический вход первого триггера 16 и по переходу сигнала «Сброс обратно из нулевого уровня в единичный, в зависимости от установленного

g уровня сигнала на информационном входе первого триггера 16, который устанавливается при помощи перемычки на плате (не показан), взводит или сбрасывает первый триггер 16. При этом, если первый триггер 16 взведен, т.е. установлен в единич0 ное состояние, указанное устройство будет активным на магистрали ЭВМ 7, что свидетельствует о том, что из N устройств, где N - число запоминающих устройств (плат), подключенных к магистрали ЭВМ 7, при обращении в цикле «Ввод ответит

5 всегда активное устройство (плата) пассивно, в цикле «Ввод оно не ответит. При этом на магистрали активным может быть только одно устройство.

5

Ь

случае необходимости обращения к naccpiBHOMy устройству выполняется цикл I для записи новой информации в реги):тр страницы, т.е. первый регистр 24 адрес регистра страницы при этом в четвертом регистре 27 обмена того, сигнал «Сброс для обраще- к пассивным устройствам необходимо 13ряды 0-2 регистра страницы запи- номер пассивного устройства, к кото- надо обратиться. Кроме того, сигнал «C6i|oc с группой управляющих выходов 6 сопряжения активным нулевым уров- поступает в первый 14 и второй 15 1 логики и подключает единичным уров- :игнала А10 сигнал управления дешиф- 22 адреса и нулевым уровнем All сигнал управления дешифрато- 22 адреса, поступающих с первого логики 14, с его седьмого и восьмого выходов на первый и второй входы блока коммутации, при этом так как сигнал синхронизации активного устройства «СИЛ пает из магистрали ЭВМ 7 единичным уровнем через блок 6 сопряжения, а с его упра:(ляющих выходов - на второй блок логики нулевым уровнем, происходит ь информации в первый регистр 24 ia нулевыми уровнями сигналов М - запись с первой группы ин- входов-выходов старщих раз«Выюдреги :т обмана хран Kpoi ния в рг сать

POMJ

«C6f

блок|а

нем

блок|н

нем

ратоЬом

сигнала

ром

блок

в

8

с

ПОСТ}

формационных

15

запш

обмена

юрл

рЯДО

Г кого

рали

так

деши ся в

П)

переходу сигнала «СИА из единич- в нулевое состояние происходит запо1ие адреса, поступающего из магист- ЭВМ 7 в третий регистр 26 обмена, 1.ак в это время сигналы управления {оратором адреса 22 А11 и А10 находят-, дикичном состоянии.

В

ется А10

:лучае, если поступающий адрес явля- лдресом регистра страницы, то сигнал принимает .единичное состояние, АИ - нулевэе и происходит подключение к первой rf уппе информационных входов-выходов блока коммутации 8 первого регистра 24 обмена.

В ;лучае, если поступающий адрес является г дресом «Окна, то сигнал А10 принимает пулевое, АИ единичное значение и про- ИСХОД1Т подключение к первой группе информационных входов-выходов блока 8 ком- мутац|ии второго регистра 25 обмена.

:ь с входов блока 8 коммутации ;ляется .в четвертый регистр 27 так как адрес регистра обмена, ;нного к указанной группе входов, изменяется. Если адрес, записанный в треты м регистре 26 обмена, является адре- )егистра страницы, то срабатывает втора; 1 схема 28 сравнения блока 8 ком- мутащи и сигналы ФО, Ф1, Ф2, ФЗ выставляются единичным уровнем. Если же адрес, записанный в третьем регистре 26 обмена, ся адресом «Окна, то единичное

состояние примут сигналы Ф2 и ФЗ. Далее первый блок 14 логики в случае, если записанный в третий регистр 26 обмена адрес является адресом регистра страницы, вы- 5 ставляет на свой четвертый выход единичный уровень сигнала - сигнал управления, первой схемой 3 сравнения, который по линии поступает на вход первой схемы 3 сравнения и разрещает ее Q работу в режиме определения равенства кодов, поступающих на ее первую и вторую группы информационных входов. В случае, если записанный в третий регистр 26 обмена адрес является адресом регистра «Окна, то первый блок 4 логики выстав- 15 ляет на свой щестой выход нулевой уровень сигнала «128 - сигнал выборки регистра «Окна, который по линии «128 поступает на четвертый вход второго блока 15 логики и подготавливает выборку сиг- налов: «СИПЗ - сигнал синхронизации пассивн ого устройства до задержки, необходимой для согласования обмена по времени, «ЗПА - сигнал определения направления передачи через вторую группу информационных входов-выходов блока 8 комму- 25 тации, «МВК и «СКВ - сигналы выборки восьми младших и восьми старших банков памяти блока 1 памяти.

В цикле «Ввод в фазе ввода данных процессор (не показан) вырабатывает сигнал «Ввод, который поступает на второй блок 30 15 логики,и, в случае, если идет обращение к регистру страницы, второй блок 16 логики вырабатывает сигнал «ЧТ1 - сигнал чтения информации в первую группу информационных входов-выходов блока 8 коммутации и считывает из первого регистра 24 обмена 5 данные на магистраль ЭВМ 7. В случае, если идет обращение к ячейкам «Окна, то вырабатывается сигнал «МВК, «СВК, «ЧТЬ и «СИПЗ и идет чтение данных через второй регистр 25 обмена, при этом 0 сигналы «МВК, и «СВК поступают на дещифратор 4 номера страницы и вырабатывается сигнал разрешения выбранного банка, из блока 1 считывается информация, адрес которой выставлен первую и вторую группы информационных выходов 5 блока 8 коммутации.

В цикле «Вывод, если идет обращение к регистру страницы и если младщие разряды данных, поступающие с магистрали ЭВМ 7 через блок 6 сопряжения на вторую группу

0 информационных входов первой схемы 3 сравнения, совпали с информацией, установленной на первой группе информационных входов первой схемы 3 сравнения, первая схема 3 сравнения выдает сигнал «СПД - сигнал совпадения данных, который посту5 пает на первый 14 и второй 15 блоки логики, и далее первый блок 14 логики выдает сигнал «УЬ - сигнал установки в единичное состояние первого триггера 16,

нулевым уровнем устанавливает первый триггер 16 в единичное состояние, если он не был установлен.

Далее вырабатываются сигналы «СП 1C («ЗП1М), идет запись информации в первый регистр 24 обмена и готовится выдача сигнала «СИПЗ, а на вторую группу информационных выходов блока 8 коммутации выставляется адрес - данные, записанные в первый регистр 24 обмена по адресу регистра страницы.

Если младшие разряды, поступающие на вторую группу информационных входов первой схемы 3 сравнения не совпадают с информацией, установленной на первой группе входов первой схемы 3 сравнения, то ожидается сигнал «СИП, поступающий с магистрали ЭВМ 7 от платы, на которой данная информация совпала, и если этот «СИП приходит через блок 6 сопряжения на первый блок 14 логики, то первый блок 14 логики вырабатывает сигнал «УО - сигнал установки в нулевое состояние первого триггера 16, а затем сбрасывает его.

Если сигнал «СИП из магистрали ЭВМ 7 не проходит (т.е. нет платы с таким номером),то первый триггер 16 не срабатывает и активная плата остается активной. Если адрес, по которому идет обращение, является адресом «Окна, то в цикле «Вывод сигнал «Вывод поступает на первый 14 и второй 15 блоки логики, при этом второй блок 15 логики вырабатывает сигналы «МВК, «СВК, «ЗАП, «ЗП1С, «ЗП1М, «СИПЗ, а информация, поступающая с магистрали ЭВМ 7 через второй регистр обмена 25, выдается на вторую группу информационных входов-выходов блока 8 коммутации, а с третьего регистра 26 обмена, выдается на первую группу информационных выходов разряды адреса «Окна, с нулевого по седьмой, а с первого регистра 24 обмена выдаются старшие разряды содержимого регистра страницы, с восьмого по пятнадцатый, причем разряды с тринадцатого по пятнадцатый поступают на дешифратор 4 номера страницы.

При поступлении сигналов «МВК, «СВК дешифратор 4 номера банка выдает разрешение выборки на соответствующие страницы памяти блока 1 памяти.

В случае, если запоминающее устройство работает в режиме ЭОЗУ, т.е. сигнал «Упр - сигнал выборки режима работы, находится в единичном состоянии, то информация на вторую группу информационных выходов блока 8 коммутации поступает не из первого регистра 24 обмена, а из третьего регистра 26 обмена, т.е. не производится обращение к регистру страницы.

Работа запоминающего устройства в режиме «ЭПЗУ (энергонезависимого постоянного запоминающего устройства) характерна тем, что отсутствует запись в блоке 1 памяти.

т.е. второй блок 15 логики не вырабатывает сигналов «МВК и «СВК в цикле «Вывод.

В режиме «ЭОЗУ в устройстве преду- смотрена возможность подключения и отключения банка памяти с помощью перемычек (не показаны), подключенных к группе информационных входов мультиплексора выборки страницы 13 (8 страниц по 10 4кх16).

Сигналы, поступающие на первую группу входов первого блока 14 логики позволяют выделить область системного ОЗУ, предназначенную для работы с вычислительными устройствами (не показаны).

Питание в блок 1 памяти подается от щины питания ЭВМ4-5В или от щины питания ЭВМ4-БАТ, либо от установленного на плату резервного источника 12 питания.

Использование изобретения позволит 20 уменьшить номенклатуру устройств, подключаемых к ЭВМ за счет использования устройства в качестве ВЭЗУ, ЭПЗУ или ЭОЗУ, а также позволит переставлять платы запоминающих устройств из одного конструктивного места в другое без потери инфор- 25 мации.

Формула изобретения

Запоминающее устройство, содержащее блок памяти, блок управления, дешифратор номера страницы, выходы которого соединены с входами выборки страниц блока памяти, отличающееся тем, что, с целью расширения области применения устройства путем обеспечения работы устройства в ка- честве энергонезависимого запоминающего устройства или энергонезависимого оперативного .запоминающего устройства, или энергонезависимого постоянного запоминающего устройства, в него введены блок коммутации, мультиплексор выбора страницы

0 блока памяти, три элемента односторонней проводимости, резервный источник питания, информационные входы-выходы первой группы блока коммутации являются информационными входами-выходами устройства, информационные входы-выходы второй группы блока коммутации соединены с информационными входами-выходами блока памяти, выходы первой группы блока коммута/хии соединены с входами выбора первой группы блока управления и адресными входами

Q первой группы блока памяти, выходы второй группы блока коммутации соединены с соответствующими адресными входами второй группы блока памяти, входами дешифратора номера страницы и с входами первой группы мультиплексора выбора страницы, входы

5 второй группы которого являются входами установки кода выбранных страниц устройства, выходы третьей группы блока коммутации соединены с входами выбора команд второй

группы; блока управления, входы третьей группы блока управления являются входами

выбора

кода номера блока управления являются входами установки кода номера устройства, вхо- ронизации блока управления являют- вляющими входами устройства и соеДЫ СИИ)

ся упра динены входам номера

номера устройства, входы установки

с соответствующими управляющими -I блока коммутации, дешифратора страницы и блока памяти, управляющие выходы блока управления соединены с соответствующими управляющими входам 1 блока коммутации и дешифра

я группа

3-я Вх 2 3-я группагруппа

Грутты i

Входы

Группа

тора номера страницы, выход мультиплексора выбора страницы соединены с входами выборки блока управления, вход установки режима которого является входом установки режима устройства, выход синхронизации блока управления является выходом синхронизации устройства, вход питания блока памяти соединен с выходами элементов односторонней проводимости, выходы которых подключены соответственно к выходам резервного источника питания и к первой и второй щинам питания устройства.

Таблица 1 СОЗУ I Фяк

Фикс Упр А10 АИ УО I У1 1сОЗУ|фякс 1128 | А-8

3-я 1-я Входы груп- группа па

1 I 1

1 1 1 1 1 1 1 О О 1

Выходы

о

О О О 1 О О О О

о о о о

ТаСлица2

ПЗУ-- ОЗУ| СИПЗ СВК МВК сип I СИПЗ 4т ll Зп1м Зп1с| Зап MBKJCBK

О О l 1 1 1111 V

11111 11000 11111

Входы

Выходы

| для с | |||

| Машина для разделения сыпучих материалов и размещения их в приемники | 0 |

|

SU82A1 |

| Боронной оборотный зуб из углового металла | 1913 |

|

SU681A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| лектронный диск - внешнее ЗУ ЭВМ | |||

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

| Пюпитр для работы на пишущих машинах | 1922 |

|

SU86A1 |

Авторы

Даты

1990-11-23—Публикация

1988-01-14—Подача