4

:д

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с группой блоков памяти | 1987 |

|

SU1587518A1 |

| Устройство для сопряжения процессора с группой блоков памяти | 1987 |

|

SU1501071A1 |

| Устройство для параллельного обмена информацией | 1983 |

|

SU1164688A1 |

| МИКРОЭВМ | 1991 |

|

SU1819017A1 |

| Устройство для обмена информацией между абонентами | 1986 |

|

SU1383376A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для сопряжения процессора с группой устройств памяти | 1986 |

|

SU1348843A1 |

| Многопроцессорная вычислительная система | 1987 |

|

SU1792540A3 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| АДАПТЕР-КОММУТАТОР МАГИСТРАЛЕЙ | 2000 |

|

RU2188449C2 |

Изобретение относится к вычис- лительной технике, в частности к автоматизированному контролю, управлению и обработке информации. Целью изобретения является увеличение производительности системы за счет возможности непрерывной и независимой работы двух процессоров. Управляющая вычислительная система содержит микро-ЭВМ 1, содержащую процессор 2 с устройством 3 ввода/вывода, оперативным запоминающим устройством 4 и внешними устройствами 5, блок 6 управления, мультиплексор 7, основное оперативное запоминающее устройство 8, блок 9 управления доступом, второй процессор 10, постоянное запоминающее устройство 11, оперативное запоминающее устройство 12 второго процессора. 5 ил.

cpua.l

Изобретение относится к вычислительной технике, в частности к автоматизированному управлению технологическими процессами и контролю и обработке информа1 1и.

Целью изобретения является повышение производительности системы за счет возможности непрерывной и независимой работы двух процессоров.

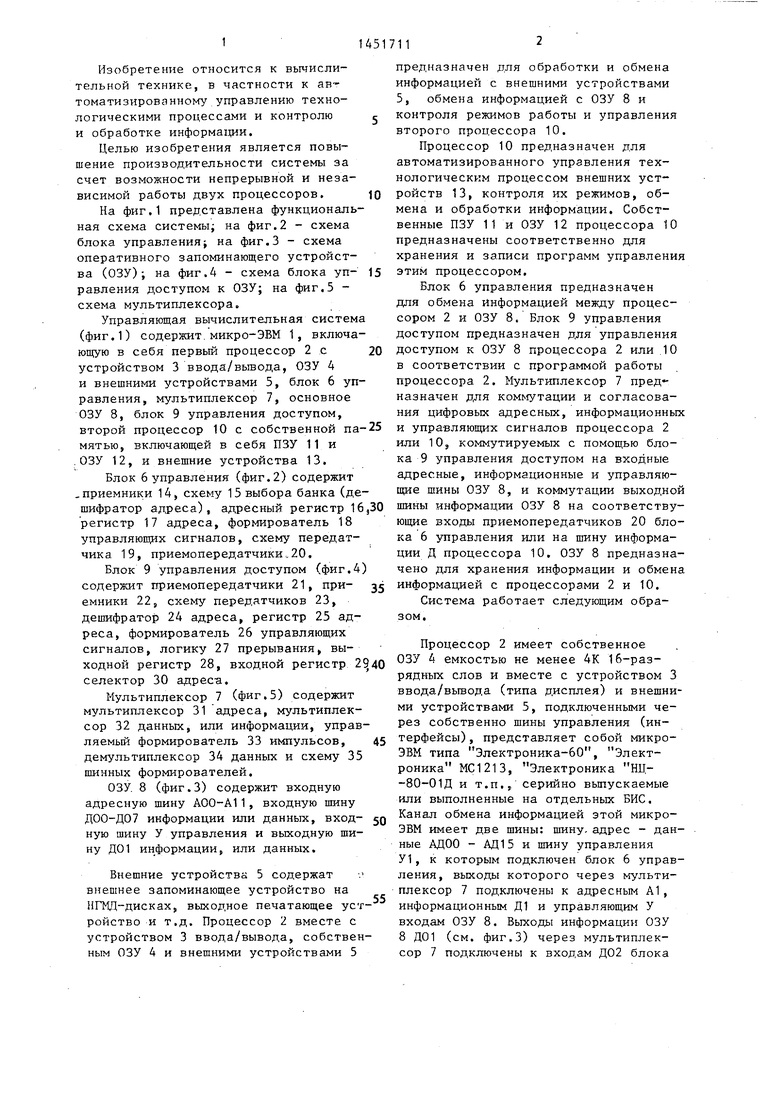

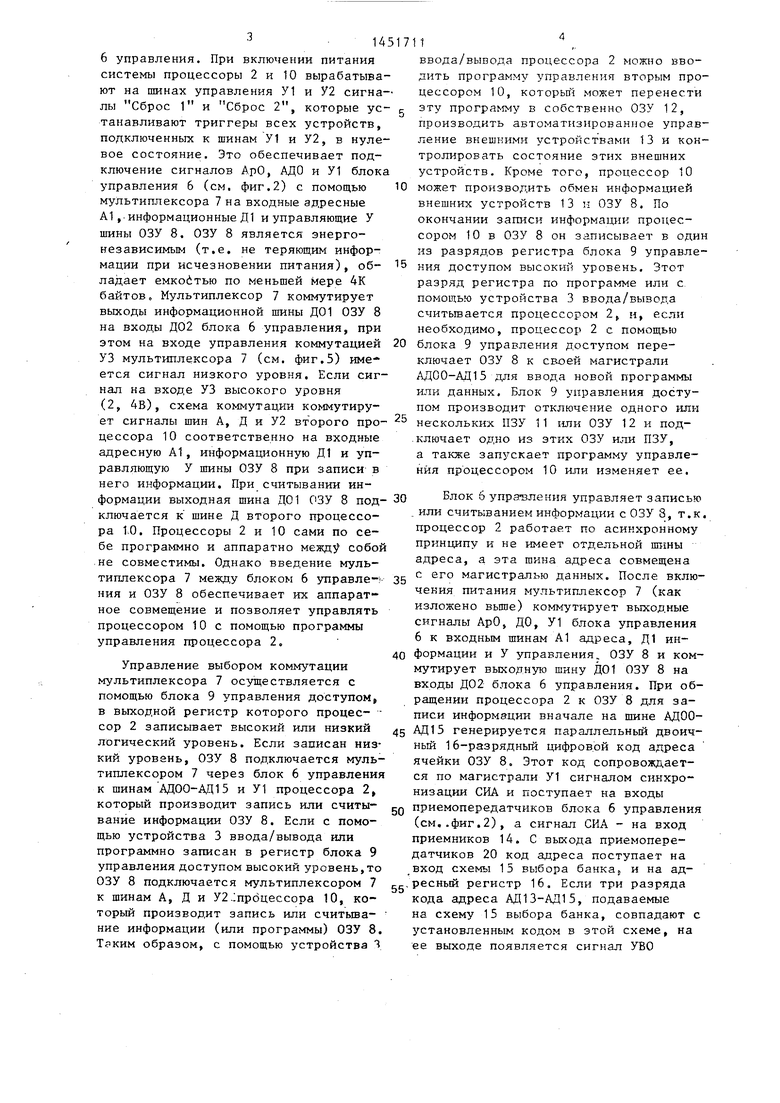

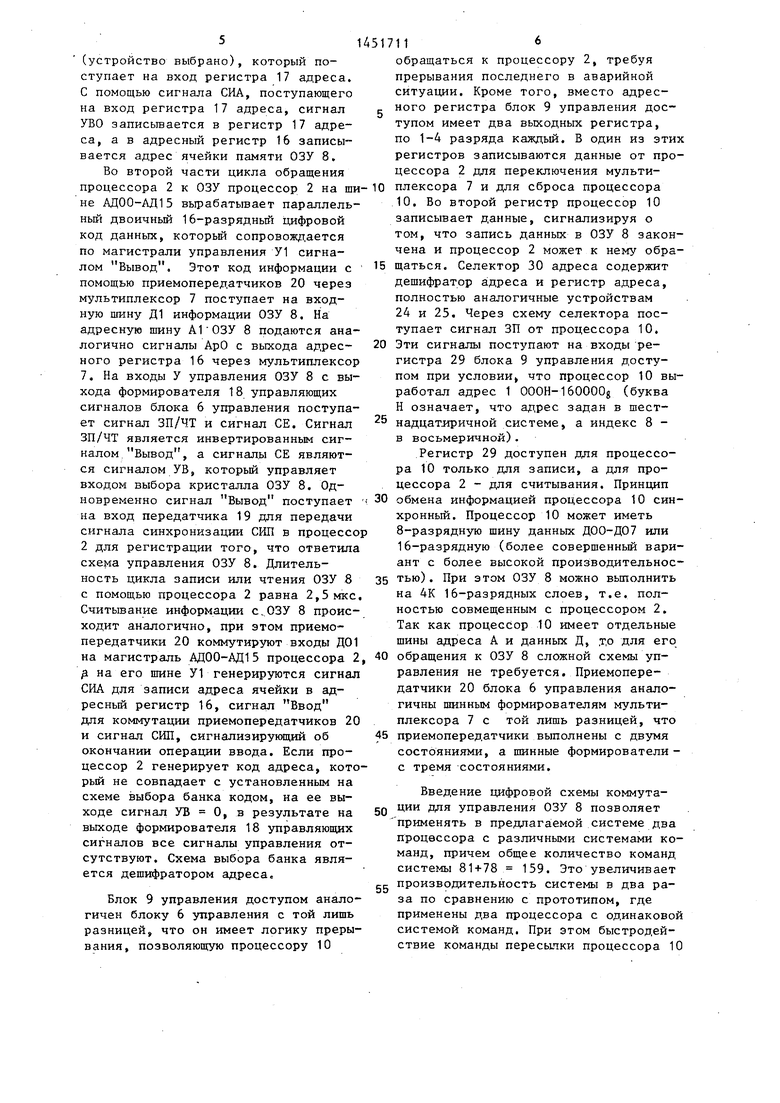

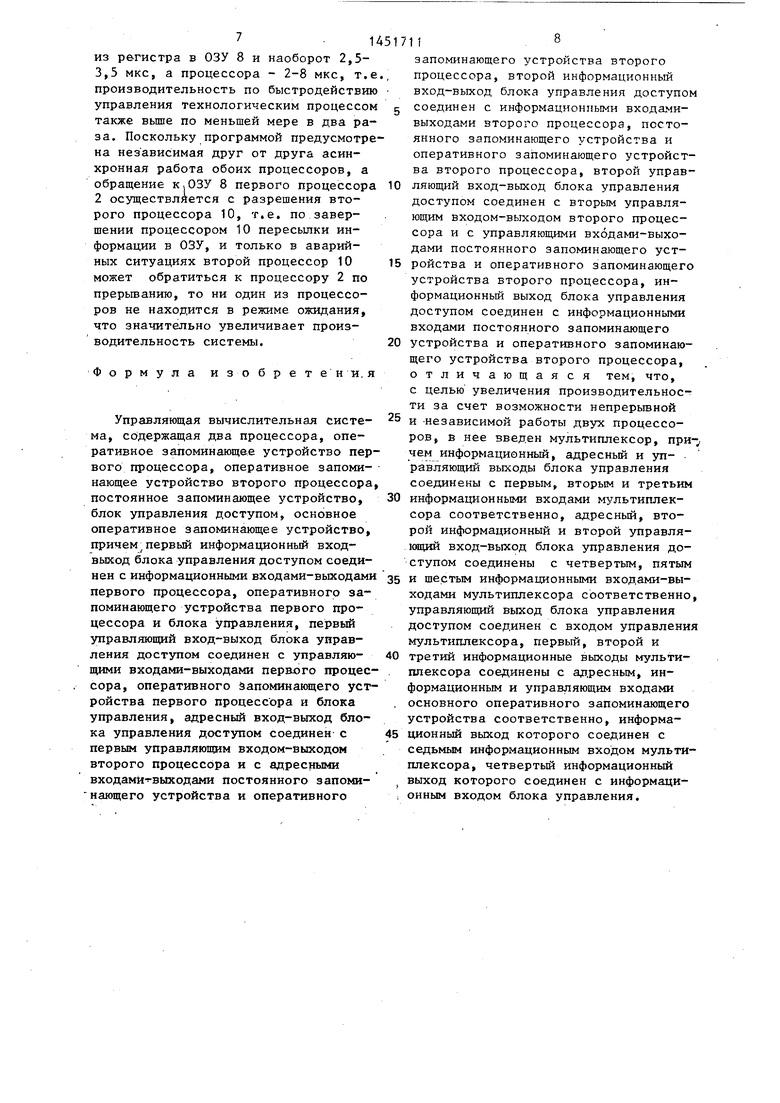

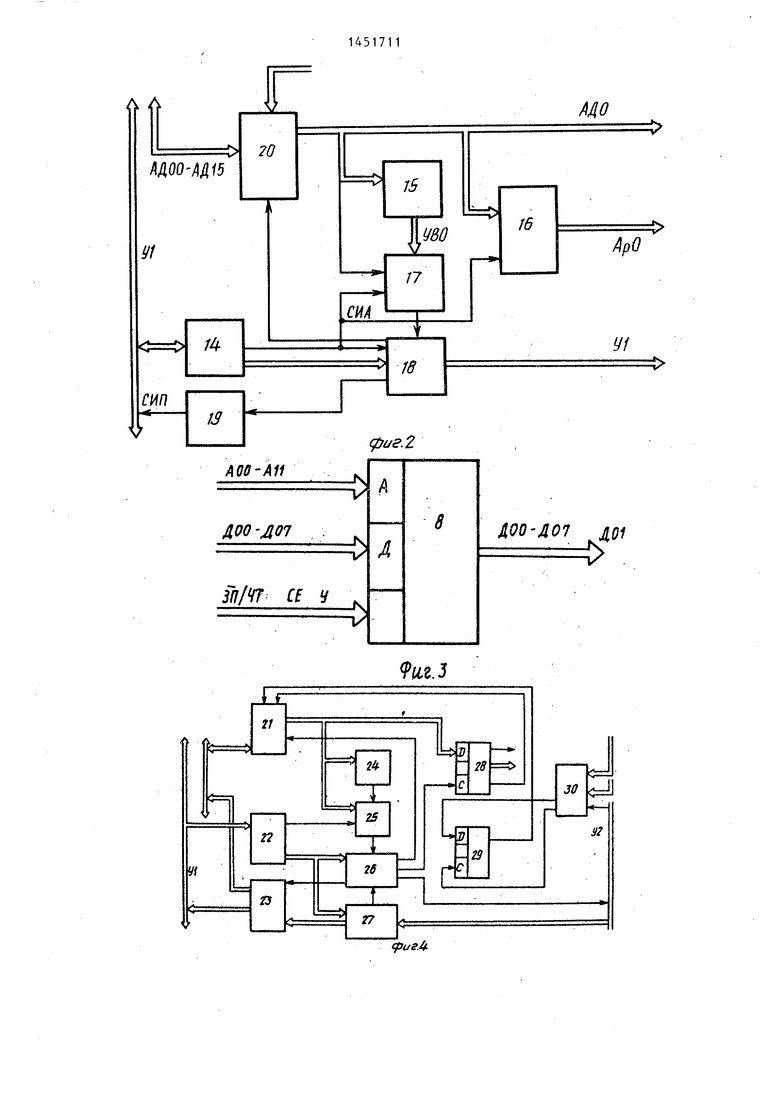

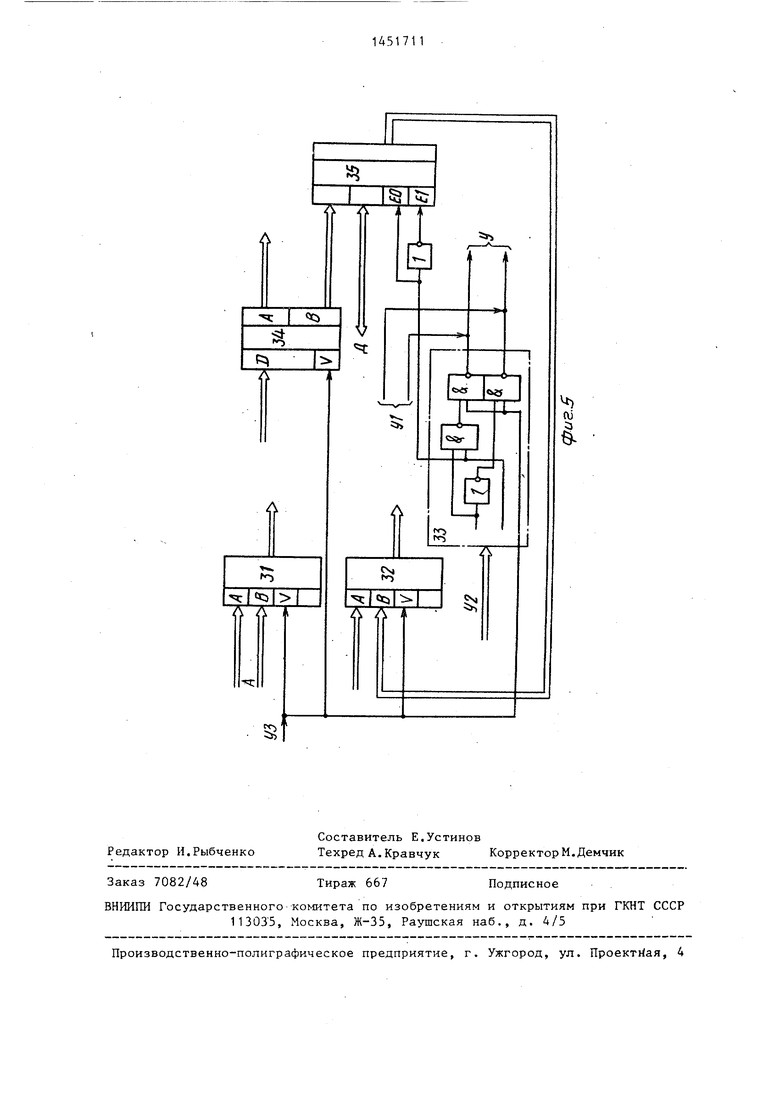

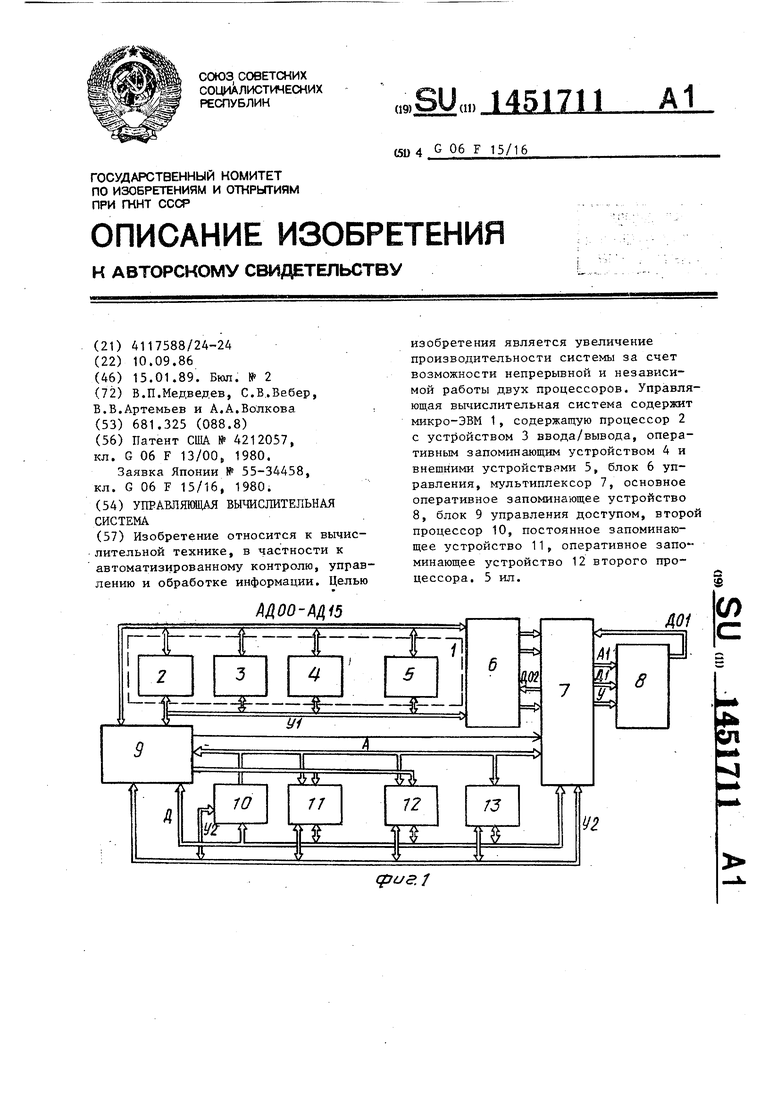

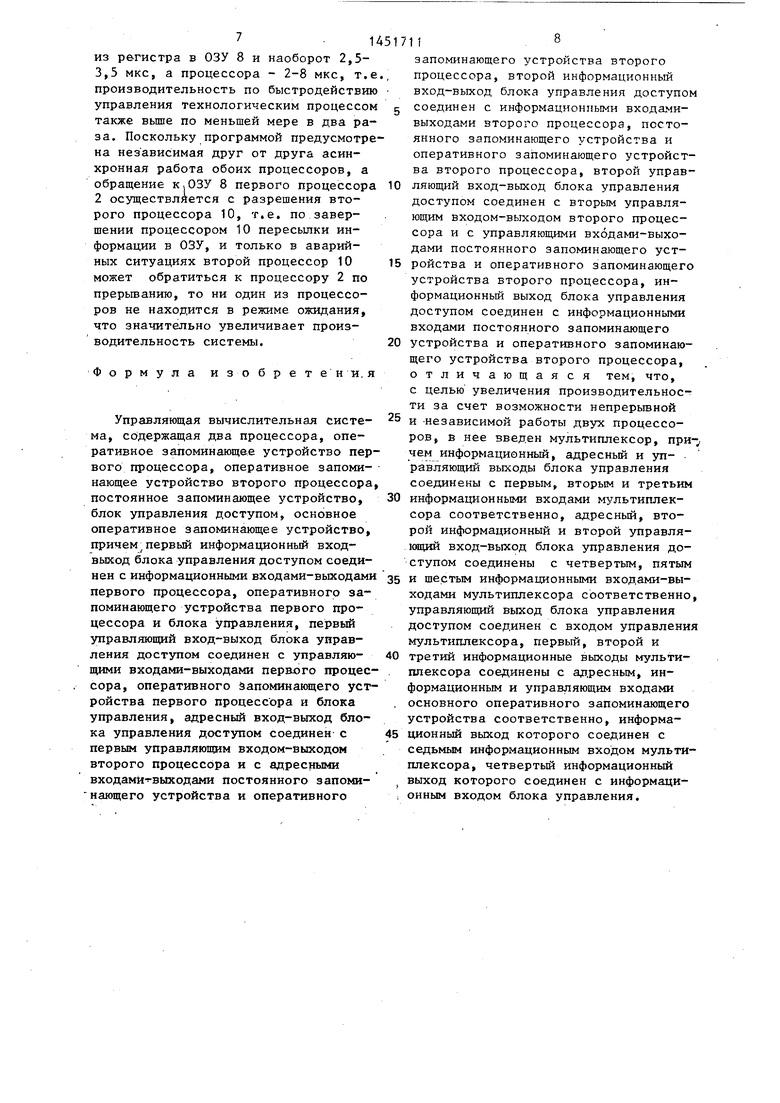

На фиг.1 представлена функциональная схема системы; на фиг.2 - схема блока управленияj на фиг.З - схема оперативного запоминающего устройства (ОЗУ); на фиг.4 - схема блока уп- равления доступом к ОЗУ; на фиг.З - схема мультиплексора.

Управляющая вычислительная система (фиг.1) содержит. микро-ЭВМ 1, включающую в себя первый процессор 2 с устройством 3 ввода/вьшода, ОЗУ 4 и внешними устройствами 5, блок 6 управления, мультиплексор 7, основное ОЗУ 8, блок 9 управления доступом, второй процессор 10 с собственной памятью, включающей в себя ПЗУ 11 и .ОЗУ 12, и внешние устройства 13.

Блок 6 управления (фиг.2) содержит .приемники 14, схему 15 выбора банка (дешифратор адреса), адресный регистр 16 регистр 17 адреса, формирователь 18 управляющих сигналов, схему передатчика 19, приемопередатчики.20.

Блок 9 управления доступом (фиг.4 содержит приемопередатчики 21, при- емники 22, схему передатчиков 23, дешифратор 24 адреса, регистр 25 адреса, формирователь 26 управляющих сигналов, логику 27 прерывания, выходной регистр 28, входной регистр 2 селектор 30 адреса.

Мультиплексор 7 (фиг,5) содержит мультиплексор 31 адреса, мультиплексор 32 данных, или информации, управляемый формирователь 33 импульсов, демультиплексор 34 данных и схему 35 шинных формирователей.

ОЗУ. 8 (фиг. 3) содержит входную адресную шину АОО-А11, входную шину ДОО-Д07 информации или данных, вход- ную шину У управления и выходную шину Д01 ин формации, или данных.

Внешние устройства 5 содержат внешнее запоминающее устройство на НГМД-дисках, выходное печатающее устройство и т.д. Процессор 2 вместе с устройством 3 ввода/вывода, собственным ОЗУ 4 и внешними устройствами 5

5 0

5

0

5

предназначен для обработки и обмена информацией с внешними устройствами 5, обмена информацией с ОЗУ 8 и контроля режимов работы и управления второго процессора 10.

Процессор 10 предназначен для автоматизированного управления технологическим процессом внешних устройств 13, контроля их режимов, обмена и обработки информации. Собственные ПЗУ 11 и ОЗУ 12 процессора 10 предназначены соответственно для хранения и записи программ управления этим процессором.

Блок 6 управления предназначен для обмена Информацией между процессором 2 и ОЗУ 8. Блок 9 управления доступом предназначен для управления доступом к ОЗУ 8 процессора 2 или 10 в соответствии с программой работы процессора 2. Мультиплексор 7 назначен для коммутации и согласования цифровых адресных, информационных и управляющих сигналов процессора 2 или 10, коммутируемых с помощью блока 9 управления доступом на входные адресные, информационные и управляющие шины ОЗУ 8, и коммутации выходной шины информации ОЗУ 8 на соответствующие входы приемопередатчиков 20 блока 6 управления или на шину информации Д процессора 10. ОЗУ 8 предназначено для хранения информации и обмена информацией с процессорами 2 и 10.

Система работает следующим образом.

Процессор 2 имеет собственное ОЗУ 4 емкостью не менее 4К 16-разрядных слов и вместе с устройством 3 ввода/вьшода (типа дисплея) и внешними устройствами 5, подключенными через собственно шины управления (интерфейсы) , представляет собой микро- ЭВМ типа Электроника-60, Электроника МС1213, Электроника НЦ- -80-01Д и т.п., серийно выпускаемые или выполненные на отдельных БИС. Канал обмена информацией этой микро- ЭВМ имеет две шины: шину, адрес - данные АД00 - АД15 и шину управления У1, к которым подключен блок 6 управления, выходы которого через мультиплексор 7 подключены к адресным А1, информационным Д1 и управляющим У входам ОЗУ 8. Выходы информации ОЗУ 8 Д01 (см. фиг.З) через мультиплексор 7 подключены к входам Д02 блока

- 14 6 управления. При включении питания системы процессоры 2 и 10 вырабатывают на шинах управления У1 и У2 сигналы Сброс 1 и Сброс 2, которые ус танавливают триггеры всех устройств, подключенных к шинам У1 и У2, в нулевое состояние. Это обеспечивает подключение сигналов АрО, АДО и У1 блок управления 6 (см. фиг.2) с помощью мультиплексора 7 на входные адресные А1 , информационные Д1 и управляющие У шины ОЗУ 8. ОЗУ 8 является энергонезависимым (т.е. не теряющим информации при исчезновении питания), об- ладает емкостью по меньшей мере 4К байтов. Мультиплексор 7 коммутирует выходы информационной шины Д01 ОЗУ 8 на входы Д02 блока 6 управления, при этом на входе управления коммутацией УЗ мультиплексора 7 (см. фиг.5) име- ется сигнал низкого уровня. Если сигнал на входе УЗ высокого уровня (2, 4В), схема коммутации коммутирует сигналы шин А, Д и У2 вт орого про- цессора 10 соответственно на входные адресную А1, информационную Д1 и уп- равляюш;ую У шины ОЗУ 8 при записи в него информации. При считывании информации выходная шина Д01 ОЗУ 8 под- ключается к шине Д второго процессора 10. Процессоры 2 и 10 сами по себе программно и аппаратно между собой не совместимы. Однако введение мультиплексора 7 между блоком 6 управле-;- ния и ОЗУ 8 обеспечивает их аппаратное совмещение и позволяет управлять процессором 10 с помощью программы управления процессора 2.

Управление выбором коммутации

мультиплексора 7 осуществляется с помощью блока 9 управления доступом, в выходной регистр которого процес- - сор 2 записывает высокий или низкий логический уровень. Если записан низкий уровень, ОЗУ 8 подключается мультиплексором 7 через блок 6 управления к шинам АДОО-АД15 и У1 процессора 2,

который производит запись или считы

вание информации ОЗУ 8. Если с помощью устройства 3 ввода/вывода или программно записан в регистр блока 9 управления доступом высокий уровень,то ОЗУ 8 подключается мультиплексором 7 к шинам А, Д и У2.:процессора 10, который производит запись или считьша- ние информации (или программы) ОЗУ 8. Таким образом, с помощью устройства

11

ввода/вывода процессора 2 можно вводить программу управления вторым процессором 10, которьш может перенести эту программу в собственно ОЗУ 12, производить автоматизированное управление внешними устройствами 13 и контролировать состояние этих внешних устройств. Кроме того, процессор 10 может производить обмен информацией внешних устройств 13 м ОЗУ 8. По окончании записи информации процессором 10 в ОЗУ 8 он записывает в оди из разрядов регистра блока 9 управления доступом высокий уровень. Этот разряд регистра по программе или с. помощью устройства 3 ввода/вывода считьшается процессором 2 и, если необходимо, процессор 2 с помощью блока 9 управления доступом переключает ОЗУ 8 к своей магистрали АДОО-АД15 для ввода новой программы или данных. Блок 9 управления доступом производит отключение одного или нескольких ПЗУ 11 или ОЗУ 12 и под-ключает одно из этих ОЗУ или ПЗУ, а также запз скает программу управления процессором 10 или изменяет ее.

Блок 6 управления управляет записью или считыванием информации с ОЗУ 8, т.к процессор 2 работает по асинхронному принципу и не имеет отдельной шины адреса, а эта шина адреса совмещена с его магистралью данных. После включения питания мультиплексор 7 (как изложено вьш1е) коммутирует выходные сигналы АрО, ДО, У1 блока управления 6 к входным шинам А1 адреса, Д1 информации и У управления. ОЗУ 8 и коммутирует выходную шину Д01 ОЗУ 8 на входы Д02 блока 6 управления. При обращении процессора 2 к ОЗУ 8 для записи информации вначале на шине АДОО- АД15 генерируется параллельный двоичный 16-разрядньга цифровой код адреса ячейки ОЗУ 8. Этот код сопровождается по магистрали У1 сигналом синхронизации СИА и поступает на входы приемопередатчиков блока 6 управления (см..фиг,2), а сигнал СИА - на вход приемников 14. С выхода приемопередатчиков 20 код адреса поступает на вход схемы 15 выбора 6aHKas и на адресный регистр 16. Если три разряда кода адреса АД13-АД15, подаваемые на схему 15 выбора банка, совпадают с установленным кодом в этой схеме, на ее выходе появляется сигнал УВО

5

(устройство выбрано), который поступает на вход регистра 17 адреса. С помощью сигнала СИЛ, поступающего на вход регистра 17 адреса, сигнал УВО эаписьтается в регистр 17 адреса, а в адресный регистр 16 записывается адрес ячейки памяти ОЗУ 8,

Во второй части цикла обращения процессора 2 к ОЗУ процессор 2 на ши не АДОО-АД15 вьфабатьгоает параллель- ньй двоичный 16-разрядный цифровой код данных, который сопровожд,ается по магистрали управления У1 сигналом Вывод. Этот код информации с помощью приемопередатчиков 20 через мультиплексор 7 поступает на входную шину Д1 информации ОЗУ 8. На адресную шину АГОЗУ 8 подаются аналогично сигналы АрО с выхода адрес- ного регистра 16 через мультиплексор 7. На входы У управления ОЗУ 8 с выхода формирователя 18 управляющих сигналов блока 6 управления поступает сигнал ЗП/ЧТ и сигнал СЕ. Сигнал ЗП/ЧТ является инвертированным сигналом Вывод, а сигналы СЕ являются сигналом УВ, которьм управляет входом выбора кристалла ОЗУ 8. Одновременно сигнал Вывод поступает на вход передатчика 19 для передачи сигнала синхронизации СИП в процессо 2 для регистрации того, что ответила схема управления ОЗУ 8. Длительность цикла записи или чтения ОЗУ 8 с помощью процессора 2 равна 2,5мкс Считьшание информации с.ОЗУ 8 происходит аналогично, при этом приемопередатчики 20 коммутируют входы Д01 на магистраль АДОО-АД15 процессора 2 ft на его шине У1 генерируются сигнал СИА для записи адреса ячейки в ад- ресньй регистр 16, сигнал Ввод для коммутации приемопередатчиков 20 и сигнал СИП, сигнализирующий об окончании операции ввода. Если процессор 2 генерирует код адреса, который не совпадает с установленным на схеме выбора банка кодом, на ее выходе сигнал УВ О, в результате на выходе формирователя 18 управляющих сигналов все сигналы управления отсутствуют. Схема выбора банка является дешифратором адреса,

Блок 9 управления доступом аналогичен блоку 6 управления с той лищь разницей, что он имеет логику прерывания, позволяющую процессору 10

116

обращаться к процессору 2, требуя прерывания последнего в аварийной ситуации. Кроме того, вместо адресного регистра блок 9 управления доступом имеет два выходных регистра, по 1-4 разряда каждый. В один из этих регистров записываются данные от процессора 2 для переключения мультиплексора 7 и для сброса процессора 10. Во второй регистр процессор 10 записывает данные, сигнализируя о том, что запись данных в ОЗУ 8 закончена и процессор 2 может к нему обращаться. Селектор 30 адреса содержит дешифратор а:дреса и регистр адреса, полностью аналогичные устройствам 24 и 25. Через схему селектора поступает сигнал ЗП от процессора 10. Эти сигналы поступают на входы регистра 29 блока 9 управления доступом при условии что процессор 10 выработал адрес 1 OOOH-160000g (буква Н означает, что ад,рес задан в шестнадцатиричной системе, а индекс 8 - в восьмеричной).

Регистр 29 доступен для процессора 10 только для записи, а для процессора 2 - для считывания. Принцип обмена информацией процессора 10 синхронный. Процессор 10 может иметь 8-разрядную шину данных ДОО-Д07 или 16-разрядную (более совершенньй вариант с более высокой производительностью) . При этом ОЗУ 8 можно выполнить на 4К 16-разрядных слоев, т.е. полностью совмещенным с процессором 2. Так как процессор 10 имеет отдельные шины адреса А и данных Д, ,т,о для его обращения к ОЗУ 8 сложной схемы управления не требуется. Приемопередатчики 20 блока 6 управления аналогичны шинным формирователям мультиплексора 7 с той лишь разницей, что приемопередатчики вьшолнены с двумя состояниями, а шинные формирователи- с тремя состояниями.

Введение цифровой схемы коммутации для управления ОЗУ 8 позволяет применять в предлагаемой системе два процессора с различными системами команд, причем общее количество команд системы 81+78 159. Это увеличивает производительность системы в два раза по сравнению с прототипом, где применены два процессора с одинаковой системой команд. При этом быстродействие команды пересылки процессора 10

1 из регистра в ОЗУ 8 и наоборот 2,5- 3,5 МКС, а процессора - 2-8 мкс, т.е производительность по быстродействию управления технологическим процессом также выше по меньшей мере в два раза. Поскольку программой предусмотрена нез авис:имая друг от друга асинхронная работа обоих процессоров, а обращение к,ОЗУ 8 первого процессора 2 осуществляется с разрешения второго процессора 10, т.е. по завершении процессором 10 пересылки информации в ОЗУ, и только в аварийных ситуациях второй процессор 10 может обратиться к процессору 2 по прерьгоанию, то ни один из процессоров не находится в режиме ожидания, что значительно увеличивает производительность системы.

Формула изобретени.я

Управляющая вычислительная систе- ма, содержащая два процессора, оперативное запоминающее устройство первого процессора, оперативное запоминающее устройство второго процессора постоянное запоминающее устройство, блок управления доступом, основное оперативное запоминающее устройство, причем первый информационный вход- выход блока управления доступом соединен с информационными входами-выходами первого процессора, оперативного запоминающего устройства первого процессора и блока управления, первый управляющий вход-выход блока управления доступом соединен с управляю- щими входами-выходами первого процессора, оперативного Запоминающего устройства первого процессора и блока управления, адресный вход-выход блока управления доступом соединен с первым управляющим входом-выходом второго процессора и с адресными входамй-гвыходами постоянного запоминающего устройства и оперативного

11«

запоминающего устройства второго процессора, второй информационный вход-выход блока управления доступом соединен с информационными входами- выходами второго процессора, постоянного запоминающего устройства и оперативного запоминающего устройства второго процессора, второй управляющий вход-выход блока управления доступом соединен с вторым управляющим входом-выходом второго процессора и с управляющими входами-выходами постоянного запоминающего устройства и оперативного запоминающего устройства второго процессора, информационный выход блока управления доступом соединен с информационными входами постоянного запоминающего устройства и оперативного запоминающего устройства второго процессора, отличающаяся тем, что, с целью увеличения производительности за счет возможности непрерьгоной и -независимой работы двух процессоров, в нее введен мультиплексор, при чем информационный, адресный и уп- равляющий выходы блока управления соединены с первым, вторым и третьим информационными входами мультиплексора соответственно, адресный, второй информационный и второй управля- кяций вход-выход блока управления доступом соединены с четвертым, пятым и шестым информационными входами-выходами мультиплексора соответственно управляющий выход блока управления доступом соединен с входом управлени мультиплексора, первый, второй и третий информационные выходы мультиплексора соединены с адресным, информационным и управляющим входами основного оперативного запоминающего устройства соответственно, информа- 1ЩОННЫЙ выход которого соединен с седьмым информационным входом мультиплексора, четвертый информационный выход которого соединен с информационным входом блока управления.

Л

ЛАОО А/1 5

20

У1

/4

А00-А11

ДОО -Л0

311/47 а У

/Jyf

/5

Тш

/(5

XI/

т-

/7

/

Г8

l

фиг.2

ЛОО 407 Л01

te.5

i QQ

|tgi|

Л Л

Редактор И.Рыбченко

Составитель Е.Устинов

Техред А.Кравчук КорректорМ.Демчик

Заказ 7082/48

Тираж 667

ВНИИГШ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

л

wr

V

toe

«k

aj

SN

Подписное

| Патент США № 4212057, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство двукратного усилителя с катодными лампами | 1920 |

|

SU55A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-01-15—Публикация

1986-09-10—Подача