1

Изобретение относится к области вычислительной технике, в частности к арифметическим устройствам последовательно-параллельного действия.

Известно устройство умножения двоичных чисел, представленных последовательным кодом, содержащее сумматор, регистры множимого и множителя, элементы И, первые входы которых соединены с управляющей шиной устройства, вторые входы первого и второго элемента И соединены с информационными шинами, а выходы - с п-ым разрядом сумматора. Выход первого элемента И соединен с (п-1)-ым разрядом регистра множителя, выход третьего элемента И соединен со входом 1-го разряда регистра множимого {.

К недостаткам этого устройства следует отнести малый диапазон изменения чисел и дополнительные затраты оборудования, так как разрядная сетка сумматора имеет 2п разрядов.

Известно также устройство для умножения двоичных чисел, содержащее регистры сомножителей, множительный блок, блоки приема сомножителей, блоки записи и блок управления 2.

Недостатками указанного устройства являются малый диапазон предс-гавления чисел, увеличение аппаратурных затрат за счет введения дополнительных блоков записи, приема информации,

.блока управления и блоков выборки информации.

Наиболее близким к предлагаемому является устройство для умножения, содержащее регистры множимого и множителя, комбинационный сумматор частичных произведений, регистр частичных произведений, преобразователь позиционного кода в знакоразрядный и схемы подключения учетверенного множимого. 3 .

К недостаткам известного устройства следует отнести малый диапазон изменения чисел, дополнительные затраты оборудования за счет удлинения на п разрядов сумматора частичных произведений.

Цель изобретения - увеличение диапазона представления чисел и сокращения объема оборудования.

Поставленная цель достигается тем, что устройство для умножения, содержащее комбинадионный сумматор частичных произведений, регистры множимого и множителя, преобразователь позиционного кода в знакоразрядный, причем выходы регистра множимого соединены

соответственно со входами первой группы комбинационного сумматора частичных произведений, содержит регистр порядков множимого, триггер управления, элементы задержки, сумматор по модулю два, элементы И-ИЛИ, элементы И, ИЛИ, блок элементов ИЛИ, причем выходы регистра порядка множимого соединены соответственно со входами первой группы блока элементов ИЛИ, выходы которого соединены со входами регистра частичных произведений, выходы которого соединены со сдвигом на один разряд в сторону старших разрядов со входами второй группы комбинационного сумматора частичных произведений, выходы четырех старших разрядов которого соединены со входами преобразователя позиционного кода в энакоразрядный,- первый выход которого соединен со входом первого элемента задержки, а второй выход - со входом второго элемента задержки, первый и второй выходы преобразователя позиционного кода в знакоразрядный соединены с первым и вторым входами первого элемента ИЛИ соответственно, выход которого соединен с первым входом сумматора по модулю два и первым входом Первого элемента И, второй вход которого соединен с выходом второго элемента ИЛИ, входы которого соединены с выходами элементов задержки соответственно, второй вход сумматора по модулю два соединен с выходом второго старшего разряда комбинационного .сумматора частичных произведений, первые входы первых групп первого и второго элементов И-ИЛИ соединены соответственно с первым и вторым выходами преобразователя позиционного кода в знакоразрядный, первый вход второй группы первого элемента И-ИЛИ соединен с выходом первого элемента задержки, первый вход второй группы второго элемента И-ИЛИ соединен с выходом второго элемента задержки, выход триггера -управления соединен со вторыми входами первых и вторых групп первого и второго.элементов И-ИЛИ, вторые входы вторых групп-первого и второго элементов И-ИЛИ являются инверсными, вход третьей группы второго элемента И-ИЛИ соединен с выходом второго элемента И, выходы первого и второго элементов И-ЙЛИ соединены с выходами выдачи знакоразрядных кодов гЬезультата устройства соответственно, селективные входы комбинациOHHOfo сумматора частичных произведений соединены со входами третьего элемента И соответственно, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен со входом сигнала выделения порядка множителя устройства, вход регистра множимого устройства соединен со входом ввода мантиссы .«1ножимого устройства, нулевой вход

триггера управления и установочный вход регистра частичных произведений соединены со входом сигнала сброса устройства, вход регистра порядков множимого соединен со входом ввода с порядка множимого устройства, выходы разрядов комбинационного сумматора частичных произведений, начиная с третьего старшего, соединены со входами второй группы блока элементов

ИЛИ, начиная со второго, первый вход |второй группы входов блока элементов ИЛИ соединен с выходом сумматора по модулю два.

Кроме того, преобразователь позиционного кода в знакоразрядный содержит четыре элемента И и два элемента ИЛИ, причем первые входы первого, второго, третьего и четвертого элементов И соединены с первым входом преобразователя, вторые входы первого и третьего элементов И соединены со вторым входом преобразователя, вторые входы второго и четвертого элементов И соединены с третьим входом.прео.бразователя, третий вход четвертого элемента И соединен с четвертым входом преобразователя, выходы первого, второго, третьего и четвертого элементов И соединены со входами сооответственно первого и второго элементов ИЛИ, выходы которых

подключены соответственно к первому и второму выходам преобразователя.

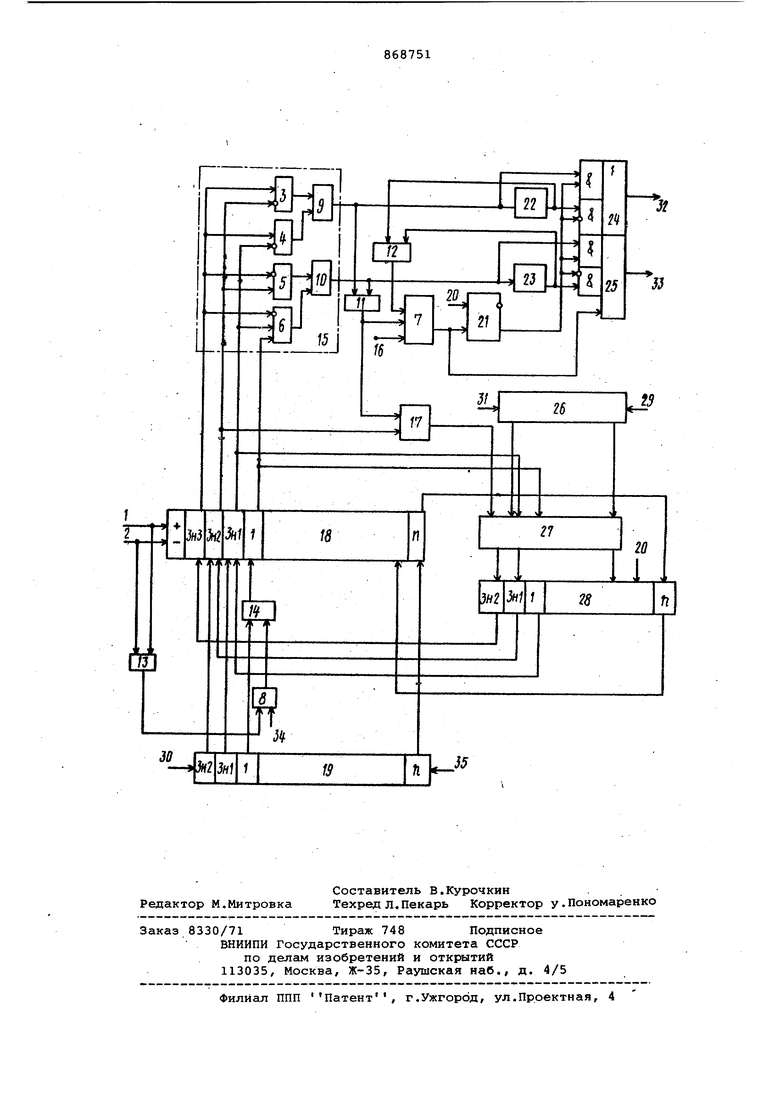

На чертеже приведена блок -схема предлагаемого устройства.

Устройство содержит селективные входы 1 и 2, на которые.поступают знакоразрядные коды (положительные и отрицательные); элементы 3-8, элементы ИЛИ 9-14, преобразователь 15

позиционного кода в знакоразрядный, вход 16 поступления сигнала нормализации мантиссы произведения, сумматор 17 по модулю два, комбинационный сумматор 18 частичных произведеНИИ, регистр 19 множимого, вход 20 поступления сигнала сброса в нуль, триггер 21 управления, .элементы 22 и 23 задержки, элементы И-ИЛИ 24 и 25, регистр 26 порядка множимого,

блок 27 элементов ИЛИ, регистр 28 частичных произведений, вход 29 сигнала выдачи порядка множимого, информационные входы 30 и 31 ввода мантиссы и порядка сооответственно, информационные . выходы 32 и 33 выдачи знакоразрядных кодов результата и вход 34 сигнала выделения порядка множителя .

При этом выходы регистра 26 соединены через блок. 27 элементов ИЛИ со

входами регистра 2В. Выходы регистра 2 28 соединены со смещением на один разряд в сторону старших разрядов со входами сумматора 18. Выходы, четыре старших разряда и сумматор. 18 соединены со входами преобразователя 15,

выходы которого соединены со входами элементов 22 и 23 задержки и через элемент ИЛИ 11 - с одними входами сумматора 17 по модулю два и элементом И 7, второй вход которого соединен через элемент ИЛИ 12 с выходами элементов 22 и 23 задержки. Второй вход сумматора 17 по модулю два соединен со вторым выходом комбинационного сумматора 18. Входы элементов И-ИЛИ 24 и 25 соединены с выходами преобразователя 15, элементов 22 и 23 задержки, элемента И 7 и единичным выходом триггера 21.

Устройство работает следующим образом.

Предварительно сбрасывается в нуль (по входу 20) регистр 28 и триггер 21 управления. Записывается порядок множимого (по входу 29) в регистр 26 сигналом, поступающим на вход 31, мантисса множимого (по входу 35) в регистр 19 сигналом, поступающим на вход 30. Суммирование порядков осуществляется по сигналу выделения .порядков, поступающему на вход 34, следующим образом.Предварительно порядок множимого перезаписывается из регистра 26 в старшие разряды регистра 28. На селективные BXOjBJ сумматора 18 поступает старшими разрядами вперед порядок множителя в виде знакоразрядных кодов. В зависимости от знаковых разрядов порядка множителя (операндам ) сумматор 18 настраивается на суммирование (вычитание) единичного разряда, поступающего с выхода элемента И 8, с полноразрядным кодом порядка множимого (операнда 6 ), поступающего на входы сумматора 18 с выхода регистра 2В. При этом с приходом каждого последующего разряда(начиная со старшего разряда операнда а ) промежуточная сумма порядков поступает с выхода регистра 28 на вход сумматора 18 со сдвигом на один разряд в сторону старших разрядов. Из сумматора 18 информация подается в преобразователь 15 кода, где она преобразуется из позиционного кода в знакоразрядный и выдается на выходы 32 и 33fi в виде {О, ±1 .

В преобразователе 15 анализируются четыре (три знаковых и один старший, значащий) разряда промежуточной суммы $ .На основании анализа этих рарядов преобразователь 15 выдает коды 0, ±1 . При этом код (+1) выдается на.выход, когда вычислительная сумма + 3,, а код (-1) , когда вычисленная сумма $ i-3. При выдаче кода (+1) вырабатывается сумматором 17 по модулю два сигнал, коррекция знака Зн2 промежуточной суммы $ с (+) на (-) и, наоборот, при выдаче кода (-1) вырабатывается сигнал коррекции знака Зн2 с (-) на (+), причем сигнал коррекции знака вырабатывается

только тогда, когда сумма по модулю два меньше четырех. Во всех последующих тактах суммирование порядков выполняется аналогично первому такту.

Умножение мантисс осуществляется в следующей последовательности.

Анализируется старшая цифра множителя, поступающего на входы 1 и 2. Если старшая цифра множителя-1, то в сумматоре 18 суммируется множимое с содержимым регистра 28, если старoшая цифра-множителя-, то множимое с содержи 1ым регистра 28 вычитается, При умножении на второй разряд множителя производится перезапись информации с регистра 28 в сумматоре 18

5 со сдвигом влево на один разряд. Затем анализируется значение второго разряда множителя и осуществляется суммирование (вычитание) множимого с полученной в первом такте суммой аналогично выше указанному. Таким

0 образом, в каждом такте множимое передается в сумматор, если значение i разряда м 1ожителя +1, либо не передается, если значение i разряда множителя О, и сумма сдвигается

5 на один разряд влево. Из сумматора информация подается в преобразователь 15, где преобразуется из позиционного кода в знакоразрядный аналогично выше указанному, причем ин0формация выдается через элементы 22 и 22q задержки на выходы 32 , и 33vi : В виде i разряда произведения О ,±1} / если вычисленная мантисса нормализованная.

5

Нормализация вычисленной мантиссы осуществляется в первом такте по сигналу, поступающему на вход 16. При этом, если нулевой разряд произведения О и первый разряд произведения Of то элементом И 7 выдается отри0цательное приращение порядка (), которое поступает на выход 33 через элемент И-ИЛИ 25. По этому приращению переключается триггер 2.1 в единичное состояние и потенциалом

5 открываются соответствующие схемы И элементов И-ИЛИ 24 и 25о. При этом выключаются элементы 22.и 232 задержки, что равносильно умножению вычисленной мантиссы на два.

0

Предлагаемое устройство по сравнению с известными позволяет увеличить диапазон изменения чисел, например, при шестиразрядном порядке числа могут изменяться в диапазоне от 2 до 2 , а также сократить

5 расход оборудования за счет уменьшения на п разрядов сумматора и регистра частичных произведений и за счет того, что операции как над порядками, так и над мантиссами вы0полняются на одном и том же сумматоре.

Формула изобретения 1. Устройство для умножения, содержащее комбинационный сумматор

5

частичных проиэведеиий, регистры множимого и множителя, преобразователь позиционного кода в знакоразрядный, причем выходы регистра множимого соединены соответственно со в одами первой группы комбинационного сумматора частичных произведений, отличающееся тем, что, с целью увеличения диапазона представления чисел и сокращения объема оборудования, оно содержит регистр порядков множимого, триггер управления, элементы задержки, сумматор по Модулю два, элементы ИгИЛИ, элементы И, ИЛИ, блок элементов ИЛИ, причем выходы регистра порядка множимого соединены соответственно со входами первой группы блока элементов ИЛИ, выходы которого соединены со входами регистра частичных произведений, выходы которого соединены со сдвигом н один разряд в сторону старших разрядов со входами второй группы комбина. ционного сумматора частичных произведений, выходы четырех старших разрядо которого соединены со входами преобразователя позиционного кода в знакоразрядный, первый выход которого соединен со входом первого элемента задержки, а второй выход - со входом второго элемента задержки, первый и второй выходы преобразователя- позиционного кода в знакоразрядный соединены с первым и вторым входами первого элемента ИЛИ соответственно, выход которого соединен с первым входом сумматора по модулю два и первым входом первого элемента И, второй вход которого соединен с выходом второго элемента ИЛИ, входы которого содинены с выходами элементов задержки соответственно, второй вход сумматора по модулю два соединен с выходом второго старшего разряда комбинационного сумматора частичных произведений , первые входы первых групп перSoro и второго элементов. И-ИЛИ соединены соответственно с первым и вторым выходами преобразователя позиционного кода-в знакоразрядный, первый вход второй группы первого элемента И-ИЛИ соединен с выходом первого элемента задержки, первый вход второй группы второго элемента И-ИЛИ соединен с выходом второго элемента задержки, выход триггера управления соединен со вторыми входами первых

и. вторых групп первого и второго элементов И-ИЛИ, вторые входы вторых . rpyjpn первого и второго элементов И-ИЛИ являются инверсными, вход третьей группы второго элемента И-ИЛИ

соединен с выходом второго элемента И, выходы первого и второго элементов И-ИЛИ соединены с выходами выдачи знакоразрядных кодов результата устройства сооответственно, селективные входы комбинационного сумматора частичных произведений соединены со входами третьего :элемента И соответственно, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен со входом сигнала выделения порядка множителя устройства, вход регистра множимого устройства соединен со входом ввода мантиссы множимого устройства, нулевой вход триггера управления и установочный вход регистра частичных произведений соединены со входом сигнала сброса устройства, вход регистра порядков множимого соединен со входом ввода порядка множимого устройства, выходы разрядо комбинационного сумматора частичных произведений, начиная с третьего старшего, соединены со входами второй группы блока элементов ИЛИ, начиная со второго, первый вход второй группы входов блока элементов ИЛИ соединен с выходом сумматора по модулю два.

2. Устройство по п. 1,отличающееся тем., что преобразователь позиционного кода в знакоразрядный содержит четыре элемента И и .два элемента ИЛИ, причем первые входы первого, второго, третьего и четвертого элементов И соединены с первым входом преобразователя, вторые входы первого и третьего элементов И соединены со вторым входом преобразователя, вторые входы второго и четвертого элементов И соединены с третьим входом преобразователя, третий вход четвертого элемента И соединен с четвертым входом преобразователя, выходы первого, второго, третьего и четвертого элементов И соединены со входами соответственно первого и второго элементов ИЛИ, выходы которых подключены соответственно к первому и второму выходам преобразователя.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 631919, кл, G 06 F 7/38, 1976.

2.Авторское свидетельство СССР №450169, кл. G 06 F 7/39, 1972.

3.Каган Б.М,, Каневский М.М. Цифровые вычислительные машины и систе

мы. М., Энергия

1974, с. 342344 (прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1984 |

|

SU1226447A1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Устройство для деления с плавающей запятой | 1979 |

|

SU860063A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Устройство для умножения | 1989 |

|

SU1612295A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1020818A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

Авторы

Даты

1981-09-30—Публикация

1979-10-18—Подача