Изобретение относится к вычислительной технике и может быть использовано для умножения многоразрядных последовательных кодов с иррациональ- ными основаниями, кодов золотой пропорции.

Цель изобретения - повышение быстродействия устройства.

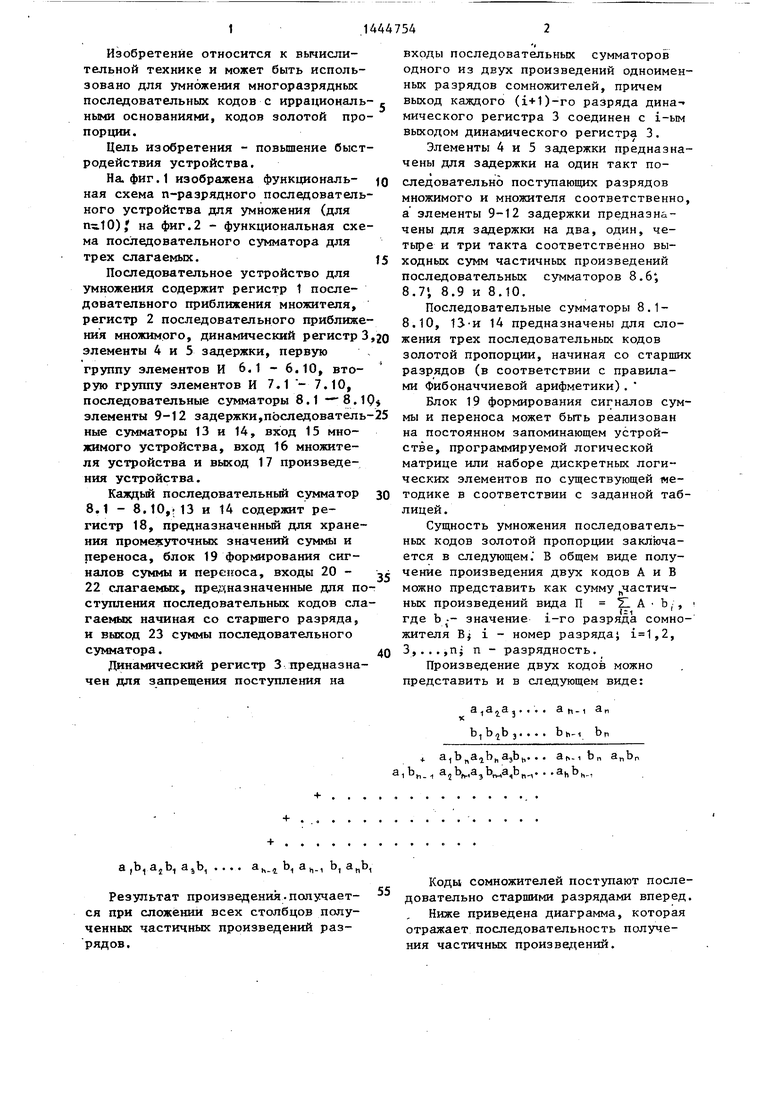

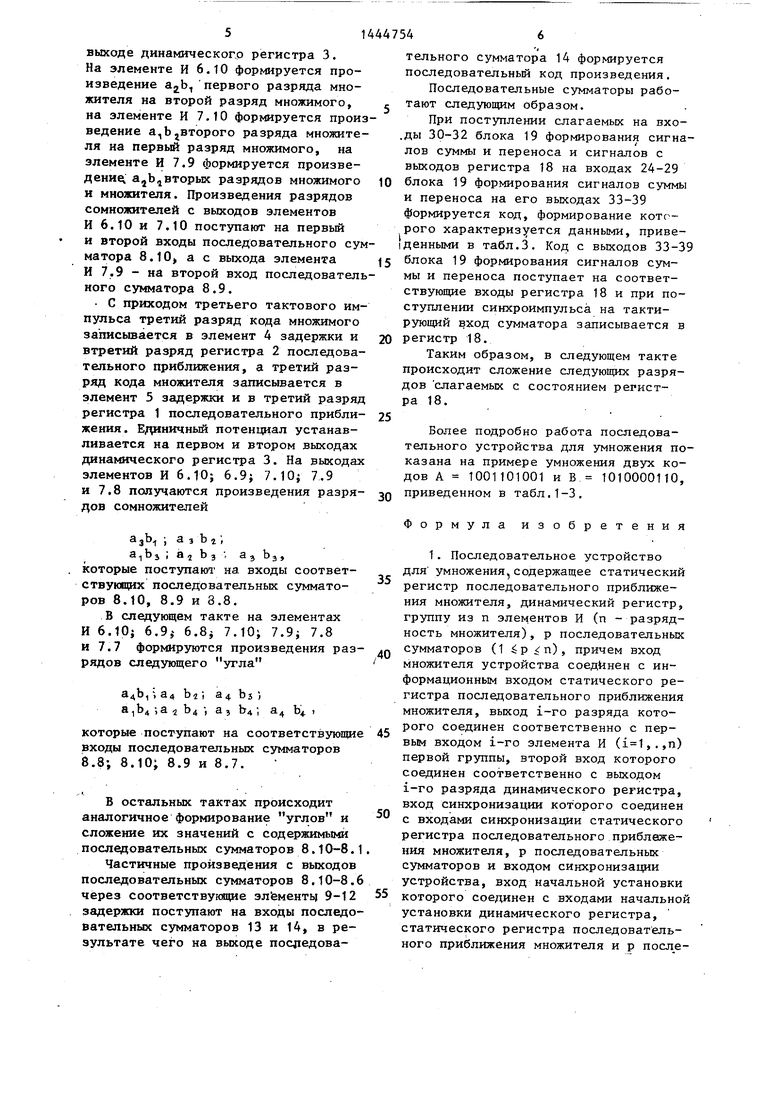

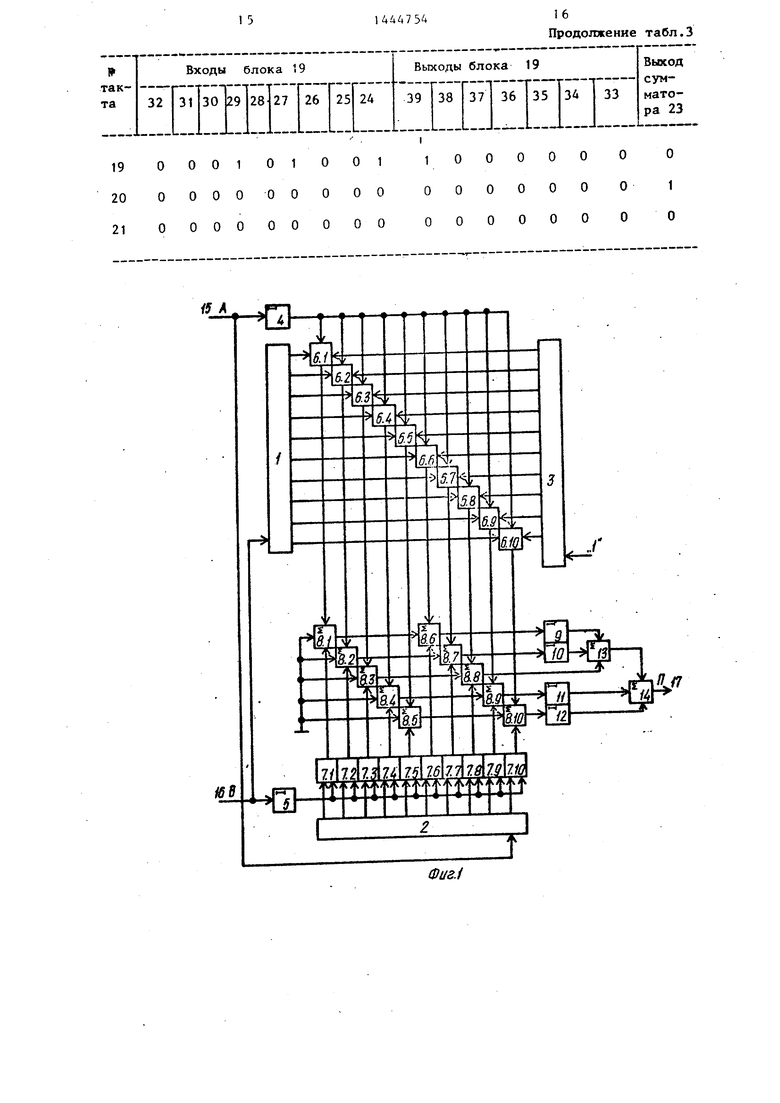

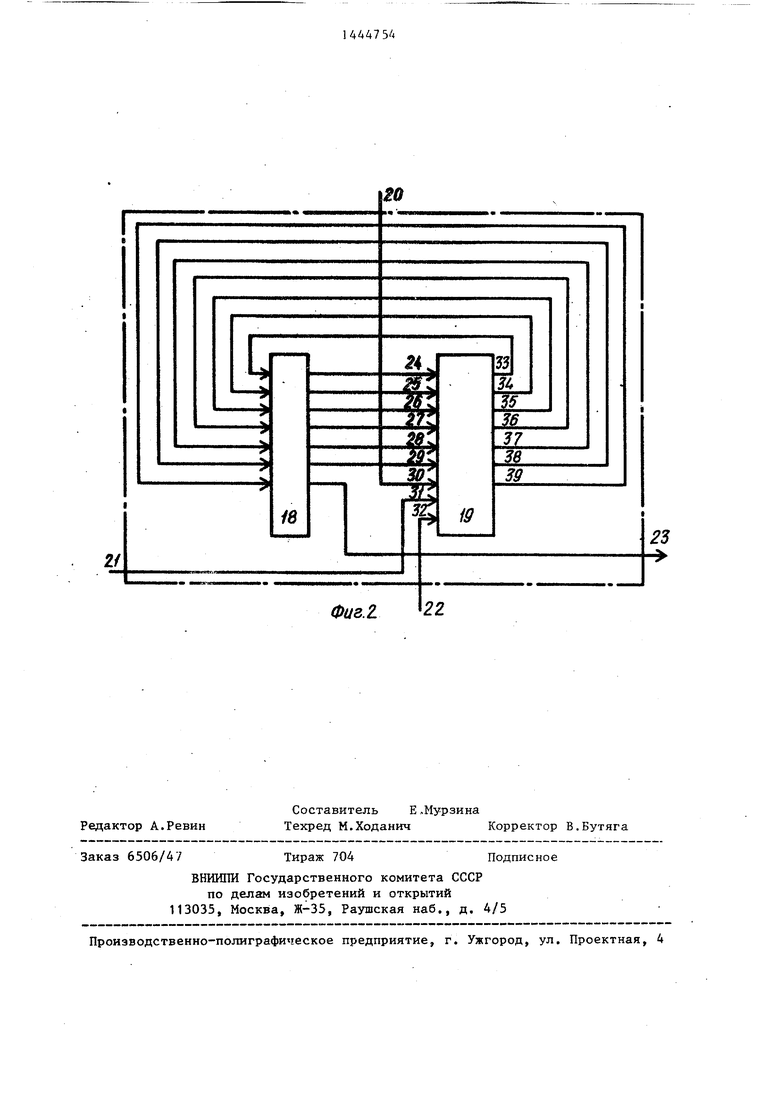

На фиг.1 изображена функциональ- ная схема п-разрядного последовательного устройства для умножения (для n:i10)f на фиг.2 - функциональная схема последовательного сумматора для трех слагаемых.

Последовательное устройство для умножения содержит регистр 1 последовательного приближения множителя.

Последовательные сумматоры 8.1- 8.10, 13-и 14 предназначены для слорегистр 2 последовательного приближения множимого, динамический регистр 3,го жения трех последовательных кодов элементы 4 и 5 задержки, первую золотой пропорции, начиная со старших группу элементов И 6.1 - 6,10, вто- разрядов (в соответствии с правила- рую группу элементов И 7.1 - 7.10, ми Фибоначчиевой арифметики). последовательные сумматоры 8.1 -S lp Блок 19 формирования сигналов сум- элементы 9-12 задержки,последователь-25 мы и переноса может быть реализован ные сумматоры 13 и 14, вход 15 множимого устройства, вход 16 множителя устройства и выход 17 произведения устройства.

Каждьй последовательньй сумматор 8.1 - 8.10,г13 и 14 содержит регистр 18, предназначенный для хранения промежуточных значений суммы и переноса, блок 19 формирования сигналов суммы и переноса, входы 20 - 22 слагаемых, предназначенные для поступления последовательных кодов слагаемых начиная со старшего разряда, и выход 23 суммы последовательного сумматора.40

Динамический регистр 3 предназначен для запрещения поступления на

30

35

на постоянном запоминающем устройстве, программируемой логической матрице или наборе дискретных логических элементов по существующей методике в соответствии с заданной таблицей.

Сущность умножения последовательных кодов золотой пропорции заключается в следующем. В общем виде получение произведения двух кодов А и В можно представить как сумму частичных произведений вида И 51 А b,, где b -- значение i-ro разряда сомножителя Bj i - номер разряда} ,2, 3,...,п- п - разрядность.

Произведение двух кодов можно представить и в следующем виде:

входы последовательных сумматоров одного из двух произведений одноименных разрядов сомножителей, причем выход каждого (i+1)-ro разряда дина-- мического регистра 3 соединен с i-ым выходом динамического регистра 3.

Элементы 4 и 5 задержки предназначены для задержки на один такт последовательно поступающих разрядов множимого и множителя соответственно, а элементы 9-12 задержки предназначены для задержки на два, один, четыре и три такта соответственно выходных сумм частичных произведений последовательных сумматоров 8.6; 8.7; 8.9 и 8.10.

Последовательные сумматоры 8.1- 8.10, 13-и 14 предназначены для сложения трех последовательных кодов золотой пропорции, начиная со старших разрядов (в соответствии с правила- ми Фибоначчиевой арифметики). Блок 19 формирования сигналов сум- мы и переноса может быть реализован

жения трех последовательных кодов золотой пропорции, начиная со старших разрядов (в соответствии с правила- ми Фибоначчиевой арифметики). Блок 19 формирования сигналов сум- мы и переноса может быть реализован

на постоянном запоминающем устройстве, программируемой логической матрице или наборе дискретных логических элементов по существующей методике в соответствии с заданной таблицей.

Сущность умножения последовательных кодов золотой пропорции заключается в следующем. В общем виде получение произведения двух кодов А и В можно представить как сумму частичных произведений вида И 51 А b,, где b -- значение i-ro разряда сомножителя Bj i - номер разряда} ,2, 3,...,п- п - разрядность.

Произведение двух кодов можно представить и в следующем виде:

а,а,а,.... а., а„

b bijbj.... bh-1 bn

. a,,,b,,... a., bn ,b., ajb,a,,bn. ...,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1989 |

|

SU1612295A1 |

| Арифметическое устройство | 1979 |

|

SU860065A1 |

| Последовательное множительное устройство | 1980 |

|

SU888110A1 |

| Последовательно-параллельное устройство для умножения чисел в дополнительном коде | 1985 |

|

SU1259252A1 |

| Устройство для умножения | 1981 |

|

SU1032453A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для умножения двух @ -разрядных чисел | 1988 |

|

SU1575174A1 |

| Устройство для умножения | 1991 |

|

SU1807481A1 |

| Устройство для умножения | 1989 |

|

SU1635176A1 |

| Последовательное множительное устройство | 1981 |

|

SU987620A1 |

Изобретение относится к области вычислительной техники и может быть использовано для умножения многоразрядных последовательных кодов с иррациональными основаниями кодов золотой пропорции. Цель изобретения - повышение быстродействия. Цель достигается путем уменьшения величины задержки и устранения зависимости задержки устройства от разрядности сомножителей за счет разбиения последовательности последовательньк сумматоров на К последовательных ветвей. 1 з.п. ф-лы, 2 ил. 2 табл. с (Л

a,b,ajb, ajb, a. Ц a., b, а„Ь,

Коды сомножителей поступают после- Результат произведения.получает- довательно старшими разрядами вперед.

ся при сложении всех столбцов полученных частичных произведений разрядов.

Ниже приведена диаграмма, которая отражает последовательность получения частичных произведений.

55555

44445

33345

22 3 4 5

1 23 4 5

где 1 - соответствующее частичное

произведение при поступлени первых разрядов сомно-.ште- лей;

2 - соответствующие частичные произведения при поступлении вторьк разрядов сомножителей;n - соответствующие частичные

произведения при поступлени п-х разрядов сомножителей. Таким образом, за n тактов получаются все частичные произведения i-x разрядов сомножителей.

Дпя сложения n получаемых углов частичных произведений необходимо иметь n последовательно соединенных последовательных сумматора. На первые входы сумматоров поступают частичные произведения одной стороны угла, на вторые входы - другой стороны угла. На третьи входы послдовательных сумматоров поступают выходы сумм из предьщущего суммато- ра. С каждым тактом (по мере поступления очередньк разрядов слагаемых) происходит одновременный сдвиг промежуточных сумм последовательных сумматоров, причем n последовательны сумматоров разбиты на к последовательных ветвей. Выходы первых к сумматоров поступают на последовательный сумматор 7ЩЯ к слагаемых, причем выход каждого i-ro последовательного сумматора (i к) задерживается на (i-1) такт.

На выходе последовательного сумматора для к слагаемых формируется последовательный код результата произведения .

Последовательное устройство для умножения работает следующим образом.

n-1 n

n-ln

n-ln

n-ln

n-1n

0

5

0

5

0 5

0

5

На вход начальной установки устройства поступает единичньш сигнал, который устанавливает регистры 1-3 и последовательные сумматоры 8.1- 8.10, 13 и 14 в нулевое состояние. После снятия сигнала начальной установки на входы 15 и 16 множимого и множителя поступают последовательные коды сомножителей старшими разрядами вперед.

С приходом первого тактового им- пульса старшие разряды множимого записываются в элемент 4 задержки и в первьм разряд регистра 2 последовательного приближения множимого, а множителя - в элемент 5 задержки и в первый разряд регистра 1 последовательного приближения множителя. В первый разряд динамического регистра 3 записывается единица. Выход каждого (i+1)-ro разряда динамического регистра 3 соединен с i-ым выходом динамического регистра 3. На входы элементов И 6.10 и 7.10 поступают значения старших разрядов множимого и множителя. На третьем входе эле- мента И 6.10 присутствует нулевой потенциал с первого выхода динамического регистра 3. На второй вход последовательного сумматора 8.10 поступает значение произведения старших разрядов а-,Ь, с выхода элемента И 7.10.

С приходом второго тактового импульса второй разряд кода множимого записывается в элемент 4 задержки и во второй разряд регистра 2 последовательного приближения, а второй разряд кода множителя записывается в элемент 5 задежки и во второй разряд регистра 1 последовательного приближения множителя. Единичный потенциал устанавливается на первом

выходе динамического регистра 3. На элементе И 6.10 формируется произведение , первого разряда множителя на второй разряд множимого, на элементе И 7.10 формируется произведение a,bjBToporo разряда множителя на первый разряд множимого, на элементе И 7.9 формируется произведена аjb,вторых разрядов множимого и множителя. Произведения разрядов сомножителей с выходов элементов И 6.10 и 7.10 поступают на первьй и второй входы последовательного сумматора 8.10, а с выхода элемента И 7.9 - на второй вход последовательного сумматора 8.9.

С приходом третьего тактового импульса третий разряд кода множимого записьгаается в элемент 4 задержки и втретий разряд регистра 2 последовательного приближения, а третий разряд кода множителя записывается в элемент 5 задержки и в третий разряд регистра 1 последовательного прибли- жения. Единичный потенциал устанавливается на первом и втором выходах динамического регистра 3. На выходах элементов И 6.10; 6.9; 7.10; 7,9 и 7.8 получаются произведения разря- дов сомножителей

азЦ ; а 3 b 4 , J ; а j b 3

г Ьз,

которые поступают на входы соответствующих последовательных сумматоров 8.10, 8.9 и 8.8.

В следующем такте на элементах И 6.10; 6.9,- 6.8; 7.10; 7.9; 7.8 и 7.7 формируются произведения разрядов следующего угла

адЬ, , а4 Ь« ; а Ъ ,а 2 Ь4 , а 3 Ьл ;

Ь

которые поступают на соответствующие входы последовательных сумматоров 8.8; 8.10; 8.9 и 8.7.

В остальных тактах происходит аналогичное формирование углов и сложение их значений с содержимыми последовательных сумматоров 8.10-8.1.

Частичные произведения с выходов последовательных сумматоров 8.10-8.6 через соответствуняцие элементы 9-12 задержки поступают на входы последовательных сумматоров 13 и 14, в результате чего на выходе пос41едова5

0 5 о

5

0

5

0

5

тельного сумматора 14 формируется последовательный код произведения.

Последовательные сумматоры работают следующим образом.

При поступлении слагаемых на вхо- .ды 30-32 блока 19 формирования сигналов суммы и переноса и сигналов с выходов регистра 18 на входах 24-29 блока 19 формирования сигналов суммы и переноса на его выходах 33-39 формируется код, формирование которого характеризуется данными, приведенными в табл.3. Код с выходов 33-39 блока 19 формирования сигналов суммы и переноса поступает на соответствующие входы регистра 18 и при поступлении синхроимпульса на тактирующий вход сумматора записывается в регистр 18.

Таким образом, в следующем такте происходит сложение следующих разрядов слагаемых с состоянием регистра 18.

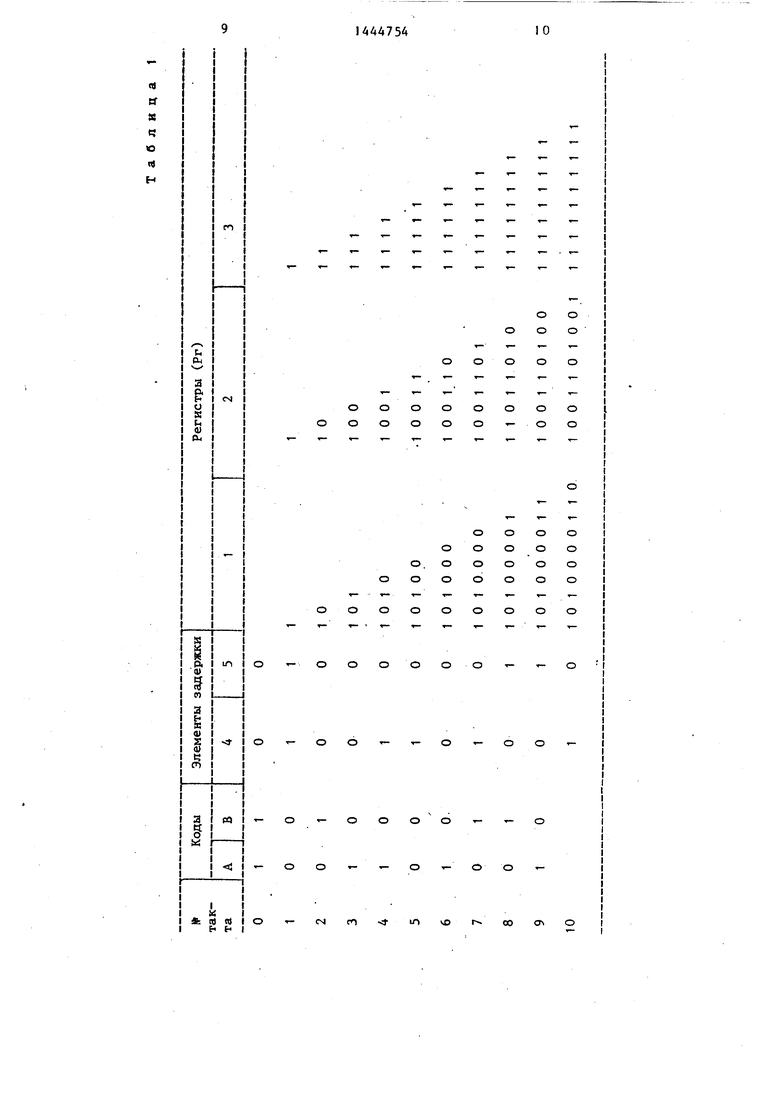

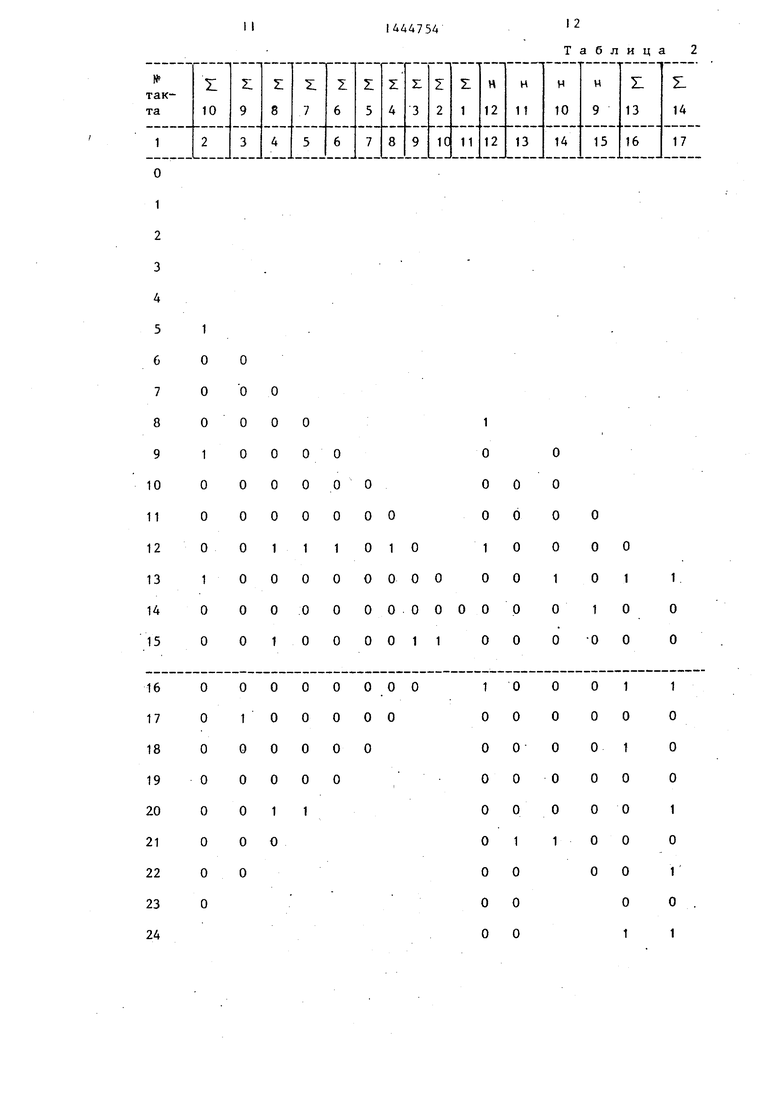

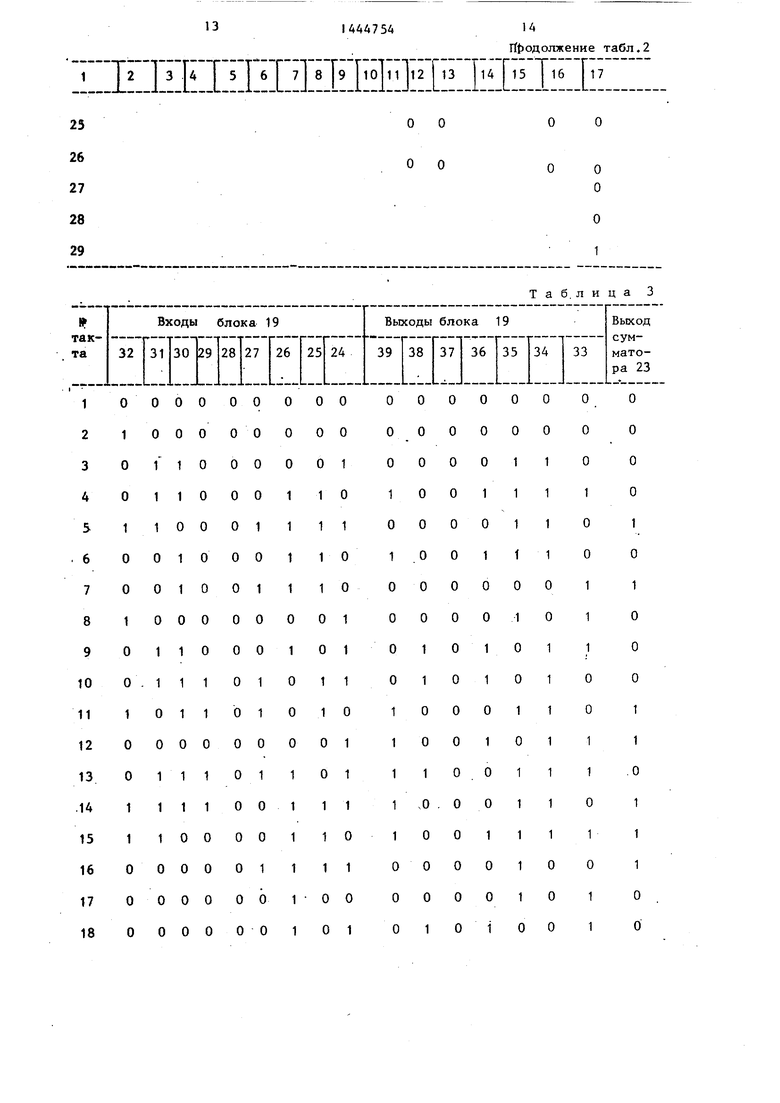

Более подробно работа последовательного устройства для умножения показана на примере умножения двух кодов А 1001101001 и В 1010000110, приведенном в табл.1-3.

Формула изобретения

довательных сумматоров, о т л и ч а- ю щ е е с и тем, что, с целью повышения быстродействия, в него введены статический регистр последовательного приближения множимого,вторая группа из п элементов И, шесть элементов задержки и п-р+2 последовательных сумматоров, причем вход множимого устройства соединен с входом первого элемента задержки и информационным входом статического регистра последовательного приближения множимого, выход i-ro разряда которого соединен соответственно с пер- вым входом i-ro элемента И второй группы, второй вход которого через второй элемент задержки соединен с входом множителя устройства, вход логической единицы которого соединен с информационным входом динамическог регистра, выход первого элемента задержки соединен, с третьим входом каждого i-ro элемента И первой группы, выход которого соединен соответст- венно с первым информационным входом i-ro последовательного сумматора, второй информационньй вход кото- рогр соединен соответственно с выходом i-ro элемента И второй группы, выходы первого и второго последовательных сумматоров соответственно через третий и четвертьй элементы задержки соединены с первым и вторым информационными входами (п+1)-го по- следовательного сумматора, третий информационный вход которого соединен с выходом (п-«-2)-го последовательного сумматора, первьш и второй информационные входы которого соединены со- ответственно с выходами пятого и шестого элементов задержки, входы которых соединены соответственно с выходами четвертого и пятого последовательных сумматоров, выход третьего последовательного сумматора соединен с третьим информационным входом (п+2)-го последовательного сумматоЭ4 8

ра, выход j-ro последовательного сумматора (j-6,...,n) соединен соответственно с третьим информационным входом (j-5)-ro последовательного сумматора, третий информационный вхо каждого j-ro последовательного сумматора соединен с входом логического нуля устройства, выход результата которого соединен с выходом (п-ь1)-го последовательного сумматора, входы синхронизации статического регистра последовательного приближения множимого и каждого из п-р+2 последовательных сумматоров соединены с входо синхро шзации устройства, вход начальной установки которого соединен с входами начальной установки статического регистра последовательного приближения множимого и каждого из п-р+2 последовательных сумматоров.

1

О О О 1 О О

о 1

о о

о о о

000 000 000 000

о 1 1

000

о о о

о 1

о

о о о

000

1 010

о 0000

о 000000

00011 о

Таблица

о о о о 1

о о

о

оо

о1

1о

оо

1 о о

13

I 444754

14 Itfодолжение табл.2

19 000101001100000 ОО

20 000000000 000000 о 1

21 000000000000000 00

Фиг.

22

| Устройство для умножения | 1983 |

|

SU1130859A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1983 |

|

SU1200280A1 |

| Стахов А.П | |||

| Коды золотой пропорции | |||

| М.: Радио и связь, 1984 | |||

| Титцё У., Шейк К | |||

| Полупроводниковая схемотехника, М.: Мир, 1982, с | |||

| Способ изготовления фасонных резцов для зуборезных фрез | 1921 |

|

SU318A1 |

| Последовательное устройство для умножения | 1985 |

|

SU1262482A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-12-15—Публикация

1987-07-06—Подача