(Л

со

00

ел

Изобретение относится к автоматике и технике связи и может быть использовано в системах передачи информации.

Цель изобретения - повьт1ение помехозащищенности.

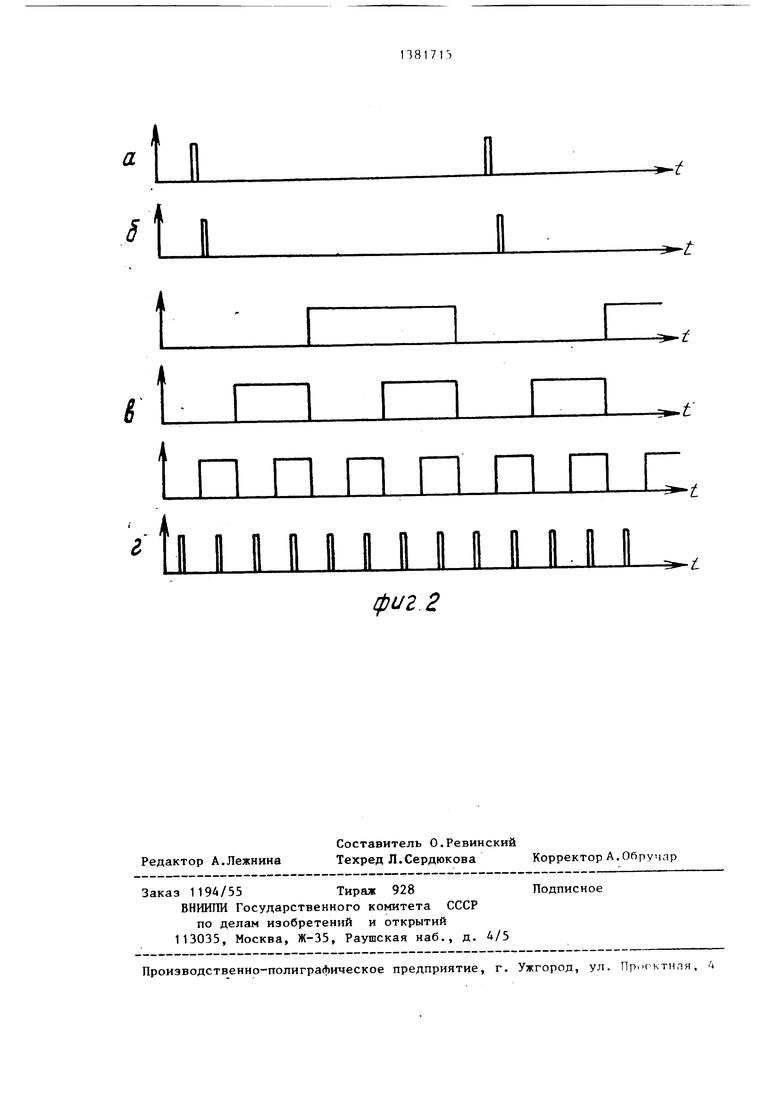

На фиг. 1 представлена функциональная схема дельта-кодера; на фиг. 2 - изображены временные диаг- раммы сигналов на выходах блока синхронизации.

Дельта-кодер содержит компаратор 1, триггер 2, первый и второй регистры 3 и 4 сдвига, элемент ИЛИ 5,пер- вый,второй и третий элементы И 6,7 и 8, мультиплексор 9, бдок 10 синхронизации, счетчик 11, блок 12 постоянной памяти, первый и второй буферные регистры 13 и 14, первый и второй арифметико-логические блоки 15 и 16, делитель 17, цифроаналого- вый преобразователь (ЦАП) 18, дешифратор 19, блок 20 мультиплексоров, вход 21 и выход 22.

Дельта-кодер работает следующим образом.

В результате сравнения входного сигнала U(t) с сигналом аппроксимации и (t) с выхода ЦАП 18 на вы- ходе компаратора 1 образуется двоичный сигнал, который с приходом очередных тактовых импульсов частотой f с первого выхода блока 10 синхронизации (фиг. 2с) записывается в триггер 2 и регистр 3 сдвига, последовательно продвигается по разрядам данных блоков и анализируется на наличие пачек однотипных символов при помощи элементов И 6 и 7 и эле- мента ИЛИ 5. В случае, когда сигнал Y(t) на выходе триггера 2 содержит пачки однотипных символов, на выходе элемента ИЛИ 5 появляются единичные импульсы.

Сигнал с выхода элемента ИЛИ 5 с приходом импульсов тактовой последовательности записывается в регистр 4 сдвига и по аналогии с сигналом в регистре 3 сдвига последова- тельно смещается на один разряд с приходом каждого импульса с первого выхода блока 10 синхронизации.

Таким образом, во втором регистре 4 сдвига в любой момент времени на- ходится фрагмент цифрового сигнала Y(t), полученного из выходного сигнала Y(t) кодера и отображающего nJipTHocTb однотипных символов в пачках сигнала Y(t) на интервале времени tp, cooтвeтcтвyюп eм длине (разрядности) второго регистра 4 сдвига. Если разрядность регистра 4 сдвига равна 1, то длительность данного интервала ut„ определяется как dty 1 -Т(., где Тс

период импульсной последовательности стробирующЕЙ кодер.

Записанный в регистр 4 сдвига фрагмент цифрового сигнала Y(t) в каждом такте стробирующей последовательности анализируется при помощи мультиплексора 9 и счетчика 11. Анализ происходит следующим образом. В промежутках между импульсами сигнала тактовой частоты f на управляющие входы мультиплексора 9 пос тупагот быстроизменяющиеся неповторяющиеся комбинации сигналов с третьих выходов блока 10 синхронизации (фиг. 2в). Каждой комбинацией сииво- лов на управляющих входах мультиплексора 9 один из его информационных входов проключается на выход. Таким образом, за один такт стробирующей последовательности f, все выходы регистра 4 сдвига поочередно подключаются через мультиплексор 9 и трети элемент И 8,на второй вход которого короткий единичный импульс поступает в момент опроса каждого разряда регистра 4 (фиг, 2г), на счетный вход счетчика 11.На счетчик 11 в течение каждого такта стробирутощей последовательности поступает столько единичных импульсов, сколько единичных символов записано в регистре 4 сдвига,Так как число единичных символов в любой момент времени пропорционально плотности цифрового сигнала Y(t) на анализируемом интервале fltq, то двоичное число на выходе счетчика 11 в конце каждого интервала Тр 1/f также пропорциональн

числу однотипных симводов в пачках цифрового ДМ-сигнала Y(t) на интервале tg. Следовательно данное число может быть использовано для установки оптимального шага квантования, с которым следует обрабатывать текущий фрагмент входного сигнала.

С каждым тактом стробирующей последовательности ff число с выхода счетчика 11 переписывается в первый буферный регистр 13 и поступает на

управляющие входы блока 20 мультн- плексорпв, проключая соответствующий шаг квантования (в виде двоичного числа) из блока 12 постоянной памяти на первую группу входов первого арифметико-логического блока 15. Счетчик 11 в этот момент устанавливается в исходное состояние импул, сом по установочному входу (фиг. 26)

Лмпульсные последовательности на первом и втором выходах блока 10 синхронизации отличаются одна от другой небольшим фазовым сдвигом,что необходимо для согласованной работы регистрового оборудования (триггер 2 регистры 3 и Д сдвига) и блоков, анализирующих текущий фрагмент цифрового сигнала (счетчик 11, первый буферный регистр 13). Короткие импульсы на четвертом выходе блока 10 поступают в течение опроса каждого разряда регистра 4 сдвига, что необходимо для нормальной работы счетчика 11 в случае, когда в регистре 4 сдвига записаны единичные импульсы в соседних разрядах.

Восстачовление аппроксимирующего сигнала U(t) в дельта-кодере осуществляется при помощи первого и второго арифметико-логического блоков 15 и 16, второго буферного регистра 14, делителя 17, дешифратора 19 и цифроаналогового преобразователя 18, Первый арифметико-логический блок 15 в каждом такте работы осуществляет основную операцию по формированию аппроксимирующего сигнала, сложение или вычитание двоичного числа, отображающего шаг квантования, с двоичным числом, полученным в результате аналогичной операции в предыдущем такте, хранящимся во втором буферном регистре 14 и отоб.ражающим фактически аппроксимирующий сигнал U (t). При помощи второго арифметико-логи ческого блока 16 осуществляется дополнительная операимя с числом, отображающим сигнал U(t). Сущность данной операции сводится к уменьшению (по абсолютному значению) двоичного числа на выходе первого арифметико-логического блока 15 на некоторую сравнительно небольшую величину, которая определяется числом, хранящимся во втором буферном регистре 14.Данная операция выполняется при помощи второго арифметико- логического блока 16, на вторую

0

5

0

5

0

5

0

5

группу входов которого заводится небольшая часть числа, хранящегося во втором буферном регистре 14, полученная при помощи делителя 17. Управление вторым арифметико-логическим блоком 16 осуществляется при помощи дешифратора 19, который анализирует двоичное число, записанное во второй буферный регистр 14, ив зависимости от знака аппроксимирующего сигнала U(t), отображенного данным числом, выдает на своем выходе 1 или О. В случае, когда U(t)7 О, потенциал на выходе дешифратора 19 соответствует О, в результате чего второй арифметико-логический блок 16 производит операцию вычитания. В случае, когда U(t) г О,второй арифметико-логический блок 16 производит операцию сложения.

Второй арифметико-логический блок 16, дешифратор 19 и делитель 17 образуют дополнительную петлю отрицательной обратной связи, оказывающую стабилизирующее влияние на работу дельта-кодера. Если выбрать коэффициент деления делителя 17 достаточно большим (таким,чтобы на вторую группу входов второго арифметико-логического блока 16 поступала очень малая часть числа, хранящегося во втором буферном регистре 14), то введение блоков 16 и 17 не окажет существенного влияния на качество восстанавливаемого сигнала U (t) в силу его детерминированности. Однако при этом значительно повысится помехозащищенность устройства, так как результаты воздействия на блок восстановления аппроксимирующего сигнала случайных (недерминированных) помех и сбоев будут постепенно сводиться к нулю по цепочке: второй арифметико-логический блок 16 - второй буферный регистр 14 --делитель 17,а не накапливаться во втором буферном регистре 15.

Таким образом, значительно повышается помехоустойчивость дельта-ко- дера,

В предлагаемом дельта-кодере по сравнению с протипом отсутствуют цепи формирования интервала анализа цифрового сигнала Y(t), так как эквивалентный интервал анализа задается аппаратурно , при помощи регистра 4 сдвига. При этом автоматически отпадает необходимость в дополнительной синхронизации интервалов анализа и исключается возможность сбоев в работе канала передачи из-за рассин- хронизации кодера и декодера при вы- соком уровне шумов в канале.

Формула изобретени Дельта-кодер,, содержащий компаратор, перйый вход которого является входом дельта-кодера,выход компаратора соединен с информационным входом триггера, выход которого подключен к информационному входу первого регистра сдвига, управляющему входу первого арифметико-логического блока и является выходом дельта-кодера, прямые и инверсные выходы разрядов первого регистра сдвига подключены к входам соответственно первого и второго элементов И, выходы которых соединены с входами элемента ИЛИ, третий элемент И, счетчик, первый буферный регистр, дешифратор,блок постоянной памяти, выходы которого подключены к информационным входам блока мультиплексоров, выходы которого подключены к первым информационным входам первого арифметико-логического блока, второй буферный регистр, выходы которого подключены к вторым информационным входам первого арифметико-логического блока и входам цифроаналогового преобразователя, выход которого соединен с вто

рым входом компаратора,входы синхронизации триггера и первого регистра сдвига объединены, отличаю- щ и и с я тем,что,с целью повьшения помехозащищенности, в дельта-кодер

0 5 О

5

введены мультиплексор, делитель, второй арифметико-логический блок, второй регистр сдвига и блок синхро- низа1Ц1И, первый выход которого подключен к объединенным входам синхронизации триггера и первого регистра сдвига и входу синхронизации второго регистра сдвига, выход элемента ИЛИ соединен с информационным входом второго регистра сдвига, выходы которого подключены к информационным входам мультиплексора, выход которого соединен с первым входом третьего элемента И, второй выход блока синхронизации подключен к установочному входу счетчика и стробирующим входам буферных регистров и делителя, информационные входы которого объединены с входами дешифратора и подключены к выходам второго буферного регистра, третьи выходы блока синхронизации подключены к управляющим входам мультиплексора, четвертый выход блока синхронизации соединен с вторым входом третьего элемента И,выход которо го подключен к счетному входу счетчика, выходы которого соединены с информационными входами первого буферного регистра, выходы которого подключены к управляющим входам блока мультиплексоров, выходы первого арифметико-логического блока,выходы делителя и выход дешифратора подключены соответственно к первым и вторым информационным и управляющему входам второго арифметико-логического блока, выходы которого соединены с информационными входами второго буферного регистра.

A

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-кодек | 1987 |

|

SU1427572A1 |

| Дельта-кодер | 1984 |

|

SU1197088A1 |

| Дельта-кодер | 1987 |

|

SU1429321A1 |

| Дельта-кодер | 1986 |

|

SU1381716A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Дельта-кодер | 1985 |

|

SU1290529A1 |

| Дельта-кодер | 1988 |

|

SU1646056A1 |

| Дельта-кодер | 1989 |

|

SU1612375A1 |

| Дельта-кодер | 1987 |

|

SU1441482A1 |

| Устройство связи с дельта-модуляцией | 1986 |

|

SU1365364A1 |

Изобретение относится к автоматике и технике связи. Его использование в системах передачи информации обеспечивает повьппение помехозащищенности. Дельта-кодер содержит компаратор 1, триггер 2, регистр 3 сдвига, элемент ИЛИ 5, элементы И 6-8, счетчик 11,блок 12 постоянной памяти, буферные регистры 13, 14, арифметико-логический блок 15, цифро- аналоговый преобразователь 18,дешифратор 19 и блок 20 мультиплексоров. Введение ре гистра-4 сдвига, мультиплексора 9, блока 10 синхронизации, арифметико-логического блока 16 и делителя 17 обеспечивает сведение к нулю воздействия случайных помех и сбоев на работу дельта-кодера. 2 ил.

.t

фиг 2

| Дельта-кодер | 1984 |

|

SU1197088A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Дельта-кодер | 1985 |

|

SU1290529A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-03-15—Публикация

1986-06-10—Подача