Изобретение относится к вычислительной технике и может быть использовано в системах для сопряжения устройств, осуществляющих обмен информацией.

Цель изобретения - расширение области применения за счет обеспечения обмена информацией между разноскорост ными, а также синхронными и асинхронными источником и приемником информации.

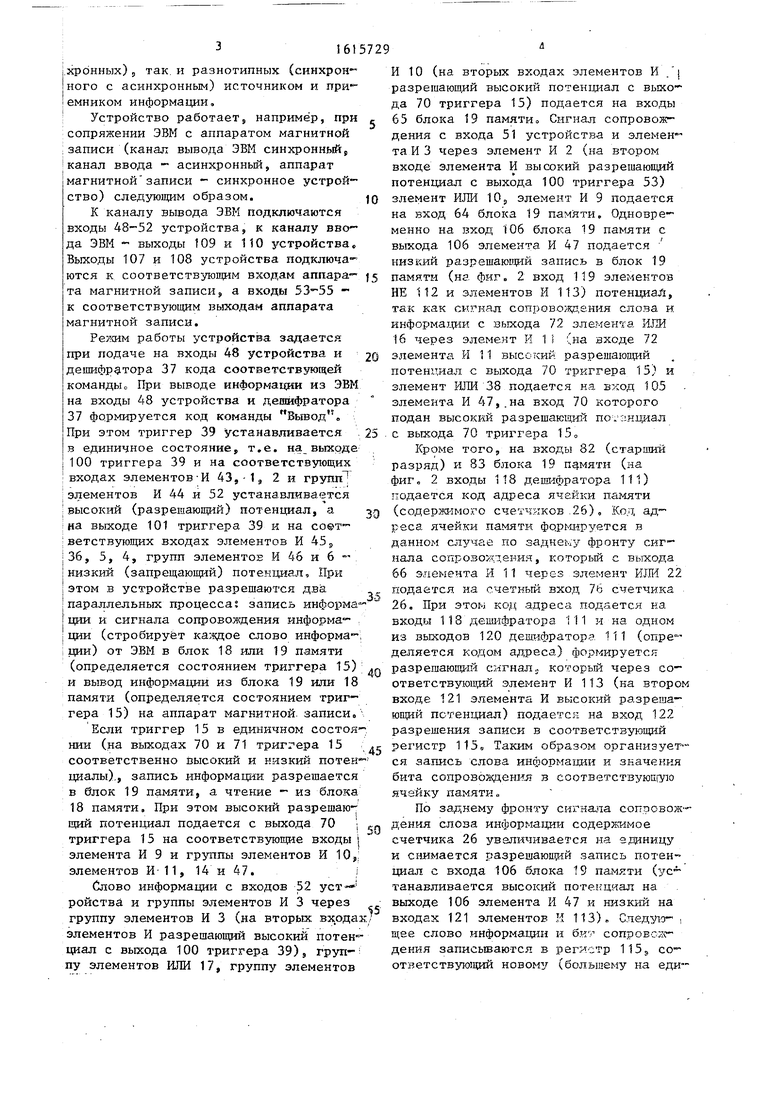

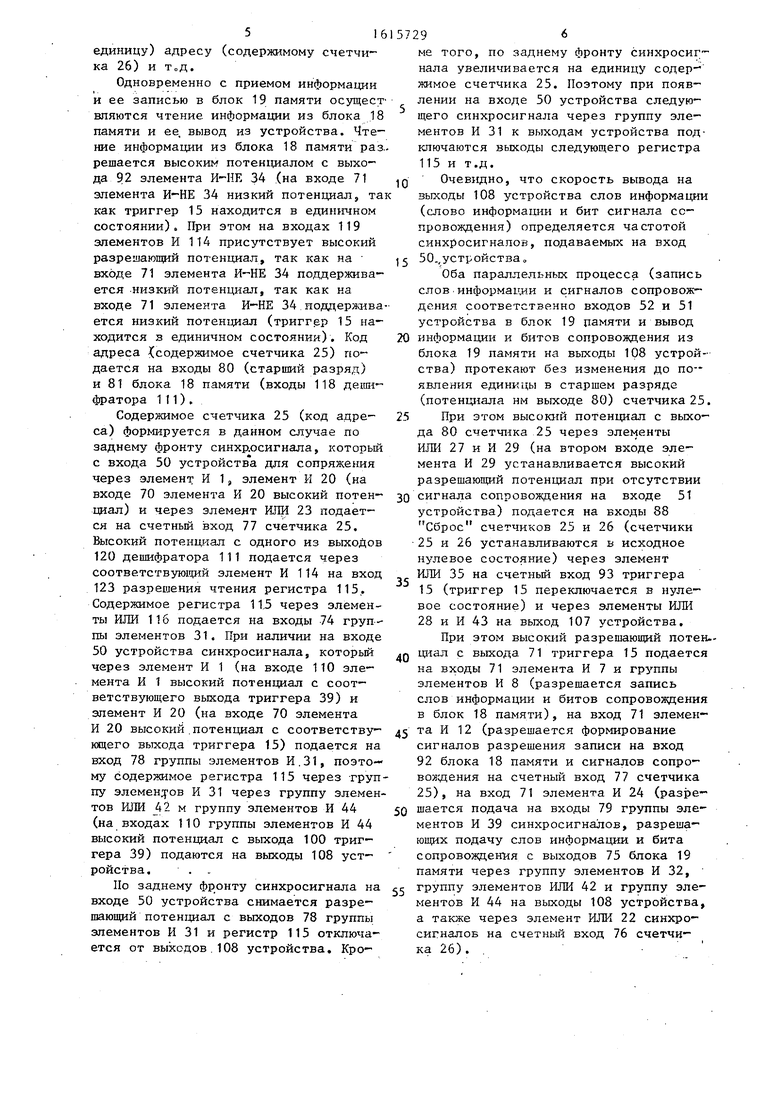

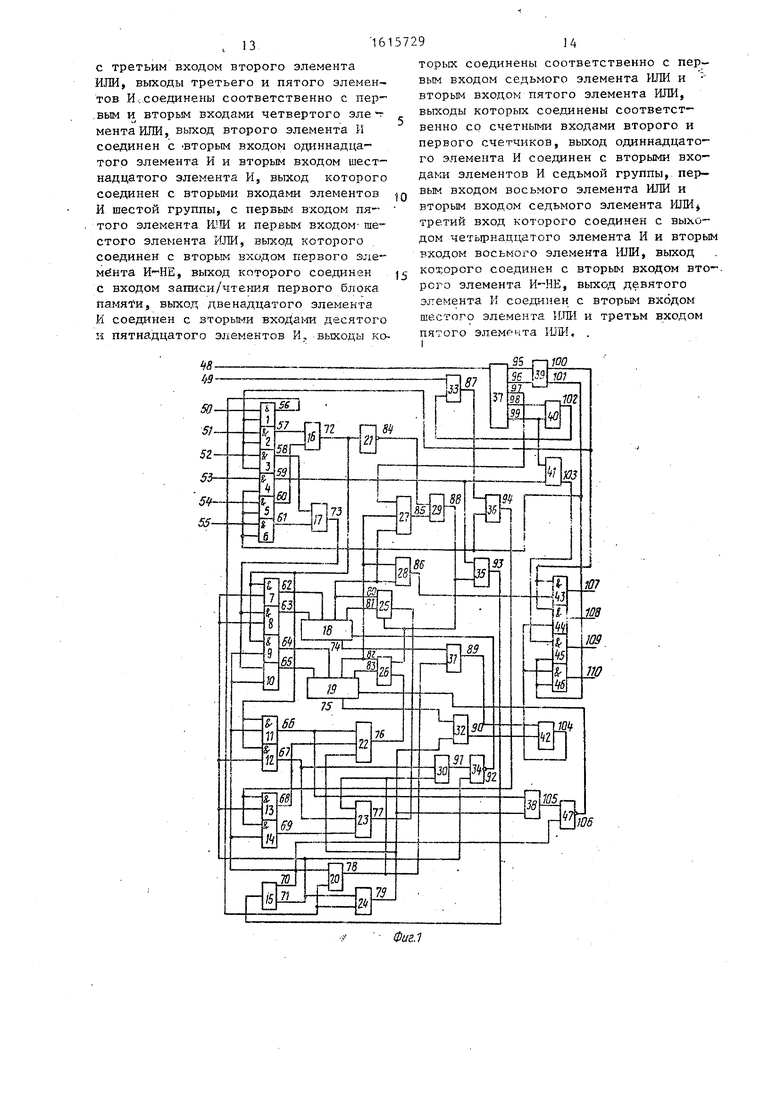

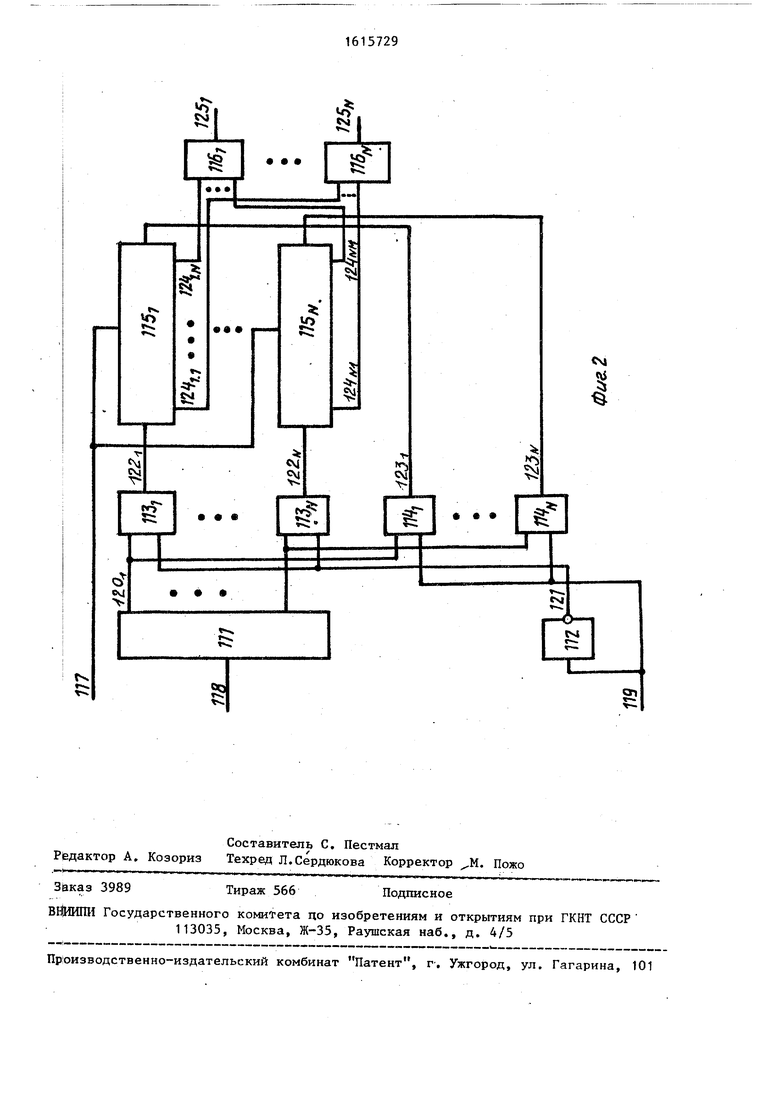

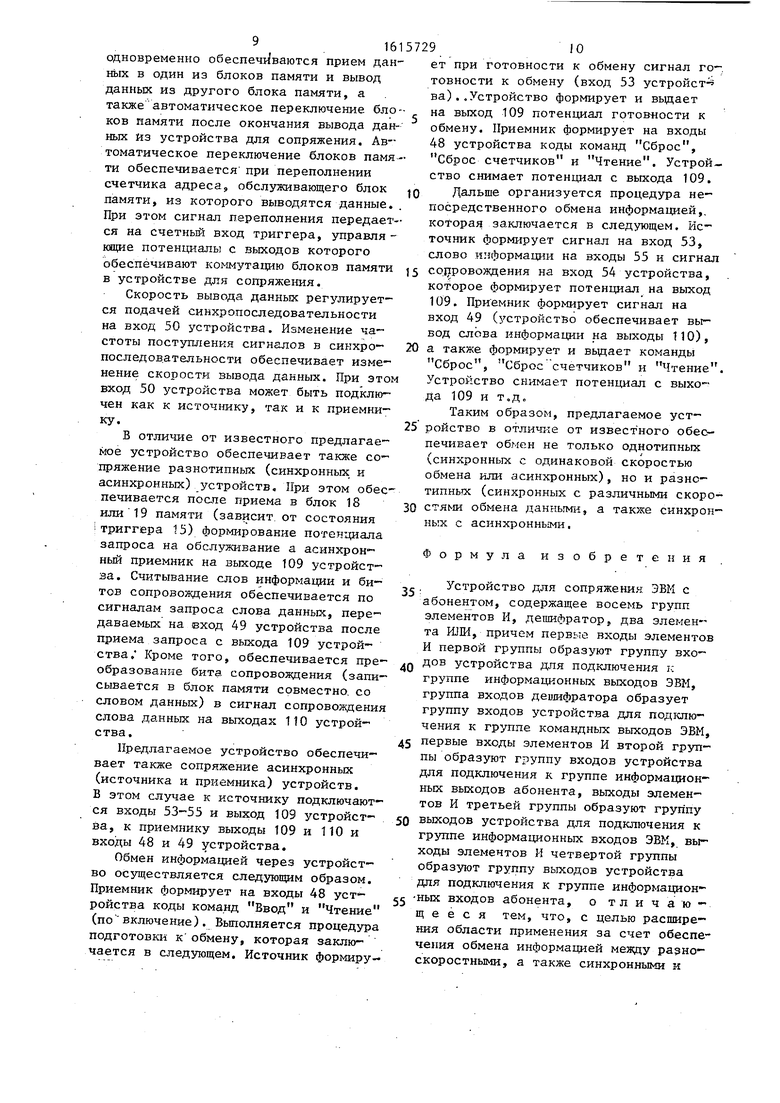

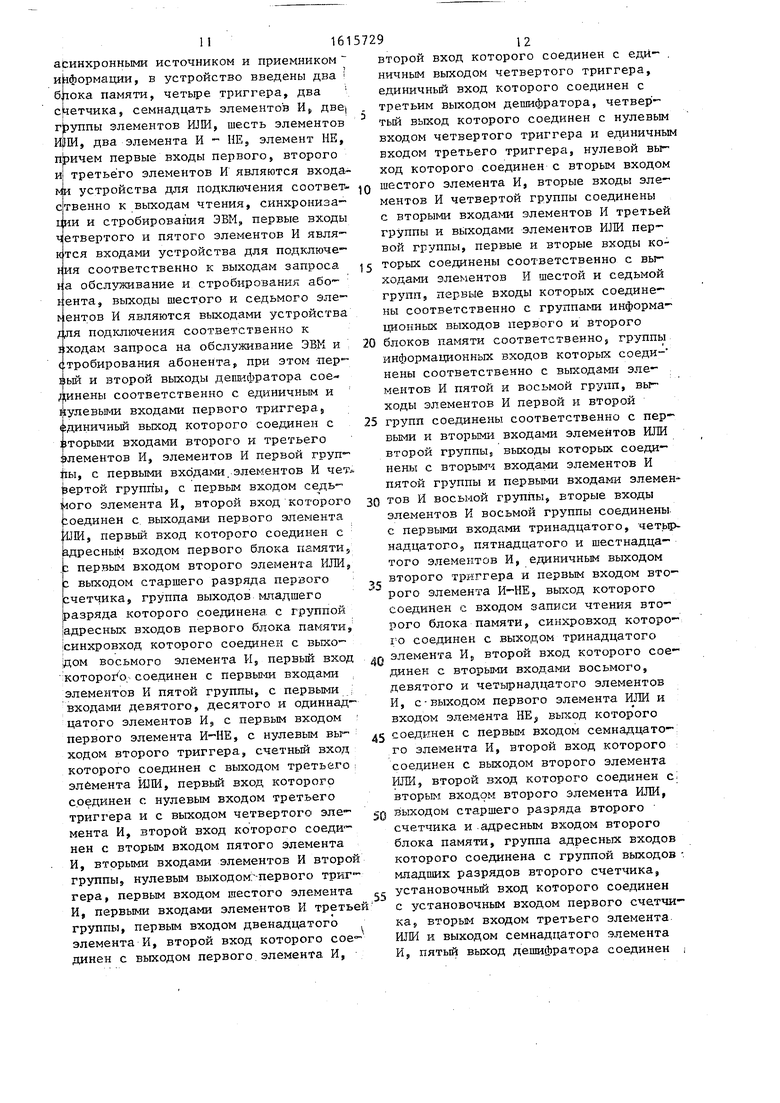

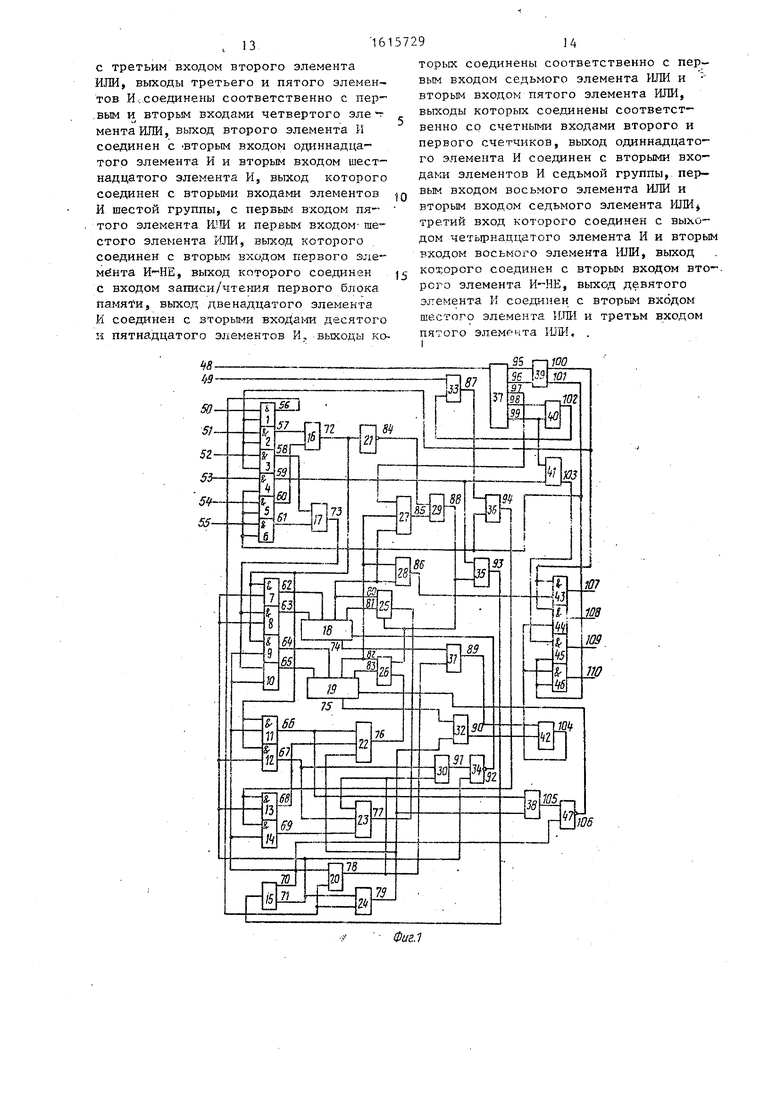

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - схема блока памяти..

Устройство Хфиг„ 1) содержит элементы И 1 и 2, группу элементов ИЗ, элементы И 4 и 5, группу элементов И 6, элемент И 7, группу элементов И 8, элемент И 9, группу элементов . И 10, элементы И 11-14, триггер 15, элемент ИЛИ 16, вторую группу элемен-,. тов ИЛИ 17, блоки 18 и 19 памяти.

элемент И 20, элемент НЕ 21, элементы ИЛИ 22 и 23, И 24, счетчики 25 и 26, .элементы ИЛИ 27 и 28, И 29, ИЛИ 30, группы элементов И 31 и 32, элементы И 33, И-НЕ 34, ИЛИ 35, И 36, дешифра- .тор 37, элемент ИЛИ 38, триггеры 39- 41, первую группу элементов ИЛИ 42, элемент И 43, группу элементов И 44, элемент И 45, группу элементов И 46, элемент И-НЕ 47, входы 48-55, внутренние входы и выходы 56-106 и выходы 107-110.

. . 18 и 19 памяти содержат (фиг. 2) дешифратор Ш; элемент НЕ 112, группы элементов И 113 и 114, группу регистров из, группу элемен- .тов ШШ 116, входы 117-119, внутренние входы и выходы 120-124 и выходы .125.

Устройство может использоваться при организации обмена информацией как однотипных (синхронных или асино:

ел ю

ico

3161

хронных)5 так, и разнотипных (синхронного с асинхронным) источником и при- емником информации.

Устройство работает, например, при сопряжении ЭВМ с аппаратом магнитной записи (канал вывода ЭВМ синхронный, канал ввода асинхронный, аппарат магнитной записи - синхронное устройство) следующим образом.

К каналу вывода ЭВМ подключаются входы 48-52 устройства, к каналу ввода ЭВМ - выходы 109 и 110 устройства, Выходы 107 и 108 устройства подключа- ются к соответствзпощим входам аппара- та магнитной записи, а входы - к соответствующим выходам аппарата магнитной записи.

Режим работы устройства задается при подаче на входы 48 устройства и дешифратора 37 кода соответствующей команды При выводе информации из ЭВМ на входы 48 устройства и дешифратора 37 формируется код команды Вьюод ( При этом триггер 39 устанавливается в единичное состояние, т.е. на выходе 100 триггера 39 и на соответствующих входах элементов-И 43, - 1 2 и групп элементов И 44 и 52 устанавливается высокий (разрешающий) потенциал, а на выходе 101 триггера 39 и на со©т- ветствующих входах элементов И 45 36, 5, 4, групп элементов И 46 и 6 - низкий (запрещающий) потенциал. При этом в устройстве разрешаются два параллельных процесса; запись информа ции и сигнала сопровождения информа- ции (стробируёт ка;«дое слово информации) от ЭВМ в блок 18 или 19 памяти

40

(определяется состоянием триггера 15) и вывод информации из блока 19 или 18 памяти (определяется состоянием триггера 15) на аппарат магнитной, записи

Если триггер 15 в единичном состоя-. НИИ (на выходах 70 и 71 триг:гера 15 .с соответственно высокий и низкий потен циалы),, запись информации разрешается в блок 19 памяти, а чтение - из блока 18 памяти. При этом высокий разрешающий потенциал подается с выхода 70 триггера 15 на соответствзтащие входы элемента И 9 и группы элементов И 10, элементов И-11, 14 и 47.i

Слово информации с входов 52 ройства и группы элементов И 3 через группу элементов И 3 (на вторых вхрдак/ элементов И разрешающий высокий потен - циал с выхода 100 триггера 39), груп- пу элементов ИЛИ 17, группу элементов

50

, 0

15

20 , 25 о , ,

35

40

. .с

к/ -

50

И 10 (на вторых входах элементов И . | paзpeшaюш й высокий потенциал с выхо- да 70 триггера 15) подается на входы

65блока 19 памятио Сигнал сопровождения с входа 51 устройства и элемен та И 3 через элемент И 2 (на втором входе элемента И высокий разрешающий потенциал с выхода 100 триггера 53) элемент ИЛИ 10, элемент И 9 подается на вход 64 блока 19 памяти. Одновременно на вход 106 блока 19 памяти с выхода 106 элемента И 47 подается низкий разрешающий запись в блок 19 памяти (на фиг, 2 вход 119 элементов НЕ 112 и элементов И 113) потенциал, так как сигнал соп1 ово кдения слова и информации с выхода 72 элемента ИЛИ 16 через элемент И 11 (на входе 72 элементс1 И 11 высо7 :ий разрешающий потенциа.т; с выхода 70 триггера 15) и элемент ШЖ 38 подается на вход 105 элемента И 47,.на вход 70 которого подан высокий разрешаю1г(ий по анциал

с выхода 70 триггера 15

Кроме того, на входы 82 (старший разряд) и 83 блока 19 памяти (на фиг„ 2 входы 118 дешифратора 111) подается код адреса ячейки памяти (содержимого счетчиков .26), Код адреса ячейки памяти форг-сируется в данном случае по заднему фронту сигнала сопровожл,евия, которьй с. выхода

66элемента И 11 через элемент ИШ 22 подается на счетный вход 76 счетчика 26, При этом код адреса подается ка входы 118 дешифратора 111 и на одном из выходов 120 дешифратора 111 (опре - делается кодом адреса) формируется разрешающий сигнал; коуорьй через со- ответствуюшда элемент И 113 (на втором входе 121 элемента И высокий разрешающий потенциал) подается на вход 122 разрешения записи в соответствующий регистр 115„ Таким образом организует - ся запись слова информации и значения бита сопровожденил в соответствуюкгую ячейку памяти„

По заднему фронту сигнала сопровождения слова информации содержимое счетчика 26 увеличивается на еданицу и снимается разрешающий запись потенциал с входа 106 блока 19 памяти (устанавливается высокий потенциал на выходе 106 элемента И 47 и низкий на входах 121 элементов И 113) Следую- i ш;ее слово информации и бк сопрово;-: дения записьшаются в регистр 115s со- ответствуютций новому (большему на едиединицу) адресу (содержимому счетчика 26) и ТоД,

Одновременно с приемом информации и ее записью в блок 19 памяти ocjraiecT вляются чтение информации из блока 18 памяти и ее, вывод из устройства. Чтение информации из блока 18 памяти разрешается высоким потенциалом с выхода 92 элемента И-НЕ 34 (на входе 71 элемента И-НЕ 34 низкий потенциал, та как триггер 15 находится в единргчном состоянии). При этом на входах 119 элементов И 114 присутствует высокий разрешающий потенциал, так как на входе 71 элемента И-НЕ 34 поддерживается низкий потенциал, так как на входе 71 элемента И-НЕ 34 поддержива ется низкий потенциал (триггер 15 находится S единичном состоянии). Код адреса содержимое счетчика 25) подается на входы ВО (старший разряд) и В1 блока 18 памяти (входы 118 де1аи- фратора 1М).

Содержимое счетчика 25 (код адреса) формируется в данном случае по заднему фронту синхросигнала, который с входа 50 устройств а для сопряжения через элемент И 1, элемент И 20 (на входе 70 элемента И 20 высокий потенциал) и через элемент ИЛИ 23 подается на счетный вход 77 счетчика 25. Высокий потенциал с одного из выходов 120 дешифратора 111 подается через соответствующий элемент И 114 на вход 123 разрешения чтения регистра 115. Содержимое регистра 113 через элементы ИЛИ 11 б подается на входы 74 груп -- пы элементов 31. При наличии на входе 50 устройства синхросигнала, которьй через элемент И 1 (на входе 110 элемента И 1 высокий потенциал с соответствующего выхода триггера 39) и элемент И 20 (на входе 70 элемента

При этом высокий разрешающий по щ-1ал с выхода 71 триггера 15 подае на входы 71 элемента И 7 и группы элементов И 8 (разрешается запись слов информации и битов сопровожде в блок 18 памяти), на вход 71 элем

И 20 высокий.потенхщал с соответству- 5 та И 12 (разрешается формирование

ющего выхода триггера 15) подается на вход 78 группы элементов И.31, поэтому содержимое регистра 115 через труппу элемен;ров И 31 через группу элементов ШШ 2 м группу элементов И 44 (на входах 110 группы элементов И 44 высокий потенциал с выхода 100 триггера 39) подаются на выходы 108 устройства.

По заднему фронту синхросигнала на входе 50 устройства снимается разрешающий потенхдаал с выходов 78 группы элементов И 31 и регистр 115 отключается от выходов.108 устройства, Кросигналов разрешения записи на вход 92 блока 18 памяти и сигналов сопр волсдения на счетный вход 77 счетчи 25), на вход 71 элемента И 24 (раз

50 шается подача на входы 79 группы э ментов И 39 синхросигналов, разреш ющих подачу слов информации и бита сопровождения с выходов 75 блока 1 памяти через группу элементов И 32

55 группу элементов ИЛИ 42 и группу э ментов И 44 на выходы 108 устройст а также через элемент ИЛИ 22 синхр сигналов на счетньш вход 76 счетчи ка 26) ..

не того, по заднему фронту синхросигнала увеличивается на единицу содер- жимое счетчика 25. Поэтому при появлении на входе 50 устройства следующего синхросигнала через группу элементов И 31 к выходам устройства подключаются выходы следующего регистра 115 и т.д.

Очевидно, что скорость вывода на выходы 108 устройства слов информации (слово информации и бит сигнала сопровождения) определяется частотой синхросигнапов, подаваемых на вход 5 50.,устройствао

Оба параллельных процесса (запись слов информапли и сигналов сопровождения соответственно входов 52 и 51 устройства в блок 19 памяти и вывод 0 информации и битов сопровождения из блока 19 памяти на выходы 108 устройства) протекают без изменения до появления единицы в старшем разряде (потенциала нм выходе 80) счетчика 25.

При этом высокий потенциал с выхода 80 счетчика 25 через элементы ИЛИ 27 и И 29 (на втором входе элемента И 29 устанавливается высокий разрешающий потенциал при отсутствии сигнала сопровождения на входе 51 устройства) подается на входы 88 Сброс счетчиков 25 и 26 (счетчики 25 и 26 устанавливаются в исходное нулевое состояние) через элемент ИЛИ 35 на счетньш вход 93 триггера 15 (триггер 15 переключается в нулевое состояние) и через элементы ИЛИ 28 и И 43 на выход 107 устройства.

При этом высокий разрешающий потен-- щ-1ал с выхода 71 триггера 15 подается на входы 71 элемента И 7 и группы элементов И 8 (разрешается запись слов информации и битов сопровождения в блок 18 памяти), на вход 71 элемен-

5

0

5

0

сигналов разрешения записи на вход 92 блока 18 памяти и сигналов сопро- волсдения на счетный вход 77 счетчика 25), на вход 71 элемента И 24 (разрешается подача на входы 79 группы элементов И 39 синхросигналов, разрешающих подачу слов информации и бита сопровождения с выходов 75 блока 19 памяти через группу элементов И 32,

группу элементов ИЛИ 42 и группу элементов И 44 на выходы 108 устройства, а также через элемент ИЛИ 22 синхросигналов на счетньш вход 76 счетчика 26) ..

Таким образом, разрешаются два па раплельных процесса, однако запись слов информации и битов сопровожде ;ния разрешается в блок 18 памяти, а :чтение из блока 19 памяти и т.д. до :появления высокого потенциала на вы- I ходе 82 старшего разряда счетчика 26 Iкоторьм устанавливает в исходное ну- Iлевое состояние оба счетчика и т.д., I как-описано.

I Таким образом, вывод информации I осуществляется в данном случае из |ЭВМ на аппарат магнитной записи. Вхо I50 может быть подключен и к выходу принимающего устройства. При вводе I информации в ЭВМ на входы 48 устройс |ва и дешифратора 37 формируется код команды Ввод. При этом триггер 39 устанавливается в нулевое состояние, {т.е. на выходе 101 триггера 39 и на соответствующих входах элементов |И45, 36и5и4и групп элементов И 46 и 6 устанавливается высокий разрешающий потенциал, а на выходе 100 триггера 39 и на соответствующих входах элементов И 43, 1 и 2 и групп |элементов И 3 и 44 низкий разреша- ющий потенциал.

При этом в устройстве, как и в- пр дьщзтцем случае, разрешаются два параллельных процесса.

1. Запись информации и битов сопрвождения соответственно с входов 55 и 54 устройства-в блок 18 или 19 па- |мяти (определяется состоянием тригге 1ра 15), а также прием от абонента ; (вход 53 устройства) сигнала запроса на обслуживание и формирование по си налу запроса на обслуживание потенциала на выход 109 устройства. При это сигнал с выхода 59 элемента И 4 подается на соответствующий вход триггер 41 и устанавливает его в нулевое со- стояние. Высокий потенциал с выхода 103 триггера 41 подается через элемент И 45 на йыход 109 устройства.

.2. Вывод информации из блока 19; или 18 памяти (определяется состояни триггера 15) в ЭВМ.

Оканчивается процесс подачей на входы 48 устройства кода команды Сброс счетчика. При .этом сигналом с выхода 97 дешифратора 37 через эле менты ИЛИ 27,.И 29 и счетчики 25 и 26 устанавливаются в исходное нулевое состояние, Оба процесса в данном случае должны быть упорядочены во времени; т.е. сигнал запроса на обслуживание на входе 53 устройства дол жен формироваться после записи в бло 18 или 19 памяти (зависит от состояния триггера 15) блока данных, вывод блока данных из блока 19 или 18 памя ти (непосредственно формирование на входы 48 устройства кода команды Сброс счетчика); должны.быть обеспе

Оба процесса аналогичны описанным., 50 ены до начала записи в блок 19 или

Однако переключение состояний триггера 15 в отличие от описанного осущест - вляется по сигналам запроса на обслу- живание, подаваемом на вход 53 устрой- ства и элемента И 4. При этом сигнал i 55 с выхода 59 элемента И 4 подается -че- рез элемент ИЛИ 35 на счетный вход 93 триггера 15. Кроме того, вывод слов информации из блоков 18 и 19 осу-«

18 памяти нового блока данных.

Таким образом, предлагаемое уст- ройство в отличие от известного обес печивает сопряжение синхронных устройств с различной скоростью обмена. Согласование скоростей обмена синхронных устройств обеспечивается вкл чением в состав устройства для сопря жения двух блоков памяти. При этом

8

o

S

5

0

5

ществляется по сигналам запроса слова, формируемым принимаюшрм устройством (в данном случае ЭВМ), работающем в асинхронном режиме обмена, на вход 49 устройства для сопряжения.

Непосредственно вывод блока инфор нации из блока 18 или 19 памяти (определяется состоя1шем триггера 15) осуществляется следующим образом. На входы 48 устройства подается код ко манды Чтение и сигналом с выхода 98 дешифратора 37 триггер 40 устанавливается в единичное состояние. Высокий потенциал с выхода 102 триггера 40 подается на соответствуюнщй вход элемента И 33 и разрешает прием сигналов запроса цлова которые через элементы И 33 и 36 и элемент И 14 или 13 (зависит от состояния триггера 15) подаются на счетный вход соответствующего счетчика. Дальнейшее течение процесса аналогично описанному.

По окончании приема блока данных на входы 48 устройства подается код команды Сброс и сигналом с выхода 99 дешифратора 37 триггер 40 устанавливается в нулевое состояние (с выхода 102 триггера 40 снимается высокий 0 разрешающий потенграл), а триггер 41 . в единичное состояние,, На выходе 109 устройства устанавливается нулевой потенциал.

Оканчивается процесс подачей на входы 48 устройства кода команды Сброс счетчика. При .этом сигналом с выхода 97 дешифратора 37 через эле- менты ИЛИ 27,.И 29 и счетчики 25 и 26 устанавливаются в исходное нулевое состояние, Оба процесса в данном случае должны быть упорядочены во времени; т.е. сигнал запроса на обслуживание на входе 53 устройства должен формироваться после записи в блок 18 или 19 памяти (зависит от состояния триггера 15) блока данных, вывод блока данных из блока 19 или 18 памяти (непосредственно формирование на входы 48 устройства кода команды Сброс счетчика); должны.быть обеспе0

5

0 ены до начала записи в блок 19 или

18 памяти нового блока данных.

Таким образом, предлагаемое уст- .- ройство в отличие от известного обеспечивает сопряжение синхронных устройств с различной скоростью обмена. Согласование скоростей обмена синхронных устройств обеспечивается включением в состав устройства для сопряжения двух блоков памяти. При этом

la

одновременно обеспечр ваются прием дан нЫх в один из блоков памяти и вывод данных из другого блока памяти, а также автоматическое переключение блоков памяти после окончания вывода данных ИЗ устройства для сопряжения. Автоматическое переключение блоков памяти обеспечивается при переполнении счетчика адреса, обслуживающего блок памяти, из которого выводятся данные. При этом сигнал переполнения передается на счетньш вход триггера, управля - ющие потенциалы с выходов которого обеспечивают коммутахщю блоков памяти в устройстве для сопряжения.

Скорость вывода данных регулируется подачей синхропоследовательности на вход 50 устройства. Изменение частоты поступления сигналов в синхропоследовательности обеспечивает изменение скорости вывода данных. При этом вход 50 устройства может быть подключен как к источнику, так и к приемнику.

В отличие от известного предлагаемое устройство обеспечивает также сопряжение разнотипных (синхронных, и асинхронных) устройств. При этом обеспечивается после приема в блок 18 или 19 памяти (зависит от состояния iтриггера 15) формирование потенциала запроса на обслуживание а асинхрон- ньш приемник на выходе 109 устройства. Считывание слов информации и битов сопровождения обеспечивается по сигналам запроса слова данных, передаваемых на вход 49 устройства после приема запроса с выхода 109 устройства; Кроме того, обеспечивается преобразование бита сопровождения (записывается в блок памяти совместно, со словом данных) в сигнал сопровождения слова данных на выходах 110 устройства.

Предлагаемое устройство обеспечивает также сопряжение асинхронных (источника и приемника) устройств. В этом случае к источнику подключаются входы 53-55 и выход 109 устройст16

ва, к приемнику выходы 109 и ПО и входы 48 и 49 устройства.

Обмен информацией через устройство осуществляется следующим образом. Приемник формирует на входы 48 ройства коды команд Ввод и Чтение (по-включение). Выполняется процедура ПОДГОТОВЬ к- обмену, которая заключается в следующем. Источник формиру

729

10

ет при готовности к обмену сигнал готовности к обмену (вход 53 устройст- ва)..Устройство формирует и вьщает 2 на выход 109 потенциал готовности к обмену. Приемник формирует на входы 48 устройства коды команд Сброс, Сброс счетчиков и Чтение. Устройство снимает потенциал с выхода 109. 0 Дальше организуется процедура непосредственного обмена информацией,, которая заключается в следующем. Источник формирует сигнал на вход 53, слово информации на входы 55 и сигнал 5 сопровождения на вход 54 устройства, которое формирует потенциал на выход 109. Приемник формирует сигнал на вход 49 (устройство обеспечивает вывод слова информации на выходы 110), 0 а также формирует и вьщает команды Сброс, Сброс счетчиков и Чтение. Устройство снимает потенциал с выхода 109 и т,д,

Таким образом, предлагаемое уст- 5 ройство в отличие от извест ного обеспечивает об.мен не только однотипных асинхронных с одинаковой скоростью обмена или асинхронных), но и разно- типньгх (синхронных с различными скоро- 0 стями обмена данным-и, а также синхронных с асннхроннь:ми.

Формула изобретен и

35

5

, Устройство для сопряжения ЭВМ с абонентом, содержащее восемь групп элементов И, дешифратор, два элемента ШШ, причем первый входы элементов И первой группы образуют группу вхо- 40 Дов устройства для подключения к группе информационных выходов ЭВМ, группа входов деишфратора образует группу входов устройства для подютю- чения к группе командных выходов ЭВМ, первые входы элементов И второй группы образуют группу входов устройства для подключения к группе информационных выходов абонента, выходы элементов И третьей группы образуют группу выходов устройства для подключения к группе информационных входов ЭВМ, выходы элементов И четвертой группы образуют группу выходов устройства для подключения к группе информацион- 5 Ных входов абонента, о тл и ч а ю - Щ е е с я тем, что, с целью расширения области применения за счет обеспечения обмена информацией между разно- скоростными, а также синхронными к

0

11

асинхронными источником и приемником и -1формации, в устройство введены два i 6|iOKa памяти, четыре триггера, два сЦетчика, семнадцать элементов Ир две| группы элементов ИЛИ, шесть элементов ИрШ, два элемента И - НЕ, элемент НЕ, пЬичем первые входы первого, второго и третьего элементов И являются входами устройства для подключения соответственно к выходам чтения, синхронизации и стробировагая ЭВМ, первые входы четвертого и пятого элементов И явля- нтся входами устройства для подключения соответственно к выходам запроса va обслуживание и стробирования або- ента, выходы шестого и седьмого эле- ентов И являются выходами устройства дя подключения соответственно к ходам запроса на обслуживание ЭВМ и тробирования абонента, при этом -пер- (ьш и второй выходы дешифратора сое10

динены соответственно с единичньм и рулевыми входами первого триггераj идиничньй выход которого соединен с иторыми входами второго и третьего :шементов И, элементов И первой груп- (1ы, с первыми входами..элементов И чет Чертой группы, с первым входом ого элемента И, второй вход которого :оединен с. вькодами первого элемента iJM, первьй вход которого соединен с адресным входом первого блока памятиj .:; первым входом второго элемента ИЛИ, с. выходом старшего разряда первого схчетчика, группа выходов младшего разряда которого соединена с группой Адресных входов первого блока памяти, 1синхровход которого соединен с выходом восьмого элемента И, первый вход KOTOpoi o, соединен с первыми входами , элементов И пятой группы, с первыми ; входами девятого, десятого и одиннадцатого элементов И, с первым входом - первого элемента И-НЕ, с нулевым вы- ходом второго триггера, счетньш вход которого соединен с выходом третьего элемента ИЛИ, первьй вход которого соединен с нулевым входом третьего триггера и с выходом четвертого эле°- мента И, второй вход которого соединен с вторым входом пятого элемента И, вторыми входами элементов И второй группы, нулевым выходомг-первого триггера, первым входом шестого элемента И, первыми входами элементов И третьей группы, первым входом двенадцатого элемента И, второй вход которого сое дивен с выходом первого элемента И,

161572912

второй вход которого соединен с едй- . ничным выходом четвертого триггера, единичньй вход которого соединен с третьим выходом дешифратора, четвер- тьй выход которого соединен с нулевым входом четвертого триггера и единичным входом третьего триггера, нулевой выход которого соединен с вторым входом шестого элемента И, вторые входы элементов И четвертой группы соединены с вторыми входами элементов И третьей группы и выходами элементов ИШ первой группы, первые и вторые входы ко- 5 торых соединены соответственно с выходами элементов И шестой и седьмой групп, первые входы которых соединены соответственно с группами информационных выходов первого и второго 20 блоков памяти соответственно, группы информационных входов которых соеди- нены соответственно с выходами эле- ментов И пятой и восьмой групп, выходы элементов И первой и второй 25 групп соединены соответственно с первыми и вторыми входами элементов ИЛИ второй группы, выходы которых соединены с вторым входами элементов И пятой группы и первыми входами элемен- 30 тов И восьмой группы, вторые входы элементов И восьмой группы соединены, с первыми входами тринадцатого, чет.ыр- надцатого, пятнадцатого и шестнадцатого элементов И, единичным выходом второго тр14:ггера и первым входом вто- - рого элемента И-НЕ, выход которого соединен с входом записи чтения второго блока памяти, синхровход которого соединен с выходом тринадцатого .Q элемента И., второй вход которого соединен с вторыми входами восьмого, девятого и четьфнадцатого элементов И, с-выходом первого элемента ИЛИ и входом элемента НЕ, выход которого 45 соединен с первым входом семнадцато-; го элемента И, второй вход которого соединен с выходом второго элемента ИЛИ, второй вход которого соединен с: вторым входом второго элемента ИЛИ, 50 выходом старшего разряда второго счетчика и .адресным входом второго блока памяти, группа адресных входов которого соединена с группой выходов . младших разрядов второго счетчика, - установочньй вход которого соединен с установочным входом первого счетчика, вторым входом третьего элемента ИЛИ и выходом семнадцатого элемента И, пятый выход дешифратора соединен i

с третьим входом второго элемента ИЛИ, выходы третьего и пятого элементов И;соединены соответственно с пер- .вым и вторым входами четвертого эле мента ИЛИ, выход второго элемента И соединен с вторым входом одиннадцатого элемента И и вторым входом шестнадцатого элемента И, выход которого соединен с вторыми входами элементов И шестой группы, с первым входом пятого элемента ЮШ и первым входом- шестого элемента ИЛИ, выход которого соединен с вторым входом первого элемента И-НЕ, выход которого соединен с входом записи/чтения первого блока памятки, выход двенадцатого элемента И соединен с вторыми входами десятого и пятнадцатого элементов И, выходы ко

5

торых соединены соответственно с первым входом седьмого элемента ИЛИ и вторым входом пятого элемента ИЛИ, выходы которых соединены соответственно со счетными входами второго и первого счетчиков, выход одиннадцатого элемента И соединен с вторыми входами элементов И седьмой группы, первым входом восьмого элемента ИЛИ и вторым входом седьмого элемента ШШ третий вход которого соединен с выходом четырнадцатого элемента И и вторым входом восьмого элемента ИЛИ, выход кот,орого соединен с вторым входом вто-. роге элемента И-НЕ, выход девятого элемента И соединен с вторым входом шестого элемента И.ПИ и третьм входом

пятого элемента ШШ. . I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с абонентами | 1985 |

|

SU1302289A1 |

| Устройство для подключения ЭВМ к системной шине | 1986 |

|

SU1361571A1 |

| Устройство для сопряжения многоблочной памяти с процессором и вводно-выводными устройствами | 1984 |

|

SU1280645A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для сопряжения вычислительной машины с внешним устройством | 1985 |

|

SU1278868A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1988 |

|

SU1532939A1 |

| Устройство для сопряжения электронной вычислительной машины с общей шиной | 1983 |

|

SU1144112A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1462336A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1987 |

|

SU1515165A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1988 |

|

SU1520531A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах для сопряжения устройств, осуществляющих обмен информацией. Целью изобретения является расширение области применения за счет обеспечения обмена информацией между разноскоростными, а также синхронными и асинхронными источниками и приемниками информации. Устройство содержит два блока памяти, дешифратор, два счетчика, четыре триггера, семнадцать элементов И, восемь элементов ИЛИ, два элемента И-Не, элемент НЕ, восемь групп элементов И, две группы элементов ИЛИ. 2 ил.

ФигЛ

| Авторское свидетельство СССР № 225562, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения | 1972 |

|

SU481895A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-12-23—Публикация

1989-01-27—Подача