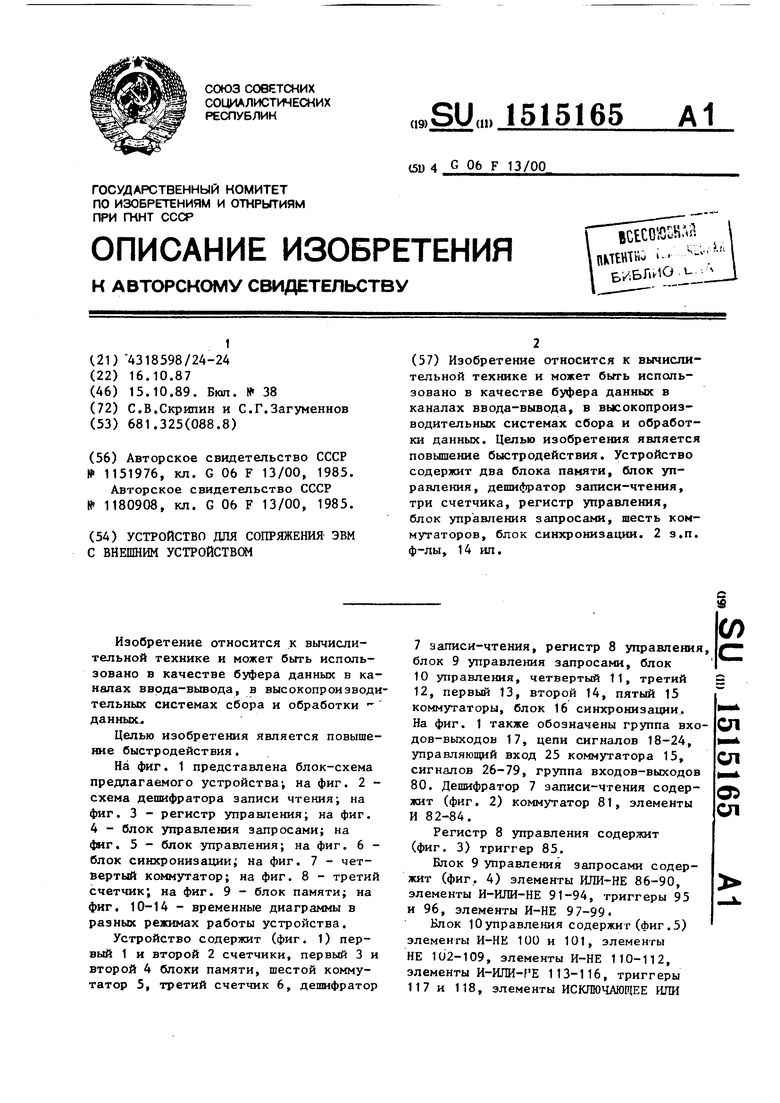

Изобретение относится к вычислительной технике и может быть использовано в качестве буфера данных в каналах ввода-вывода, в высокопроизводительных системах сбора и обработки данных

Целью изобретения является повышение быстродействия.

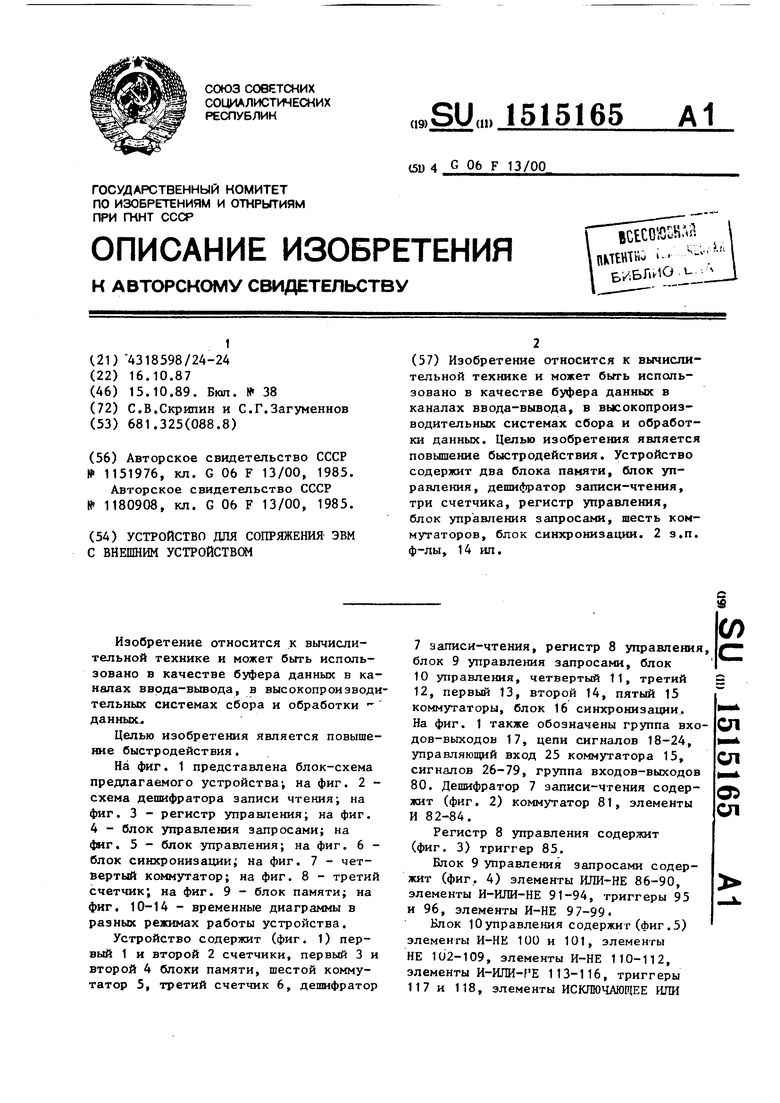

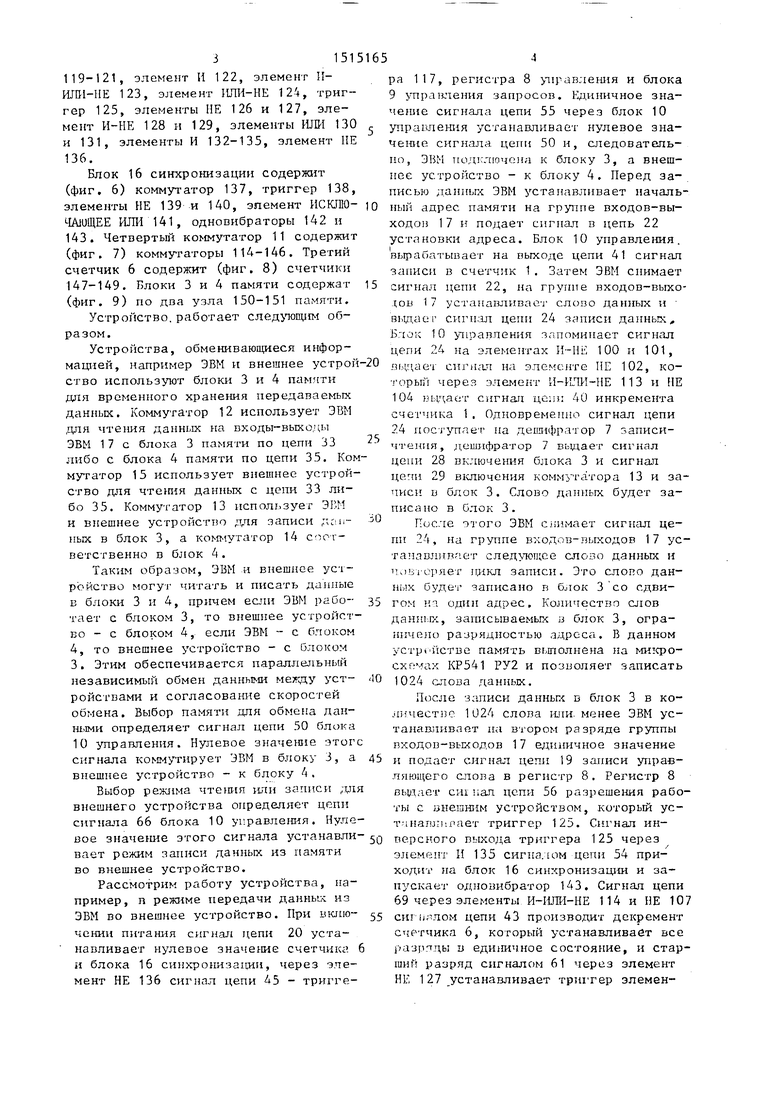

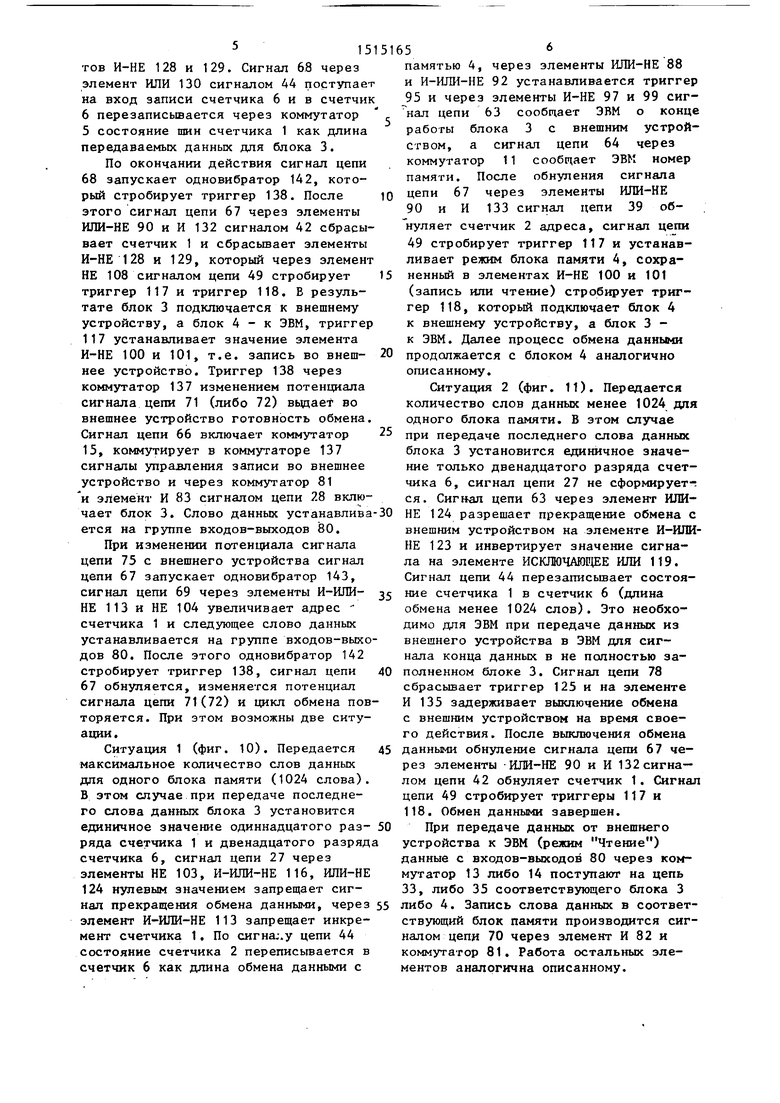

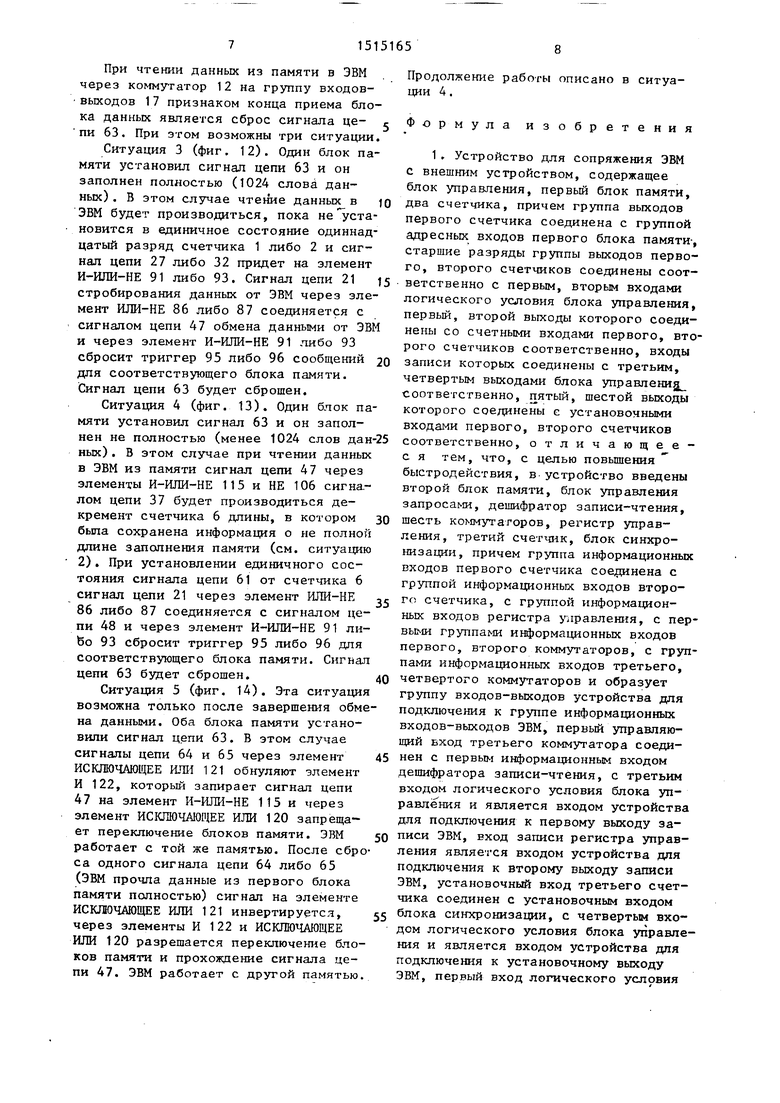

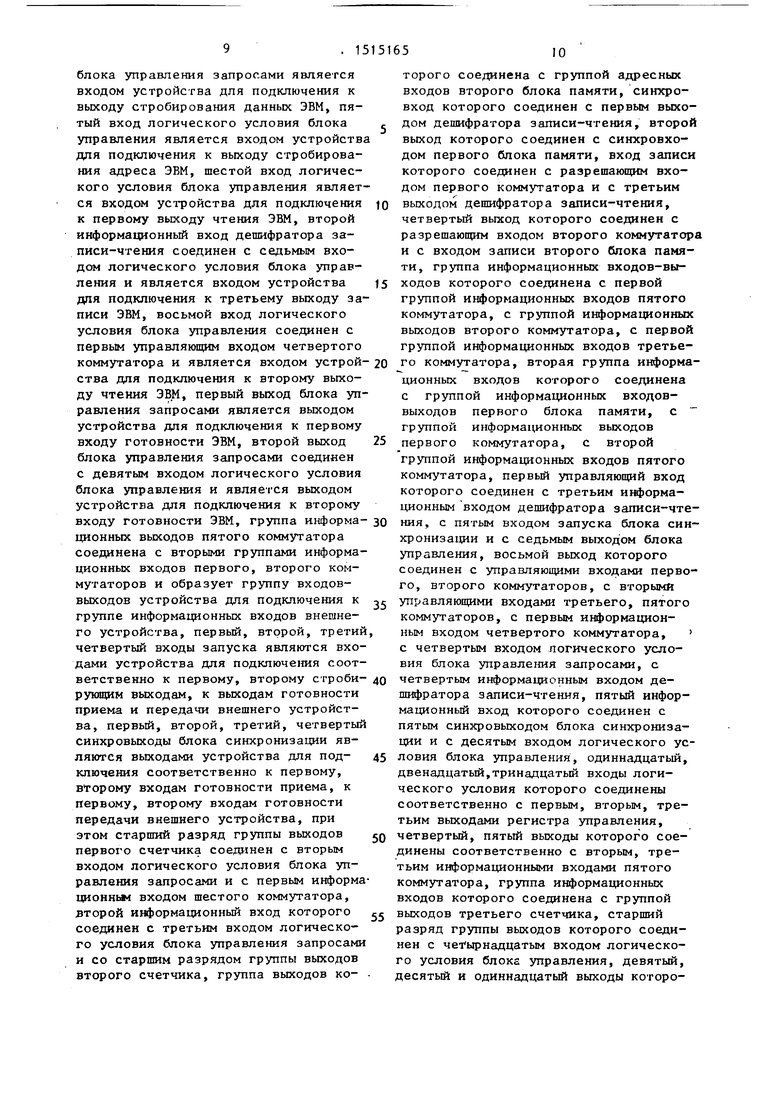

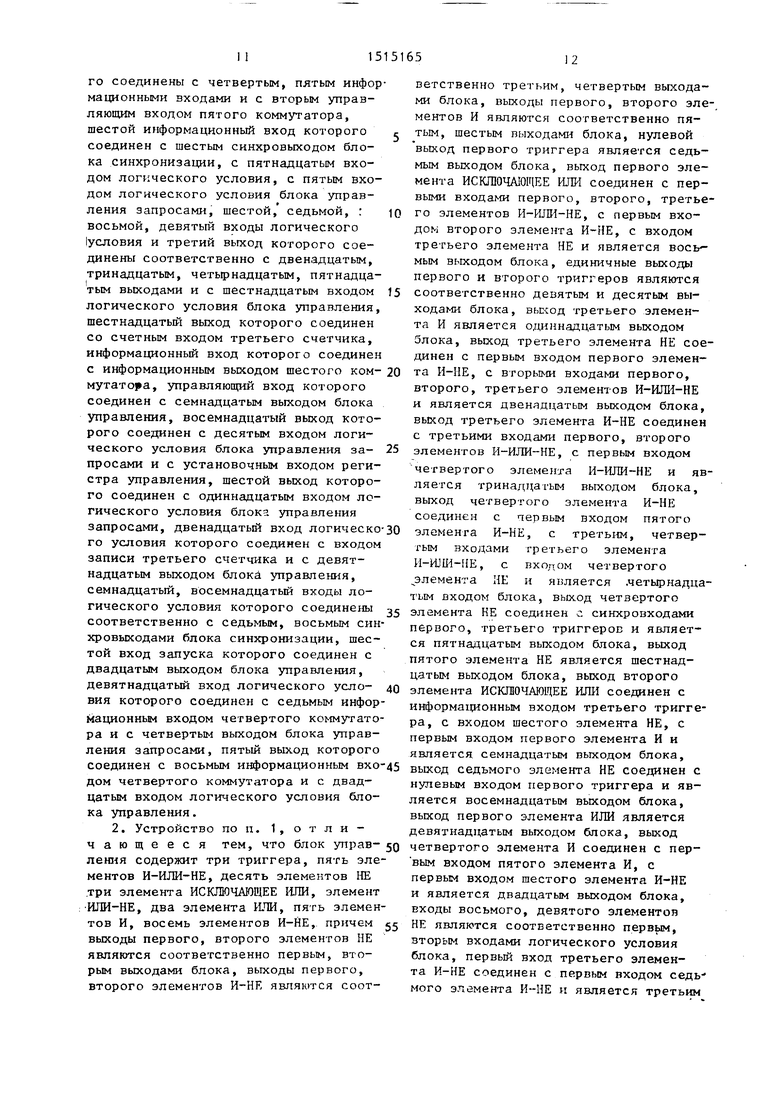

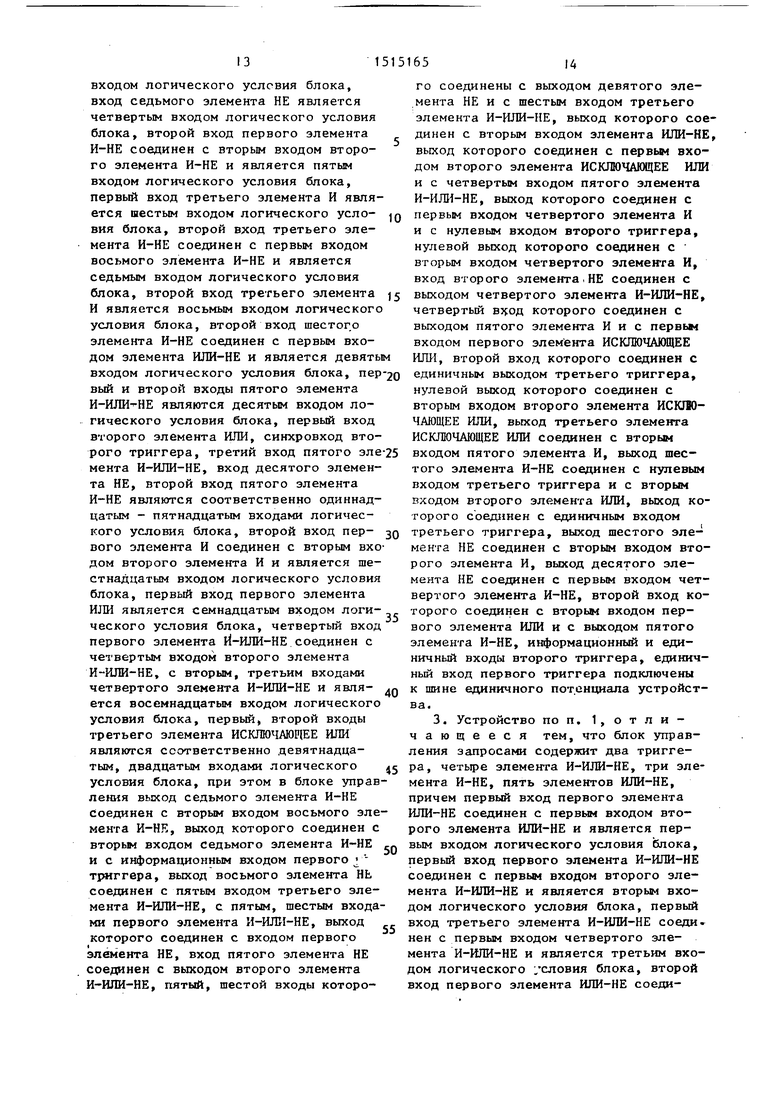

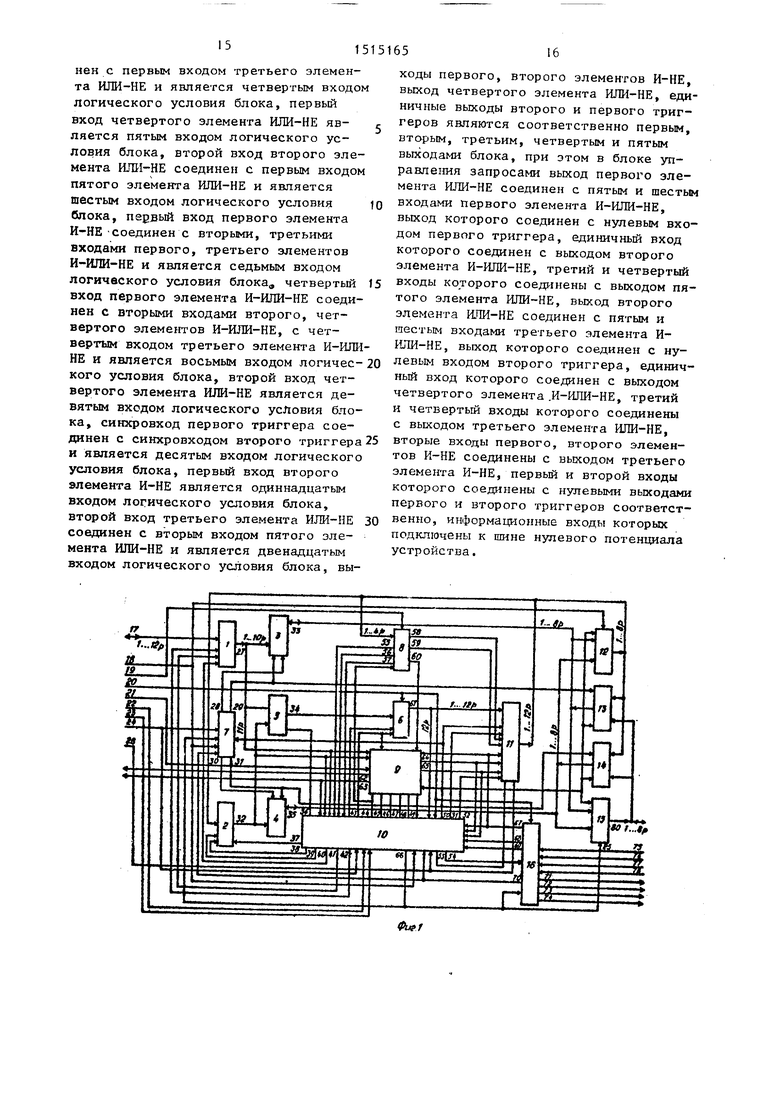

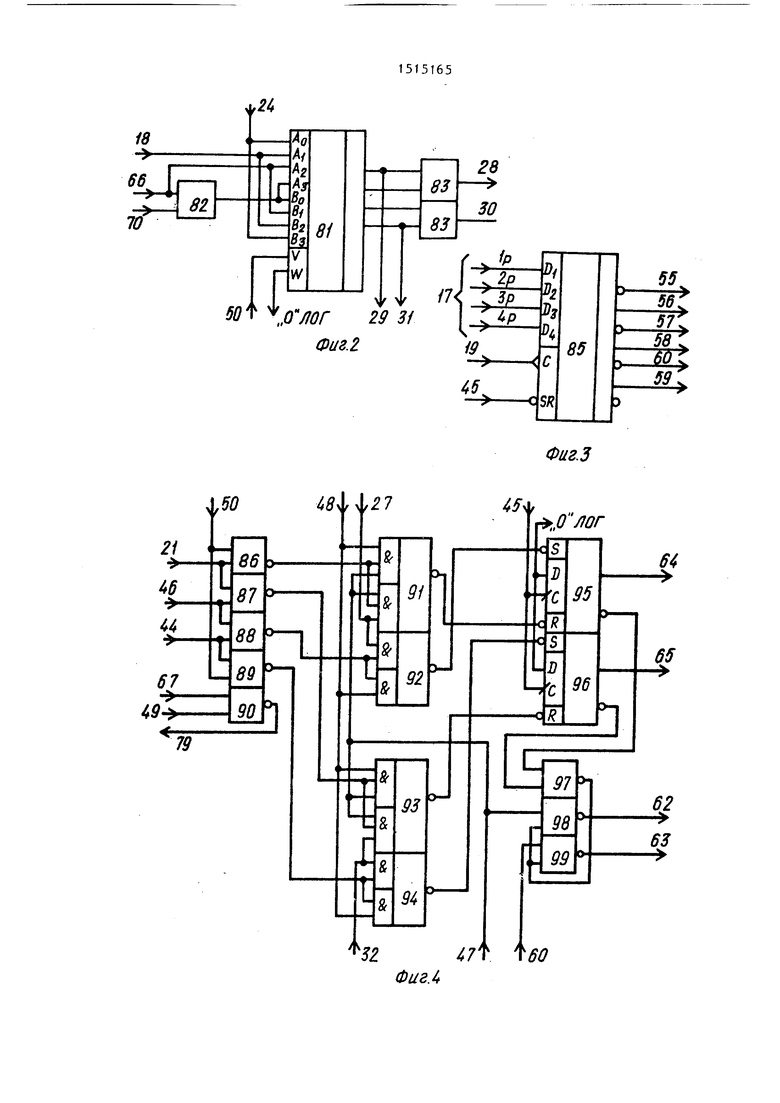

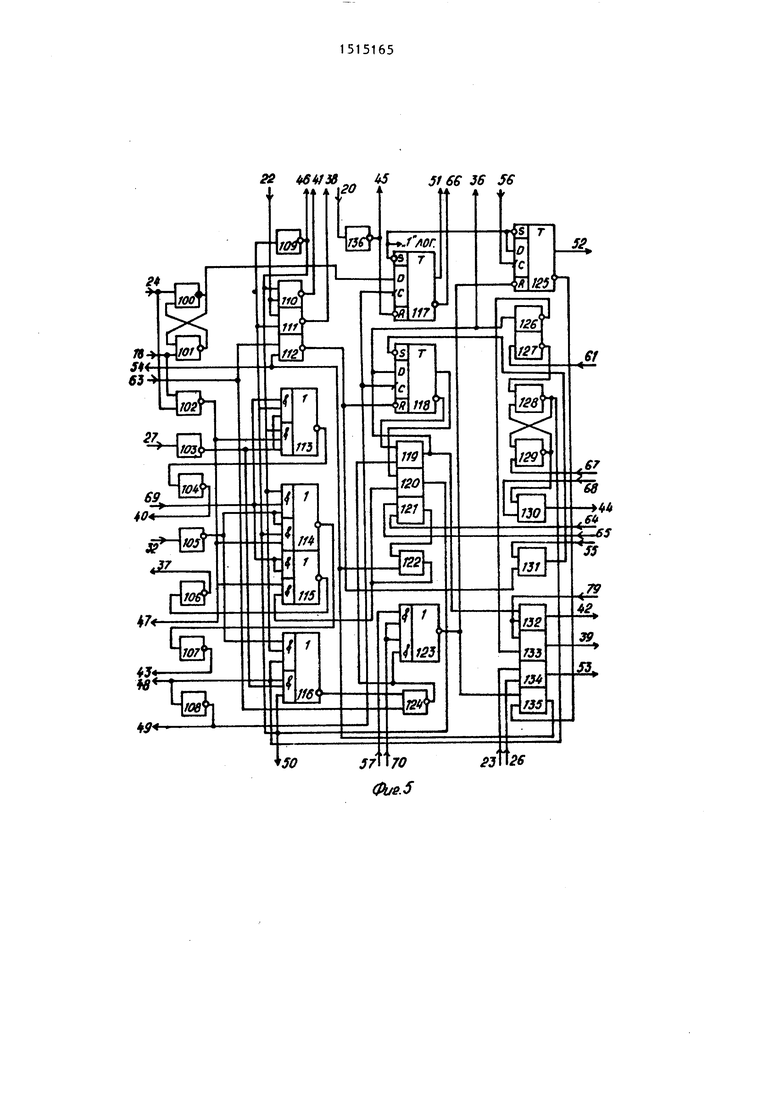

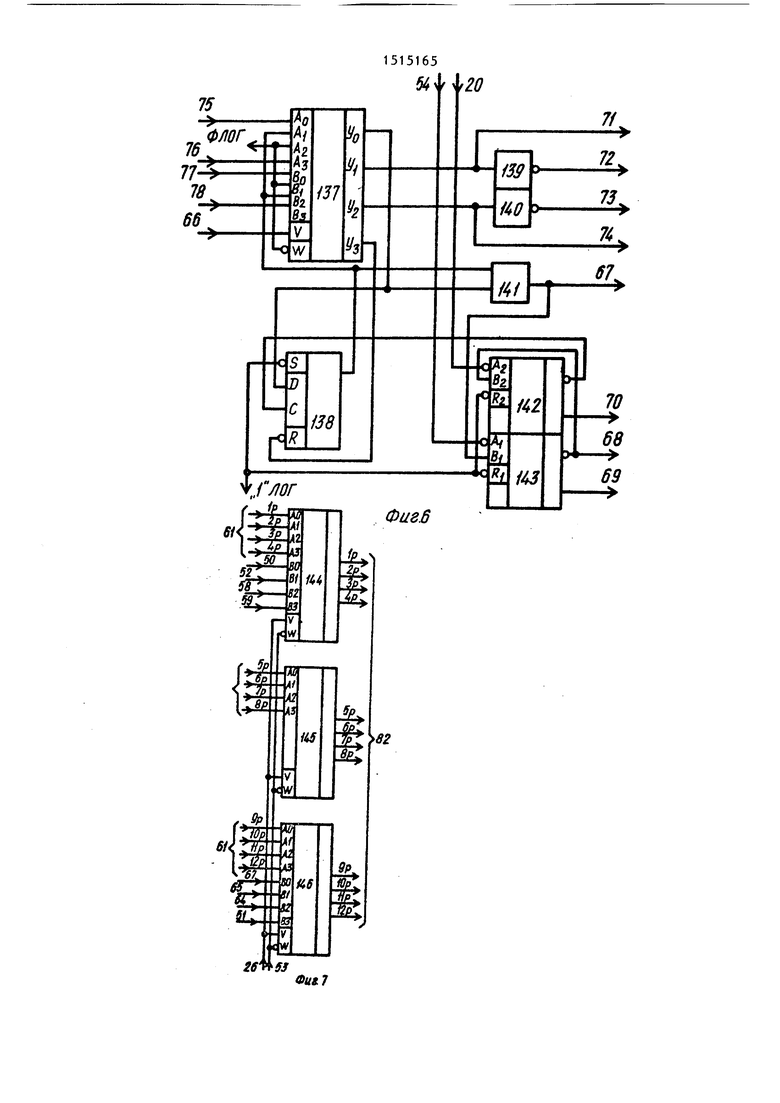

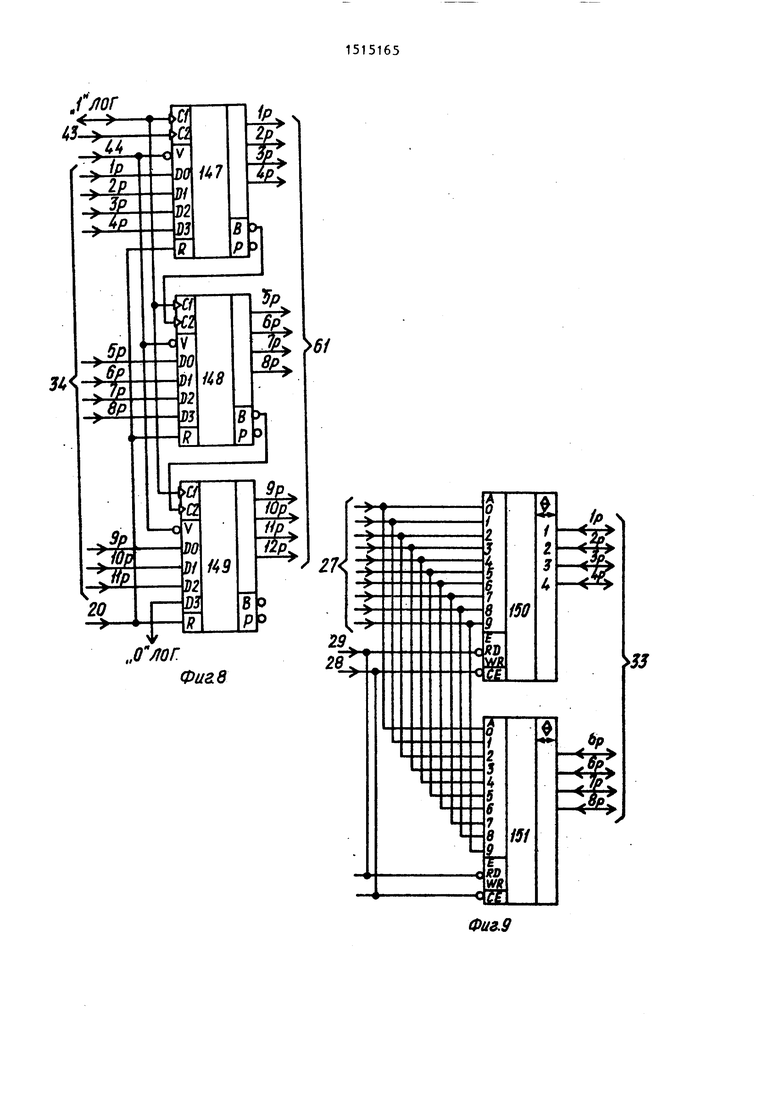

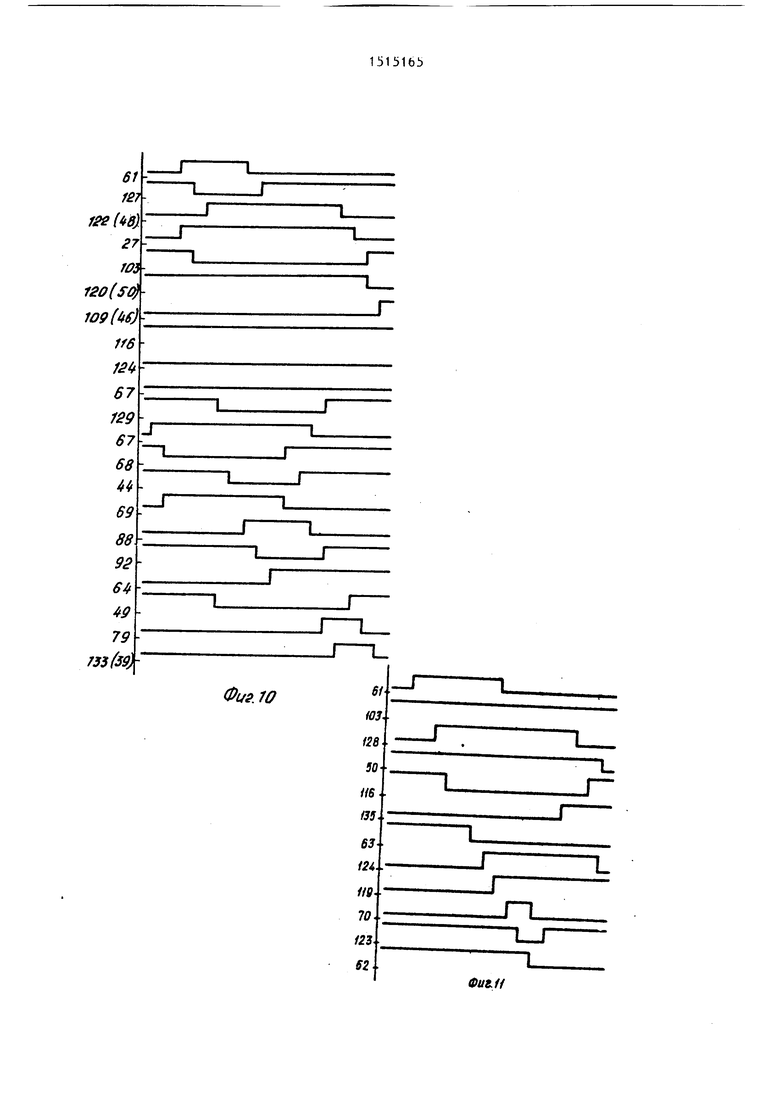

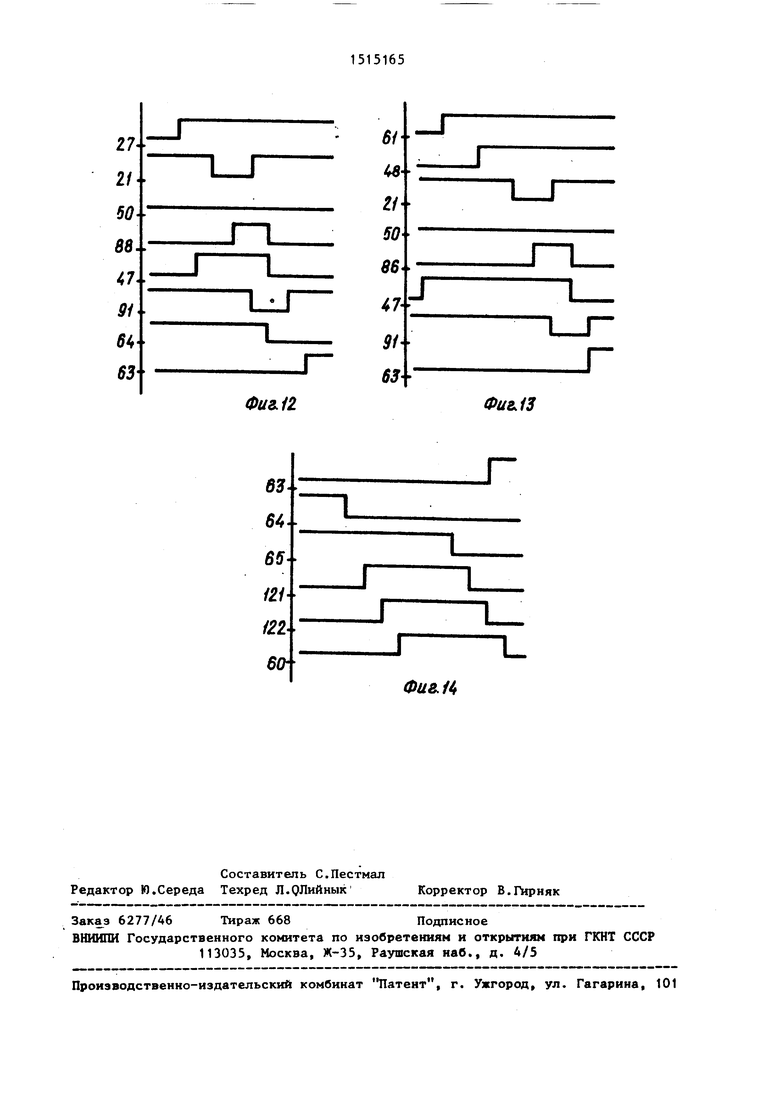

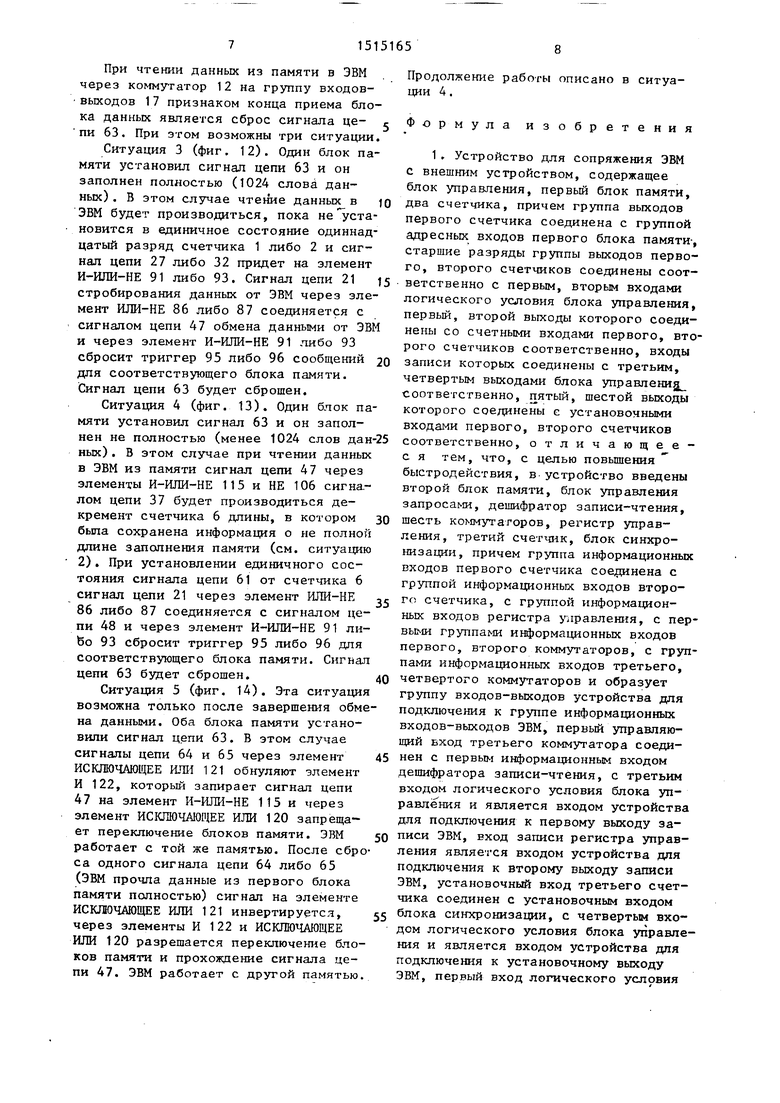

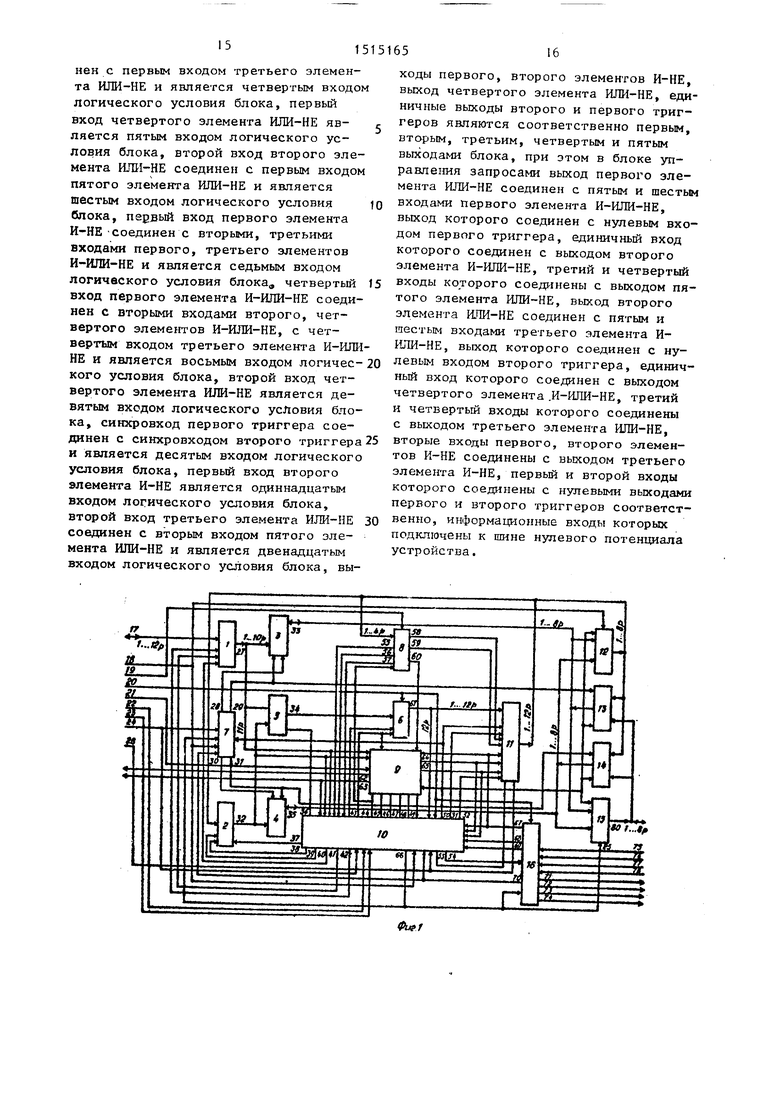

На фиг. 1 представлена блок-схема предлагаемого устройства-, на фиг. 2 - схема дешифратора записи чтения; на фиг. 3 - регистр управления; на фиг. 4 - блок управления запросами; на фиг. 5 - блок управления; на фиг. 6 - блок синхронизации; на фиг. 7 - четвертый коммутатор; на фиг. 8 - третий счетчик; на фиг. 9 - блок памяти; на фиг. 10-14 - временные диаграммы в разных режимах работы устройства.

Устройство содержит (фиг. 1) первый 1 и второй 2 счетчики, первый 3 и второй 4 блоки памяти, шестой коммутатор 5, третий счетчик 6, дешифратор

7 записи-чтения, регистр 8 управления, блок 9 управления запросами, блок 10 управления, четвертый 11, третий 12, первый 13, второй 14, пятый 15 коммутаторы, блок 16 синхронизации. На фиг. 1 также обозначены группа входов-выходов 17, цепи сигналов 18-24, управляющий вход 25 коммутатора 15, сигналов 26-79, группа входов-выходов 80. Дешифратор 7 записи-чтения содержит (фиг. 2) коммутатор 81, элементы И 82-84.

Регистр 8 управления содержит (фиг. 3) триггер 85.

Блок 9 управления запросами содержит (фиг. 4) злементы ИЛИ-НЕ 86-90, элементы И-ИЛИ-НЕ 91-94, триггеры 95 и 96, элементы И-НЕ 97-99.

Клок 10 управления содержит (фиг .5) элементы И-НЕ 100 и 101, элементы НЕ 102-109, элементы И-НЕ 110-112, элементы И-ШIИ-f E 113-116, триггеры 117 и 118, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ

(Л

ел ел

о: ел

31515165

119-121, элемент И 122, элемент И- ИЛ11-11Е 123, элемент 1ШИ-ИЕ 124, триггер 125, элементы НЕ 126 и 127, элемент И-НЕ 128 и 129, элементы ШШ 130 и 131, элементы И 132-135, элемент НЕ 136.

Блок 16 синхронизации содержит (фиг, 6) коммутатор 137, триггер 138,

элементы НЕ 139 и 140, элемент НСКЛО- )о нын адрес памяти на группе входов-выi-IAlUfllEE ИЛИ 141, одновибраторы 142 и

143. Четвертьп коммутатор 11 содержит

(фиг. 7) коммугаторы 114-146. Третий

счетчик 6 содержит (фиг. 8) счетчики

147-149. Блоки 3 и 4 памяти содержат 15

(фиг. 9) по два узла 150-151 памяти.

Устройство, работает след пощим образом.

Устройства, обменивающиеся информацией, например ЭВМ и внешнее устрой-20 ство используют блоки 3 и 4 памяти для временного хранения передаваемых данных. Коммутатор 12 использует ЭВМ ,цля чтения данных на входы-выходы ЭВМ 1 7 с блока 3 памяти по цепи 33 - либо с блока 4 памяти по цепи 35. Коммутатор 15 использует внешнее устройство для данных с цепи 33 либо 35. Коммутатор 13 использует ЭВМ и внешнее устройство для записи 0 ных в блок 3, а коммутатор 14 соответственно в блок 4.

Таким образом, ЭВМ и внешнее устройство могут читать и писать данные в блоки 3 и 4, причем если ЭВМ рабо- 35 тает с блоком 3, то внешнее устройство - с блоком 4, если ЭВМ - с блоком 4, то внешнее устройство - с блоком 3. Этим обеспечивается параллельный независимый обмен данными между уст- 40 ройствами и согласование скоростей обмена. Выбор памяти для обмена данными определяет сигнал цепи 50 блока 10 управления. Нулевое значешш этого

ходон 17 и подает сигнал в цепь 22 установки адреса. Блок 10 управления. вырабатывает на выходе цепи 41 сигнал записи в счетчик 1. Затем ЭВМ снимает сигнал цепи 22, на группе входов-выходов 17 устанавливает слово данных и выдает сигн:ш цепи 24 записи данных. Блок 10 управления запоминает сигнал цепи 24 на элементах И-НЕ 100 и 101, лыццает сиги;ш на элементе НЕ 102, ко- горьш через элемент И-ИЛИ-НЕ 113 и НЕ 104 сигнал цени 40 инкремента счетчика 1, Одновременно сигнал цепи 24 посч упает на дешифратор 7 записи- чтения, дешифратор 7 вьщает сигнал цени 28 включения блока 3 и сигнал цепи писи писано в блок 3.

После этого ЭВМ CJiiiMaeT сигнал цепи 24, на группе входов-выходов 17 устанавливает следующее слово данных и тюБЧ Оряет пдкл записи. Это слово данных будет записано в 6jioK З со сдвигом Ki один адрес. Количество слов данн1,1х, записываемых в блок 3, ограничено разрядностью адреса. В данном устрсГштве память выполнена на мизфо- схомах КР541 РУ2 и позволяет записать 1024 слова данных.

После записи данньк в блок 3 в количестве 1024 слова или. менее ЭВМ устанавливает на втором разряде группы входов-выходов 17 единичное значение

29 включения коммз татора 13 и за- в блок 3. Слово данных будет засигнала коммугирует ЭВМ в блоку 3, а 45 и подает сигнал цепи 19 записи управ- Бнешнее устройство - к блоку 4.лякмцего слова в регистр В. Регистр 8

Выбор режима чтения или запи-си ;щя внешнего устройства онределяет цепи сигнала 66 блока 10 управления. Нулевьщяет сиг нал цепи 56 разреше1адя рабо ты с внешним устройством, который ус- тчнапзп .лает триггер 125. Сигнал инра 117, регистра 8 1 равления и блока 9 Tipaнления запросов. Единичное значение сигнала цепи 55 через блок 10 упра1-1леш1я устанавливает нулевое значение сигнала цепи 50 и, следовательно, ЭВМ тюдгглгочепа к блоку 3, а внешнее устройство - к блоку 4. Перед записью данньк ЭВМ устанавливает начальходон 17 и подает сигнал в цепь 22 установки адреса. Блок 10 управления. вырабатывает на выходе цепи 41 сигнал записи в счетчик 1. Затем ЭВМ снимает сигнал цепи 22, на группе входов-выходов 17 устанавливает слово данных и выдает сигн:ш цепи 24 записи данных. Блок 10 управления запоминает сигнал цепи 24 на элементах И-НЕ 100 и 101, лыццает сиги;ш на элементе НЕ 102, ко- горьш через элемент И-ИЛИ-НЕ 113 и НЕ 104 сигнал цени 40 инкремента счетчика 1, Одновременно сигнал цепи 24 посч упает на дешифратор 7 записи- чтения, дешифратор 7 вьщает сигнал цени 28 включения блока 3 и сигнал цепи писи писано в блок 3.

После этого ЭВМ CJiiiMaeT сигнал цепи 24, на группе входов-выходов 17 устанавливает следующее слово данных и тюБЧ Оряет пдкл записи. Это слово данных будет записано в 6jioK З со сдвигом Ki один адрес. Количество слов данн1,1х, записываемых в блок 3, ограничено разрядностью адреса. В данном устрсГштве память выполнена на мизфо- схомах КР541 РУ2 и позволяет записать 1024 слова данных.

После записи данньк в блок 3 в количестве 1024 слова или. менее ЭВМ устанавливает на втором разряде группы входов-выходов 17 единичное значение

29 включения коммз татора 13 и за- в блок 3. Слово данных будет завьщяет сиг нал цепи 56 разреше1адя работы с внешним устройством, который ус- тчнапзп .лает триггер 125. Сигнал ин

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

| Устройство для сопряжения двух вычислительных машин | 1986 |

|

SU1405064A1 |

| Устройство для сопряжения ЭВМ с каналом передачи данных | 1989 |

|

SU1647580A1 |

| Двухканальное устройство для сопряжения двух электронно-вычислительных машин | 1987 |

|

SU1481780A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1988 |

|

SU1520531A1 |

| Устройство для управления обменом информацией | 1987 |

|

SU1508219A1 |

| Устройство для сопряжения двух электронных вычислительных машин (эвм) | 1984 |

|

SU1187172A1 |

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1376091A1 |

| Устройство для сопряжения ЭВМ с датчиками | 1987 |

|

SU1427375A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве буфера данных в каналах ввода-вывода, в высокопроизводительных системах сбора и обработки данных. Целью изобретения является повышение быстродействия. Устройство содержит два блока памяти, блок управления, дешифратор записи-чтения, три счетчика, регистр управления, блок управления запросами, шесть коммутаторов, блок синхронизации. 2 з.п. ф-лы, 14 ил.

вое значеьше этого сигнала устанавли-59 версного выхода триггера 125 через

вает режим записи дан11ых из памяти во внешнее устройство.

Рассмотрим работу устройства, например, п реткиме передачи данных из ЭВМ во внешнее устройство. При включении питания сигнал цепи 20 устанавливает нулевое значение счетчика 6 и блока 16 синхронизации, через элемент НЕ 136 сигнал цепи 45 - триггеэлемепт И 135 сигна.юм цепи 54 приходит на блок 16 синхронизац11и и запускает одновибратор 143. Сигнал цепи 69 через элементы И-1ШИ-НЕ 114 и НЕ 107 сиг||ялом цепи 43 производит декремент Счетчика 6, который устанавливает все разряды в единичное состояние, и старший разряд сигналом 61 через элемент НЕ 127 устанавливает триггер элемен515151656

тов И-НЕ 128 и 129. Сигнал 68 черезпамятью , через элементы ШШ-НЕ 88

элемент ИЛИ 130 сигналом 44 поступает на вход записи счетчика бив счетчик 6 перезаписьтается через коммутатор 5 состояние шин счетчика 1 как длина передаваемых данных для блока 3.

По окончании действия сигнал цепи 68 запускает одновибратор 142, который стробирует триггер 138. После этого сигнал цепи 67 через элементы ИЛИ-НЕ 90 и И 132 сигналом 42 сбрасывает счетчик 1 и сбрасьшает элементы И-НЕ 128 и 129, который через элемент НЕ 108 сигналом цепи 49 стробирует триггер 117 и триггер 118. В результате блок 3 подключается к внешнему устройству, а блок 4 - к ЭВМ, триггер 117 устанавливает значение элемента И-НЕ 100 и 101, т.е. запись во внеш- нее устройство. Триггер 138 через коммутатор 137 изменением потенциала сигнала цепи 71 (либо 72) ввдает во внешнее устройство готовность обмена. Сигнал цепи 66 включает коммутатор 15, коммутирует в коммутаторе 137 сигналы управления записи во внешнее устройство и через коммутатор 81 и элемент И 83 сигналом цепи 28 включает блок 3. Слово данных устанавлива ется на группе входов-выходов 80.

При изменении потенциала сигнала цепи 75 с внешнего устройства сигнал цепи 67 запускает одновибратор 143, сигнал цепи 69 через элементы И-ИЛИ- НЕ 113 и НЕ 104 увеличивает адрес счетчика 1 и следующее слово данных устанавливается на группе входов-выходов 80. После этого одновибратор 142 стробирует триггер 138, сигнал цепи 67 обнуляется, изменяется потенциал сигнала цепи 71(72) и цикл обмена повторяется. При этом возможны две ситуации.

Ситуация 1 (фиг. 10). Передается максимальное количество слов данных для одного блока памяти (1024 слова). В этом случае при передаче последнего слова данных блока 3 установится единичное значение одиннадцатого раз- ряда счетчика 1 и двенадцатого разряд счетчика 6, сигнал цепи 27 через элементы НЕ 103, И-ИЛИ-НЕ 116, ИЛИ-НЕ 124 нулевым значением запрещает сигнал прекращения обмена данными, через 55 либо 4. Запись слова данных в соответэлемент И-ИЛИ-НЕ 113 запрещает инкремент счетчика 1. По сигна;.у цепи 44 состояние счетчика 2 переписывается в счетчик 6 как длина обмена данными с

и И-ИЛИ-НЕ 92 устанавливается триггер 95 и через элементы И-НЕ 97 и 99 сиг- нал цепи 63 сообщает ЭВМ о конц работы блока 3 с внешним устройством, а сигнал цепи 64 через коммутатор 11 сообщает ЭВМ номер памяти. После обнуления сигнала цепи 67 через элементы ИЛИ-НЕ 90 и И 133 сигнал цепи 39 обнуляет счетчик 2 адреса, сигнал цепи 49 стробирует триггер 117 и устанавливает режим блока памяти 4, сохраненный в элементах И-НЕ 100 и 101 (запись или чтение) стробирует триггер 118, который подключает блок 4 к внешнему устройству, а блок 3 - к ЭВМ. Далее процесс обмена данными продолжается с блоком 4 аналогично описанному.

Ситуация 2 (фиг. 11). Передается количество слов данных менее 1024 для одного блока памяти. В этом случае при передаче последнего слова данных блока 3 установится единичное значение только двенадцатого разряда счетчика 6, сигнал цепи 27 не сформируется. Сигнал цепи 63 через элемент ИЛИ- НЕ 124 разрешает прекращение обмена с внешним устройством на элементе И-ИЛИ НЕ 123 и инвертирует значение сигнала на элементе ИСКЛЮЧАЮПЩ ШШ 119. Сигнал цепи 44 перезаписьшает состояние счетчика 1 в счетчик 6 (длина обмена менее 1024 слов). Это необходимо для ЭВМ при передаче данных из внешнего устройства в ЭВМ для сигнала конца данных в не полностью заполненном блоке 3. Сигнал цепи 78 сбрасывает триггер 125 и на элементе И 135 задерживает выключение обмена с внешним устройством на время своего действия. После выключения обмена данными обнуление сигнала цепи 67 через элементы ИЛИ-НЕ 90 и И 132 сигналом цепи 42 обнуляет счетчик 1. Сигна цепи 49 стробирует триггеры 117 и 118. Обмен данными завершен.

При передаче данных от внешнего устройства к ЭВМ (режим Чтение) данные с входов-выходов 80 через коммутатор 13 либо 14 поступают на цепь 33, либо 35 соответствующего блока 3

ствующий блок памяти производится сигналом цепи 70 через элемент И 82 и коммутатор 81. Работа остальных элементов аналогична описанному.

При чтении данных из памяти в ЭВМ через коммутатор 12 на группу входов- выходов 17 признаком конца приема блока данных является сброс сигнала це- пи 63. При этом возможны три ситуации. Ситуация 3 (фиг. 12). Один блок памяти установил сигнал цепи 63 и он заполнен полностью (1024 слови данных) . В этом случае чтение данных в ЭВМ будет производиться, пока не установится в единичное состояние одиннадцатый разряд счетчика 1 либо 2 и сигнал цепи 27 либо 32 придет на элемент И-ИЛИ-НЕ 91 либо 93. Сигнал цепи 21 стробирования данных от ЭВМ через элемент ИЛИ-НЕ 86 либо 87 соединяется с сигналом цепи 47 обмена данными от ЭВМ и через элемент И-ИЛИ-НЕ 91 либо 93 сбросит триггер 95 либо 96 сообщений для соответствующего блока памяти. Сигнал цепи 63 будет сброшен.

Ситуация 4 (фиг. 13). Один блок памяти установил сигнал 63 и он заполнен не полностью (менее 1024 слов дан ньк). В этом случае при чтении данных в ЭВМ из памяти сигнал цепи 47 через элементы И-ИЛИ-НЕ 115 и НЕ 106 сигналом цепи 37 будет производиться декремент счетчика 6 длины, в котором бьиа сохранена информаи;ия о не полной длине заполнения памяти (см. ситуацию 2). При установлении единичного состояния сигнала цепи 61 от счетчика 6 сигнал цепи 21 через элемент ИЛИ-НЕ 86 либо 87 соединяется с сигналом цепи 48 и через элемент И-ИЛИ-НЕ 91 либо 93 сбросит триггер 95 либо 96 для соответствующего блока памяти. Сигнал цепи 63 будет сброшен.

Ситуация 5 (фиг. 14). Эта ситуация возможна только после завершения обмена данными. Оба блока памяти установили сигнал цепи 63. В этом случае сигналы цепи 64 и 65 через элемент ИСКЛЮЧАЮЩЕЕ ИШ1 121 обнуляют элемент И 122, который запирает сигнал цепи 47 на элемент И-ШШ-НЕ 115 и через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 120 запрещает переключение блоков памяти. ЭВМ работает с той же памятью. После сброса одного сигнала цепи 64 либо 65 (ЭВМ прочЛа данные из первого блока памяти полностью) сигнал на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 121 инвертируется, через элементы И 122 и ИСКЛЮЧАЮЩЕЕ ИЛИ 120 разрешается переключение блоков памяти и прохождение сигнала цепи 47. ЭВМ работает с другой памятью.

Продолжение работы описано в ситуации 4.

Формула изобретения

блока управления запросами является входом устройства для подключения к выходу стробирования данных ЭВМ, пятый вход логического условия блока управления является входом устройств для подключения к выходу стробирования адреса ЭВМ, шестой вход логического условия блока управления является входом устройства для подключения к первому выходу чтения ЭВМ, второй информационный вход дешифратора записи-чтения соединен с седьмым входом логического условия блока управления и является входом устройства для подключения к третьему выходу записи ЭВМ, восьмой вход логического условия блока управления соединен с первым управляющим входом четвертого коммутатора и является входом устрой- ства для подключения к второму выходу чтения ЭВМ, первый выход блока управления запросами является выходом устройства для подключения к первому входу готовности ЭВМ, второй выход блока управления запросами соединен с девятым входом логического условия блока управления и является выходом устройства для подключения к второму входу готовности ЭВМ, группа информа- ционных выходов пятого коммутатора соединена с вторыми группами информационных входов первого, второго коммутаторов и образует группу входов- выходов устройства для подключения к группе информационных входов внешнего устройства, первый, второй, третий четвертый входы запуска являются входами устройства для подключения соответственно к первому, второму строби- рующим выходам, к выходам готовности приема и передачи внешнего устройства, первый, второй, третий, четвертый синхровыходы блока синхронизации являются выходами устройства для под- ключения соответственно к первому, второму входам готовности приема, к первому, второму входам готовности передачи внешнего устройства, при этом старший разряд группы выходов первого счетчика соединен с вторым входом логического условия блока управления запросами и с первым информа ЦИОНН1Д4 входом шестого коммутатора,

второй информационный вход которого

соединен с третьим входом логического условия блока управления запросами и со старшим разрядом группы выходов второго счетчика, группа выходов ко- торого соединена с группой адресных входов второго блока памяти, синхро- вход которого соединен с первым выходом дешифратора записи-чтения, второй выход которого соединен с синхровхо- дом первого блока памяти, вход записи которого соединен с разрешающим входом первого коммутатора и с третьим выходом дешифратора записи-чтения, четвертый выход которого соединен с разрешающим входом второго коммутатор и с входом записи второго блока памяти, группа информационных входов-выходов которого соединена с первой группой информационных входов пятого коммутатора, с группой информационных выходов второго коммутатора, с первой группой информационных входов третьего коммутатора, вторая группа информационных входов которого соединена с группой информационных входов- выходов первого блока памяти, с группой информационных выходов первого коммутатора, с второй группой информационных входов пятого коммутатора, первый управляющий вход которого соединен с третьим информационным входом дешифратора записи-чтения, с пятым входом запуска блока синхронизации и с седьмым выходом блока управления, восьмой выход которого соединен с управляющими входами первого, второго коммутаторов, с вторыми управляющими входами третьего, пятого коммутаторов, с первым информационным входом четвертого коммутатора, с четвертым входом логического условия блока управления запросами, с четвертым информационным входом дешифратора записи-чтения, пятый инфор- мационньй вход которого соединен с пятым синхровыходом блока синхронизации и с десятым входом логического условия блока управления, одиннадцатый, двенадцатый,тринадцатый входы логического условия которого соединены соответственно с первым, вторым, третьим выходами регистра управления, четвертый, пятый выходы которого соединены соответственно с вторым, третьим информационными входами пятого коммутатора, группа информационных входов которого соединена с группой выходов третьего счетчика, старший разряд группы выходов которого соединен с чет ырнадцатым входом логического условия блока управления, девятый, десятый и одиннадцатый выходы которого соединены с четвертым, пятым информационными входами и с вторым управляющим входом пятого коммутатора, шестой информационный вход которого соединен с шестым синхровыходом блока синхронизации, с пятнадцатьм входом логического условия, с пятым входом логического условия блока управления запросами, шестой, седьмой, : восьмой, девятый входы логического условия и третий выход которого соединены соответственно с двенадцатым, тринадцатым, четырнадцатым, пятнадцатым выходами и с шестнадцатым входом логического условия блока управления, шестнадцатьй выход которого соединен со счетным входом третьего счетчика, информационный вход которого соединен с информационным выходом шестого ком- мутатора, управляющий вход которого соединен с семнадцатым выходом блока управления, восемнадцатый выход которого соединен с десятым входом логического условия блока управления за- просами и с установочным входом регистра управления, шестой выход которого соединен с одиннадцатым входом логического условия блока управления запросами, двенадцатый вход логическо го условия которого соединен с входом записи третьего счетчика и с девятнадцатым выходом блока зшравления, семнадцатый, восемнадцатый входы логического условия которого соединены соответственно с седьмым, восьмым син хровыходами блока синхронизации, шестой вход запуска которого соединен с двадцатым выходом блока управления, девятнадцатый вход логического уело- ВИЯ которого соединен с седьмым информационным входом четвертого коммутатора и с четвертым выходом блока управления запросами, пятый выход которого соединен с восьмым информационным вхо дом четвертого коммутатора и с двадцатым входом логического условия блока управления.

входом логического условия блока, вход седьмого элемента НЕ является четвертым входом логического условия блока, второй вход первого элемента И-НЕ соединен с вторым входом второго элемента И-НЕ и является пятым входом логического условия блока, первый вход третьего элемента И является шестым входом логического уело- ВИЯ блока, второй вход третьего элемента И-НЕ соединен с первым входом восьмого элемента И-НЕ и является седьмым входом логического условия блока, второй вход третьего элемента И является восьмым входом логического условия блока, второй вход шестог,о элемента И-НЕ соединен с первым входом элемента ИЛИ-НЕ и является девяты входом логического условия блока, пер вый и второй входы пятого элемента И-ИЛИ- НЕ являются десятым входом логического условия блока, первый вход второго элемента ИЛИ, синхровход второго триггера, третий вход пятого эле мента И-ИЛИ-НЕ, вход десятого элемента НЕ, второй вход пятого элемента И-НЕ являются соответственно одиннадцатым - пятнадцатым входами логического условия блока, второй вход пер- вого элемента И соединен с вторым входом второго элемента И и является шестнадцатым входом логического условия блока, первый вход первого элемента ИЛИ является семнадцатым входом логического условия блока, четвертый вход первого элемента ri-ИЛИ-НЕ соединен с четвертым входом второго элемента И-ИЛИ-НЕ, с вторым, третьим входами четвертого элемента И-ИЛИ-НЕ и явля- ется восемнадцатым входом логического условия блока, первый, второй входы третьего элемента ИСКЛЮЧАЮР(ЕЕ ИЛИ являются соответственно девятнадцатым, двадцатым входами логического условия блока, при этом в блоке управления выход седьмого элемента И-НЕ соединен с вторым входом восьмого элемента И-НЕ, выход которого соединен с

вторым входом седьмого элемента И-НЕ

и с информационным входом первого триггера, выход восьмого элемента НЬ соединен с пятым входом третьего элемента И-ИЛИ-НЕ, с пятым, шестым входами первого элемента И-ИЛИ-НЕ, выход которого соединен с входом первого элемента НЕ, вход пятого элемента НЕ соединен с выходом второго элемента И-ИЛИ-НЕ, пятый, шестой входы которо QJ5 2о 5 0 Qj 5

0

5

го соединены с выходом девятого элемента НЕ и с шестым входом третьего элемента И-ИЛИ-НЕ, выход которого соединен с вторым входом элемента Ш1И-НЕ, выход которого соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с четвертым входом пятого элемента И-ИЛИ-НЕ, выход которого соединен с первым входом четвертого элемента И и с нулевым входом второго триггера, нулевой выход которого соединен с вторым входом четвертого элемента И, вход второго элемента.НЕ соединен с выходом четвертого элемента И-ИЛИ-НЕ, четвертый которого соединен с выходом пятого элемента И и с первьм входом первого элемента ИСКГООЧАЮЩЕЕ ИЛИ, второй вход которого соединен с единичным выходом третьего триггера, нулевой выход которого соединен с вторым входом второго элемента ИСКЛО- ЧАЮЩЕЕ ИЛИ, выход третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторым входом пятого элемента И, выход шестого элемента И-НЕ соединен с нулевым входом третьего триггера и с вторым входом второго элемента ИЛИ, выход которого соединен с единичным входом третьего триггера, выход шестого элемента НЕ соединен с вторым входом второго элемента И, выход десятого элемента НЕ соединен с первым входом четвертого элемента И-НЕ, второй вход которого соединен с вторым входом первого элемента ИЛИ и с выходом пятого элемента И-НЕ, информационный и единичный входы второго триггера, единич- ньш вход первого триггера подключены к шине единичного пот.снциала устройства.

блока, первьй вход первого элемента И-НЕ Соединен с вторыми, третьими входами первого, третьего элементов И-ИЛИ-НЕ и является седьмым входом логического условия блока четвертый вход первого элемента И-ИЛИ-НЕ соединен с вторыми входами второго, четвертого элементов И-ИЛИ-НЕ, с четвертым входом третьего элемента И-ИЛИ НЕ и является восьмым входом логичес- кого условия блока, второй вход четвертого элемента ИЛИ-НЕ является девятым входом логического условия блока, синхровход первого триггера соединен с синхровходом второго триггера и является десятым входом логического условия блока, первый вход второго элемента И-НЕ является одиннадцатым входом логического условия блока, второй вход третьего элемента ИЛИ-НЕ соединен с вторым входом пятого элемента ШШ-НЕ и является двенадцатым входом логического условия блока, выходы первого, второго элементов И-НЕ, выход четвертого элемента ИЛИ-НЕ, единичные выходы второго и первого триггеров являются соответственно первым, вторым, третьим, четвертым и пятым выходами блока, при этом в блоке управления запросами выход первого элемента ИЛИ-НЕ соединен с пятым и шестым входами первого элемента И-ИЛИ-НЕ, выход которого соединен с нулевым входом первого триггера, единичный вход которого соединен с выходом второго элемента И-ИЛИ-НЕ, третий и четвертый входы которого соединены с выходом пятого элемента ИЛИ-НЕ, выход второго элемента ИЛИ-НЕ соединен с пятым и шестым входами третьего элемента И- ИЛИ-НЕ, выход которого соединен с нулевым входом второго триггера, единичный вход которого соединен с выходом четвертого элемента .И-ИЛИ-НЕ, третий и четвертый входы которого соединены с выходом третьего элемента ИЛИ-НЕ, вторые входы первого, второго элементов И-НЕ соединены с выходом третьего элемента И-НЕ, первьй и второй входы которого соединены с нулевыми выходами первого и второго триггеров соответственно, информационные входы которых подключены к шине нулевого потенциала устройства.

Фиг.2

Фиг.З

г2 516€ 36 56

г

Фив. 5

/P.

5 Ж

w

Й

..o/ror

Фиад

33

Фиг,9

Фиг.ц

Фиг./4

| Устройство для управления обменом | 1983 |

|

SU1151976A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обмена данными между оперативной памятью и внешним устройством | 1984 |

|

SU1180908A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-10-15—Публикация

1987-10-16—Подача