Изобретение относится к автоматике и вычислительной технике и может быть использовано в измерительных .устройствах различного назначения.

Цель изобретения - повышение точности работы устройства.

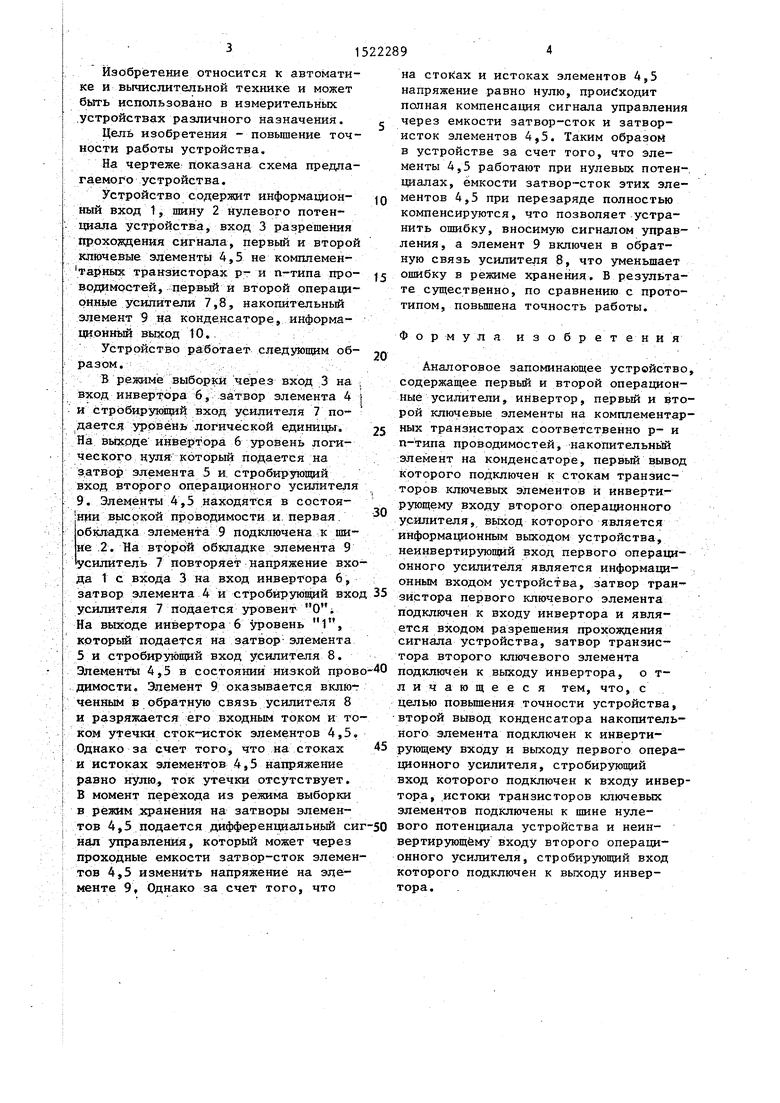

На чертеже: доказана схема предлагаемого устройства.

Устройство содержит информацион- ный вход 1, шину 2 нулевого потенциала устройства, вход 3 разрешения ирохозвдения сигнала, первьй и второй ключевые элементы 4,5 не комплемен- тарных транзисторах р- и п-типа про- водимостей, первьй и второй операционные усилители 7,8, накопительный элемент 9 на конденсаторе, информационный выход 10.

Устройство работает следующим образом. ;..: ; .. , .. .;,, :, , / .

В режиме выборки через ВХОД 3 на вход инвертора 6, затвор элемента 4 и стробируЮщий вход усилителя 7 подается уррвёнь логической едини1р г. На выходе инвертора 6 уровень логического нуля: который подается на з.атвор элемента 5 и. стробщ ующий вход второго операционного усилителя 9. Элементы 4,5 находятся в состоянии высокой проводимости и. первая . обкладка элемента 9 подключена к шине .2. На второй обкладке элемента 9 усилитель 7 повторяет напряжение входа 1 с входа 3 на вход инвертора 6, затвор элемента 4 и стробирующий вхо усилителя 7 подается уровент На выходе инвертора 6 уровень 1, которьй подается на затвор элемента 5 и стробирующий вход усилителя 8. Элементы 4,5 в состоянии низкой пров димости. Элемент 9 оказывается включенным в обратную связь усилителя 8 и разряжается его входным током и током утечки сток-исток элементов 4,5 Однако за счет того, что на стоках и истоках элементов 4,5 напряжение равно нулю, ток утечки отсутствует. В момент перехода из режима выборки в режим хранения на затворы элементов 4,5 подается дифференциальньй си нал управления, которьгй может через проходные емкости затвор-сток элементов 4,5 изменить напряжение на эле менте 9 Однако за счет того, что

0

5

е

о

50

0

35

40

45

на стоках и истоках элементов 4,5 напряжение равно нулю, происходит полная компенсация сигнала управления через емкости затвор-сток и затвор- исток элементов 4,5. Таким образом в устройстве за счет того, что элементы 4,5 работают при нулевых потен-, циалах, ёмкости затвор-сток этих элементов 4,5 при перезаряде полностью компенсируются, что позволяет устранить ошибку, вносимую сигналом управления, а элемент 9 включен в обратную связь усилителя 8 что уменьшает ошибку в режиме хранения. В результате суш;ественно, по сравнению с прототипом, повьшена точность работы.

Формула изобретения

Аналоговое запоминающее устройство, содержащее первьй и второй операдаон- ные усилители, инвертор, первый и второй ключевые элементы на комплементарных транзисторах соответственно р- и п-типа проводимостей, -накопительный элемент на конденсаторе, первый вывод которого подключен к стокам транзисторов ключевых элементов и инвертирующему входу второго Операционного усилителя, выход которого является информационным выходом устройства, неинвертирующий вход первого операционного усилителя является информационным входом устройства, затвор транзистора первого ключевого элемента подключен к входу инвертора и является входом разрешения прохождения сигнала устройства, затвор транзистора второго ключевого элемента подключён к выходу инвертора, о т- ли чающееся тем, что, с целью повьш1ения точности устройства, второй вывод конденсатора накопительного элемента подключен к инвертирующему входу и выходу первого опера- 1ЩОННОГО усилителя, стробирую1щй вход которого подключен к входу инвертора, истоки транзисторов ключевых элементов подключены к шине нулевого потенциала устройства и неин- вертирующёму входу второго операда- онного усилителя, стробирующий вход которого подключен к выходу инвертора.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДАТЧИК КОНТРОЛЯ НИТИ | 1993 |

|

RU2062748C1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU858110A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU920843A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU841057A1 |

| Усилитель считывания | 1981 |

|

SU1015435A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| ГЕНЕРАТОР ИМПУЛЬСНЫХ НАПРЯЖЕНИЙ | 2017 |

|

RU2682015C1 |

| Буферный усилитель (его варианты) | 1983 |

|

SU1112409A1 |

| Узловой элемент сеточной модели для решения задач тепломассопереноса | 1988 |

|

SU1522246A1 |

| Динамический усилитель считывания на МДП-транзисторах | 1986 |

|

SU1336101A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в измерительных устройствах различного назначения. Цель изобретения - повышение точности устройства. Достигается за счет того, что схема включения ключевых элементов 4, 5 на комплементарных транзисторах работает при нулевых потенциалах стока и истока. Это позволяет скомпенсировать влияние синфазного напряжения. Накопительный элемент 9 на конденсаторе включен в обратную связь операционного усилителя 8, что уменьшает его токи утечки. 1 ил.

| Апексеенко А.Г | |||

| и др | |||

| Применение прецизионных аналоговьк микросхем | |||

| М.: Радио и связь, 1985, с | |||

| Кран машиниста для автоматических тормозов с сжатым воздухом | 1921 |

|

SU194A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Хоровиц П | |||

| и др.Искусство схемотехники | |||

| - М.: Мир, 1983, ч | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ модулирования для радиотелефонии | 1923 |

|

SU409A1 |

Авторы

Даты

1989-11-15—Публикация

1988-03-04—Подача