Фиг. 1

Изобретение относится к вычислительной технике и может быть использовано в устройствах контроля полупроводниковых оперативных устройство

Цель изобретения - повышение достоверности контроля устройств

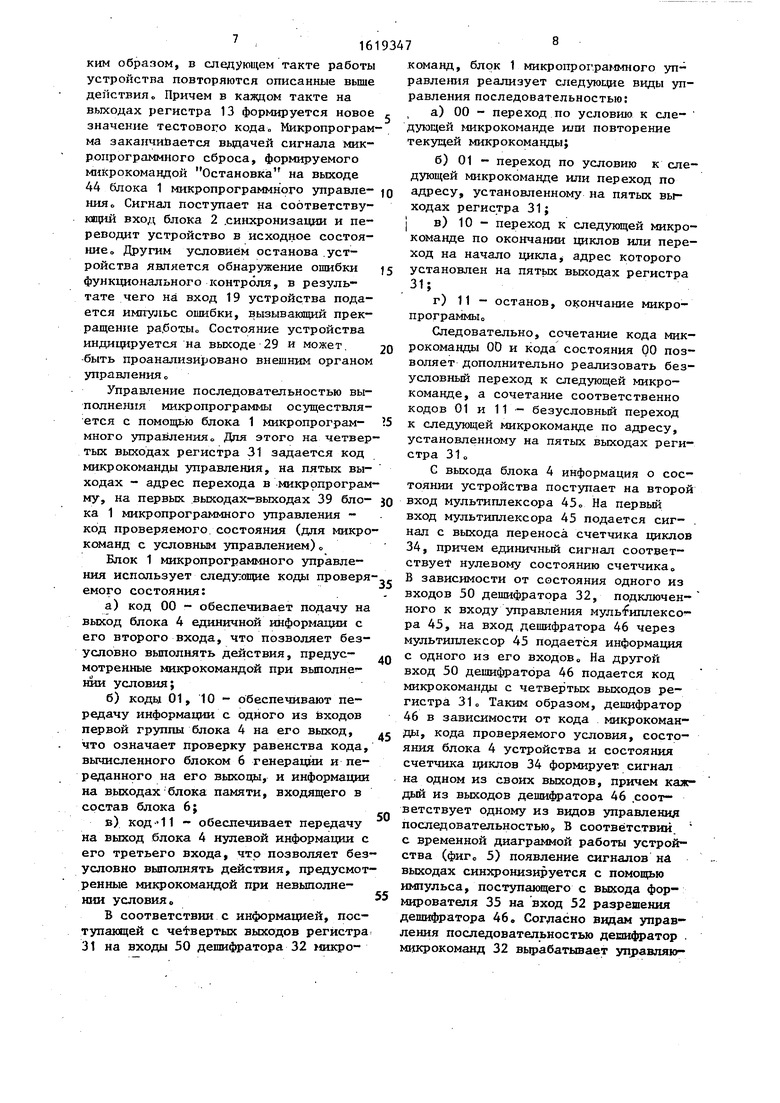

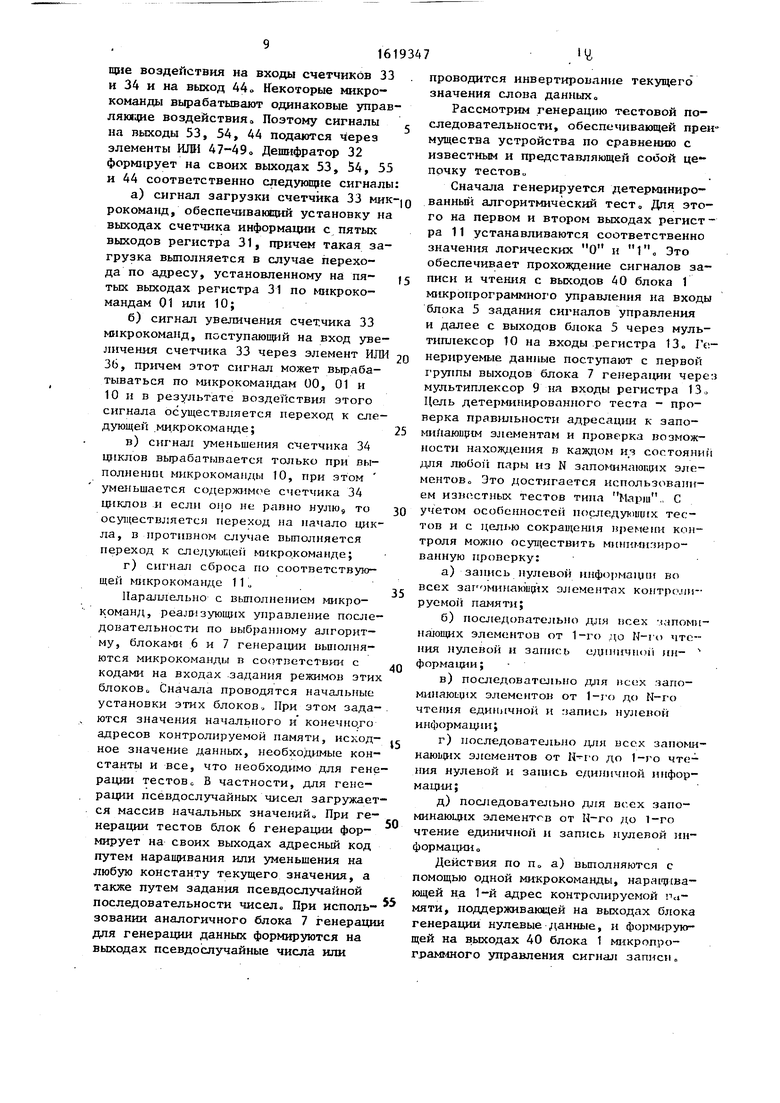

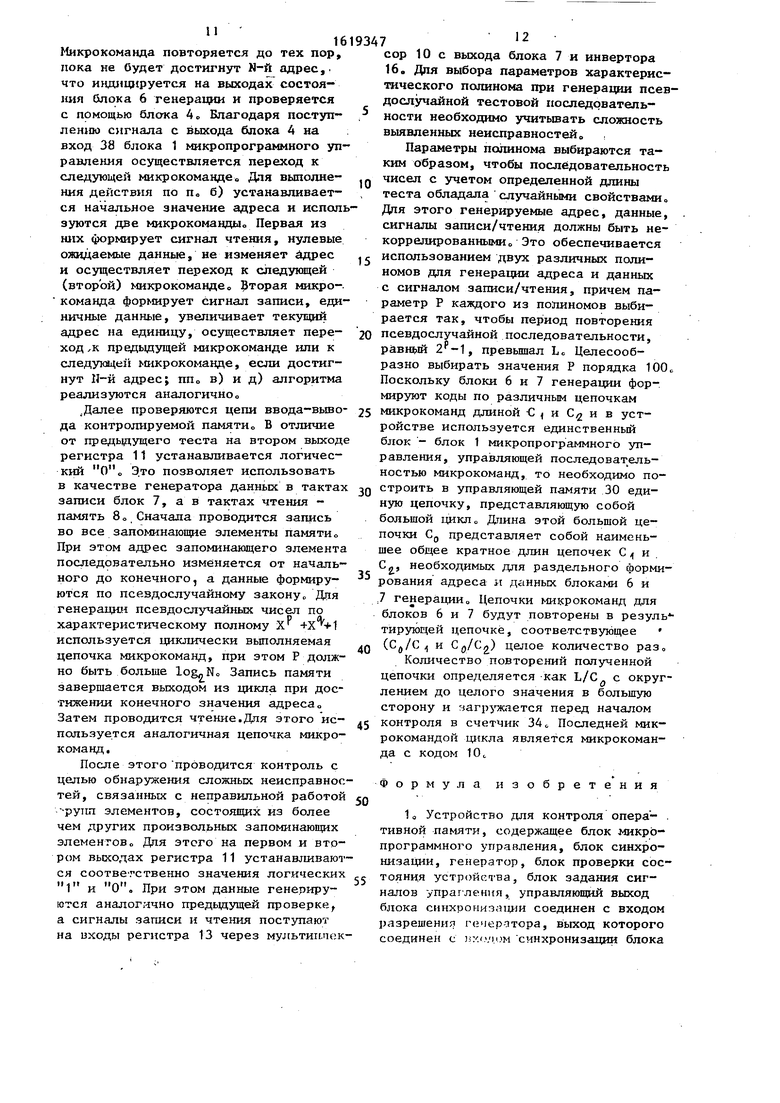

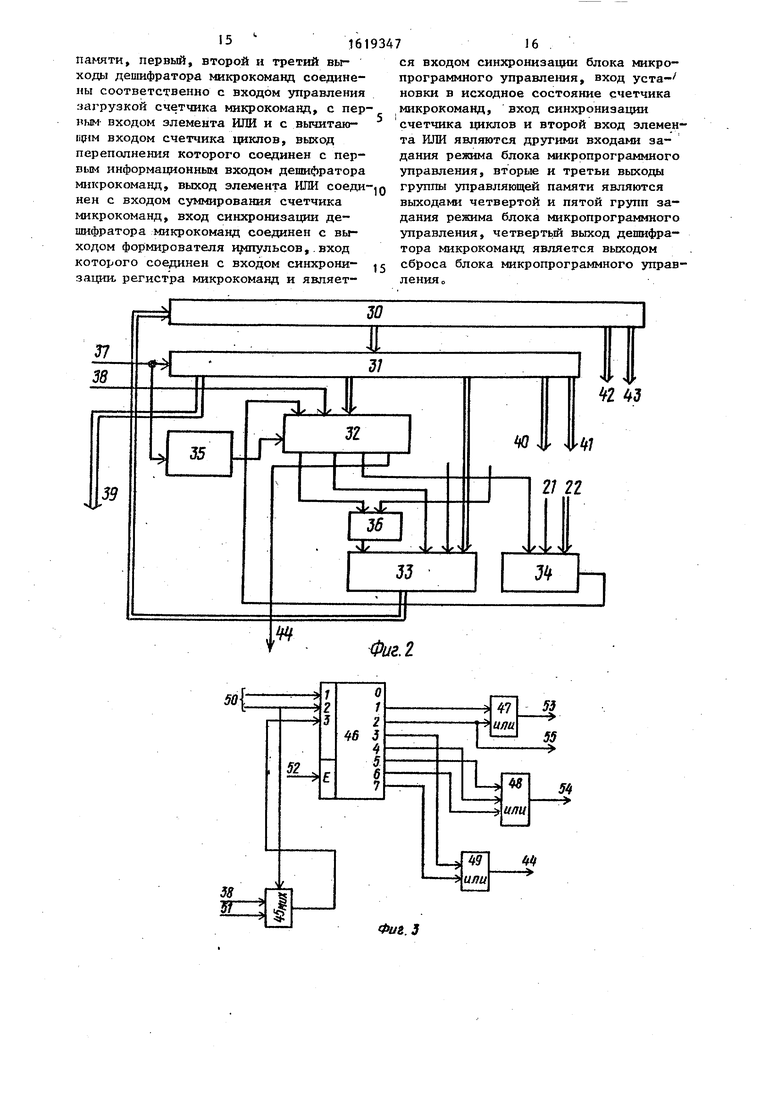

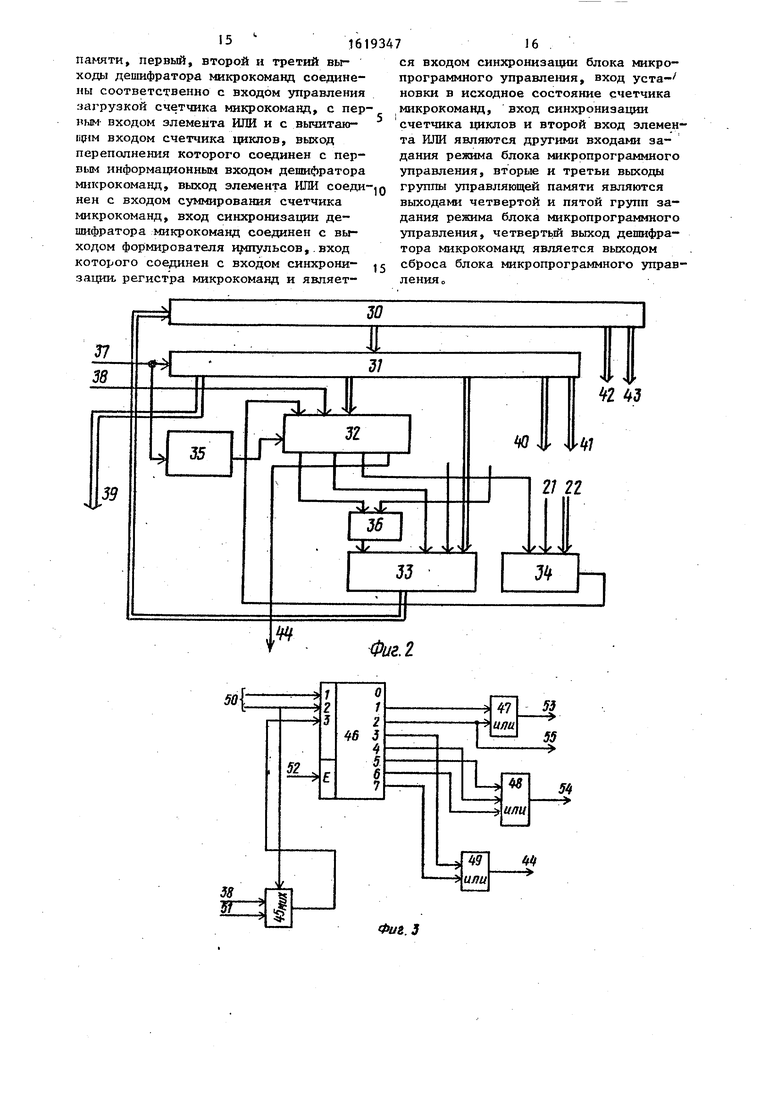

На фиго 1 представлена структурная схема устройства; на фиг 2 - структурная схема блока микропрограммного управления; на фиг0 3 - структурная схема дешифратора микрокоманд; на фиг 4 - структурная схема генератора периода; на фиг„ 5 - временная диаграмма работы устройства

Устройство содержит блок 1 микропрограммного управления, блок 2 синхронизации, генератор 3, блок 4 проверки состояния устройства, блок 5 задания сигналов управления, первый 6 и второй 7 блоки генерации, блок 8 памяти, первый 9 и второй 10 мультиплексоры, регистр 11 режима, элемент ИЛИ 12, выходной регистр 13, формирователь 14 импульсов, элемент И 15, инвертор 16, входы запуска 17 и сброса 18 устройства, вход 19 сброса уст- ройства по ошибке, входы 20-23 задания режима устройства, входы 24 зада- ния режима, адресные выходы 25, ин- формационные выходы 26, выходы 27 записи, выходы 28 чтения, выход 29 сос- тояния

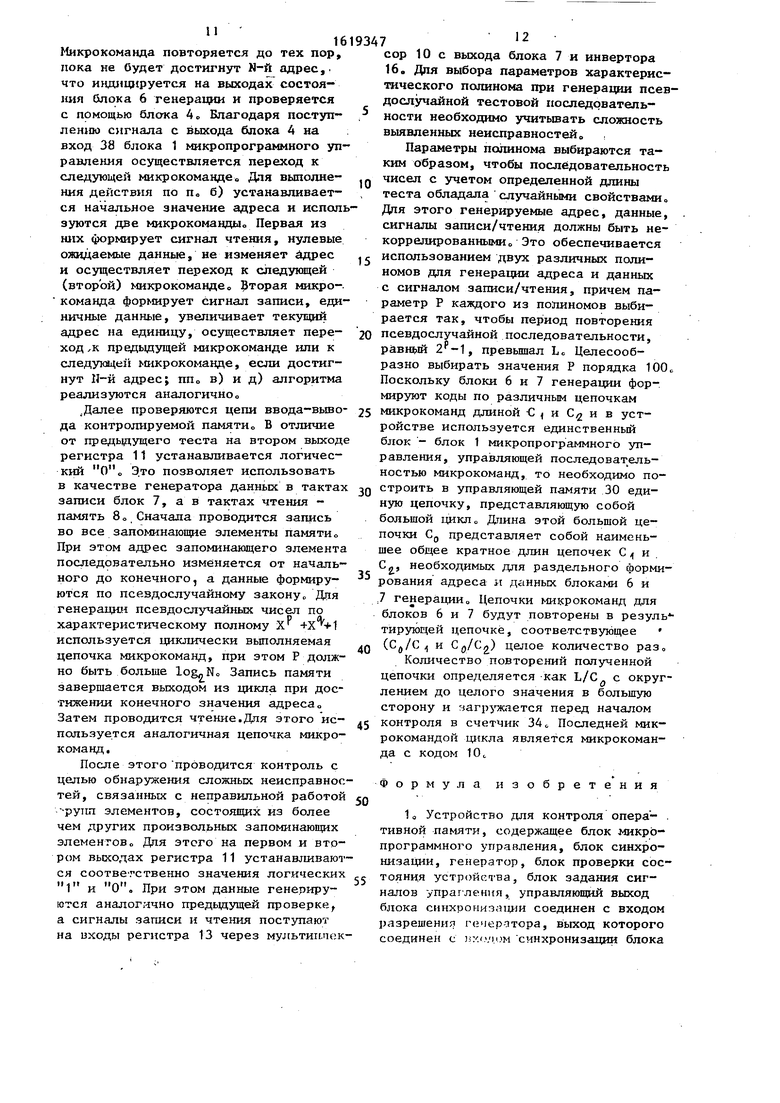

Блок 1 микропрограммного управления содержит узел памяти 30, регистр 31 микрокоманд, дешифратор 32 микрокоманд, счетчик 33 микрокоманд, счетчик 34 циклов, формирователь 35 импульсов, элемент ИЛИ 36, вход 37 синхронизации, вход 38, вход 20 сброса счетчика микрокоманд, вход 21 загрузки счетчика циклов, информационные входы 22 счетчика циклов, вход 23 наращивания адреса управляющей памяти, 39-44 выходы блока микропрограмм- ного управленияо

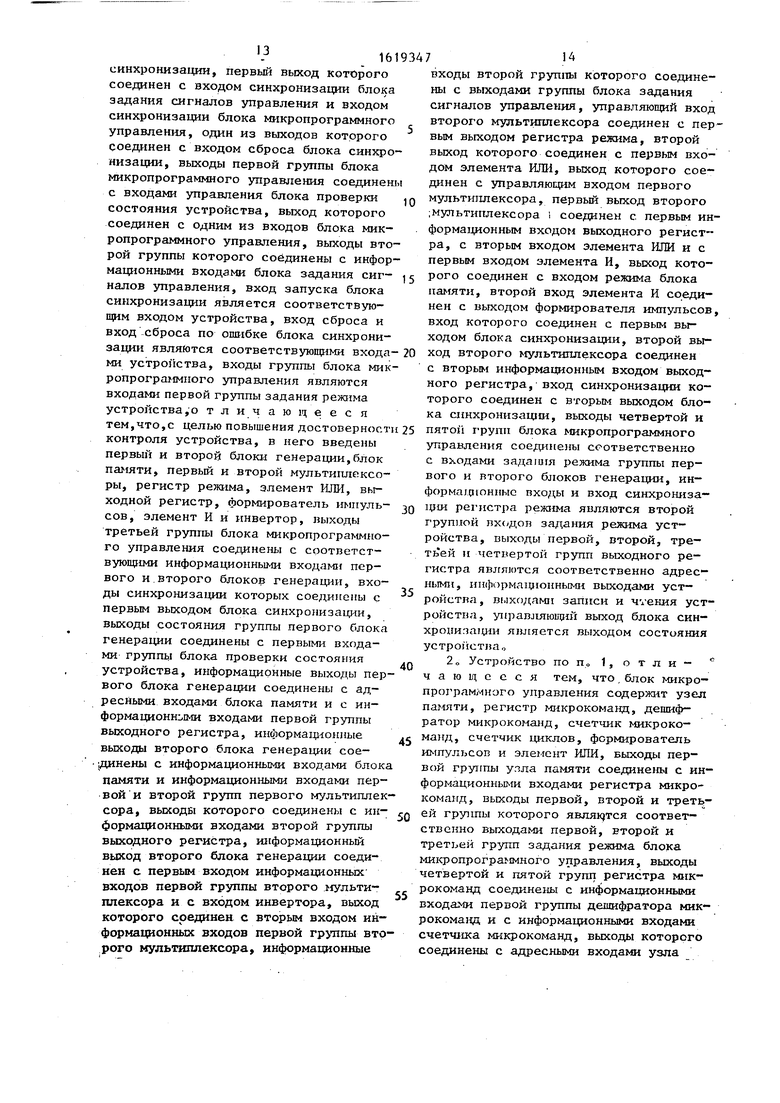

Дешифратор 32 микрокоманд содержит мультиплексор 45, деинфратор 46,элементы ИЛИ 47-49, информационные входы 50 первой группы дешифратора, информационный вход 51 дешифратора, вход 52 синхронизации дешифратора, выходы с 53 по 550

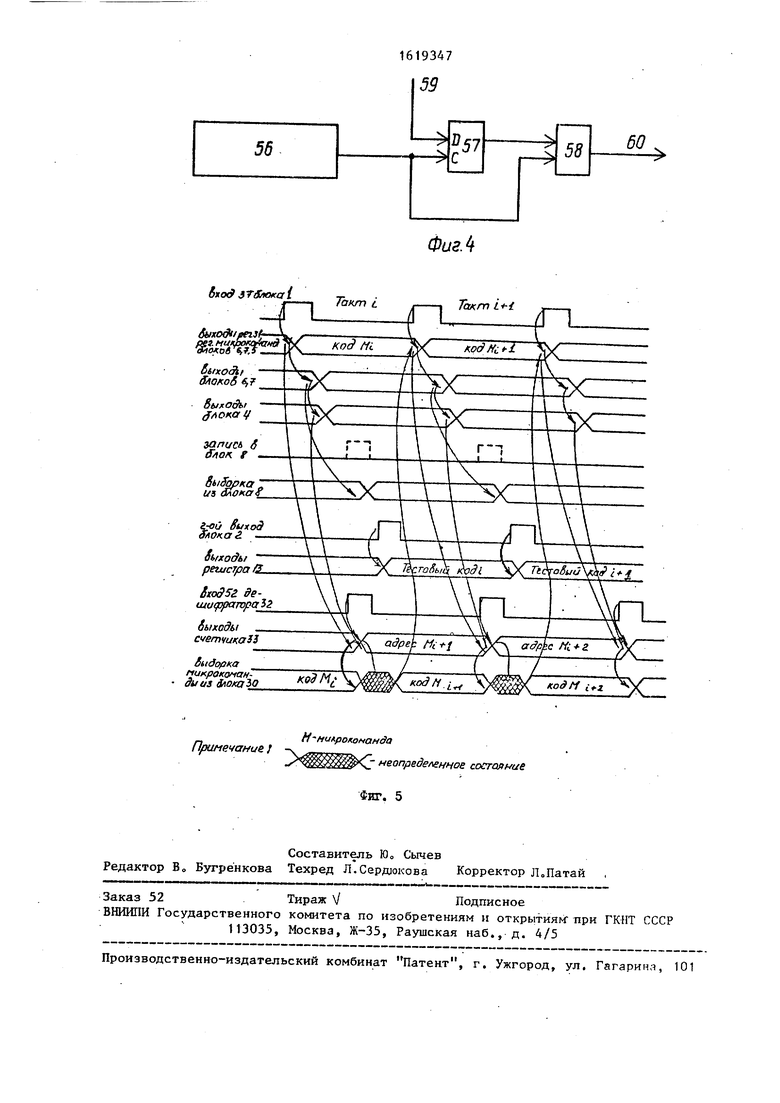

Генератор 3 содержит генератор 56, триггер 57, элемент И 58

Управление работой устройства может осуществляться любым из известных способов, в том числе с помощью ЭВМ, для чего должен использоваться соот

o

Q ,-

5

0

ветствующий интерфейс, преобразующий машинные команды в информационные и необходимые сигналы управления При этом информационные сигналы могут подаваться на информационные входы регистра 11, счетчика 34, управляющей памяти 30 (не показаны)0 Сигналы управления могут обеспечивать запись информации на входах перечисленных блоков, а также воздействовать на устройство через входы 17, 18,20, 23 и 21о

В начале работы устройства его необходимо привести в исходное состояние „ Для этого подается импульс на вход 18 блока 2 синхронизации, в результате чего на его управляющем выходе устанавливается логический нуль, который передается на вход 59 генератора 3 Очередным импульсом с выхода генератора 56 на вход синхронизации триггера 57 нулевая информация с входа триггера передается на его выход и препятствует прохождению импульсов через элемент И 58 на выходе 60 генератора 3, Ввиду отсутствия импульсов на входе синхронизации блока 2 синхронизации на выходах его синхронизирующие импульсы не вырабатываются Это обеспечивает поддержание блоков устройства в исходном состоянии

Устройство генерирует тестовые последовательности по микропрограмме, предварительно загруженной в узел памяти 30о

Загрузка в узел памяти 30 производится последовательно, начиная с нулевого адреса, причем каждое слово памяти представляет собой одну микрокоманду Установка нулевого адреса производится сигналом, поступающим на вход 20, который сбрасывает счетчик 33 микрокоманд в нулевое состояние Наращивание адреса памяти 30 при ее загрузке производится сигналом, поступающим на вход 23 Проходя с второго входа элемента ИЛИ 36 на вход наращивания счетчика 33, сигнал обеспечивает задание следующего адре- са на входах памяти 30 После завершения загрузки микропрограммы вновь осуществляется сброс счетчика 33 сигналом с входа 20 Это обеспечивает последующее выполнение микропрограммы, начиная с нулевого адреса 30 памяти При необходимости через входы 21 и 22 устанавливается начальное

состояние счетчика циклов 34 блока 1 микропрограммного управления

С помощью загрузки информации в регистры 11 через входы 24 задается режим работы устройства Запуск работы устройства осуществляется подачей импульса на вход 17 блока 2 синхронизации. Это вызывает появление на его управляющем выходе логической 1, поступающей на вход 59 разрешения генератора 3 Тем самым обеспечивается запись единичного сигнала в триггер 57 по переднему фронту первого импульса, поступившего с выхода геиера- тора 56 на его вход синхронизации„ После этого сигнал с выхода триггера 57 разрешает прохождение тактовых импульсов на выход 60 через элемент И 58 о Тактовые импульсы поступают на вход синхронизации блока 2 синхронизации, вызывая появление на его выходах синхросигналов в соответствии с временной диаграммой работы устройства Периодическое появление на выхода блока 2 синхронизации сигналов, синхронизирующих блоки устройства, обеспечивает работу устройства по тактам в соответствии с загруженной микропрограммой, при этом в каждом такте осуществляется выборка и выполнение микрокомандыо Вначале проводится выборка кода микрокоманды из памяти 30 по адресу, определяемому состоянием на выходах счетчика 33„ Импульсом, поступившим с первого выхода блока 2 синхронизации на входы синхронизации блоков;1, 5, 6 и 7, информация с выходов памяти 30 записывается соответственно с регистр 31, в блок 5 злда- ния сигналов управления и в регистры микрокоманд блоков 6 и 7 генерации, которые формируют очередные значения адресов и данных0 Коды сигналов записи и чтения непосредственно передаются на выходы блока . 5 задания сигналов управления„ В зависимости от состояния на первом выходе регистра 11 режима, второй мультиплексор 10 передает на входы выходного регистра 13 в качестве сигналов записи н чтения сигналы с выходов блока 5 задания -сигналов управления, либо сигналы с второго выхода блока 7 генерации и выхода инвертора 1б„ Адресные сигналы с выходов блока 6 генерации поступают на первые входы регистра 13 а также на адресные входы блока 8 памяти Способ формирования данных на

$ 0 5 0 о

5

вторых входах регистра 13 определяется режимом управления мультиплексора 9. Заданная на втором выходе регистра

11логическая 1 через элемент НИИ

12поступает на вход управления мультиплексора 9„ Этим обеспечивается прохождение данных с выходов блока 7 генерации на выходы мультиплексора 9„ Другой режим формирования данных реализуется при наличии на втором выходе регистра 11 логического В этом режиме единичный сигнал с первого выхода мультиплексора 10, синхронизированный импульсом с выхода формирователя 14, поступает через элемент И 15 на вход записи блока 8 памяти, Тем самым в тактах записи обеспечивается запись в блок 8 памяти информации, поступающей с выходов блока 7, по адресу, который с выходов блока 6 подается на адресные входы блока 8„ Одновременно сигнал с первого выхода мультиплексора 9 обеспечивает подключение выходов блока 7 через мультиплексор 9 на входы регистра 13„ При отсутствии сигнала записи (в тактах чтения) мультиплексор 9 осуществляет подачу на входы регистра 13 информации с выходов блока 8 памяти„ В этом случае в качестве данных используется информация, записанная ранее по адресу, определяемому блоком 6о В конце такта работы устройства импульсом с второго выхода блока 2 осуществляется запись информации в регистр и передача ее на выходы 25-28 устройства , Кроме того,

в текущем такте информация о состоянии блока 6, фиксирующая совшщение текущего адреса с заранее определенными величинами, поступает на первые входы блока 4„ В соответствии с кодом, установленным на входах управления блока 4 на выход блока 4 и далее на вход 38 блока 1 микропрограммного управления поступает информация с одного из входов блока 4„ Адрес микрокоманды, подлежащий выполнению в слЈ дующем такте работы устройства, определяется информацией на четвертых и пятых выходах регистра 31, текущим состоянием счетчика 33, состоянием выхода переноса счетчика 34 и информацией на входе 38 блока 1 микропрограммного управления о Заданный таким способом адрес следующей микрокоманды записывается в счетчик 33 о Далее проводится выборка кода микрокоманды из памяти 30 и последующая запись в регистр 31, Та

ким образом, в следующем такте работы устройства повторяются описанные выше действия Причем в казвдом такте на выходах регистра 13 формируется новое значение тестового кода. Микропрограмма заканчивается выдачей сигнала микропрограммного сброса, формируемого микрокомандой Остановка на выходе 44 блока 1 микропрограммного управления Сигнал поступает на соответствующий вход блока 2 синхронизации и переводит устройство в исходное состояние. Другим условием останова устройства является обнаружение ошибки функционального контроля, в результате чего на вход 19 устройства подается импульс ошибки, вызывающий прекращение работы Состояние устройства индицируется на выходе 29 и может быть проанализировано внешним органом управления

Управление последовательностью выполнения микропрограммы осуществляется с помощью блока 1 микропрограммного управления Для этого на четвертых выходах регистра 31 задается код микрокоманды управления, на пятых выходах - адрес перехода в микропрограмму, на первых выходах-выходах 39 бло- ка 1 микропрограммного управления - код проверяемого состояния (для микрокоманд с условным управлением).

Блок 1 микропрограммного управления использует следугощие коды проверяемого состояния:

а)код 00 - обеспечивает подачу на выход блока 4 единичной информации с его второго входа, что позволяет безусловно выполнять действия, предусмотренные микрокомандой при выполнении условия;

б)коды 01, 10 - обеспечивают передачу информации с одного из входов первой группы блока 4 на его выход, что означает проверку равенства кода, вычисленного блоком 6 генерации и переданного на его выходы, и информации на выходах блока памяти, входящего в состав блока 6;

в)код-11 - обеспечивает передачу на выход блока 4 нулевой информации с его третьего входа, что позволяет безусловно выполнять действия, предусмотренные микрокомандой при невыполнении условия,

В соответствии с информацией, поступающей с четвертых выходов регистра 31 на входы 50 дешифратора 32 микро

0

5

0

5

5

JQ

40

45

50

5

команд, блок 1 микропрограммного управления реализует следующие виды управления последовательностью:

а) 00 - переход по условию к следующей микрокоманде или повторение текущей микрокоманды;

б) 01 - переход по условию к следующей микрокоманде или переход по адресу, установленному на пятых выходах регистра 31;

j в) 10 - переход к следующей микрокоманде по окончании циклов или переход на начало цикла, адрес которого установлен на пятых выходах регистра 31;

г) 11 - останов, окончание микропрограммы о

Следовательно, сочетание кода микрокоманды 00 и кода состояния 00 позволяет дополнительно реализовать безусловный переход к следующей микрокоманде, а сочетание соответственно кодов 01 и 11 - безусловный переход к следующей микрокоманде по адресу, установленному на пятых выходах регистра 31.

С выхода блока 4 информация о состоянии устройства поступает на второй вход мультиплексора 45. На первый вход мультиплексора 45 подается сигнал с выхода переноса счетчика циклов 34, причем единичный сигнал соответствует нулевому состоянию счетчика В зависимости от состояния одного из входов 50 дешифратора 32, подключен- ного к входу управления мультиплексора 45, на вход дешифратора 46 через мультиплексор 45 подается информация с одного из его входов. На другой вход 50 дешифратора 46 подается код микрокоманды с четвертых выходов регистра 31. Таким образом, дешифратор 46 в зависимости от кода микрокоманды, кода проверяемого условия, состояния блока 4 устройства и состояния счетчика циклов 34 формирует сигнал на одном из своих выходов, причем каждый из выходов дешифратора 46 .соответствует одному из видов управления последовательностью, В соответствий с временной диаграммой работы устройства (фиго 5) появление сигналов на выходах синхронизируется с помощью импульса, поступающего с выхода формирователя 35 на вход 52 разрешения дешифратора 46. Согласно видам управления последовательностью дешифратор микрокоманд 32 вырабатывает управляю

щие воздействия на входы счетчиков 33 и 34 и на выход 44 Некоторые микрокоманды вырабатывают одинаковые управляющие воздействия Поэтому сигналы на выходы 53, 54, 44 подаются через элементы ИЛИ 47-49 Дешифратор 32 формирует на своих выходах 53, 54, 55 и 44 соответственно следующие сигналы

а)сигнал загрузки счетчика 33 МИК рокоманд, обеспечивающий установку на выходах счетчика информации с пятых выходов регистра 31, причем такая загрузка выполняется в случае перехода по адресу, установленному на пя- тых выходах регистра 31 по микрокомандам 01 или 10;

б)сигнал увеличения счетчика 33 микрокоманд, поступающий на вход увеличения счетчика 33 через элемент ИЛИ ЗЬ, причем этот сигнал может вырабатываться по микрокомандам 00, 01 и

10 и в результате воздействия этого сигнала осуществляется переход к следующей микрокоманде;

в)сигнал уменьшения счетчика 34 циклов вырабатывается только при выполнении микрокоманды 10, при этом уменьшается содержимое счетчика 34 циклов и если оно не равно нулю, то осуществляется переход на начало цикла, в противном случае выполняется переход к следующей микрокоманде;

г)сигнал сброса по соответствующей микрокоманде 11„

Параллельно с выполнением микрокоманд, реализующих управление последовательности по выбранному алгоритму, блоками 6 и 7 генерации выполняются микрокоманды в соответствии с кодами на входах задания режимов этих блоков о Сначала проводятся начальные установки этих блоков, При этом задаются значения начального и конечного адресов контролируемой памяти, исход- ное значение данных, необходимые константы и все, что необходимо для генерации тестов с В частности, для генерации псевдослучайных чисел загружается массив начальных значений При генерации тестов блок 6 генерации формирует на своих выходах адресный код путем наращивания или уменьшения на любую константу текущего значения, а также путем задания псевдослучайной последовательности чисел При исполь- зовании аналогичного блока 7 генерации для генерации данных формируются на выходах псевдослучайные числа или

0

5

Q 5

0

,-

5

0

0

проводится инвертирование текущего значения слова данных

Рассмотрим генерацию тестовой последовательности, обеспечивающей преимущества устройства по сравнению с известным и представляющей собой цепочку тестов„

Сначала генерируется детерминированный алгоритмический тест Для этого на первом и втором выходах регист - ра 11 устанавливаются соответственно значения логических О и Это обеспечивает прохождение сигналов записи и чтения с выходов 40 блока 1 микропрограммного управления на входы блока 5 задания сигналов управления и далее с выходов блока 5 через мультиплексор 10 на входы регистра 13. Генерируемые данные поступают с первой группы выходов блока 7 генерации через мультиплексор 9 на входы регистра 13 Цель детерминированного теста - проверка правильности адресации к запоминающим элементам и проверка возможности нахождения п каждом из состояний для любой пары из N запоминающих элементов Это достигается использованием известных тестов типа Марш С учетом особенностей последующих тестов и с целью сокращения времени контроля можно осуществить миншшчиро- ванную проверку:

а)запись нулевой информации во всех запоминающих элементах контролируемой памяти;

б)последовательно для нсех члпомн- нающих элементов от 1-го цо N-Iо чтения нулевой и запись единичном ин- ч формации;

в)последовательно для псох чапо- минаюцих элементов от 1-го до N-го чтения единичной и чапись нулевой информации;

г)последовательно для ыссх запоминающих элементов от N-го до 1-го чтения нулевой и запись единичной информации;

д)последовательно для всех запоминающих элементов от Н-го до 1-го чтение единичной и запись нулевой информации о

Действия по п а) выполняются с помощью одной микрокоманды, наращивающей на 1-й адрес контролируемой памяти, поддерживающей на выходах блока генерации нулевые данные, и формирующей на выходах 40 блока 1 микропрограммного управления сигнал записи.

11

Микрокоманда повторяется до тех пор, пока не будет достигнут N-й адрес, что инддцнруется на выходах состояния блока 6 генерации и проверяется с помощью блока 4„ Благодаря поступ- лешоо сигнала с выхода блока 4 на вход 38 блока 1 микропрограммного управления осуществляется переход к следующей микрокоманде„ Для выполнения действия по п« б) устанавливается начальное значение адреса и используются две микрокоманды., Первая из них формирует сигнал чтения, нулевые ожидаемые данные, не изменяет адрес и осуществляет переход к следующей (второй) микрокомандео Эторая микро- команда формирует сигнал записи, единичные данные, увеличивает текущий адрес на единицу, осуществляет перехода предыдущей микрокоманде или к следующей микрокоманде, если достигнут 11-й адрес; пп0 в) и д) алгоритма реализуются аналогичное

1619347

с 1 ти

, н в

к

.0 ч т си к

.г и н с р р

20 п р р По ми

12

сор 10 с выхода блока 7 и инвертора 16. Для выбора параметров характеристического полинома при генерации псевдослучайной тестовой последрвательности необходимо учитывать сложность выявленных неисправностей,,

Параметры полинома выбираются таким образом, чтобы последовательность

0 чисел с учетом определенной длины теста обладала случайными свойствами„ Для этого генерируемые адрес, данные, сигналы записи/чтения должны быть некоррелированными о Это обеспечивается

г использованием двух различных полиномов для генерации адреса и данных с сигналом записи/чтения, причем параметр Р каждого из полиномов выбирается так, чтобы период повторения

0 псевдослучайной последовательности, равный 2Р-1, превышал Lo Целесообразно выбирать значения Р порядка 100„ Поскольку блоки 6 и 7 генерации формируют коды по различным цепочкам

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1170457A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Устройство управления контролем | 1985 |

|

SU1285471A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство управления | 1989 |

|

SU1654820A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах контроля полупроводниковых оперативных запоминающих устройств Цель изобретения а повышение достоверности контроля устройства „ Устройство содержит блок 1 микропрограммного управления, блок 2 синхронизации, генератор 3, блок 4 проверки состояния устройства, блок 5 задания сигналов управления, первый 6 и второй 7 блоки генерации, блок 8 памяти, первый 9 и второй 10 мультиплексоры, регистр 11 режима, элемент ИЛИ 12, выходной регистр 13, формирователь 14 импульсов, элемент И 15, инвертор 16, ход 17 запуска и вход 18 сброса устройства, вход 19 сброса устройства по ошибке, входы 20-24, адресные выходы 25, информационные выходы 26, выходы 27 записи и выходы 28 чтения,выход 29 состояния, 1 з.п, ф-лы, 5 ил„ -10 с S (Л с 24 с& 5 со V

Далее проверяются цепи ввода-выво- 25 микрокоманд длиной € f и С2 и в уст- да контролируемой памяти В отличие ройстве используется единственный от предыдущего теста на втором выходе блок - блок 1 микропрограммного управления, управляющей последовательностью микрокоманд, то необходимо по30

регистра 11 устанавливается логический Это позволяет использовать

в качестве генератора данных в тактах записи блок 7, а в тактах чтения - память 8о Сначала проводится запись во все запоминающие элементы памяти При этом адрес запоминающего элемента последовательно изменяется от начального до конечного, а данные формируются по псевдослучайному закону„ Для генерации псевдослучайных чисел по характеристическому полному X +Х%-1 используется циклически выполняемая цепочка микрокоманд, при этом Р должно быть больше lognNo Запись памяти завершается выходом из цикла при достижении конечного значения адреса Затем проводится чтение.Для этого используется аналогичная цепочка микрокоманд.

После этого проводится контроль с целью обнаружения сложных неисправностей, связанных с неправильной работой сп рупп элементов, состоящих из более чем других произвольных запоминающих элементов„ Для этого на первом и втором выходах регистра 11 устанавливаются соответственно значения логических 1 и О. При этом данные генерируются аналогично предыдущей проверкеt а сигналы записи и чтения поступают на входы регистра 13 через мультишшк35

40

45

55

строить в управляющей памяти 30 единую цепочку, представляющую собой большой цикл о Длина этой большой цепочки С0 представляет собой наименьшее общее кратное длин цепочек С ц к С, необходимых для раздельного формирования адреса и данных блоками 6 и 7 генерациио Цепочки микрокоманд для

блоков 6 и 7 будут повторены в резуль тирующей цепочке, соответствующее

(СЙ/С4 и ) целое количество раз„

Количество повторений полученной цепочки определяется как L/C с округлением до целого значения в большую сторону и загружается перед началом контроля в счетчик 340 Последней микрокомандой цикла является микрокоманда с кодом 10,,

Формула изобретения

1 о Устройство для контроля оперативной памяти, содержащее блок микропрограммного управления, блок синхронизации, генератор, блок проверки состояния устройства, блок задания сигналов упрагления, управляющий выход блока синхрониоации соединен с входом разрешения геиерптора, выход которого соединен с ьхс/тм синхронизации блока

0

п

5

0

5

5

строить в управляющей памяти 30 единую цепочку, представляющую собой большой цикл о Длина этой большой цепочки С0 представляет собой наименьшее общее кратное длин цепочек С ц к С, необходимых для раздельного формирования адреса и данных блоками 6 и 7 генерациио Цепочки микрокоманд для

блоков 6 и 7 будут повторены в резуль - тирующей цепочке, соответствующее

(СЙ/С4 и ) целое количество раз„

Количество повторений полученной цепочки определяется как L/C с округлением до целого значения в большую сторону и загружается перед началом контроля в счетчик 340 Последней микрокомандой цикла является микрокоманда с кодом 10,,

Формула изобретения

1 о Устройство для контроля оперативной памяти, содержащее блок микропрограммного управления, блок синхронизации, генератор, блок проверки состояния устройства, блок задания сигналов упрагления, управляющий выход блока синхрониоации соединен с входом разрешения геиерптора, выход которого соединен с ьхс/тм синхронизации блока

131619

синхронизации, первый выход которого соединен с входом синхронизации блока задания сигналов управления и входом синхронизации блока микропрограммного управления, один из выходов которого соединен с входом сброса блока синхронизации, выходы первой группы блока микропрограммного управления соединены с входами управления блока проверки состояния устройства, выход которого соединен с одним из входов блока микропрограммного управления, выходы второй группы которого соединены с информационными входами блока задания сиг- налов управления, вход запуска блока синхронизации является соответствующим входом устройства, вход сброса и вход сброса по ошибке блока синхронизации являются соответствующими входа- ми устройства, входы группы блока микропрограммного управления являются входами первой группы задания режима устройства,о тличающееся тем,что,с целью повышения достоверности контроля устройства, в него введены первый и второй блоки генерации,блок памяти, первый и второй мультиплексоры, регистр режима, элемент ИЛИ, выходной регистр, формирователь импульсов, элемент И и инвертор, выходы третьей группы блока микропрограммного управления соединены с соответствующими информационными входами первого и второго блоков генерации, входы синхронизации которых соединены с первым выходом блока синхронизации, выходы состояния группы первого блока генерации соединены с первыми входами группы блока проверки состояния устройства, информационные выходы первого блока генерации соединены с адресными входами блока памяти и с информационными входами первой группы выходного регистра, информационные выходы второго блока генерации соединены с информационными входами блока памяти и информационными входами первой и второй групп первого мультиплексора, ВЫХОДЕ которого соединены с ни- формационными входами второй группы выходного регистра, информационный выход второго блока генерации соединен с первым входом информационных входов первой группы второго мультиплексора и с входом инвертора, выход которого соединен с вторым входом информационных входов первой группы второго мультиплексора, информационные

Q 5 0 5 Q

0

5

40

5

5

714

входы второй группы которого соединены с выходами группы блока задания сигналов управления, управляющий вход второго мультиплексора соединен с первым выходом регистра режима, второй выход которого соединен с первым входом элемента ИЛИ, выход которого соединен с управляющим входом первого мультиплексора, первый выход второго .мультиплексора . соединен с первым информационным входом выходного регистра, с вторым входом элемента ИЛИ и с первым входом элемента И, выход которого соединен с входом режима блока памяти, второй вход элемента И соединен с выходом формирователя импульсов, вход которого соединен с первым выходом блока синхронизации, второй выход второго мультиплексора соединен с вторым информационным входом выходного регистра, вход синхронизации которого соединен с вторым выходом блока синхронизации, выходы четвертой и пятой групп блока микропрограммного управления соединены соответственно с входами задания режима группы первого и второго блоков генерации, информационные входы и вход синхронизации регистра режима являются второй группой входов задания режима устройства, выходы первой, второй, третьей и четвертой групп выходного регистра являются соответственно адресными, информационными выходами устройства , выходами записи и устройства, упрапляюьцш выход блока син- хроцитации является выходом состояния устройства.,

2 Устройство по п„ отличающееся тем, что блок микропрограммного управления содержит узел памяти, регистр микрокоманд, дешифратор микрокоманд, счетчик микрокоманд, счетчик циклов, формирователь импульсов и элемент ИЛИ, выходы первой группы уша памяти соединены с информационными входами регистра микрокоманд, выходы первой, второй и третьей группы которого является соответственно выходами первой, второй и третьей групп задания режима блока микропрограммного управления, выходы четвертой и пятой групп регистра микрокоманд соединены с информационными входами первой группы дешифратора микрокоманд и с информационными входами счетчика микрокоманд, выходы которого соединены с адресными входами узла

памяти, первый, второй и третий выходы дешифратора микрокоманд соединены соответственно с входом управления загрузкой счетчика микрокоманд, с первым входом элемента ИЛИ и с вычитаю- ii(HM входом счетчика циклов, выход переполнения которого соединен с первым информационным входом дешифратора микрокоманд, выход элемента ИЛИ соеди нен с входом суммирования счетчика микрокоманд, вход синхронизации дешифратора микрокоманд соединен с выходом формирователя импульсов, вход которого соединен с входом синхронизации, регистра микрокоманд и являет

5

ся входом синхронизации блока микропрограммного управления, вход уста-/ новки в исходное состояние счетчика микрокоманд, вход синхронизации счетчика циклов и второй вход элемента ИЛИ являются другими входами задания режима блока микропрограммного управления, вторые и третьи выходы группы управляющей памяти являются выходами четвертой и пятой групп задания режима блока микропрограммного управления, четвертый выход дешифратора микрокоманд является выходом сброса блока микропрограммного управления

&хо& ЗТ&юка I

Такт i

&ход5г де- щифратуроЪё

быходы

SudopKO микрокоманды из ЗлокаЪО

Примечание J

Н нифокоманда

j- нео Фяг. 5

I ,

кодМ t ЧХГГ

j- неопределенное состояние Фяг. 5

| Устройство для контроля оперативной памяти | 1984 |

|

SU1231540A1 |

Авторы

Даты

1991-01-07—Публикация

1989-02-20—Подача