Изобретение от1юси ся к вычислительной технике и может быть испол;.:. аовано для проверки работоспособ ности оперативной памяти на интегральных микросхемах при массовом их производстве или для входного контр ля оперативной памяти.

Цель изобретения -- повьшгение быстродействия и упрощение устройства ,

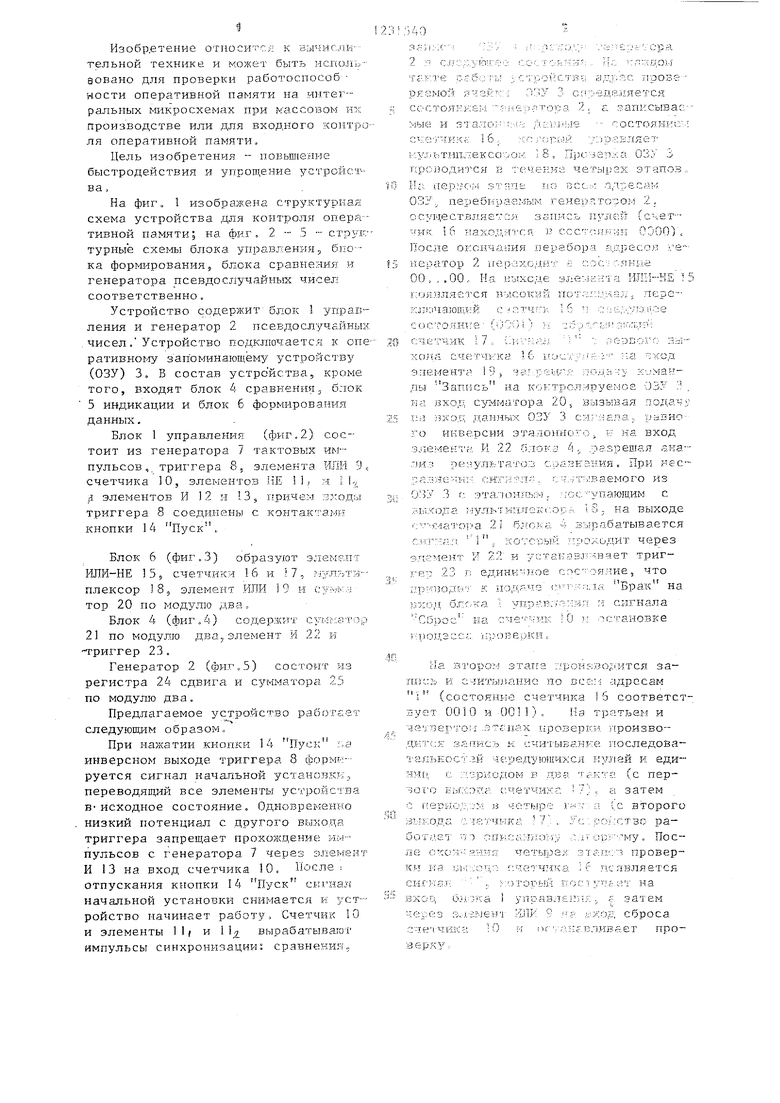

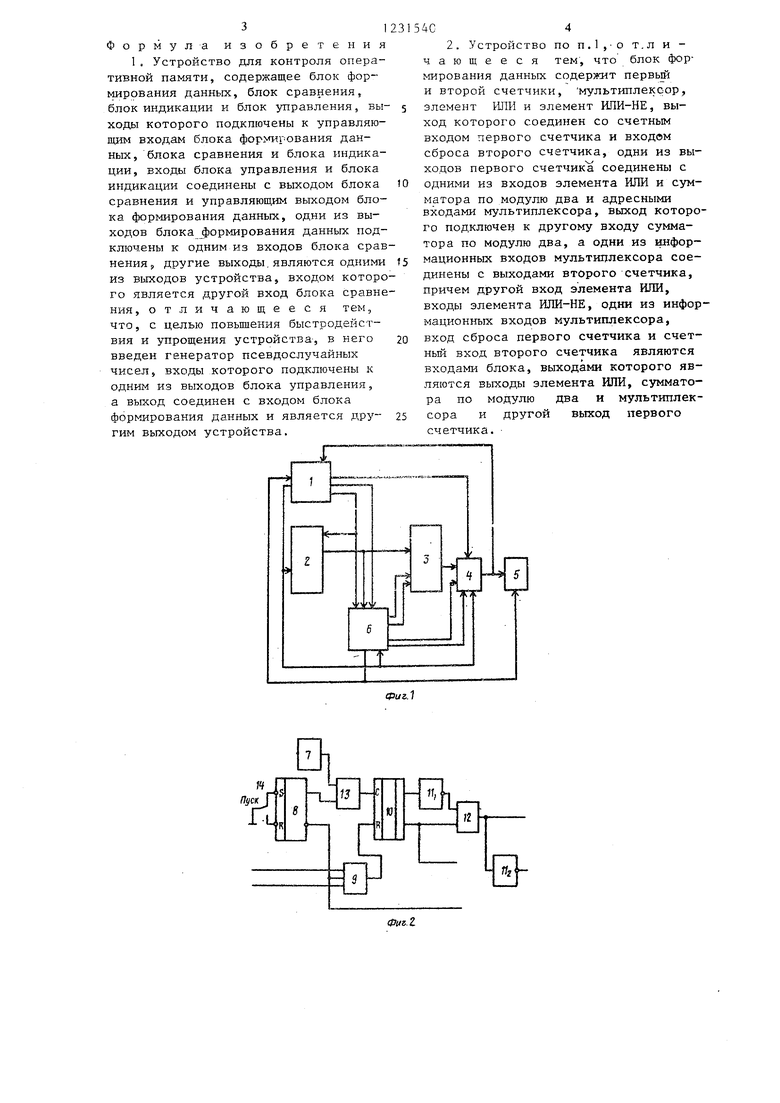

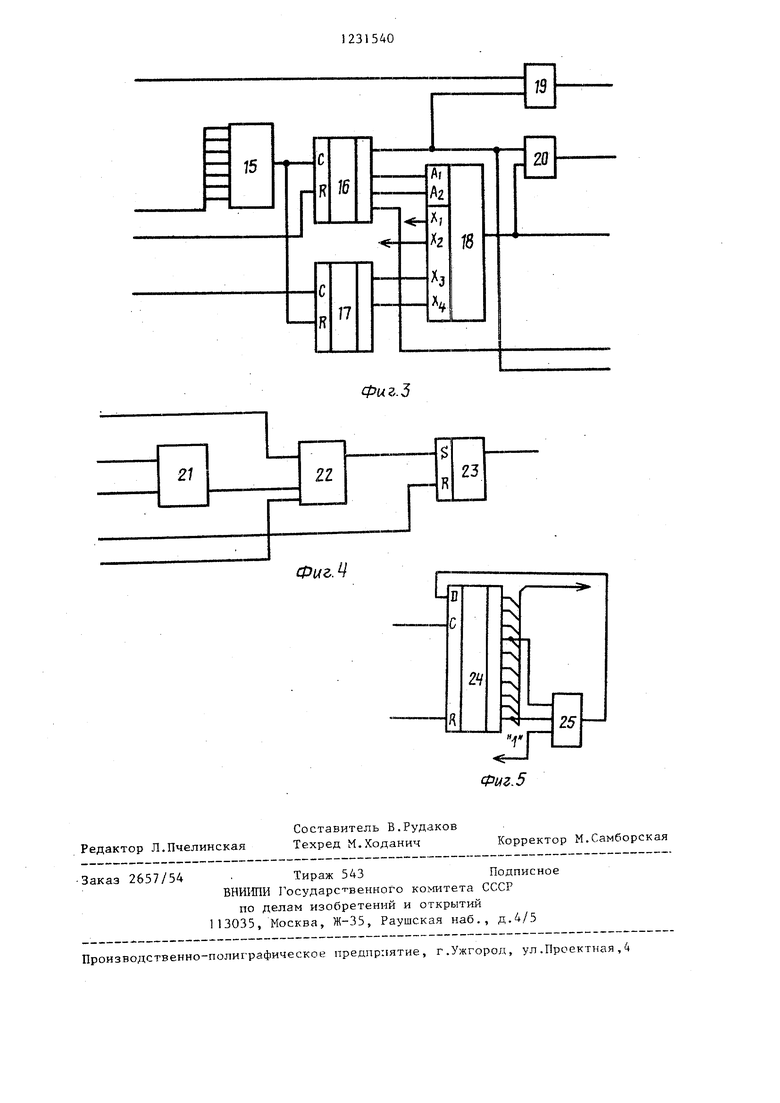

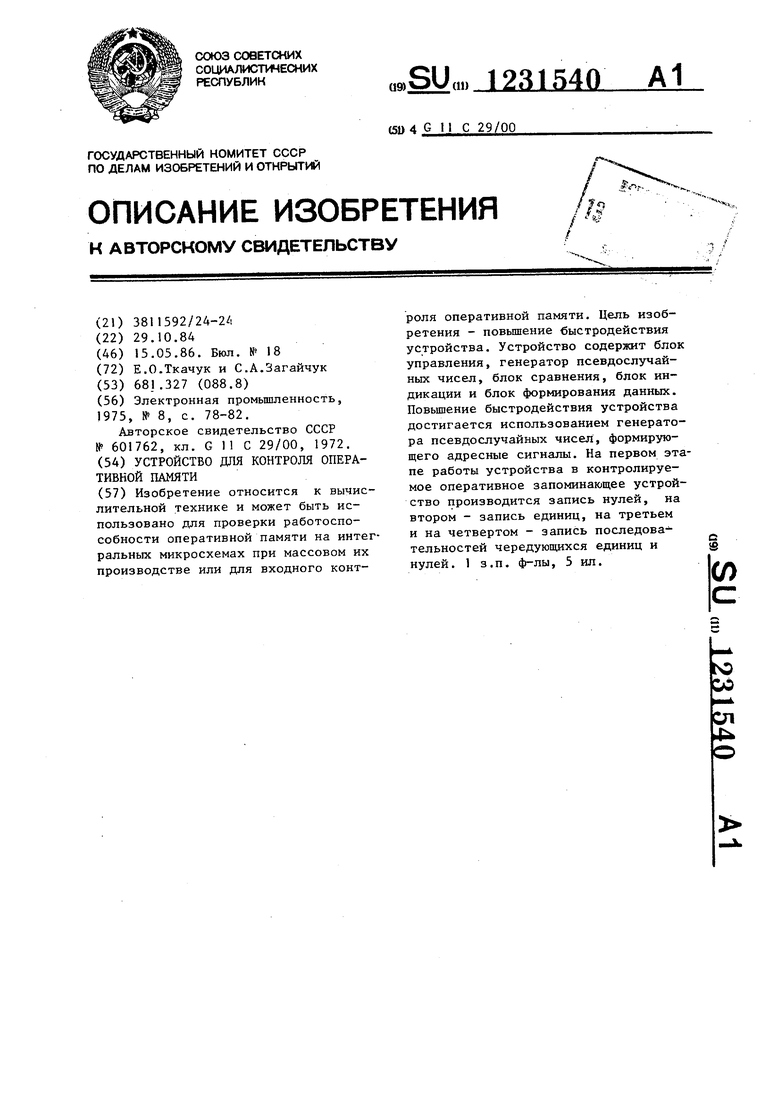

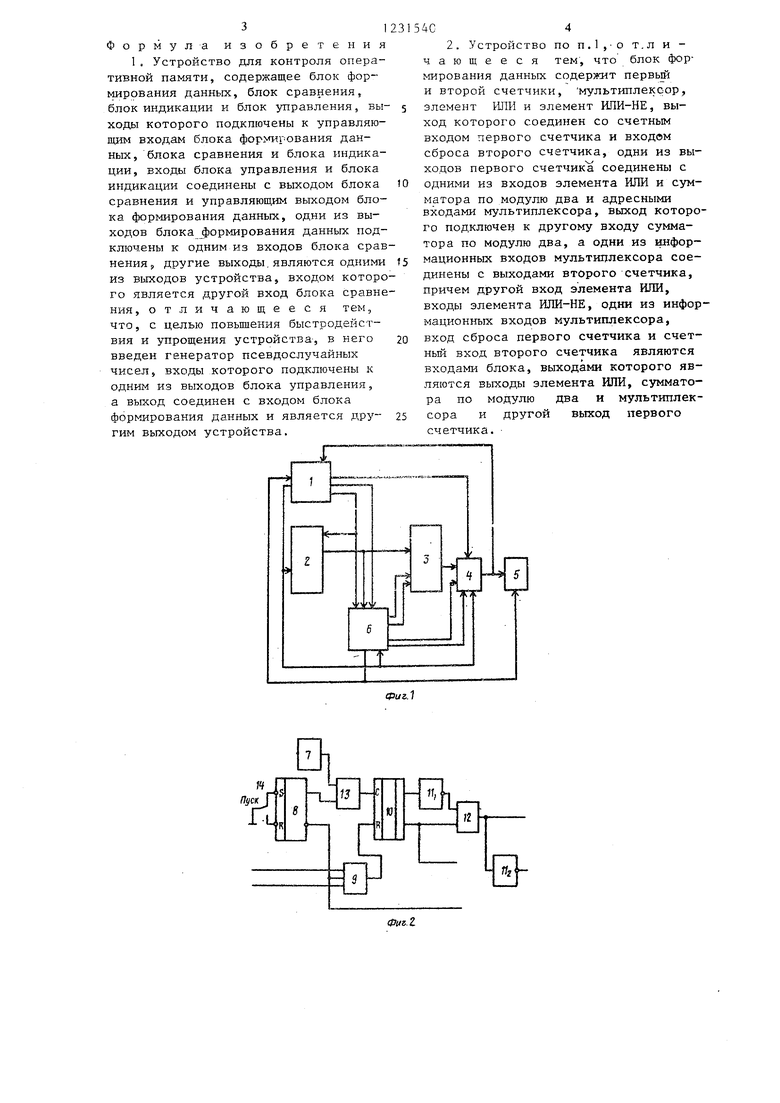

На фиг. 1 изображена структурная схема устройства для контроля опера тивной памяти; на фиг. 2 - 5 - струк турные блока управлен5 я, бпо-- ка формирования, блока сравнения и генератора псевдослучайных чисел соответственно.

Устройство содержит блок 1 управления и генератор 2 псевдослучайны , чисел. Устройство подключается к он ративног-гу заноминающемз устройству (ОЗУ) 3. В состав устройства, кроме того, входят блок 4 сравнения, 6:ioK 5 индикации и блок 6 формирования данных,

Блок 1 управления (фиг.2) состоит из генератора 7 тактовых им-- пульсов, триггера 8, элемента ИЛИ 9 счетчика 10, элементов НЕ П, и j; i-,- fi элементов И 12 и 13, г-ричем зходы триггера 8 соединены с контактам : кнопки 14 Пуск,,

Блок 6 (фиг.З) образуют элеме.пт ИЛИ-НЕ 15, счетчики 16 и 57, глуллти- плексор 18з элемент ИЛИ 19 и .ч тор 20 по модулю два

Блок 4 (фиг.4) содержит суг- катор 21 по модулю два,элемент И 22 и --триггер 23 .

Генератор 2 (фиг„5) состоит из регистра 24 сдвига и сумматора 2Ь по модулю два.

Предлагаемое устройство работает следующим образом

При нажатии кнопки 14 Пус1; :.,э инверсном выходе триггера 8 формируется сигнал начальной устаноики., переводящий все элементы устройства в-исходное состояние. Одновременно низкий потенциал с другого вьисода триггера запрещает прохохсцение импульсов с генератора 7 через элемент И 3 на вход счетчика 10, После ; отпускания ктгопки 14 Пуск С1.;гна;п начальной установки снимается к устройство начинает работу. Счетчик 10 и элементы 11/ и 11; вырабатываю с импульсы синхронизации: сравнения.

2 ; cji :;::. ::о ,. i о ; ;;;-7-- . п:. )..} Te.i-vi e сг6 .::гь; .ойстз : ,c JIDOBS

cc CTOHi- K i ii :i :;i Toi:;a 2, a записывас/- yshiK и зта. то; л -лличе - ocTOHHir;:; -: c :;e j iKj c i 6,, ;(: :; г;гый .;:.)О.ь;Еляет :.у,т ътиплексо .;;ОИ. 18, .-:а ОЗУ 3 г;pt;jюдитcя Е : еч:е};иа четырах этапов,,

, перебкраемь м , 2, осу1 ;ествляе :::;я запись iiyjiefi (счет-- -I HK i6 нахсд-п ся в ccc ix i HHH ОЭООУ, После ОЕСнчация перебора а.йресов л е- нератор 2 iiep-2 x.cfs,KT- s -лякне 00,,, 00., На кътходе ИЛЫ-НЕ 5 г:оя,вляс1хя въ сокий no ivviiij -vgji. перс- 1:лк1ча)откй с 16 ; с:;а-:-;-,;;, ю iioe

COCTO,riHUe () }л :;г,: / ЬП :ио:;;т;1;

счетчик 17 (. :T -i- .i : ,; яезЕогг} за- ;ола счетчика 16 1(ос;ту, / Jia ход элементе 19, ejjzeMrjv пода ч v киман- ды Saniicb на К ::.::тролируемое ОЗУ , па вход сумматора 20 вызывая гюдач;:; Иг }зход данных ОЗУ 3 ,-, разного инверсии эталонногоJ lia вход эле -лектк И 22 блока : ., ,разрешая акали т ре 1у,льтатоз с,айзнг;шя. При яес- а::«не - :и1- сиг;;:-,, : :-;.;т,1:ваемого из О)- 3 с эта,, 1он: 1:ь:,), /гос- упающим с гь, 1эда мульти:1,17СК1:О1;,:- 18, на выходе ,4атот: а 21 б:гока - з:;лрабатывается сиг: ;:;-| Г ; ;хо :срый 7-роходит через И 22 и устаназл:: - вает тригт-ет 23 Г; спс оя,|ше, что

:1Л,:ч Брак на

17:од бгТ Ка упрйв:;а :чг) г сигнала CriDoc на ;0 п :-м:ч;ановке

На второ;- этапе :7рок;-::гю,г1ится за- niicb и )5ание по ссеп ;щрссам i (состояние счетчика 5 соответст зует 0010 и())„ На тратьем и 4G ; Азег то;; , гфовертги лроизво- .ЧКТСЕ зйписъ к считыванке г оследова- та,льнос гзй чг редуюпгахсл кулей и еди- с, л-:;,риодом в два (с пер- -50го ..г 1:четчик:г . t затем с (евио;::- М в четыре а ;с второго :31,,, :, -ггтчикй 7 ,, 3,:, рокстзо ра- т О 1 ;:самном;у ,:.i (:ip:--,- му, Пос- ,ле скон--зния четыре, провер- Kt на :лч::с-ц: ; :четч 1ка б пс является си,Г на,т- ., ;-:оторь;й постуч йт на вхоц Ол,: }ка 1 управлвпн,-: ., г затем 4ev:e3 s..,ii,jeH i ИЛИ 9 ,L-ji:op, сброса счеччшсу 10 f-i i f /AHf вливает про31

Формула изобретения 1 . Устройство для контроля оперативной памяти, содержащее блок формирования данных, блок сравнения, блок индикации и блок управления, вы- ходы которого подключены к управляющим входам блока формирования данных, блока сравнения и блока индикации, входы блока управления и блока индикации соединены с выходом блока сравнения и управляющим выходом блока формирования данных, одни из выходов блока )ормирования данных подключены к одним из входов блока сравнения, другие выходы, являются одними из выходов устройства, входом которого является другой вход блока сравнения, отличающееся тем, что, с целью повышения быстродействия и упрощения устройства, в него введен генератор псевдослучайных чисел, входы которого подключены к одним из выходов блока управления, а выход соединен с входом блока формирования данных и является дру гим выходом устройства.

4С4

2. Устройство по п.1, О т.л и - чающееся тем, что блок формирования данных содержит первый и второй счетчики, мультиплексор, элемент ИЛИ и элемент ИЛИ-НЕ, выход которого соединен со счетным входом первого счетчика и входом сброса второго счетчика, одни из выходов первого счетчикЖ соединены с одними из входов элемента ИЛИ и сумматора по модулю два и адресными входами мультиплексора, выход которого подключен к другому входу сумматора по модулю два, а одни из информационных входов мультиплексора соединены с выходами второго счетчика, причем другой вход элемента ИЛИ, входы элемента ИЛИ-НЕ, одни из информационных входов мультиплексора, вход сброса первого счетчика и счетный вход второго счетчика являются входаьш блока, выходами которого являются выходы элемента ШШ, сумматора по модулю два и мультиплексора и другой выход первого счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков оперативной памяти | 1986 |

|

SU1358003A1 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1413676A1 |

| Устройство для контроля блоков памяти | 1981 |

|

SU951408A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1352624A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Генератор псевдослучайных сигналов | 1987 |

|

SU1437974A1 |

Изобретение относится к вычислительной технике и может быть использовано для проверки работоспособности оперативной памяти на интегральных микросхемах при массовом их производстве или для входного контроля оперативной памяти. Цель изобретения - повьшение быстродействия устройства. Устройство содержит блок управления, генератор псевдослучайных чисел, блок сравнения, блок индикации и блок формирования данных. Повышение быстродействия устройства достигается использованием генератора псевдослучайных чисел, формирующего адресные сигналы. На первом этапе работы устройства в контролируемое оперативное запоминающее устройство производится запись нулей, на втором - запись единиц, на третьем и на четвертом - запись последовательностей чередующихся единиц и нулей. 1 3.п. ф-лы, 5 ил. (Л

Фиг.

Фиг.З

w

f

Фиг. 5

Редактор Л.Пчелинская

Составитель В.Рудаков Техред М.Ходанич

Заказ 2657/54

Тираж 543Подписное

ВНШШИ Государст венного ко1У1итета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Пронзводственно-полиг рафическое предпр:1ятие, г.Ужгород, ул.Проектт{ая ,4

Корректор М.Санборская

| Электронная промьшшенность, 1975, № 8, с | |||

| Парный автоматический сцепной прибор для железнодорожных вагонов | 0 |

|

SU78A1 |

| Устройство для контроля полупроводниковых оперативных накопителей | 1976 |

|

SU601762A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-05-15—Публикация

1984-10-29—Подача