зователь код - частота (Ц) 8, формирователь управляющих сигналов (ФУС) 9, блок 10 усреднения. Цель достигается введением блока 10 усреднения, ФУС 9, П 8, БВРС 7. БВРС 7 разделяет во времени сигналы с выходов блока 10 усреднения и П 8, П 8 формирует импульсные последовательности

Изобретение относится к электросвязи и радиотехнике и может использоваться в системах передачи дискретной информации для синхронизации опорного колебания и в навигационных системах для синхронизации вторичных часов.

Цель изобретения - повышение точности синхронизации и увеличение времени поддержания синхронизма при пропадании входных синхроимпульсов,

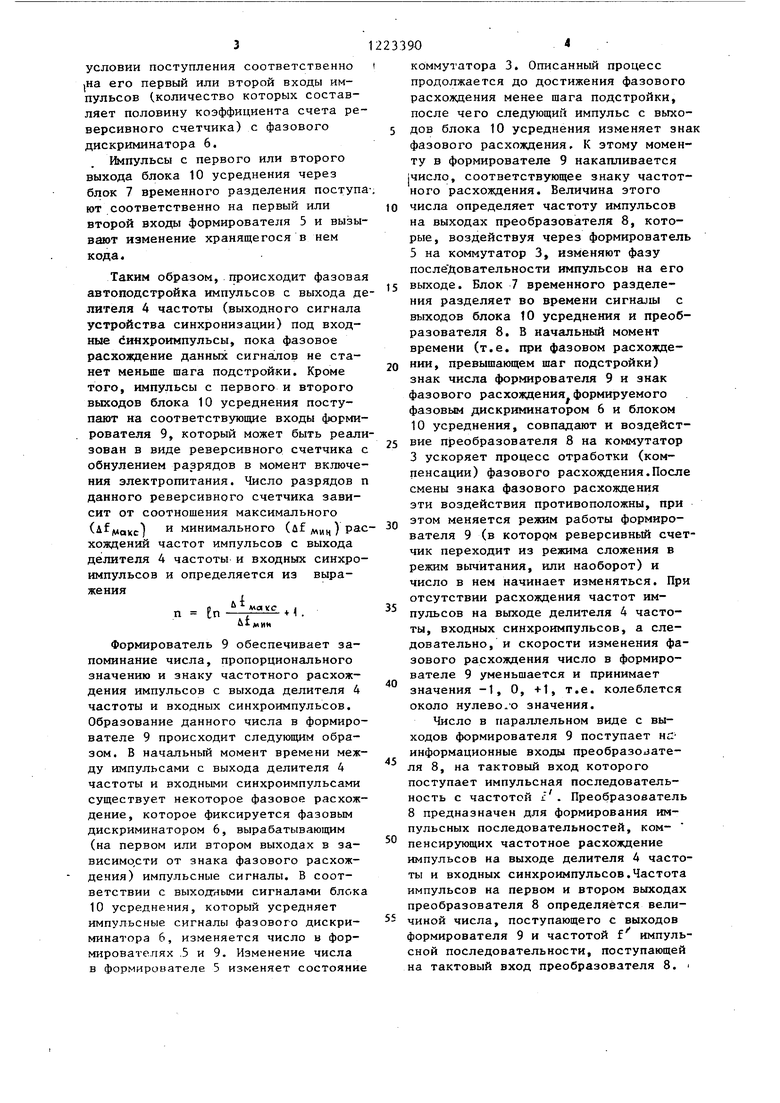

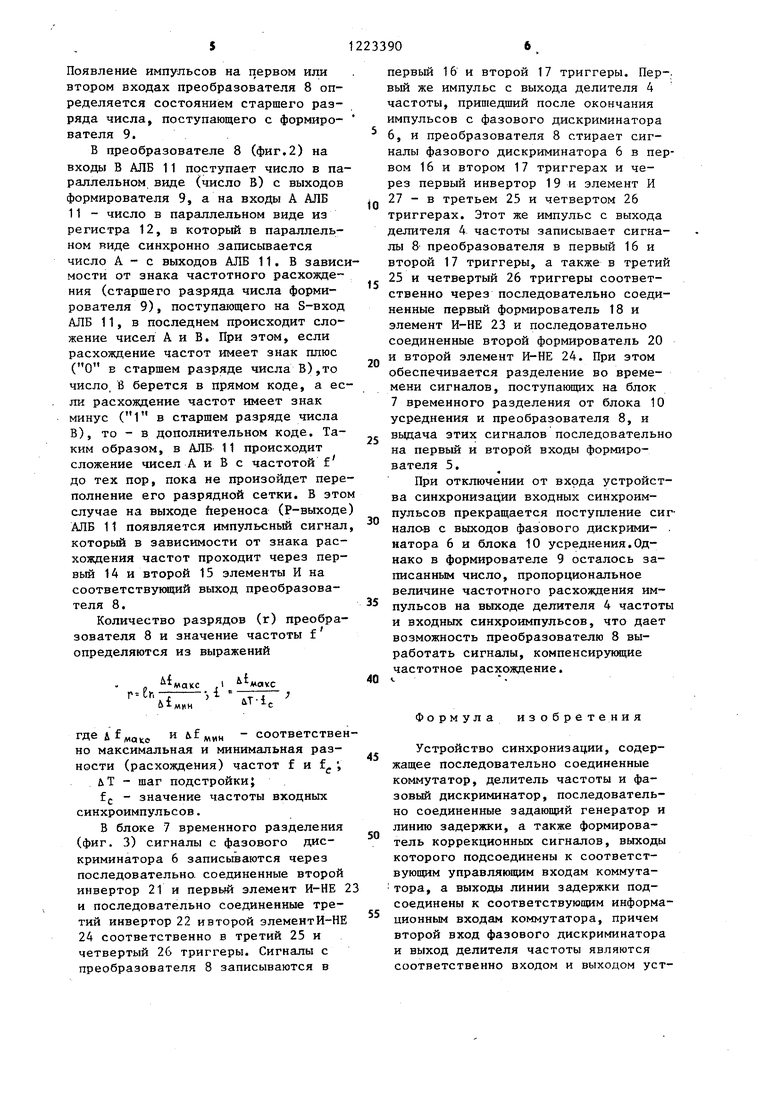

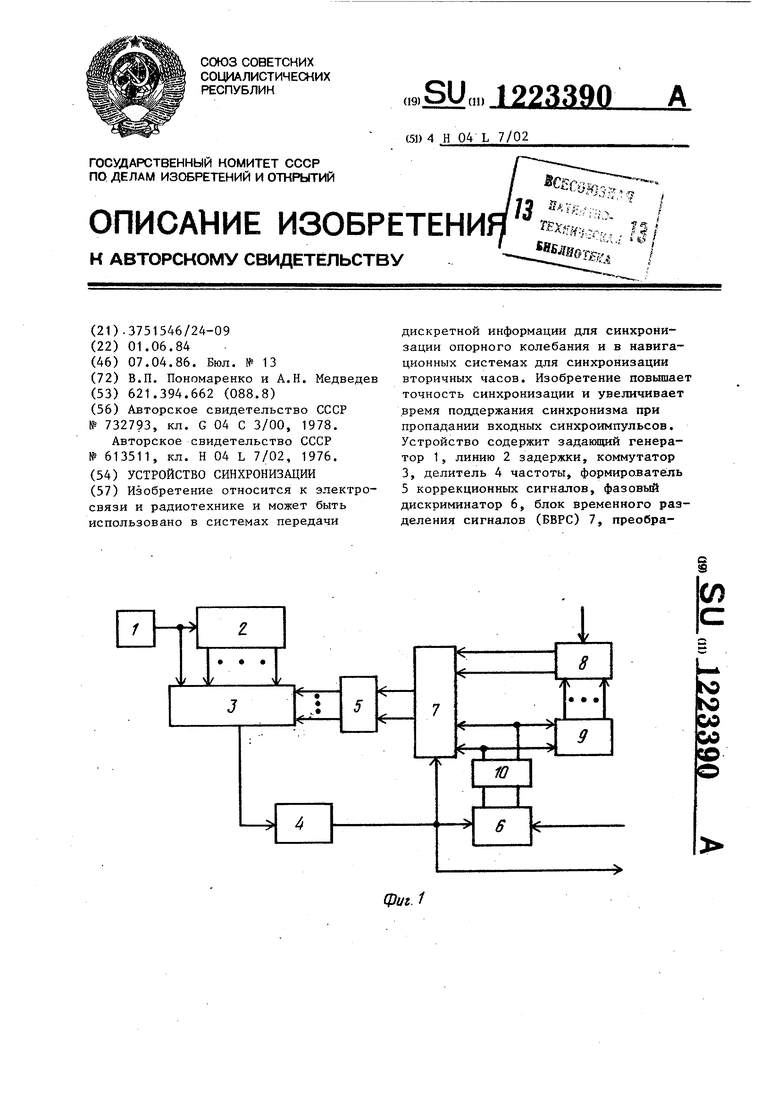

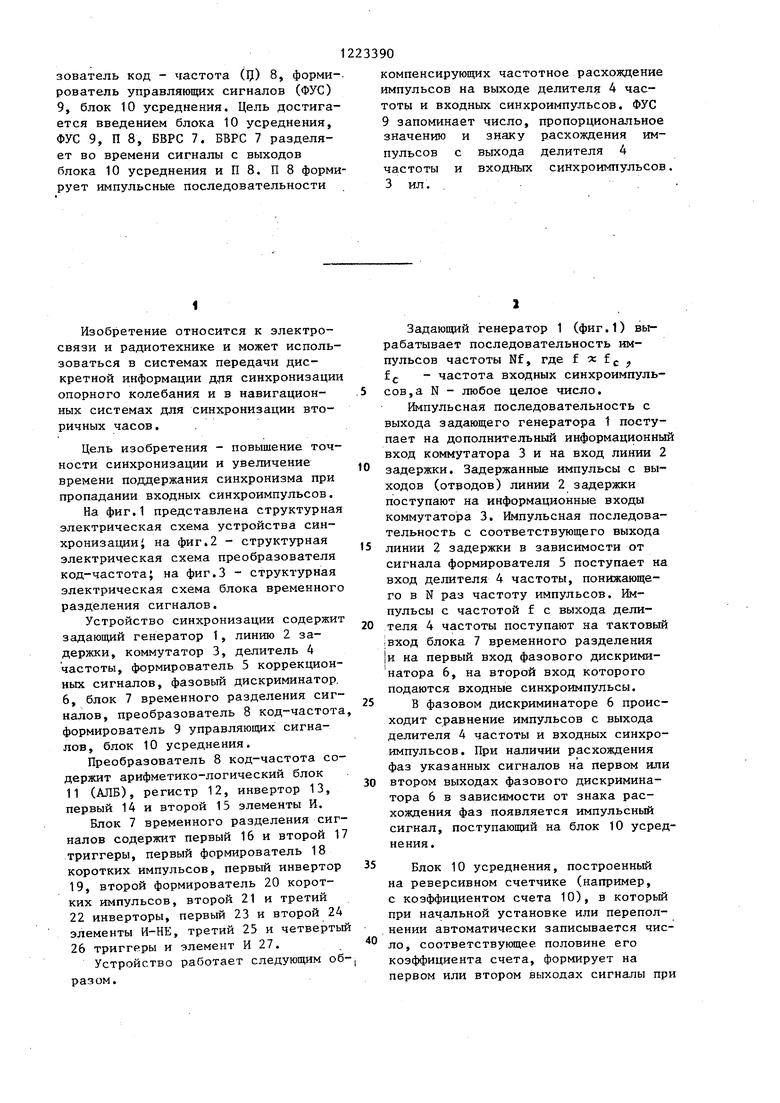

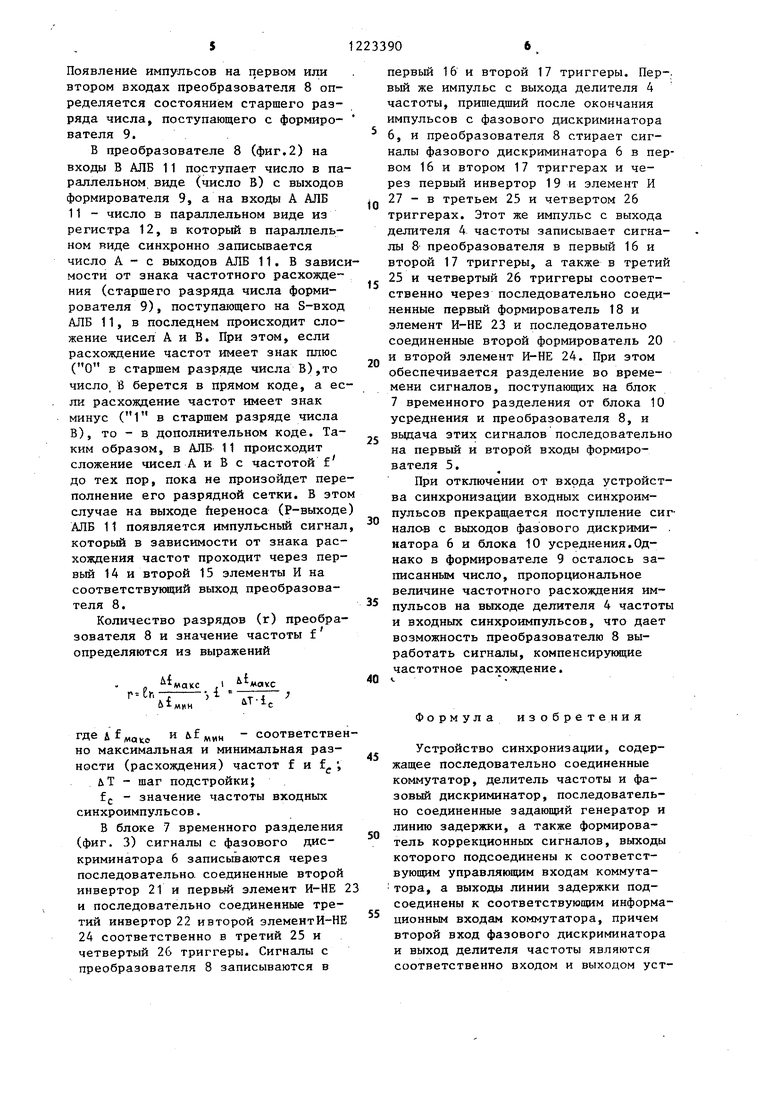

На фиг.1 представлена структурная электрическая схема устройства синхронизации i на фиг.2 - структурная электрическая схема преобразователя код-частота; на фиг.З - структурная электрическая схема блока временного разделения сигналов.

Устройство синхронизации содержит задающий генератор 1, линию 2 задержки, коммутатор 3, делитель 4 частоты, формирователь 5 коррекцион- ных сигналов, фазовый дискриминатор. 6, блок 7 временного разделения сигналов, преобразователь 8 код-частота формирователь 9 управляющих сигналов, блок 10 усреднения.

Преобразователь 8 код-частота содержит арифметико-логический блок 11 (АЛБ), регистр 12, инвертор 13, первый 14 и второй 15 элементы И.

Блок 7 временного разделения сигналов содержит первый 16 и второй 17 триггеры, первый формирователь 18 коротких импульсов, первый инвертор 19, второй формирователь 20 коротких импульсов, второй 21 и третий 22 инверторы, первый 23 и второй 24 элементы И-НЕ, третий 25 и четвертый 26 триггеры и элемент И 27.

Устройство работает следующим образом.

компенсирующих частотное расхождение импульсов на выходе делителя 4 частоты и входных синхроимпульсов. ФУС 9 запоминает число, пропорциональное значению и знаку расхождения импульсов с выхода делителя 4 частоты и входных синхроимпульсов. 3 ил. ..

5

0

5

0

5

0

Задающий генератор 1 (фиг.1) вырабатывает последовательность импульсов частоты Nf, где f ж f ,, fc - частота входных синхроимпульсов, а N - любое целое число.

Импульсная последовательность с выхода задающего генератора 1 поступает на дополнительный информационный вход коммутатора 3 и на вход линии 2 задержки. Задержанные импульсы с выходов (отродов) линии 2 задержки поступают на информационные входы коммутатора 3, Импульсная последовательность с соответствующего выхода линии 2 задержки в зависимости от сигнала формирователя 5 поступает на вход делителя 4 частоты, понижающего в N раз частоту импульсов. Импульсы с частотой f с выхода делителя 4 частоты поступают на тактовый I вход блока 7 временного разделения |и на первый вход фазового дискрими- натора 6, на второй вход которого подаются входные синхроимпульсы.

В фазовом дискриминаторе 6 происходит сравнение импульсов с выхода делителя 4 частоты и входных синхроимпульсов . При наличии расхождения фаз указанных сигналов на первом или втором выходах фазового дискриминатора 6 в зависимости от знака расхождения фаз появляется импульсный сигнал, поступающий на блок 10 усреднения.

Блок 10 усреднения, построенный на реверсивном счетчике (например, с коэффициентом счета 10), в который при начальной установке или переполнении автоматически записывается число, соответствующее половине его коэффициента счета, формирует на первом или втором выходах сигналы при

условии поступления соответственно jHa его первый или второй входы импульсов (количество которых составляет половину коэффициента счета реверсивного счетчика) с фазового дискриминатора 6.

Импульсы с первого или второго выхода блока 10 усреднения через блок 7 временного разделения поступа ют соответственно на первый или второй входы формирователя 5 и вызывают изменение хранящегося в нем кода.

Таким образом, происходит фазовая автоподстройка импульсов с выхода делителя 4 частоты (выходного сигнала устройства синхронизации) под входные йи«хроимпульсы, пока фазовое расхождение данных сигналов не станет меньше шага подстройки. Кроме того, импульсы с первого и второго выходов блока 10 усреднения поступают на соответствующие входы формирователя 9, который может быть реализован в виде реверсивного счетчика с обнулением разрядов в момент включения электропитания. Число разрядов п данного реверсивного счетчика зависит от соотношения максимального

) и минимального (uf мич ) хождений частот импульсов с выхода делителя 4 частоты и входных синхроимпульсов и определяется из выражения

п en Л1(ии

Формирователь 9 обеспечивает запоминание числа, пропорционального значению и знаку частотного расхождения импульсов с выхода делителя 4 частоты и входных синхроимпульсов. Образование данного числа в формирователе 9 происходит следующим образом. В начальный момент времени между импульсами с выхода делителя 4 частоты и входными синхроимпульсами существует некоторое фазовое расхождение, которое фиксируется фазовым дискриминатором 6, вырабатывающим (на первом или втором выходах в за- висимо,сти от знака фазового расхождения) импульсные сигналы. В соответствии с выходными сигналами блока 10 усреднения, который усредняет импульсные сигналы фазового дискриминатора 6, изменяется число в формирователях .5 и 9. Изменение числа в формирователе 5 изменяет состояние

2233904

коммутатора 3. Описанный процесс

продолжается до достижения фазового расхоящения менее шага подстройки, после чего следующий импульс с выхо5 дов блока 10 усреднения изменяет знак фазового расхозкдения, К этому моменту в формирователе 9 накапливается 1число, соответствующее знаку частотного расхождения. Величина этого

to числа определяет частоту импульсов на выходах преобразователя 8, которые, воздействуя через формирователь 5 на коммутатор 3, изменяют фазу после Довательности импульсов на его

15 выходе. Блок 7 временного разделения разделяет во времени сигналы с выходов блока 10 усреднения и преобразователя 8. В начальный момент времени (т.е. при фазовом расхозвде20 НИИ, превышающем шаг подстройки) знак числа формирователя 9 и знак фазового расхождения формируемого фазовым дискриминатором 6 и блоком 10 усреднения, совпадают и воздейст25 вие преобразователя 8 на коммутатор 3 ускоряет процесс отработки (компенсации) фазового расхождения.После смены знака фазового расхождения эти воздействия противоположны, при

JQ этом меняется режим работы формирователя 9 (в KOTOpQM реверсивный счетчик переходит из режима сложения в режим вычитания, или наоборот) и число в нем начинает изменяться. При отсутствии расхождения частот импульсов на выходе делителя 4 частоты, входных синхроимпульсов, а следовательно, и скорости изменения фазового расхождения число в формирователе 9 уменьшается и принимает значения -1, О, +1, т.е. колеблется около нулево. о значения.

Число в параллельном виде с выходов формирователя 9 поступает информационные входы преобразо1зате40

45

ля 8, на тактовый вход которого

поступает импульсная последователь- -I

50

ность с частотой г . Преобразователь 8 предназначен для формирования импульсных последовательностей, компенсирующих частотное расхождение импульсов на выходе делителя 4 частоты и входных синхроимпульсов.Частота импульсов на первом и втором выходах преобразователя 8 определяется вели- 55 чиной числа, поступающего с выходов формирователя 9 и частотой f импульсной последовательности, поступающей на тактовый вход преобразователя 8.

Появление импульсов на первом или втором входах преобразователя 8 определяется состоянием старшего разряда числа, поступающего с формиро- вателя 9.

В преобразователе 8 (фиг,2) на входы В АЛБ 11 поступает число в параллельном виде (число В) с выходов формирователя 9, а на входы А АЛБ 11 - число в параллельном виде из регистра 12, в который в параллельном виде синхронно записывается число А - с выходов АЛБ 11. В зависимости от знака частотного расхождения (старшего разряда числа формирователя 9), поступающего на S-вход АЛБ 11, в последнем происходит сложение чисел А и В. При этом, если расхождение частот имеет знак плюс (О в старшем разряде числа В),то число, В берется в прямом коде, а если расхождение частот имеет знак минус (1 в старшем разряде числа В), то - в дополнительном коде. Таким образом, в АЛБ 11 происходит сложение чисел А и В с частотой f до тех пор, пока не произойдет переполнение его разрядной сетки, В это случае на выходе переноса (Р-выходе АЛБ 11 появляется импульсньй сигнал который в зависимости от знака расхождения частот проходит через первый 14 и второй 15 элементы И на соответствунщий выход преобразователя 8,

Количество разрядов (г) преобразователя 8 и значение частоты f определяются из выражений

-h

«aicc .1

bf

,i

мин

где д f.

и f

/иокс --мин - соответственно максимальная и минимальная разности (расхождения) частот f и f ,

ЛТ - шаг подстройки;

fj - значение частоты входных синхроимпульсов.

В блоке 7 временного разделения (фиг. 3) сигналы с фазового дискриминатора 6 записываются через последовательно, соединенные второй инвертор 21 и первый элемент И-НЕ 23 и последовательно соединенные третий инвертор 22 ивторой элементИ-НЕ 24 соответственно в третий 25 и четвертый 26 триггеры. Сигналы с преобразователя 8 записываются в

0

5

0

5

0

5

0

первый 16 и второй 17 триггеры. Пер-, вый же импульс с выхода делителя 4 частоты, прип1едший после окончания импульсов с фазового дискриминатора 6, и преобразователя 8 стирает сигналы фазового дискриминатора 6 в первом 16 и втором 17 триггерах и через первый инвертор 19 и элемент И 27 - в третьем 25 и четвертом 26 триггерах. Этот же импульс с выхода делителя 4 частоты записывает сигналы 8- преобразователя в первый 16 и второй 17 триггеры, а также в третий 25 и четвертый 26 триггеры соответственно через последовательно соединенные первый формирователь 18 и элемент И-НЕ 23 и последовательно соединенные второй формирователь 20 и второй элемент И-НЕ 24, При этом обеспечивается разделение во време- мени сигналов, поступающих на блок 7 временного разделения от блока 10 усреднения и преобразователя 8, и выдача этих сигналов последовательно на первый и второй входы формирователя 5,

4

При отключении от входа устройства синхронизации входных синхроимпульсов прекращается поступление сиг- нало-в с выходов фазового дискрими- . натора 6 и блока 10 усреднения,Однако в формирователе 9 осталось записанным число, пропорциональное величине частотного расхождения импульсов на выходе делителя 4 частоты и входных синхроимпульсов, что дает возможность преобразователю 8 выработать сигналы, компенсируимцие частотное расхождение.

Формула изобретения

Устройство синхронизации, содержащее последовательно соединенные коммутатор, делитель частоты и фазовый дискриминатор, последовательно соединенные задающий генератор и линию задержки, а также формирователь коррекционных сигналов, выходы которого подсоединены к соответствующим управляющим входам коммута- тора, а выходы линии задержки подсоединены к соответствующим информационным входам коммутатора, причем второй вход фазового дискриминатора и выход делителя частоты являются соответственно входом и выходом устройства, отличающееся тем, что, с целью повышения точности синхронизации и увеличения времени поддержания синхронизма при пропадании входных синхроимпульсов, в него введены последовательно соединенные блок усреднения, формирователь управляющих сигналов, преобразователь код - частота и блок временного разделения сигналов, при зто первый и второй выходы фазового дискриминатора через блок усреднения подсоединены соответственно к первому и второму дополнительным инфор510

2233908

мационным входам блока временного разделения сигналов, первый и второй выходы которого подсоединены соответственно к первому и второму входам формирователя коррекционных сигналов, выход задающего генератора подсоединен к дополнительному информационному входу коммутатора, а тактовый вход блока временного разделения сигналов подключен к выходу делителя частоты, причем тактовый вход преобразователя код - частота является дополнительным входом устройства.

I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство компенсации сдвига частот | 1985 |

|

SU1316097A2 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

| Устройство для синхронизации часов по радиоканалу | 1983 |

|

SU1230442A2 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1415446A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство тактовой синхронизации с переменным коррекционным эффектом | 1984 |

|

SU1297242A1 |

| Резервированный генератор импульсов | 1989 |

|

SU1619440A1 |

| Устройство дискретной фазовой синхронизации | 1978 |

|

SU748894A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

Изобретение относится к электросвязи и радиотехнике и может быть использовано в системах передачи дискретной информации для синхронизации опорного колебания и в навигационных системах для синхронизации вторичных часов. Изобретение повышает точность синхронизации и увеличивает время поддержания синхронизма при пропадании входных синхроимпульсов. Устройство содержит задающий генератор 1, линию 2 задержки, коммутатор 3, делитель 4 частоты, формирователь 5 коррекционных сигналов, фазовый дискриминатор 6, блок временного разделения сигналов (БВРС) 7, преобрафиг. f

Редактор О. Бугир

Составитель В. Орлов

Техред И.Попович Корректор Л. Пилипенко

Заказ 17-26/60 Тираж 624 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная,4

| Устройство для синхронизации часов | 1978 |

|

SU732793A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для фазовой синхронизации | 1976 |

|

SU613511A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-04-07—Публикация

1984-06-01—Подача