i

(Л

С

Изобретение относится к вычислительной технике, а именно к быстродействующим логическим системам, -и может Сыть использовано в полупроводниковых запоминающих устройствах, в устройствах вычислительной техники и автоматики.

Целью изобретения является снижение потребляемой мощности дешифратора.

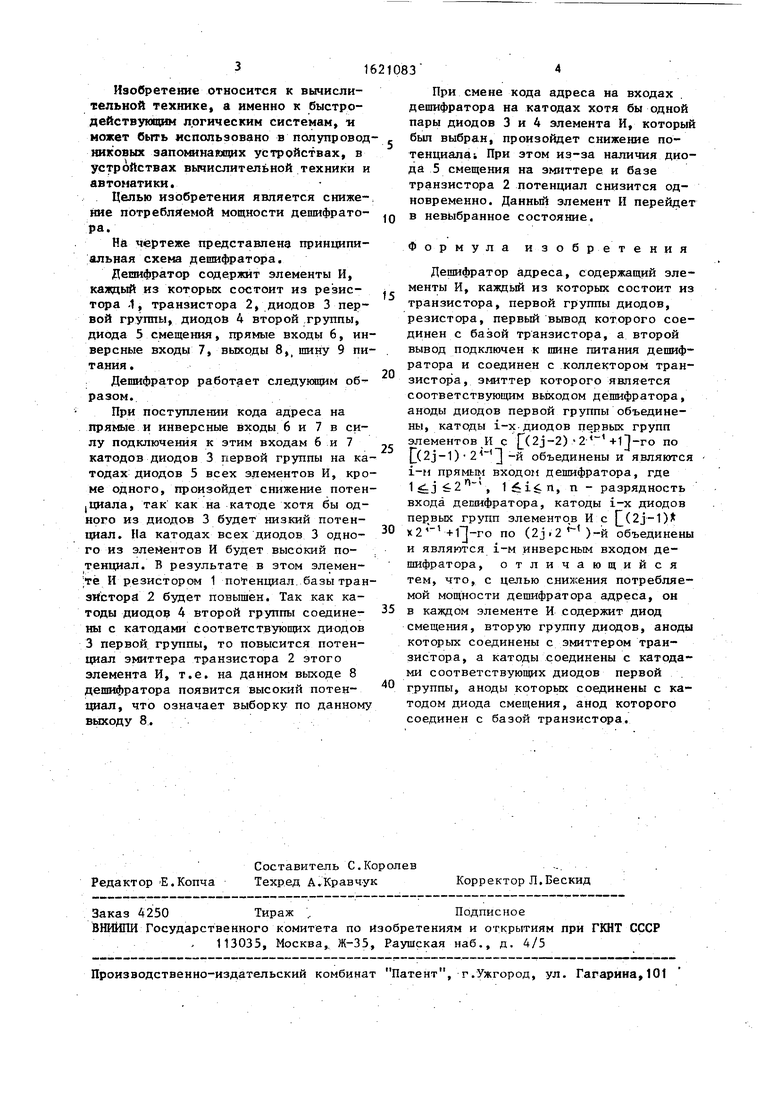

На чертеже представлена принципиальная схема дешифратора.

Дешифратор содержит элементы И, каждый из которых состоит из резистора -1, транзистора 2, диодов 3 первой группы, диодов 4 второй группы, диода 5 смещения, прямые входы 6, инверсные входы 7, выходы 8,, шину 9 питания .

Дешифратор работает следующим образом.

При поступлении кода адреса на прямые и инверсные входы 6 и 7 в силу подключения к этим входам 6 и 7 катодов диодов 3 первой группы на катодах диодов 5 всех элементов И, кроме одного, произойдет снижение потен- (циала, так как на катоде хотя бы одного из диодов 3 будет низкий потенциал. На катодах всех диодов 3 одного из элементов И будет высокий потенциал. В результате в этом элементе И резистором 1 потенциал базы транзистора 2 будет повышен. Так как катоды диодов 4 второй группы соединены с катодами соответствующих диодов 3 первой группы, то повысится потенциал эмиттера транзистора 2 этого элемента И, т.е. на данном выходе 8 дешифратора появится высокий потенциал, что означает выборку по данному выходу 8.

0

5

0

5

0

5

0

При смене кода адреса на входах дешифратора на катодах хотя бы одной пары диодов 3 и 4 элемента И, который был выбран, произойдет снижение потенциала; При этом из-за наличия диода 5 смещения на эмиттере и базе транзистора 2 потенциал снизится одновременно. Данный элемент И перейдет в невыбранное состояние.

Формула изобретения

Дешифратор адреса, содержащий элементы И, каждый из которых состоит из транзистора, первой группы диодов, резистора, первый вывод которого соединен с базой транзистора, а второй вывод подключен к шине питания дешифратора и соединен с коллектором транзистора, эмиттер которого является соответствующим выходом дешифратора, аноды диодов первой группы объединены, катоды 1-х диодов первых групп элементов И с Ј(2j-2) 2 1 +1 J-ro по L(2j-1) J -и объединены и являются i-м прямым входом дешифратора, где 1 :j :2n 1, .n, n - разрядность входа дешифратора, катоды 1-х диодов первых групп элементов И с Ј(2j-1) x2 - +f -ro по (2j.2M)-u объединены и являются i-м инверсным входом дешифратора, отличающийся тем, что, с целью снижения потребляемой мощности дешифратора адреса, он в каждом элементе И содержит диод смещения, вторую группу диодов, аноды которых соединены с эмиттером транзистора, а катоды соединены с катодами соответствующих диодов первой группы, аноды которых соединены с катодом диода смещения, анод которого соединен с базой транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления диодными дешифраторами адреса | 1989 |

|

SU1705869A1 |

| Дешифратор адреса | 1988 |

|

SU1608745A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| Дешифратор | 1988 |

|

SU1658210A1 |

| Дешифратор адреса | 1989 |

|

SU1672526A1 |

| Дешифратор запоминаюшего устройства | 1979 |

|

SU871330A1 |

| Функциональный преобразователь | 1979 |

|

SU805350A1 |

| Устройство для выборки координатных шин магнитного накопителя | 1983 |

|

SU1140177A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1327293A1 |

| Устройство для управления подключением электропитания | 1987 |

|

SU1427371A2 |

Изобретение относится к вычислительной технике, а именно к быстродействующим логическим схемам, может быть использовано в полупроводниковых запоминакнтих устройствах, в устройствах вычислительной техники и автоматики. Целью изобретения является снижение потребляемой мощности дешифратора. Цель достигается тем, что дешифратор содержит диоды 4 второй группы и диоды 5 смещения с соответствующими связями. При смене адреса входной ток дешифратора через диоды 4, 5 перезаряжает паразитную емкость выхода 8 дешифратора. В результате отпадает необходимость в специальных источниках тока. 1 ил.

| Микроэлектроника, т.9, вып.З, 1980, с | |||

| Камневыбирательная машина | 1921 |

|

SU222A1 |

| I Алексенко А.Г | |||

| Основы микросхемотехники | |||

| - М.: Советское радио, 1975, с | |||

| Клапанный регулятор для паровозов | 1919 |

|

SU103A1 |

Авторы

Даты

1991-01-15—Публикация

1988-10-05—Подача