ния, каждый из которых состоит из первого и второго диодов, источники тока выборки, элементы коммутаций токов выборки, каждый из которых состоит из первого и второго транзисторов, коллекторы которых соединены соответственно с первым и вторым выходами элементов памяти каждого столбца матрицы, с анода ш диодов элемента распределения тока хранения и являются входами-выходами устройства, базы являются входам выборки столбцов, а эмиттеры подключены к первым выводам первого и второго источников тока выборки, вторые выводы которых соединены с шиной напряжения питания, дешифратор выбора строк, состоящий из элементов И, каждый из- которых состоит из резистора и диодов, аноды которы подключены к первому выводу резнетора, второй вывод которого соедииен с шиной нулевого потенциала.,, буферные элементы, каждьй из которых состоит из первого, второго и третьего транзисторов, база второго тра.нзистора подключена к эмиттеру третьего транзистора, база которого является адресным входом

устройства, а коллектор соединен с шиной нулевого потенциала, база первого транзистора подключена к

33621

первой шине опорного напряжения, катоды диодов элементов И подключе- ны к коллекторам первых или вторых транзисторов буферных элементов в соответствии с двоичными номерами элементов И, источники тока хра-ь нения, первые выводы которых подключены к шине напряжения питания, отличающееся тем, что, с целью снижения потребления мощности за счет использования в режиме выборки тока хранения для питания дешифратора строк, в устройство введены переключатели тока, кговдый из которых состоит из первого и второго транзисторов, к эмиттерам которых подключен второй вывод соответствующего источника тока хранения, коллектор первого транзистора подключен к эмиттерам первого и второго транзисторов соответствующего буферного элемента, коллекторы вторьв: транзисторов подключены к катодам диодов элементов распределения тока хранения, базы первых транзисторов являются входом выборки, базы вторых транзисторов подключены к Е1торой шине опорного напряжения, а входы элементов памяти каждой строки матрицы подключены к первому выводу резистора соответствующего элемента И,

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Запоминающее устройство | 1986 |

|

SU1361630A1 |

| Формирователь сигнала выборки шины матрицы накопителя | 1981 |

|

SU1027824A1 |

| Матричный накопитель | 1986 |

|

SU1343443A1 |

| Накопитель | 1989 |

|

SU1656595A1 |

| Накопитель | 1988 |

|

SU1536442A1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1573472A1 |

| Устройство для обращения к памяти (его варианты) | 1982 |

|

SU1092561A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

1. Запоминающее устройство, содержащее матрицу элементов памяти, элементы распределения тока хранения, каждьм из которых состоит из первого и второго диодов, источники тока выборки, элементы коммутации токов выборки, каждый из которых состоит из первого и второго транзисторов, коллекторы которых соединены соответственно с первым и вторым выходами элементов памяти каждого столбца матрицы, с анодами диодов элемента распределения тока хранения и являются входами-выходами устройства, базы являются входами выборки столбцов, а эмиттеры под-, ключены к первым выводам первого и второго источников тока выборки, вторые выводы которых соединены с шиной напряжения питания, дешифратор выбора строк, состоящий из элементов ИПИ-НЕ, каждый из которых состоит из резистора, транзистора и группы транзисторов, коллектор транзистора и второй вьгеод резистора подключены к шине нулевого потенциала, база первого транзистора соединена с первой шиной опорного напряжения, а коллекторы транзисторов группы подключены к первому выводу резистора, базы транзисторов группы подключены к прямым или инверсным адресным входам в соответствии с двоичными номерами элементов ИПИ-НЕ, источники тока хранения, первые выводы которых подключены к шине напряжения питания, отличающееся тем, что, с целью сниS жения потребления мощности за счет использования в режиме выборки тока хранения для питания дешифратора строк, в устройство введены переключатели тока, каждый из которых состоит из первого и второго транГзисторов, к эмиттерам которых подключен второй вывод соответствующего :о источника тока хранения, коллектор :о первого транзистора подключен к 35 эмиттерам транзисторов соответствующего элемента ИЛИ-НЕ, коллекторы д вторых транзисторов подключены к катодам диодов элементов -распределения токов хранения, базы первых транзисторов являются входами выборки, базы вторых транзисторов подключены к второй шине опорного напряжения, а входы элементов памяти каждой строг ки матрицы подключены к первому выводу резистора соответствующего элемента ИЖ-НЕ. 2. Запоминающее устройство, содержащее матрицу элементов памяти, элементы распределения тока хране

Изобретение относится к вычислительной технике и предназначено, для использования в биполяртак статических оперативных запоминающих устройствах.

Известны запоминающие устройства содержащие матрицу элементов памяти на биполярных транзисторах с эмит терной связью lj .

Однако транзисторы элементов памяти имеют вторые эмиттеры, предназченные для записи и считывания ин-. формации, использование которьо приводит к значительному увеличению размеров матрицы элементов памяти и всего устройства,

Наиболее близким техническим решением к изобретению является а2

пo шнaющee устройство, содержащее матрицу элементов памяти, каждый из которых состоит из первого и второго биполярных одноэмиттерных транзисторов с перекрестно соединенными базовыми и коллекторньй-ш вьгоодами и двух на.грузочных элементов, первые выводы которых подключены ic коллекторам транзисторов, вторые выводы, нагрузочных элементов соединены и являются входом элемента паг-шти, а эмиттеры транзисторов - соответ- ствеяно первым и вторым выходами Известноч устройство та1сже содержит источники тока хранения, элементы распределения тока хранения, источники тока выборки и элементы коммутации токов выборки. Элемент

распределения тока хранения состоит из первого и второго диодов, катоды которых подключены к второму выводу источника тока хранения. Первые выводы источников тока хранения подключены к шине напряжения питания. Количество элементов распределения тока хранения равно числу столбцов матрицы. Аноды диодов элементов распределения тока хранения соединены с первыми и вторыми выходами элементов памяти соответствующего столбца матрицы. У элементов памяти, составляющих строку матрицы, входы подключены к одному из выходов дешифратора строк. В режиме хранения на всех выходах дешифратора строк установлено одинаковое напряжение низкого логического уровня. При этом ток хранения через диоды элементов распределения тока хранения протекает в столбцы матрицы и распределяется между эмиттерами транзисторов элементов памяти, на базах которьЬс установленвысокий логический уровень и, таким образом, сохраняются состояния- всех элементов памяти.

В режимах записи и считывания для выборки строки на одном из выходов дешифратора строк по требуемому адресу установлен высокий логический уровень. Выборка столбца матрицы осуществляется посредством установки высокого логического уровня на соответствующем входе выборки столбца, при этом токи выборки протекают через транзисторы элементов коммутации в выбранный столбец И.

Дешифратор строк известного запоминающего устройства может быть построен на элементах ИЛИ-НЕ, каждый из которых состоит из резистора, первого и второго транзисторов, группы транзисторов и источника тока 3.

В известном устройстве может быть использован дешифратор строк диодного типа, состоящий из буферных элементов и элементов И, каждый из которых содержит резистор транзиотор и диоды AJ.

Однако при описанном подключении .источников тока хранения и способе выборки строки матрицы ток в элементах памяти выбранной строки возрастает в число раз, равное количеству строк матрицы, так как в них переключается весь ток хранения. Это приводит к большому различию токов элементов памяти и токов нагрузки дешифратора строк в режимах .хранения и выборки и большому потреблению мощности.

.Цель изобретения - стабилизация токов элементов памяти и токов нагрузки дешифратора строк и снижение потребления мощности за счет использования в режиме выборки тока хранения для питания дешифратора строк.

Для достижения этой цели в запоминающее устройство первого варианта, содержащее матрицу элементов памяти, элементы распределения тока хранения, каждый из которых состоит из первого и второго диодов, источники тока выборки, элементы коммутации токов выборки, каждый из которых состоит из первого и второго транзисторов, коллекторы которых соединены соответственно с первым и вторым выходами элементов памяти каждого столбца матрицы, с анодами диодов элемента распределения тока хранения и являются входами-выходами устройства, базы являются входами выборки столбцов, а эмиттеры подключены к первым выводам первого и второго источников тока выборки, вторые выводы которых соединены с шиной напряжения питания, дешифратор выбора строк, состоявши из элементов ИЛИ-НЕ,каждый из которых состо-. ит из резистора, транзистора и группы транзисторов, коллектор транзистора ивторой вывод резистора подключены к шине нулевого потенциала, база первого транзистора соединена с первой шиной опорного напряжения, а коллекторы транзисторов группы подключены к первому выводу резистора, базы транзисторов группы подключены к прямым или инверсным адресным входам в соответствии с двоичными номерами элементов ИЛИ-НЕ, источники тока хранения , первые выводы которых подключены к шине напряжения питания, введены переключатели тока, каждый из которых состоит из первого и второго транзисторов, к эмиттерам которых подключен второй вывод соответствующего источника тока хранения, коллектор первого транзистора подключен к эмиттерам транзисторов соответствующего элемента ИЛИ-НЕ, коллекторы вторых транзисторов подключены к катодам диодов элементов

| аспределения токов хранения, базы рервых транзисторов являются входами выборки, базы вторых транзисторов подключены к второй шине опорного напряжения, а входы элементов памяти каждой строки матрицы подключены к первому выводу резистора соот ветствующего элемента .

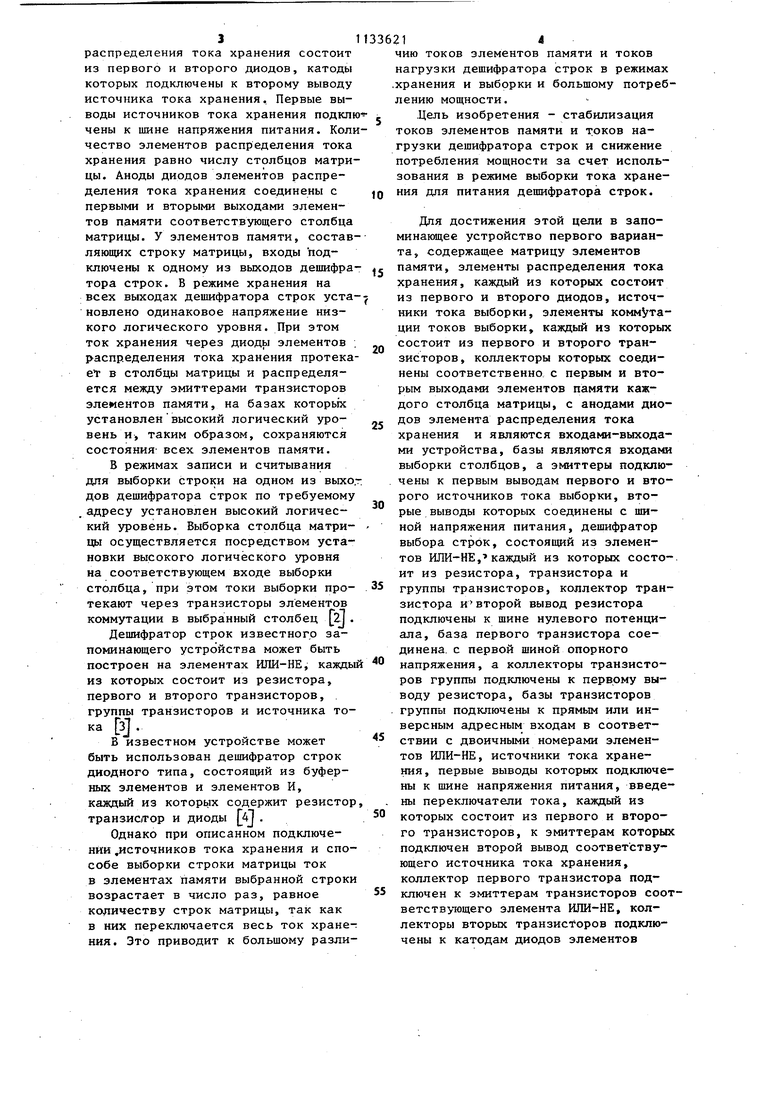

В запоминающее устройство второго варианта, содержащее матрицу элементов памяти, элементы распределения тока хранения, каждый из которых сое тоит из первого и второго диодов, источники тока выборки, элементы коммутации токов выборки, каждый из которых состоит из первого и второго транзисторов, коллекторы которых соединены соответственно с первым и вторът выходами элементов памяти каждого столбца матрицы, с анодами диодов элемента распределения тока хранения и являются входами-выходами устройства5 базы являются входами выборки столбцов f а эмиттеры подключены к первым выводам первого и второго источников тока выборки, вторые выводы которых соединены с шиной напряжения питания, дешифратор выбора строк, состоящий из эле ментов И, каждый из которых состоит из резистора и диодов, аноды которых подключены к первому выводу резистора, второй вывод которого соединен с шиной нулевого потенциала буферные элементы, ка)вдый из которых состоит из первого, второго и третьего транзисторов, база второго транзистора подключена к эмитя-еру третьего транзистора, база которого является адресным входом устройства8 а коллектор соединен с шиной нулевого потенциала, база первого транзистора подключена к первой шине опорного напряжения, катоды диодов элементов И подключены к коллекторам первых или вторых транзисторов буферных элементов в соответствии с двоичными номерами элементов И, источники тока хранения, nepsbie выв( ды которых подключены к шине напряжения питания, введены переключатели тока, каждый из которых состоит из первого и второго транзисторов, к эмиттерам которых подключен второй вывод соответствующего источника тока хранения, коллектор первого транзистора подключен к эмиттерам первого и второго транзисторов соответствующего буферного элемента, коллекторы вторых транзистгров подключены к катодам диодов элементов распределения тока хранения, базы первых транзисторов являются входом выборки, базы вторых тран: исторов подключены к второй шине опорного напряжения, а входы элементов памяти каждой строки матрицы подключены

К первому выводу резистора соответствующего элемента И.

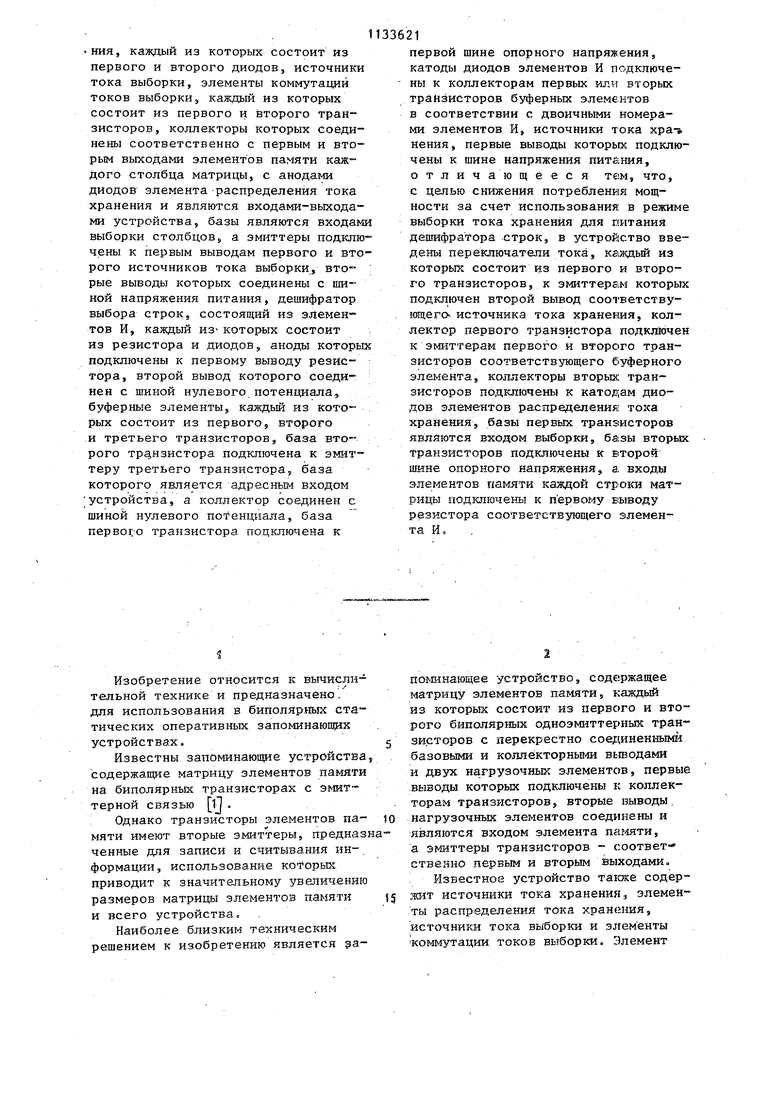

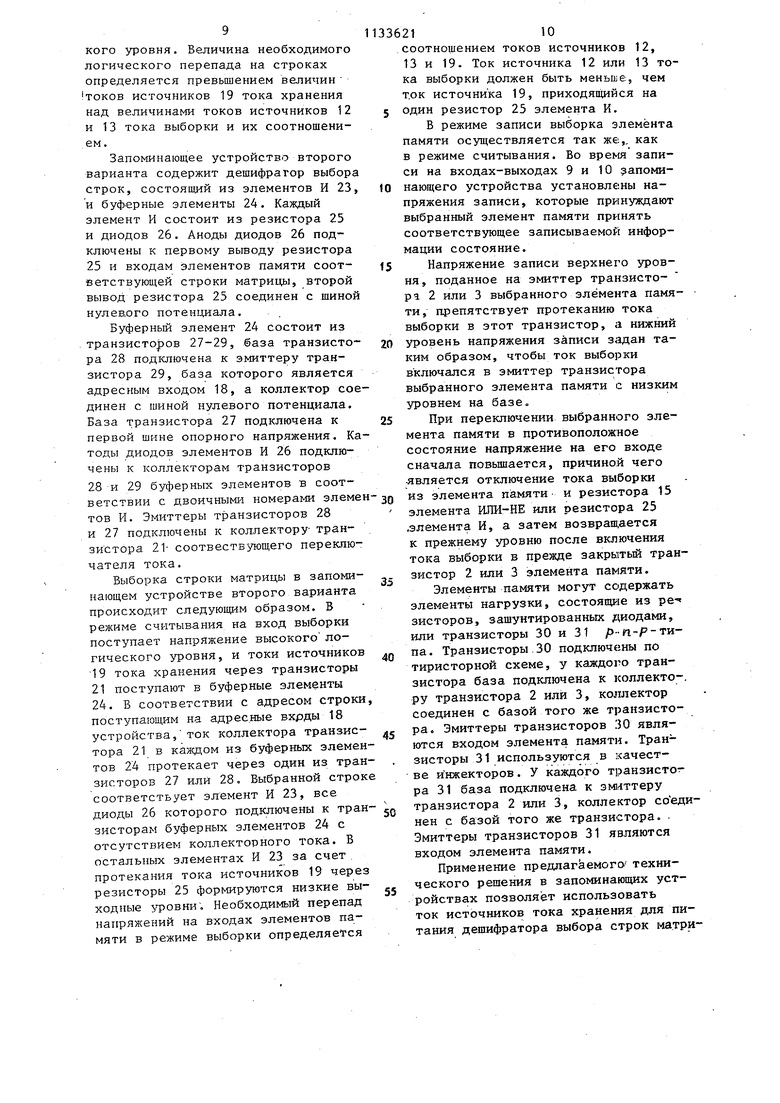

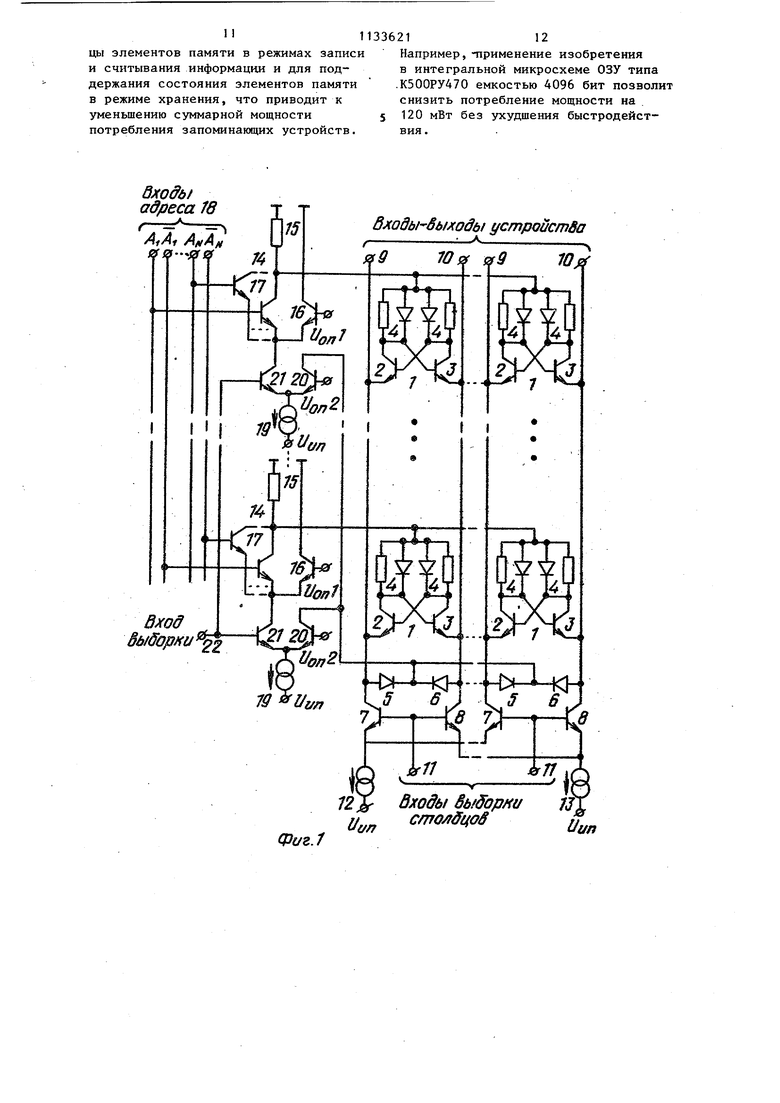

На фиг. 1 изображено запоминающее устройство (первьй вариант)}

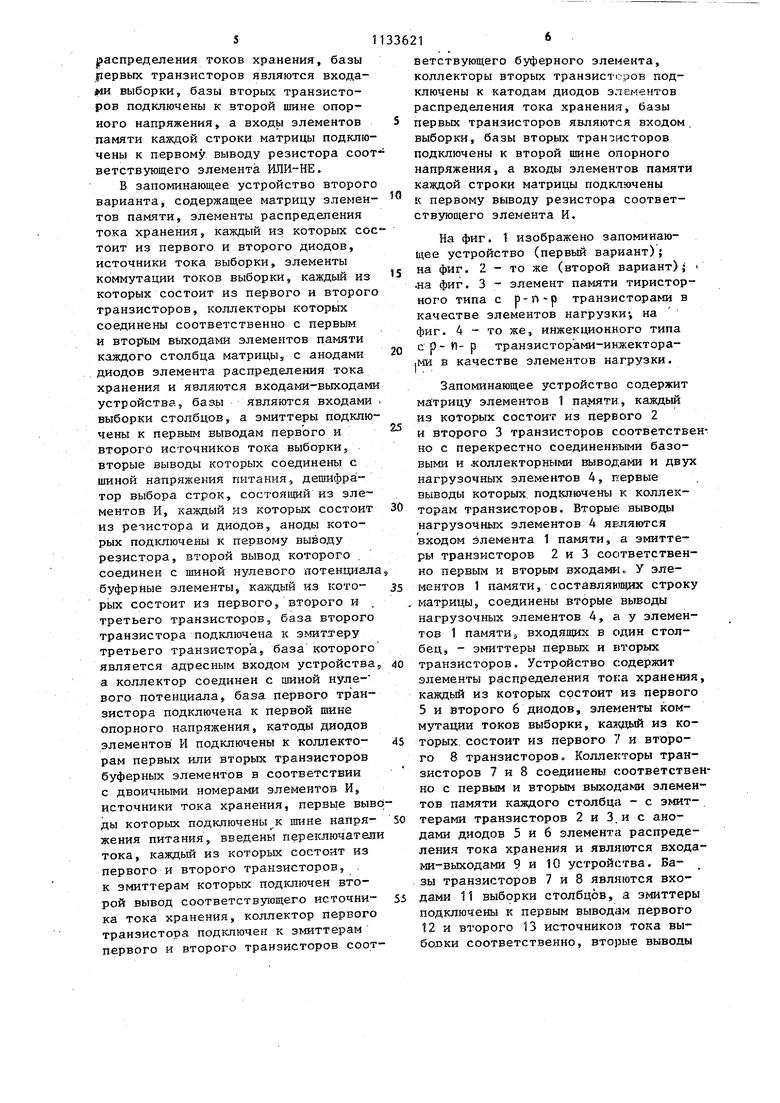

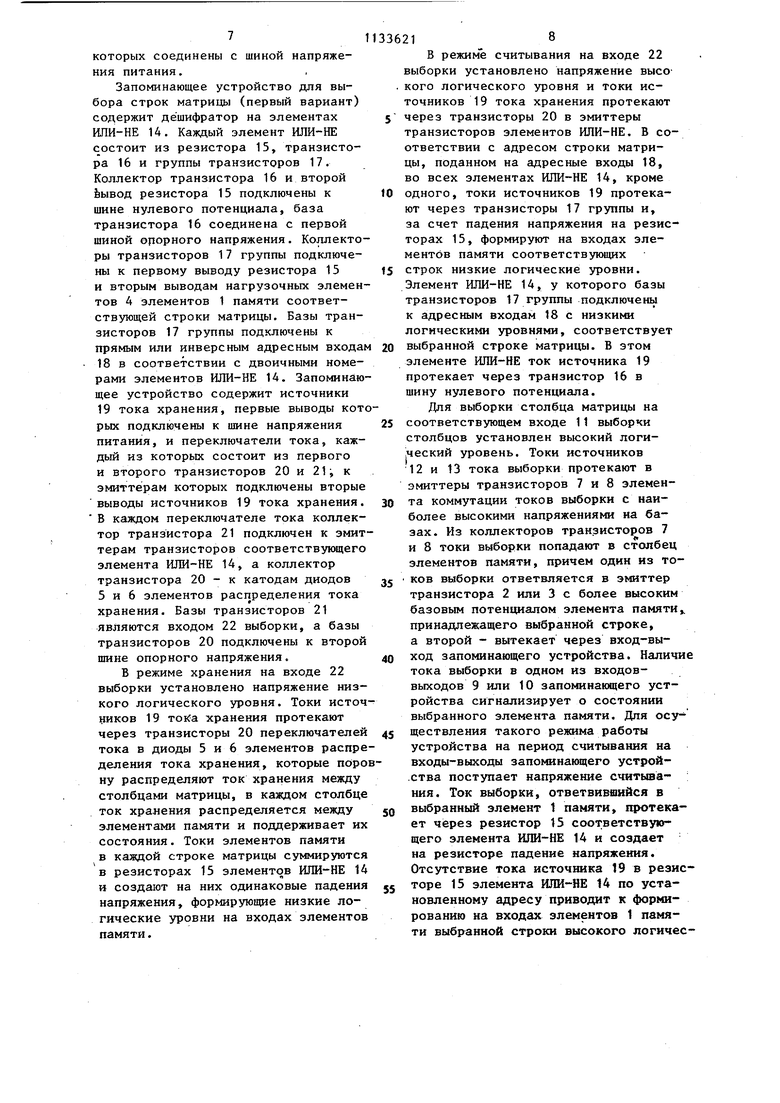

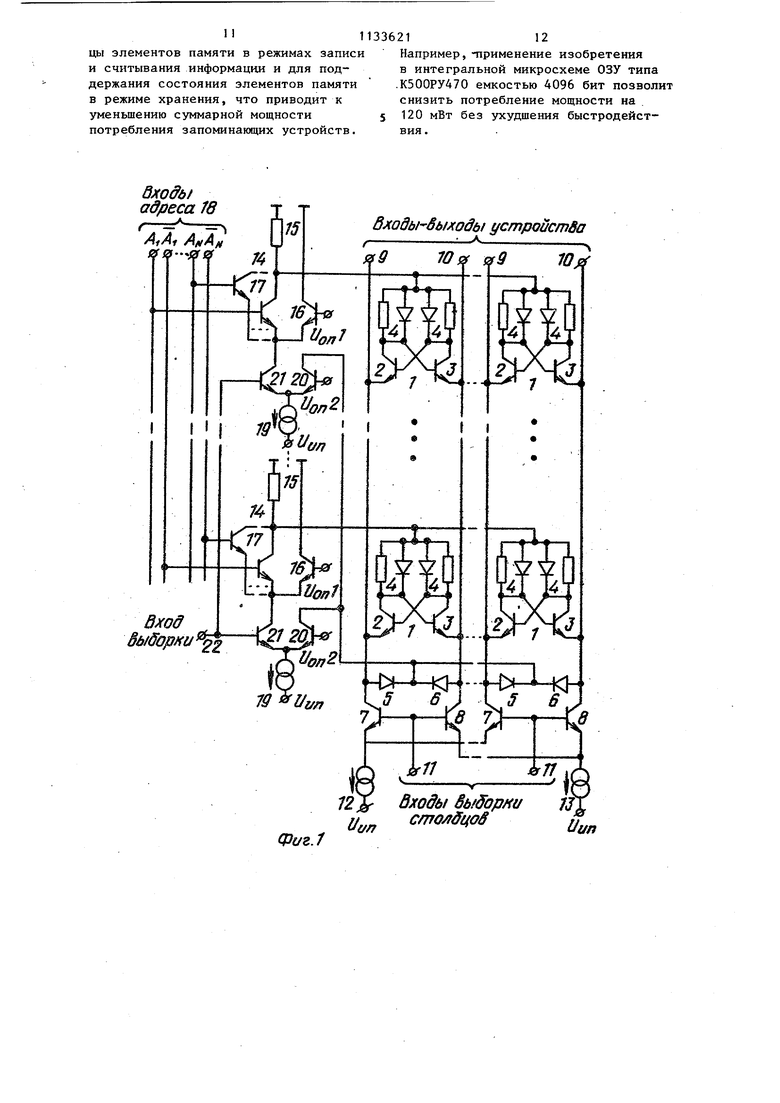

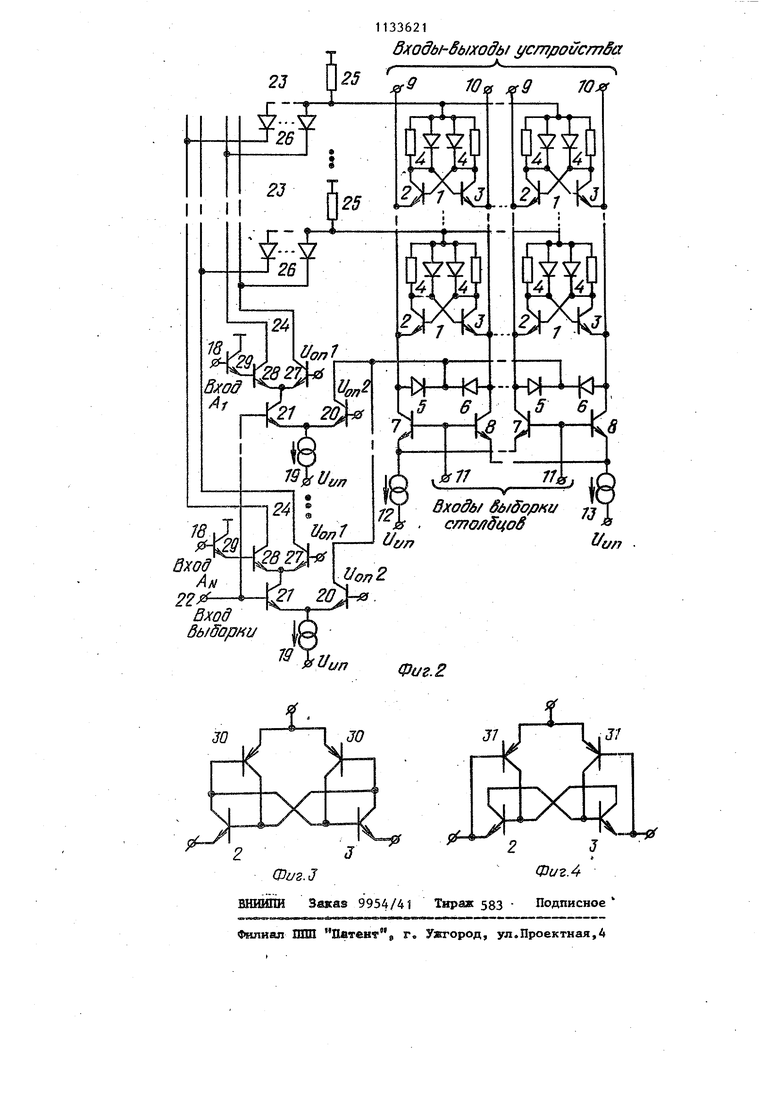

15 на фиг, 2 - то же (второй вариант); на фиг, 3 - элемент памяти тиристорного типа с р-п-р транзисторами в качестве элементов нагрузки-, на фиг. 4 - то же, инжекционкого типа

2Q с р - И- р транзисторами-ин;жектора,ьш в качестве элементов нагрузки.

Запоминающее устройство содержит матрицу элементов 1 памяти;, каждый из которых состоит из первого 2 и второго 3 транзисторов соответственно с перекрестно соединенными базовыми и -коллекторными выводами и двух нагрузочных элементов 4, первые выводы которых. под1 пючены к коллекторам транзисторов. Вторые; вывода нагрузочных элементов 4 ЯЕШЯЮТСЯ входом элемента 1 памяти, а эмиттеры транзисторов 2 и 3 соответственно первым и вторым входамио У элементов 1 памяти, составлявщих строку . матрицы, соединены вторые выводы нагрузочных элементов 4, а у элементов 1 памяти5 входящих в один столбец, эмиттеры первых и вторых

40 транзисторов. Устройство содержит

элементы распределения тока хранения, каждьй из которых состоит из первого 5 и второго 6 диодов, элементы коммутации токов выборки, каящый из которых. состоит из первого 7 и второго 8 транзисторов- Коллекторы транзисторов 7 и 8 соединены соответственно с первым и вторым выходами элементов памяти каждого столбца - с эмит-.

50 терами транзисторов 2 и З.и с анодами диодов 5 и 6 элемента распределения тока хранения и являются входа1У1и-вых:одами 9 и 10 устройства. Базы транзисторов 7 и 8 являются входами 11 выборки столбцов, а эмиттеры подключены к первым выводам первого 12 и второго 13 источников тока выболки соответственно, вторые выводы которых соединены с шиной напряжения питания. Запоминающее устройство для выбора строк матрицы (первый вариант) содержит дешифратор на элементах ИЛИ-НЕ 1А. Каждый элемент ИЛИ-НЕ состоит из резистора 15, транзистора 16 и группы транзисторов 17. Коллектор транзистора 16 и второй Ьывод резистора 15 подключены к шине нулевого потенциала, база транзистора 16 соединена с первой шиной опорного напряжения. Коллекто ры транзисторов 17 группы подключены к первому выводу резистора 15 и вторым выводам нагрузочных элемен тов 4 элементов 1 памяти соответствующей строки матрицы. Базы транзисторов 17 группы подключены к прямым или инверсным адресным входа 18 в соответствии с двоичными номерами элементов ИЛИ-НЕ 14. Запомина.ю щее устройство содержит источники 19 тока хранения, первые выводы кот рых подключены к шине напряжения питания, и переключатели тока, каждый из которых состоит из первого и второго транзисторов 20 и 21i к эмиттерам которых подключены вторые выводы источников 19 тока хранения. В каждом переключателе тока коллектор транзистора 21 подключен к эмит терам транзисторов соответствующего элемента ИЛИ-НЕ 14, а коллектор транзистора 20 - к катодам диодов 5 и 6 элементов распределения тока хранения. Базы транзисторов 21 являются входом 22 выборки, а базы транзисторов 20 подключены к второй шине опорного напряжения. В режиме хранения на входе 22 выборки установлено напряжение низкого логического уровня. Токи источ ников 19 тойа хранения протекают через транзисторы 20 переключателей тока в диоды 5 и 6 элементов распре деления тока хранения, которые поро ну распределяют ток хранения между столбцами матрицы, в каждом столбце ток храиения распределяется между элементами памяти и поддерживает их состояния. Токи элементов памяти в каждой строке матрицы суммируются в резисторах 15 элементов ИЛИ-НЕ 14 и создают на них одинаковые падения напряжения, формирующие низкие логические уровни на входах элементов памяти. 218 В режимё считывания на входе 22 выборки установлено напряжение высо кого логического уровня и токи источников 19 тока хранения протекают через транзисторы 20 в эмиттеры транзисторов элементов ИЛИ-НЕ. В соответствии с адресом строки матрицы, поданном на адресные входы 18, во всех элементах ИЛИ-НЕ 14, кроме одного, токи источников 19 протекают через транзисторы 17 группы и, за счет падения напряжения на резисторах 15, формируют на входах элементов памяти соответствующих строк низкие логические уровни. Элемент ИЛИ-НЕ 14, у которого базы транзисторов 17 группы подключены к адресным входам 18 с низкими логическими уровнями, соответствует выбранной строке матрицы. В этом элементе ИЛИ-НЕ ток источника 19 протекает через транзистор 16 в шину нулевого потенциала. Для выборки столбца матрицы на соответствующем входе 11 выборки столбцов установлен высокий логический уровень. Токи источников 12 и 13 тока выборки протекают в эмиттеры транзисторов 7 и 8 элемента коммутации токов выборки с наиболее высокими напряжениями на базах. Из коллекторов транзисторов 7 и 8 токи выборки попадают в столбец элементов памяти, причем один из токов выборки ответвляется в эмиттер транзистора 2 или 3 с более высоким базовым потенциалом элемента памяти,, принадлежащего выбранной строке, а второй - вытекает через вход-выход запоминающего устройства. Наличие тока выборки в одном из входоввыходов 9 или 10 запоминающего устройства сигнализирует о состоянии выбранного элемента памяти. Для осуществления такого режима работы устройства на период считывания на входы-выходы запоминакнцего устрой.ства поступает напряжение считьша- : ния. Ток выборки, ответвившийся в выбранный элемент 1 памяти, протекает через резистор 15 соответствующего элемента ИЛИ-НЕ 14 и создает на резисторе падение напряжения. Отсутствие тока источника 19 в резисторе 15 элемента ИЖ-НЕ 14 по установленному адресу приводит к формированию на входах элементов 1 памяти выбранной строки высокого логического уровня. Величина необходимого логического перепада на строках определяется превьшением величин ITOKOB источников 19 тока хранения над величинами токов источников 12 и 13 тока выборки и их соотношением. Запоминающее устройство второго варианта содержит дешифратор выбор строк, состоящий из элементов И 23 и буф-ерные элементы 24. Каждый элемент И состоит из резистора 25 и диодов 26. Аноды диодов 26 подключены к первому выводу резистора 25 и входам элементов памяти соответствующей строки матрицы, второй вывод резистора 25 соединен с шиной нуленого потенциала. Буферный элемент 24 состоит из транзисторов 27-29, ёаза транзистора 28 подключена к эмиттеру транзистора 29, база которого является адресным входом 18, а коллектор сое динен с шиной нулевого потенциала. База транзистора 27 подключена к первой шине опорного напряжения. Ка тоды диодов элементов И 26 подключен 1 к коллекторам транзисторов 28 и 29 буферных элементов в соответствии с двоичными номерами элеме тов И. Эмиттеры транзисторов 28 и 27 подключены к коллектору транзистора 21- соотвествующего переключателя тока. Выборка строки матрицы в запоминающем устройстве второго варианта происходит следующим образом. В режиме считывания на вход выборки поступает напряжение высокого логического уровня, и токи источников 19 тока хранения через транзисторы 21 поступают в буферные элементы 24. В соответствии с адресом строки поступающим на адрес.ные вхрды 18 устройства, ток коллектора транзистора 21 в калсдом из буферных элемен тов 24 протекает через один из тран зисторов 27 или 28. Выбранной строк соответствует элемент И 23, все диоды 26 которого подключены к тран зисторам буферных элементов 24 с отсутствием коллекторного тока. В остальных элементах И 23 за счет протекания тока источников 19 чере резисторы 25 формируются низкие выходные уровни. Необходимый перепад напряжений на входах элементов памяти в режиме выборки определяется 2110 соотношением токов источников 12, 13 и 19. Ток источника 12 или 13 тока выборки должен быть меньше, чем ток источника 19, приходящийся на один резистор 25 элемента И. В режиме записи выборка элемента памяти осуществляется так же,, как в режиме считывания. Во время записи на входах-выходах 9 и 10 апоминающего устройства установлены напряжения записи, которые принуждают выбранный элемент памяти принять соответствующее записываемой информации состояние. Напряжение записи верхнего уровня , поданное на эмиттер транзистора 2 или 3 выбранного элемента памяти, препятствует протеканию тока выборки в этот транзистор, а нижний уровень напряжения записи таким образом, чтобы ток выборки включался в эмиттер транзистора выбранного элемента памяти с низким уровнем на базе, При переключении выбранного элемента памяти в противоположное состояние напряжение на его входе сначала повьшается, причиной чего -является отключение тока выборки из элемента памяти и резистора 15 элемента ИЛИ-НЕ или резистора 23 .элемента И, а затем возврашдется к прежнему уровню после включения тока выборки в прежде закрытьш транзистор 2 или 3 элемента памяти. Элементы памяти могут содержать элементы нагрузки, состоящк1е из резисторов, зашунтированных диодами, или транзисторы 30 и 31 / --п-р-типа. Транзисторы.30 подключены по тиристорной схеме, у каждого транзистора база подключена к коллекто-. ру транэкстора 2 или 3, коллектор соединен с базой того же транзистора. Эмиттеры транзисторов 30 являются входом элемента памяти. Транзисторы 31 используются в качестве инжекторов. У каждого транзиетогра 31 база подключена к эмиттеру транзистора 2 или 3, коллектор соединен с базой того же транзистора. Эмиттеры транзисторов 31 являются входом элемента памяти. Применение предлагаемого технического решения в запоминающих устройствах позволяет использовать ток источников тока хранения для питания дешифратора выбора строк матрицы элементов памяти в режимах записи и считывания информации и для поддержания состояния элементов памяти в режиме хранения, что приводит к уменьшению суммарной мощности потребления запоминающих устройств.

72 У Входы Л71

(puz.l

Например, -применение изобретения в интегральной микросхеме ОЗУ типа .К500РУ470 емкостью 4096 бит позволит снизить потребление мощности на 120 мВт без ухудшения быстродействия.

бходы быходы устройства

lOff

сто/гдцод

Uun

Авторы

Даты

1985-01-07—Публикация

1983-04-08—Подача