ел

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Дешифратор адреса | 1988 |

|

SU1608745A1 |

| Формирователь сигналов выборки | 1985 |

|

SU1336099A1 |

| Накопитель | 1989 |

|

SU1656595A1 |

| Электронное устройство | 1987 |

|

SU1427518A2 |

| Устройство для обращения к памяти (его варианты) | 1982 |

|

SU1092561A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели переменного тока | 1985 |

|

SU1295439A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Запоминающее устройство | 1990 |

|

SU1751816A1 |

Изобретение относится к быстродействующим логическим схемам, а именно к дешифраторам, и может быть использовано в устройствах вычислительной техники и автоматики. Целью изобретения является повышение быстродействия дешифратора. Поставленная цель достигается за счет введения в дешифратор адреса диодов 6 с соответствующими связями. Диоды 6 совместно с резисторами 5 образуют элементы И, а переключатели тока на транзисторах 2, 4 и резисторах 5 - элементы ИЛИ-НЕ. Сигналы на входы элементов И могут быть поданы без инвертирования. Это позволяет исключить задержку входного сигнала при инвертировании. 1 ил.

ю

о

VI

Ю

ел ю

ON

Изобретение относится к быстродействующим логическим схемам и полупроводниковой технике и может быть использовано в устройствах вычислительной техники и автоматики.

Целью изобретения является повышение быстродействия дешифратора.

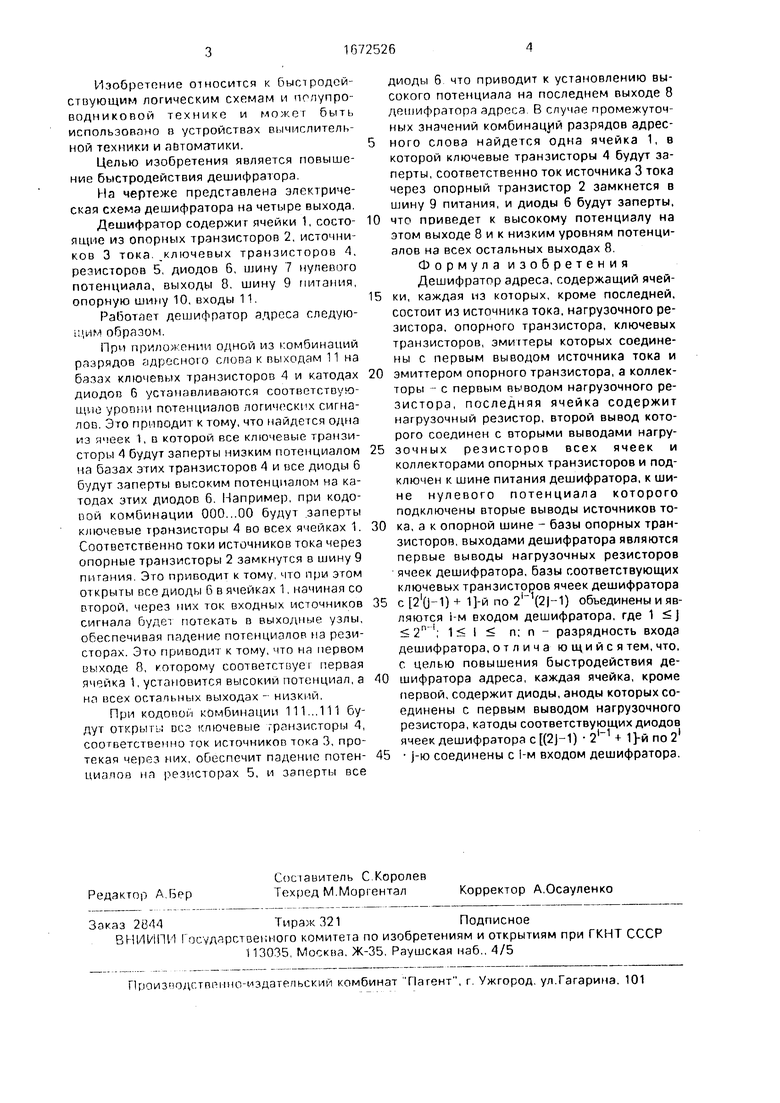

На чертеже представлена электрическая схема дешифратора на четыре выхода.

Дешифратор содержит ячейки 1, состоящие из опорных транзисторов 2, источников 3 тока, ключевых транзисторов 4, резисторов 5, диодов 6, шину 7 нулевого потенциала, выходы 8. шину 9 питания, опорную шину 10, входы 11.

1эаботает дешифратор адреса следующим образом.

При приложении одной из комбинаций разрядов адресною слова к выходам 11 на базах ключевых транзисторов А и катодах диодов 6 устанавливаются соответствующие уровни потенциалов логических сигналов. Это приводит к тому, что найдется одна из ячеек 1, в которой все ключевые транзисторы 4 будут заперты низким потенциалом на базах этих транзисторов 4 и все диоды 6 будут заперты высоким потенциалом на катодах этих диодов 6. Например, при кодо- пой комбинации 000...00 будут заперты ключевые транзисторы 4 во всех ячейках 1. Соответственно токи источников тока через опорные транзисторы 2 замкнутся в шину 9 питания. Это приводит к тому, что при этом от крыты все диоды 6 в ячейках 1, начиная со второй, через них ток входных источников сигнала будет потекать в выходные узлы, обеспечивая падение потенциалов на резисторах. Это приводит к тому, что на первом выходе 8, которому соответствую первая ячейка 1, установится высокий потенциал, а на всех остальных выходах - низкий.

При кодопой комбинации 111...111 будут открыть: осз ключевые транзисторы 4, соответственно ток источников тока 3, протекая через них, обеспечит падение потенциалов на резисторах 5, и заперты все

0

5

0

диоды 6 что приводит к установлению высокого потенциала на последнем выходе 8 дешифратора адреса В случае промежуточных значений комбинаций разрядов адресного слова найдется одна ячейка 1, в которой ключевые транзисторы 4 будут заперты, соответственно ток источника 3 тока через опорный транзистор 2 замкнется в шину 9 питания, и диоды 6 будут заперты, что приведет к высокому потенциалу на этом выходе 8 и к низким уровням потенциалов на всех остальных выходах 8. Формула изобретения Дешифратор адреса, содержащий ячейки, каждая из которых, кроме последней, состоит из источника тока, нагрузочного резистора, опорного транзистора, ключевых транзисторов, эмигтеры которых соединены с первым выводом источника тока и эмиттером опорного транзистора, а коллекторы - с первым выводом нагрузочного резистора, последняя ячейка содержит нагрузочный резистор, второй вывод которого соединен с вторыми выводами нагрузочных резисторов всех ячеек и коллекторами опорных транзисторов и подключен к шине питания дешифратора, к шине нулевого потенциала которого подключены вторые выводы источников тока, а к опорной шине - базы опорных транзисторов, выходами дешифратора являются первые выводы нагрузочных резисторов ячеек дешифратора, базы соответствующих ключевых транзисторов ячеек дешифратора 5 с 20-1) + по 2м(2|-1) объединены и являются i-м входом дешифратора, где 1 j 2П ; 1 I n: n - разрядность входа дешифратора, отлича ющийся тем, что, с. целью повышения быстродействия дешифратора адреса, каждая ячейка, кроме первой, содержит диоды, аноды которых соединены с первым выводом нагрузочного резистора, катоды соответствующих диодов

5

0

0

1-1

,1

ячеек дешифратора с (2J-1) -2 + 1}-й по 2 5 j-ю соединены с I-м входом дешифратора.

| Микроэлектроника, т | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Валиев К.А | |||

| и Орликовский А.А | |||

| Полупроводниковые интегральные схемы памяти на биполярных транзисторных структурах | |||

| М.: Сов | |||

| радио, 1979, с 222, рис | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1991-08-23—Публикация

1989-07-03—Подача