L ФФ

С

с;

СС

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1338094A1 |

| Синтезатор частот | 1986 |

|

SU1478328A1 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

| Цифровой термометр | 1987 |

|

SU1571427A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Автоматический цифровой измеритель коэффициента гармоник | 1980 |

|

SU911363A1 |

| ЦИФРОВОЙ ФАЗОВЫЙ ДИСКРИМИНАТОР | 1972 |

|

SU349007A1 |

| Цифровой фазометр | 1986 |

|

SU1368807A1 |

| Цифровое фазосдвигающее устройство | 1988 |

|

SU1622835A1 |

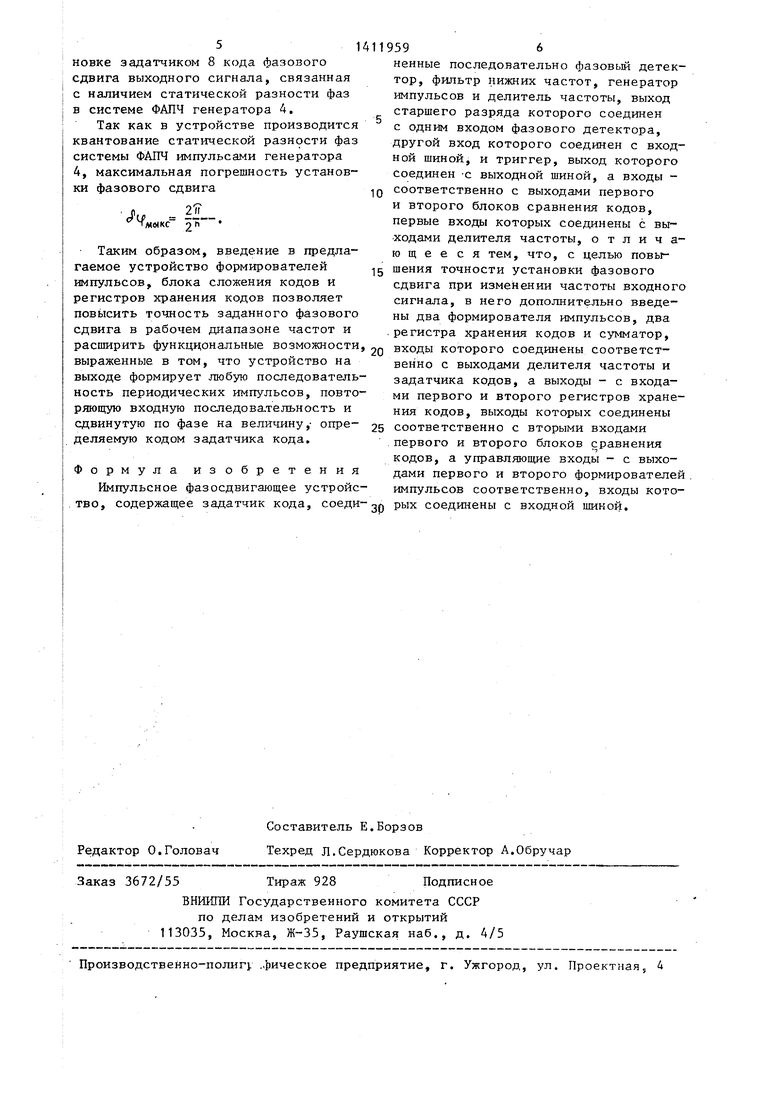

Изобретение относится к импульсной технике и может быть использовано для точной задержки периодических импульсных сигналов в системах ровой фазовой автоподстройки. Изобретение позволяет повысить точность установки фазового сдвига выходного сигнала при изменениях частоты входного сигнала. Устройство содержит фазовый детектор 1, делитель 2 частоты, фильтр 3 нижних частот, генератор 4 импульсов, блоки 5 и 6 сравнения кодов, сумматор 7, задатчик 8 кодов, регистры 9 и 10 хранения кодов, формирователи 11 и 12 импульсов, триггер 13. Введение в устройство формирователей импульсов, блока сложения кодов и регистра хранения кодов повышает точность заданного фазового сдвига в рабочем диапазоне частот и расширяет функциональные возможности устройства в связи с тем, что при этом устройство формирует на выходе любую последовательность периодических импульсов, повторяющую входную последовательность и сдвинутую по фазе на величину, определяемую кодом задатчика кода. 1 ип SS (/ с

Изобретение относится к импульс- |ной технике и может быть использова- Ио для точной задержки периодических импульсных сигналов в системах цифровой фазовой автоподстройки.

Целью изобретения является повышение точности установки фазового сдвига выходного сигнала при изменениях частоты входного сигнала.

На чертеже представлена функциональная схема импульсного фазосдви- гающего устройства

Устройство содержит фазовый детек- тор (ФД) 1, делитель 2 частоты, фильт 3 нижних частот (ФНЧ), генератор 4 импульсов, блоки 5 и 6 сравнения кодов, сумматор 7, задатчик 8 кодов, регистры 9 и 10 хранения кодов, формирователи 11 и 12 импульсов и триг- гер 13, при этом входная шина соединена с входами формирователей 1 и 12 импульсов и первым входом ФД 1, выход которого через ФИЧ 3 соединен с входом генератора 4 импульсов,, выход ко- торого подключен к входу делителя 2 частоты, выход старшего разряда кото- рого соединен с вторым входом ФД 1, а его все выходы - с первыми входами блоков 5 и 6 сравнения кодов и первыми входами сумматора 7, вторые входы которого соедш1ены с выходами задат- чика 8 кодов, а выходы - с входами регистров 9 и 10 хранения кодов, уп- равляющие входы которых соединены соответственно с выходами формирова- телей 11 и 12 импульсов, а выходы - соответственно с входами блоков 5 и 6 сравнения кодов, выходы которых соединены с входами триггера 13, выход которого соединен с выходной ши

НОЙо

Импульсное фазосдвигающее устройсво работает следующим образом.

Входной сигнал поступает на входы формирователей 11 и 12 и на вход ФД 1 , На выходе формирователя 1 1 импульсы появляются в момент времени, соответствующий переднему фронту вхоного сигнала, а на выходе формирователя 12 импульсы появляются в момент времени, соответствующий заднему фронту входного сигнала,

На второй вход ФД 1 поступает сигнал с выхода старшего разряда делителя 2, имеющего форму симметричного меандра.

Управление генератором 4 осуществляется сигналом рассс. ..асования ФД

.

который поступает на управляющий вход генератора 4 через ФНЧ 3.

При синхронизме фазовой автоподстройки частоты (ФАПЧ) частота сигнала на выходе генератора 4

f ,

где f - частота выходного сигнала

генератора 4;

F - частота входного сигнала; п - разрядность делителя частоты.

При этом между входным сигналом и сигналом с выхода старшего разряда делителя 2 существует статическая разность фаз, зависящих от частоты входного сигнала и ухода частоты генератора 4 в процессе работы.

На выходах делителя 2 формируется код текущего значения фазы импульсов старшего разряда делителя 2, С выходов делителя 2 код текущего значения фазы импульсов старшего разряда делителя 2 поступает на первые входы блоков 5 и 6 сравнения и на первый вход сумматора 7, На вторые входы сумматора 7 и задатчика 8 кода поступает управляющий код, определяющий величину сдвига фазы выходного сигнала относительно входного сигнала, На выходе сумматора 7 присутствует суммарный код текущего значения фазы сигнала старшего разряда делителя 2 и управляющего кода сдвига фазы задатчика 8 кодао С выхода сумматора 7 суммарньй код поступает на входы регистров 9 и 10 хранения кодов.

Б момент времени, соответствующий заднему фронту входного сигнала, делитель 2 на своих выходах формирует код, соответствующий статической разности фаз (ф между входным сигналом И сигналом старшего разряда делителя 2

ФБ 2 где N - значение кода в десятичной

системе счисления, В результате в регистр 10 по сигналу, поступающему на его управляющий вход, с выхода формирователя 12 в момент времени, равный заднему фронту входного сигнала, записывается код, соответствующий сумме кодов статической разности фаз в системе ФАПЧ генератора 4 и угфавляющего кода с задатчика 8 кода, а в р(гистр 9

по сигналу, поступающему на его управляющий вход, с выхода формирователя 11 записывается код, соответствующий сумме кодов текущего значения фазы старшего разряда делителя 2, в момент времени, равный переднему фронту входного сигнала, и управляющего кода задатчика 8 кода.

В момент времени, соответствующий JQ равенству текущего кода фазы делителя 2 и суммирующего кода, записанного в регистре 9, на выходах блока 5 сравнения появляется импульс, который

ЩИ11 переднему фронту вхолног о nii-i;.- -- ла;

п - разрядность делителя часто rt-.i.

Если задан нулевой фазовый сдвиг (на выходах задатчика 8 кода присутствуют сишаль логического О),а в системе ФА1ГЧ присутствует статическая разность фаз ( в регистр 10 записывается двоичный код числа N , а в регистр 9 - двоичньй код числа N..

В момент времени, равный приходу заднего фронта входного сигнала на

переводит выходной триггер 13 jj выходах делителя 2 формируется двоичный кйд числа Щ-Q , но этот код записан в регистр 10, т.е. на выходе блока 6 сравнения появляется импульс, которьш переводит триггер 13 в состояние логического О и формирует згщний фронт выходного сигнала. В момент времени, соответствующий переднему фронту входного сигнала, на выходах делителя 2 формируется двоичничное состояние, а в мси-шнт времени, соответствующий равенству текущего кода фазы делителя 2 и суммирующего кода, записанного в регистре 10, на выходе блока 6 сравнения появляет- JQ ся импульс, который переводит триггер 13 в нулевое состояние, Таким образом, на выходе устройства формируется сигнал, повторяющий форму

входного сигнала и сдвинутый по фазе 25 числа N, который записан в

регистр 9. Триггер 13 импульсов с выхода блока 5 сравнения переводится в состояние логической 1 и формирует передний фронт выходного сигнал

на величину, определяемую только кодом задатчика 8 кода„

Таким образом фазовые сдвиги переднего Lf и заднего фронтов выходного сигнала относительно заднего фронта сигнала старшего разряд делителя 2 (нулевого значения теку- щего кода фазы старшего разряда де- лителя 2), коды которых записаны в регистрах 9 и 10, равны

f , ,

где If - значение фазового сдвига, определяемого задатчиком 8 кода; (у- значение фазового сдвига переднего фронта входного сигнала относительно заднего фронта сигнала старшего разряда делителя 2 Значения i/ и Lp равны

-N||-

.

где N - значение кода в десятичной системе счисления на выходе задатчика 8 кода;

N - значение кода в десятичной системе счисления на выходах делителя 2 в момент времени, соответствуюЩИ11 переднему фронту вхолног о nii-i;.- -- ла;

п - разрядность делителя часто rt-.i.

Если задан нулевой фазовый сдвиг (на выходах задатчика 8 кода присутствуют сишаль логического О),а в системе ФА1ГЧ присутствует статическая разность фаз ( в регистр 10 записывается двоичный код числа N , а в регистр 9 - двоичньй код числа N..

В момент времени, равный приходу заднего фронта входного сигнала на

выходах делителя 2 формируется двоичный кйд числа Щ-Q , но этот код записан в регистр 10, т.е. на выходе блока 6 сравнения появляется импульс, которьш переводит триггер 13 в состояние логического О и формирует згщний фронт выходного сигнала. В момент времени, соответствующий переднему фронту входного сигнала, на выходах делителя 2 формируется двоич числа N, который записан в

регистр 9. Триггер 13 импульсов с выхода блока 5 сравнения переводится в состояние логической 1 и формирует передний фронт выходного сигнала,

Таким образом, выходной сигнал повторяет форму входного сигнала и не имеет фазового сдвига, происходит компенсация статического фазового сдвига ФАПЧ.

При изменении частоты входного сигнала либо при уходе частоты генератора 4 в режиме синхронизации происходит изменение статической разности фаз между входным сигналом и сигналом с выхода старшего разряда делителя 2 частоты на величину

45

I

Это изменение статической разности фаз в системе ФАПЧ генератора приводит к изменению текущих кодов фазы на выходах делителя 2, в момент времени, соответствующий переднему и заднему фронтам входного сигнала, учитывается в сумматоре 7 и заносится в регистры 9 и 10 хранения кодов. Тем самым компенсируется ошибка в установке эадатчиком 8 кода фазового сдвига выходного сигнала, связанная с наличием статической разности фаз в системе ФАПЧ генератора 4,

Так как в устройстве производится квантование статической разности фаз системы ФАГГЧ импульсами генератора 4, максимальная погрешность установки фазового сдвига

.

MOlKC

2ff 2

Таким образом, введение в предлагаемое устройство формирователей импулвсов, блока сложения кодов и регистров хранения кодов позволяет повысить точность заданного фазового сдвига в рабочем диапазоне частот и распшрить функциональные возможности, выраженные в том, что устройство на выходе формирует любую последовательность периодических импульсов, повторяющую входную последовательность и сдвинутую по фазе на величину,- опре- деляемую кодом задатчика кода.

Формула изобретения

Импульсное фазосдвигающее устройство, содержащее задатчик кода, соеди

5

Q 5

р

ненные последовательно фазовый детектор, фильтр нижних частот, генератор импульсов и делитель частоты, выход старшего разряда которого соединен с одним входом фазового детектора, другой вход которого соединен с входной шиной, и триггер, выход которого соединен -с выходной шиной, а входы - Q соответственно с выходами первого и второго блоков сравнения кодов, первые входы которых соединены с выходами делителя частоты, отличающееся тем, что, с целью повышения точности установки фазового сдвига при изменении частоты входного сигнала, в него дополнительно введены два формирователя импульсов, два .регистра хранения кодов и сумматор, входы которого соединены соответственно с выходами делителя частоты и задатчика кодов, а выходы - с входами первого и второго регистров хранения кодов, выходы которых соединены соответственно с вторыми входами первого и второго блоков сравнения кодов, а управляющие входы - с выходами первого и второго формирователей импульсов соответственно, входы которых соединены с входной шиной.

| Карпов Р.Г | |||

| и дро Преобразование и математическая обработка ши- ротно-импульсных сигналов - М.: Машиностроение, 1977, с.67-68 | |||

| Импульсное фазосдвигающее устройство | 1974 |

|

SU526068A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| О | |||

Авторы

Даты

1988-07-23—Публикация

1986-09-30—Подача