Изобретение относится к теплоэнергетике и может быть использовано в системах автоматического регулирования температур пара котлоафегата.

Цель изобретения - автоматизация про- цесса выбора параметров динамической настройки системы и расширение диапазоона качественного регулирования при различных режимах работы объекта.

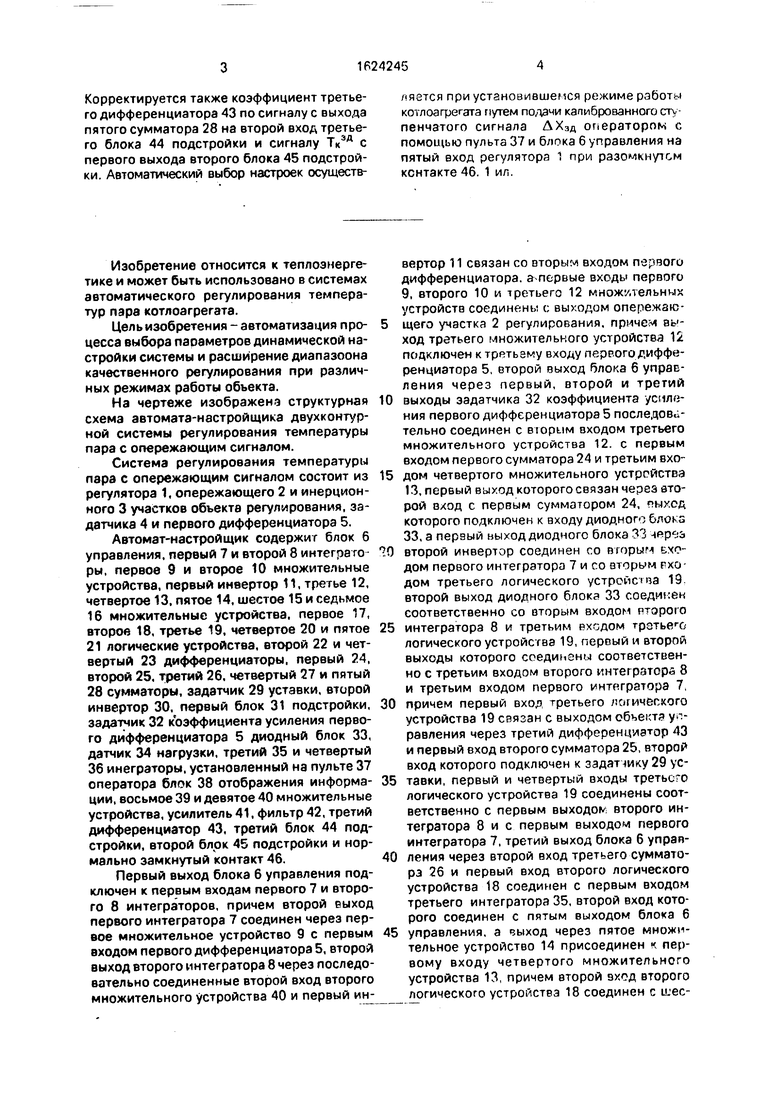

На чертеже изображена структурная схема автомата-настройщика двухконтур- ной системы регулирования температуры пара с опережающим сигналом.

Система регулирования температуры пара с опережающим сигналом состоит из регулятора 1, опережающего 2 и инерционного 3 участков объекта регулирования, за- датчика 4 и первого дифференциатора 5.

Автомат-настройщик содержит блок 6 управления, первый 7 и второй 8 интеграго ры, первое 9 и второе 10 множительные устройства, первый инвертор 11, третье 12, четвертое 13. пятое 14, шестое 15 и седьмое 16 множительные устройства, первое 17, второе 18, третье 19, четвертое 20 и пятое 21 логические устройства, второй 22 и четвертый 23 дифференциаторы, первый 24, второй 25. третий 26, четвертый 27 и пятый 28 сумматоры, задатчик 29 уставки, второй инвертор 30, первый блок 31 подстройки, задатчик 32 коэффициента усиления первого дифференциатора 5 диодный блок 33, датчик 34 нагрузки, третий 35 и четвертый 36 инегрэторы, установленный на пульте 37 оператора блок 38 отображения информа- ции, восьмое 39 и девятое 40 множительные устройства, усилитель 41, фильтр 42, третий дифференциатор 43, третий блок 44 подстройки, второй блок 45 подстройки и нормально замкнутый контакт 46.

Первый выход блока 6 управления подключен к первым входам первого 7 и второго 8 интеграторов, причем второй выход первого интегратора 7 соединен через первое множительное устройство 9 с первым входом первого дифференциатора 5, второй выход второго интегратора 8 через последовательно соединенные второй вход второго множительного устройства 40 и первый инвертор 11 связан со вторым входом первого дифференциатора, впервые входы первого 9, второго 10 и третьего 12 множительных устройств соединены с выходом опережающего участка 2 регулирования, причем выход третьего множительного устройства 12 подключен к третьему входу перрого дифференциатора 5, второй выход блока 6 управления через первый, второй и третий выходы задатчика 32 коэффициента усиления первого дифференциатора 5 последов«- тельно соединен с вторым входом третьего множительного устройства 12. с первым входом первого сумматора 24 и третьим входом четвертого множительного устройства 13, первый выход которого связан через второй вход с первым сумматором 24, «ыход которого подключен к входу диодного блоьз 33, а пераый выход диодного блока 33 второй инвертор соединен со вторым ЕХО- дом первого интегратора 7 и со вторым РХО- дом третьего логического устройснза 19 второй выход диодного блока 33 соединен соответственно со вторым входом рторого интегратора 8 и третьим РХОДОМ трзтьего логического устройства 19, первый и второй выходы которого соединены соответственно с третьим входом второго интегратора 8 и третьим входом первого интегратора 7, причем первый вхол третьего леничесхого устройства 19 связан с выходом объект; управления через третий дифференциатор 43 и первый вход второго сумматора 25, второй вход которого подключен к задатмку 29 уставки, первый и четвертый входы третьего логического устройства 19 соединены соответственно с первым выходов второго интегратора 8 и с первым выходом первого интегратора 7, третий выход блока 6 управления через второй вход третьего сумматора 26 и первый вход второго логического устройства 18 соединен с первым входом третьего интегратора 35, второй вход которого соединен с пятым выходом блока 6 управления, а «зыход через пятое множительное устройство 14 присоединен ч первому входу четвертого множительного устройства 13, причем второй вход второго логического устройства 18 соединен с шеегым входом блока 6 управления, четвертый Bt ход которою через второй вход четвертого сумматора 27 и первое логическое устройство 17 присоединен к первому входу чет-вертого интегратора 36, второй вход которого соединен с шестым выходом блока б управления, а выход четвертого интегратора 36 присоединен к первому входу блока 38 отображения информации и через второй вход пятого сумматора 28 - к второму входу блока 38 отображения информации, причем первый вход пятого сумматора 28 присоединен к выходу первого множительного устройства 9, первый вход блока 6 управления подключен к выходу шестого множительного устройства 15череч четвеотое логичэское устройство 20, причем первый вход шестого множительного устройства 15 соединен с выходом пятого множительного устройства 14, а второй вход шестого множител нэго устройства 15 соединен с выходом датчика 34 нагрузки, который подключен к второму входу четвертого множительного 13 устройства, второму входу седьмогг множительного устройства 16, четвертому входу блока 38

отображения информации и через первый и второй выходы первого блока 31 подстройки подкпючен соответственю к четвертым входам регулятора 1 и первого дифференциатора 5, причем третий пход блока 38 отобрэжения информации соединен i: выходом седьмого множительного устройства 16, третий вход которого подключен к выходу пятого сумматора 28, а первый вход - к выходу четвертого множительного устройства 13, второй вход блока 6 управления через пятое логическое устройство 21 подключен к выходу второго сумматора 25, первый пход которого через второй дифференциатор 22 связан с выходом обьекта управления, а второй подключен к задзтчику 29 уставки, четвертый вход блока 6 управления присоединен к выходу объекта управления, который также соединен с первыми выходами третьего 26 и четвертого 27 сумматоров, третий вход блока 6 управления соединен с пультом 37 оператора, пятый вход блока 6 управления через четвертый дифференциатор 23 связан с выходом датчика 34 нагрузки, седьмой выход блока 6 управления соединен с пятым входом регулятора 1, восьмой выход блока 6 управления подключен к шестому выходу регулятора 1 через второй вход нормально замкнутого контакта 46, первый вход которого соединен с выходом датчика 34 нагрузки через первый выход второго блока 45 подстройки, четвертый вход третьего дифференциатора 43 и первый вход восьмого множительного устройства 39, второй вход которого подключен к выходу третьего блока 44 подстройки, а первый и второй входы третьего блока 44 подстройки -- к выходам пятого сумматора 28, причем третий вход третьего

дифференциатора 43 подключен к выходу девятого множительного устройства 40, первый и второй входы которого соединены соответственно с уситителем 41 и выходом седьмого множительного устройства 16.

Автомэт-назтройщикдвухконтурной системы регулирования темперагуры пара с опережающим сигналом работает следующим образом.

В рабочем состоянии отрабатывается

задание Хдц поступающее с задатчика 4 или внутренние ri и внешние f2 возмущения. Регулируемая величина Х({) находится в допустимых пределах. Первый блок 31 подстройки формирует согласно нагрузке котла

сигналы D по коррекции с первого выхода - коэффициента Кр усиления регулятора 1 и второго выхода - постоянную Тд интегрирования первого дифференциатора 5.

Также осуществляется коррекция коэффициента третьего дифференциатора 43 путем подачи с выхода пятого сумматора 28 сигнала bi, нэ второй вход третьего блока 44 подстройки, а на первый вход - сигнала заданной постоянной ткзл времени со втооого выхода второго блока 45 подстройки. На выходе блока 44 получают сигнал К (bi - -ТкЗД)Ткзд, который поступает на второй вход восьмого множительного устройства 39, где умножается ла сигнал, поступающий

на первый вход с выхода второго дифференциатора 43, причем во втором блоке 45 подстройки значение заданной постоянной ткуд времени корректируется сигналом D по нагрузке котла, поступающего с выхода датчика 34 нагрузки. При этом нормально замкнутый контакт 46, пульт 37 оператора и блок 6 управления находится в исходном положении.

Режим адаптации осуществляется при

установившемся состоянии работы котла (контроль ведется на блоке 38 отобрахсения информации по сигналу D) путем подачи калиброванного ступенчатого сигнала Д Х3д по инициативе оператора через пульт 37 оператора и блок 6 управления, причем до подачи имдентифицирующего сигнала АХзд с первого выхода блока 6 управления через первые входы первого 7 и второго 8 интеграторов устанавливаются нулевые условия

- а дкд 0 и а д кд 0 , а со второго выхода блока 6 управления соответственно через первый, второй и третий выходы задатчика 32 коэффициента усиления первого дифференциатора 5 устанавливается начальное значение Kg - Кдс на третьем множительном устройстве 12, четвертом множительном устройстве 13 и первом сумматоре 24, при подаче сигнала D- 1/ai3A с выхода датчика 34 нагрузки на входы чет вертого 13, шестого 15 и седьмого 16 множительных устройств с восьмого выхода блока 6 управления осуществляется размыкание контакта 46. После этоголэсущесгвля- ется подача калиброванного ступенчатого сигнала АХ3д на пятый вход регулятора 1. Одновременно включаются третий 35 и чзт- вертый 36 интеграторы и г.одаются сигналы соответственно с третьего выхода 5 ока 6 управления (величиной 0.663 АХЭд) на t-торой вход третьего сумматор 26 и j четвертого выхода (величиной Д per) на второй вход четвертого сумматора 27. З&тем сигнал X(t) сравнивают на четвертом сумматоре 27 с Дрег и при X(t) Дрег первое логическое устройство 17, воздействуя на первый оход четвертого интегратора 36, останавпиезет его, выход которого фиксирует величину t3 поступающую на второй вход пятого сумматора 28 и первый вход блока 38 отображения информации. Далее сигнал X(t) сравнивают на третьем сумматоре 26 с величиной 0,Ь63 Д Хзд и при X{t) 0,663 ДХГд второе логическое устройство 18, воздейсл вуя на первый вход третьего интегратора 35 останавливает его, фиксируя величину to.i i, которая в пятом множительном устройстве 14 умножается на константу 0,883, на выходе которого получаем величину ai, которая поступает соответственно на шестое 15 г четвертое 13 множительное устройства, с также на первый вход пятого 28. Одновременно второй выход рторсго псги- ческого устройства 18 через шестой вход блока 6 управления обрабатывает сигнал ДХзд задатчика до нуля. При этом на пятом сумматоре 28° определяется значение - 1з, которое однсзременно подается на седьмое множительное устройство 16 и блок 38 отображения информации. Далее в шестом множительном устройстве 15 перемножаются сигналы at и 1/й1ЗД, т.е. ai/ai3A и результат сравнивают в четвертом логическом устройстве 20 с заданием 0,9 и 1,1 и если 0,9 ai/ai3fl 51,1, то через первый вход блока 6 управления цикл останавливается и с ЕЫ- хода четвертого множительного устройства 13, где происходит умножение а 1 /ai3A КДг получают сигнал Кдн, т.е. Кдг KftHl а сигнал с выхода седьмого множительного устоой- ства 16 получают равным Кин. так как КИн TA/ai3A Кдн, который и подается на третий вход блока 38 отображения информации Если же четвертое логическое устройство 20

0

5

3

5

0

5

0

0

5

установит, что 0,9 31/ьГд 1.1, то с иихоли этого устройства на первый Ы,с а 5 упоавления сигнал не поступает на остаьод- ку цикла, а с выходз четверо -о множительного устройства 13 появится оигнз/s Кдн -t Кдс, который поступит на второй; вход пео вого сумматора 24, где он сравнивается сигналом Кдс и через диодный блок 33 раз ность сигналов (Кдс - Кдч) включает m гзы; 7 и второй 8 интеграторь1, соответственно воздействуя на их вторые входы гсли (Кдс - Кдн)0, то через второй 30 включается первый интегратор 7, второй виход которого начнет корректирооап / ; нч перьев множительном устоойог е через второй вход соли ,v- - , то второ 1 выход диодно.о ;,ока 33 через OTODOM гхол интегратора 8 включает последний. исм«нчя через второй вход второю г.но /т-льного

устоойства 10 значением кд Одновременно сигналы г. диодного блгка-Г подаются на аторой и третий входы третьего логиче оп устройства 1°, где сравниваются с пятым и первым выходами по гюго 7 второго о интеграторов и в слу эе их расс- с,тоа третье логическое устро/с во г оста -fdt ли- аает первый 7 и лторой J , PVP соотиетстренно va x :еты/1 входы В результате ус1 навлиааеггя новое знамени -- Кдч - - А Ккд. о- ти . циффрренцчатор 22 опрдлРГ| iST ) /d и срэениоает с ставкой -/«зтчлча 29-к - О Уели dx(r) / ti t тс п зтсс/с п- ческоеусгроигтво 21, :.оздейству1 а В прэвпения, через второй sxo инициирует покачу НчОвого с угтенча эю втде стзия XJA, т.е продолжает до Р -пгне- .1ия уело ия 09 а /Л1зд 1.1.

Формула изобретения Автомат настроивикдвухксл;урН 4ХСч стем регулирования с опере каюа1им сигналом, содержащий (рильто подключенный я цепь обратной связи системы второй выход которого соединен с пераым входом первого дифферэнциатора, ко оторому Г)ходу которого подключен вь-хсд инерционного участка объекта, а второй выход .г.зю- щого участка объекта управления соединен с входом силителя, дифференциатор, , которого соединен с выходом инерционного участка обьекта управлег ия, о т- л ичающийся тем, что, с цель.о автоматизации процесса выбора пэрзметров динамической настройки системы и расширения диапазона качественного регулирования в широком диапазоне изменения параметров характеристик объекта, система дополнительнс снабжена блоком управления, первым, вторым, третьим и четвертым интегра- TOpdMH, первым -- девятым множительными устройствами, первым и вторым инверторами, перяим - пятым логическими устройствами, третьим и четвертым дифференциаторами, первым - шестым сумматорами, задзтчиком установки, первым, вторым и третьим блоками подстройки, задачником коэффициентов усиления первого дифференциатора. диодным блоком отображения информации, усилителем фильтром, нормально замкнутым контактом и блоком деления, причем первый выход блока управления соединен с первыми входами первого и второго интеграторов, причем второй выход первого интегратора соединен через первое множительное устройство первь.м эхо дом первого дифференциатора, второй выход второго интегратора через последо- вательно соединенные рторой вход множительного устройства и пеоиый инвертор связан с вторым входом первого дифференциатора, а первые входы первого, второго и третьего множительных устройств соедине- ны с выходами опережающего участка уп- раьления, причем выход третьего множительного устройства подключен к третьему входу первого дифференциатора, второй выход блока управления чорез оыхо- ды один, два и три задатчика коэффициента усиления первого дифференциаторе последовательно соединен с вторым входом третьего множительного устройства, с первым входом первого сумматора и третьим входом четвертого множительного устрой ства, первый выход которого связан через второй вход с первым сумматором, выход которого подключен к входу диодногс оло ка, а первый выход диодногс блока через чторой инвертор соединен с вторым аходсм первого интегратора и вторым входом третьего логического устройства, второй выход диодного блока соединен соответственно с вторым входом второго интегратора и третьим входом третьего логического устройства, первый и второй выходы которого соединены соответственно с третьим входом второго интегратора и третьим входом первого интегратора, причем первый и четвертый входы третьего логического устройства соединены соответственно с первым выходом второго интегратора и первым выходом первого интегратора, третий выход блока управления через второй вход третьего сумматора и первый вход второго логического устройства соединен с первым входом третьего интегратора, второй вход которого соединен с пятым выходом блока управления, а выход через пятое

множительное устройство присоединен к первому входу четвертого множительного устройства причем второй зчод второго логического устройства соединен с шестым чходом блока упрагления. четвертый выход которого через второй вход четвертого сумматора и первое логическое устройство присоединен к первому входу етвертого интегратора второй ЕХОД которого соединен с шестом выходом блока управления, а йыхо;, четверт-тс интегратора грисоединен к первому чхолу ( з отображения ин- формгции и 4t,p ;3 второй вход пятого сум- матора присоединен к выходу пятого множительного устройства, первый вход vroKti упраь/, подкаючеч к выходу шес- ; з множитель шго огоой;лва через четвертое логи оское устройство, причем первый вход шестого множительного уст- ройстса соединен с выходом пятого множительного устройства, а второй вход шестого множительного устройства соединен с вы- УСДОМ датчика нагрузки, который, в свою очередь, подключен . второму входу четвертого множительного устройства, второму входу седьмого множительного устройства, четвертому входу блока отображения информации и через первый и второй выходы первого блока постройки соответственно к четвертым входам регулятора и первого диффеленцигтор 1, причем третий вход бло- а отображения ормации соединен с выходом седьмого множительного устройства, третий вход которого подключен к выходу пятого сумматора, а первый вход - к выходу четвертого множительного устройства, второй чх.од блока управления через пятое логическое устройство подключен к выходу второго сумматора, первый пхсд которого через третий дифференциатор связан с выходом объекта управления, а второй подключен к задагчику уставки, четвертый вход блока упраиленил присоединен к выходу объекта управления, который также соединен с первыми входами третьего и четвертого сумматоров, третий вход блока управления соединен с пультом оператора, а пятый вход блока управления через четвертый дифференциатор связан с выходом датчика нагрузки, причем седьмой выход блока управления соединен с пятым входом регулятора, восьмой и девятый множительные устройства, подключенные первыми входами соответственно к выходу второго дифференциатора и усилителя, вторыми входами - к выходам соответственно третьего блекл подстройки и второго выхода седьмого множительного устройства, а выходами - соответственно к шестому входу регулятора через нормально замкнутый кон11162424512

такт переключателя структуры, второй вход го дифференциатора, четвертый вход которо- которого соединен с восьмым выходом го подключен к выходу датчика нагрузки че- блока управления и третьим входом аторо- рез второй блок подстройки.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕКТРОПРИВОД С АВТОМАТИЧЕСКОЙ ПОДСТРОЙКОЙ ЧАСТОТЫ ВХОДНОГО ГАРМОНИЧЕСКОГО СИГНАЛА | 2008 |

|

RU2399079C2 |

| Устройство для стабилизации положения плазменного шнура в токамаке | 1986 |

|

SU1418817A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПРОГРАММНЫХ СИГНАЛОВ УПРАВЛЕНИЯ ПРОСТРАНСТВЕННЫМ ДВИЖЕНИЕМ ДИНАМИЧЕСКИХ ОБЪЕКТОВ | 2013 |

|

RU2522855C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПРОГРАММНЫХ СИГНАЛОВ УПРАВЛЕНИЯ ПРОСТРАНСТВЕННЫМ ДВИЖЕНИЕМ ДИНАМИЧЕСКИХ ОБЪЕКТОВ | 2013 |

|

RU2523186C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПРОГРАММНЫХ СИГНАЛОВ УПРАВЛЕНИЯ ПРОСТРАНСТВЕННЫМ ДВИЖЕНИЕМ ДИНАМИЧЕСКИХ ОБЪЕКТОВ | 2013 |

|

RU2523187C1 |

| Множительно-делительное устройство | 1982 |

|

SU1088016A1 |

| Устройство адаптации | 1979 |

|

SU813358A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ПРОГРАММНЫХ СИГНАЛОВ УПРАВЛЕНИЯ | 2010 |

|

RU2453891C1 |

| Регулятор с переменной структурой | 1978 |

|

SU736046A1 |

| СИСТЕМА УПРАВЛЕНИЯ ВОЗДУШНЫМИ ВИНТАМИ ТУРБОВИНТОВЕНТИЛЯТОРНОГО ДВИГАТЕЛЯ | 1990 |

|

RU2014245C1 |

| Устройство для регулирования температуры пара | 1983 |

|

SU1129459A1 |

| Машина для добывания торфа и т.п. | 1922 |

|

SU22A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

Авторы

Даты

1991-01-30—Публикация

1987-03-25—Подача