(54) УСТРОЙСТВО АДАПТАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивная система регулирования объекта с нестационарной характеристикой,например,дуговой сталеплавильной печи | 1983 |

|

SU1068891A1 |

| Адаптивный регулятор с регулируемой обратной связью | 1985 |

|

SU1287104A1 |

| УСТРОЙСТВО РЕГУЛИРОВАНИЯ ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА | 2011 |

|

RU2465716C1 |

| Регулятор с переменной структурой | 1978 |

|

SU736046A1 |

| Самонастраивающаяся система управления | 1983 |

|

SU1138787A1 |

| САМОНАСТРАИВАЮЩАЯСЯ СИСТЕМА КОМБИНИРОВАННОГО РЕГУЛИРОВАНИЯ | 1989 |

|

RU2022313C1 |

| Система автоматического регулирования | 1987 |

|

SU1483429A1 |

| Система для программного управления правильной машиной | 1986 |

|

SU1327065A1 |

| Адаптивная система регулирования нелинейного объекта,например,шахтной печи | 1985 |

|

SU1297008A1 |

| Устройство для автоматической коррекции массы кокса | 1986 |

|

SU1381165A1 |

1

Изобретение.относится к адаптивны системам и может быть использовано для адаптации настроек регуляторов при регулировании объектов, параметры которых и условия внешней среды меняются в широких пределах.

Известны блоки адаптации содержащие дифференциатор, вход которого соединен со входом первого блока определения модуля, второй блок определения модуля, блок деления, второй вход которого подключен к выходу первого блока определения модуля, сумматор, второй вход которого подключен к выходу блока формирования уставки, ограничитель линейной зоны и инерционное звено 1.

Недостаток этих блоков заключается в низком качестве процесса адаптации из-за наличия значительной колебательности адаптируемого параметра, вызванной тем, что выходной параметр блока адаптации формируется в соответствии с соотнесением двух периодических сигналов модуля ошибки регулирования и модуля ее производной.

Наиболее близким по технической сущности и достигаемому результату к предлагаемому является блок адаптации содержащий последовательно со-, единенные дифференциатор, первый блок определения модуля, первый сумматор, первые реле, интегратор и второй сумматор, первыйвход которого соединен со вторым входом первого сумматора, а второй вход - с выходом первого формирователя уставки, и последовательно соединенные второй

0 блок определения модуля, третий сумматор, второе реле, второй интегратор и четвертый сумматор, первый вход которого соединен со,вторым входом третьего сумматора, а второй вход 5

с выходом второго формирователя уставки {2J.

Недостатками этого блока адаптации являются низкое качество и малая точность адаптации ввиду колебательного

0 характера движения формируемого сигйала к своему установившемуся значению из-за того, что корректирующий коэффициент формируется в блоке деления, на входы которюго поступают пе5риодические сигнс1лы оценки модулей ошибки регулирования и ее производной; низкой точности подстройки, из-за того, что при формировании адаптируемого параметра не учитыва0ются результаты предыдущей адаптации.

Кроме того, отношение сигналов оценки максимальных значений модулей ошибки и ее производной, определенной на участках переходных процессов где модуль ошибки регулирования возрастает, не зависит от коэффициента силения объекта регулирования, что приводит к неверному формированию адаптируемого параметра.

Цель изобретения - повышение точности устройства при изменении параметров объекта и внешних помех.

Поставленная цель достигается тем .что устройство адаптации содержит первый логический блок, последова-. тельно соединенные второй логический блок, формирователь коэффициента коррекции и формирователь адаптируемого коэффициента, выход первого сумматора соединен с первь№1 входом второго логического блока и вторым входом формирователя коэффициента коррекции, а через первый логический блок - со вторым входом первого реле, вькод третьего сумматора соединен со вторым входом второго логического блока,выход второго, i: четвертого сумматоров соединены соответственно с третьим и четвертым Bxo;.i,ajviH формирователя коэффициента коррекции, выход второго логического блока соединен со вторым входом первого логического блока, первые входы второго -и че7;вертого сумматоров соединены соответственно с пятым и шестым входами формирователя коэффициента коррекции; второй логичеС:а-гй блок содержит последовательно соединенные первый и второй функциональные преобразователи,, первый вход второго логического.блока соединен с первым входом первого функционального преобразователя и вторым - входом второго функционального преобразователя, второй вход со вторым входом первого Фун-кцяонального преобразователя и третьим входом второго функцйональиого преобразователя, а выход - с выходом второго функционального преобразователя и третьим входом первого функциональ- horo преобразователя; формирователь коэффициента коррекции содержит третье реле и последовательно соединенные третий логический блок, четвертое реле и блок деления, выход которого соединен с выход-ом формирователя коэффициента коррекции, а выход третьего логического блока через третье реле соединен со вторым входом блока деления, первый, второй третий и четвертый входы формирователя коэффициента коррекции сОединены с соответствующими входами третьего логического блока, а пятый и шестой входы - соответственно со вторыми входами третьего и четвертого реле

формирователь адаптируемого коэффициента содержит последовательно соединенные блок умножения, пятый сумматор , пятое реле, третий интегратор, шестой cvTviMaTOp, шестое реле, г четвертый интегратор, четвертый логический блок и логический инвертор, (ВЫХОД которого соединен со вторым входом шестого реле, ввлход четвертого интегратора соединен с первым

o входом блока умножения и вторым входом шестого сумматора, выход третьего интегратора соединен со входом пятого сумматора, первый вход которого соединен со вторым входом четвертоc ГО логического блока, вход формирователя адаптируемого коэффициента соединен со вторым входом блока умножения , выход четвертого логического блока соединен со вторым входом пятого реле,

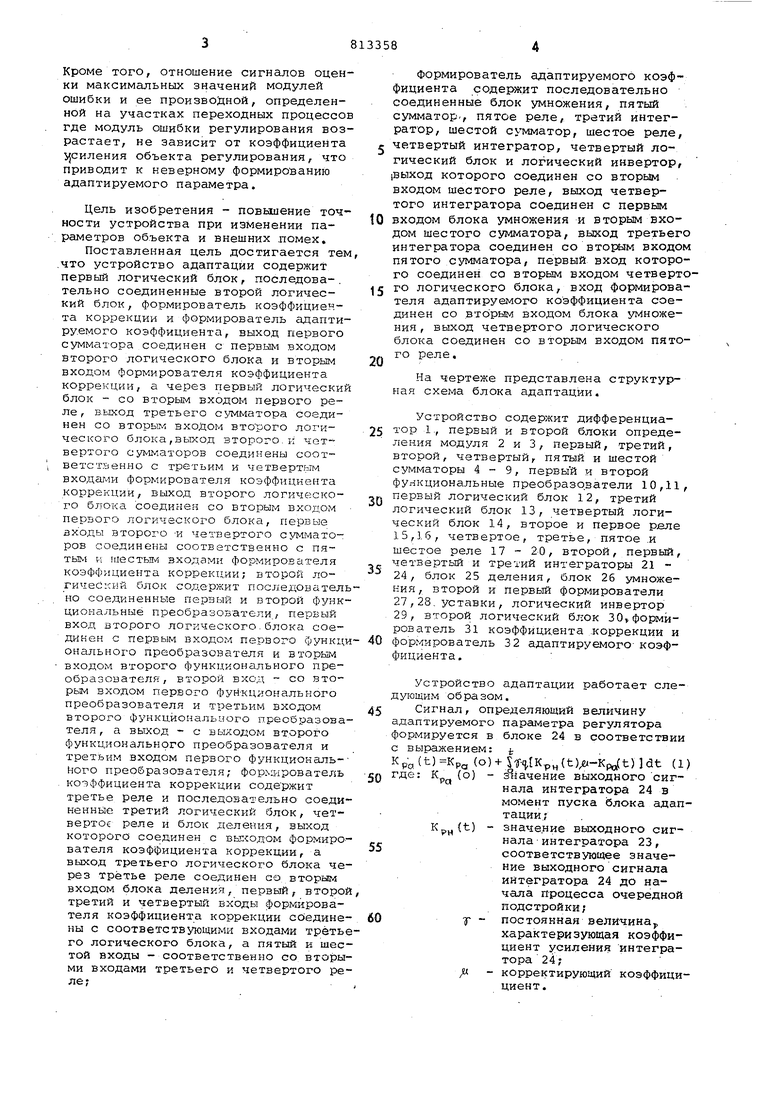

На чертеже представлена структурная схема блока адаптации.

Устройство содержит дифференциатор 1., первый и второй блоки определения модуля 2 и 3, первый, третий, второй, четвертый, пятый и шестой сумматоры 4-9, первый и второй функциональные преобразователи 10,11, Q первый логический блок 12, третий логический блок 13, четвертый логический блок 14, второе и первое реле 15,16, четвертое, третье, пятое .и шестое реле 17 - 20, второй, первый, четвертый и третий интеграторы 21 24, блок 25 деления, блок 26 умножения, второй и Первый формирователи 27,28. уставки, логический инвертор 29, второй логический блок 30,формирователь 31 коэффициента .коррекции и 0 формирователь 32 адаптируемого- коэффициента.

Устройство адаптации работает следующим образом.

5 Сигнал, определяющий величину адаптируемого параметра регулятора формируется в блоке 24 в соответствии с выражением:

)Kp., {o),Kp(t)-KpJ:t)ldt (1) Q где: Кр (о) - значение выходного сигнала интегратора 24 в момент пуска блока адаптации. Kr,u(t) - значение выходного сигг Н

нала - интегратора 23, соответствующее значение выходного сигнала интегратора 24 до начала процесса очередной подстройки;

f - постоянная величина

характеризующая коэффициент усиления интегратора 24

/( - корректирующий коэффицициент. Сигнал,определяющий значение Кр(t) формируется в интеграторе 23 следующим образом: W (t)dt, (1) где: К„„ (о) значение выходного сиг нала интегратора 23 в момент пуска устройства адаптации; постоянная величина, характеризующая коэффи циент усиления интегра ,тора 2 3. логический блок 14 формирует выходной сигнал: Г1 аРи Кр„. 10 ПРИ Кр„ Реле 17 к 18 формирует выходные сигналы:)gO () ПРИ ,и,(| IdL ПРИ ЪФО или1ЁТь) HAvif rf (Л М 1 1Л 2 зафиксированный интегратором 21 сигнал оценки очеред ного максимального значения модуля ощибки регулирования1 - сигнал оценки очередного максимального значения моду ля производной от ошибки ре гулирования,, зафиксированный интегратором 22 на участках переходного процесса, где ошибка регулирования под действием регулятора уменьшается . Реле 15 формирует выходной сигнал: )-e/t) npnie(t)ke(-fc; |e(t)-e,ct) nPMi€(tn(t) где 6(t) - сигнал оценивающий максимальные значения модуля ошибки регулированияe(t). Реле 16 формирует выходной сигнал: .)b(t)J-(o ПРИ в или (t)) вх ). ПРИ &--0 и )(t) .,1 где e,(t) - сигнал, оценивающий максимальные значения модуля производной от ошибки регулирования €., (t) на участках переходных процес-сов, где ошибка регулирования под действием регулятора уменьшается. Логический блок 11 формирует Е1ыходной сигнал: Го ПРИ (l(t),(t) е :|ft ПРИ или |€(t)(.t) l ПРИ t(t) Функциональный преобразователь 10 формирует выходной«сигнал: О ПРИ ie(t)(-fc) А ПРИ BiO MAH|l{t)(t)1 Hiewi e(t) (9) ji ПРИ n|g{t)iie(t} / Система автоматического регулирования включает сумматоры объект регулиров-ания, регулятор , и блок адаптации. При подаче на вход объекта регулирования (на чертеже не показан) возмущения f величина сигнала модуля ошибки регулирования €(t) будет расти. В соответствии с (5) входной сигнал интегратора 21 вх () 16 (t)l - 6-,(t) и на выходе последнего начинает формироваться сигнал оценки максимгшьного значения модуля ошибки регулирования g(t). Одновременно на выходе логического блока 10 в соответствии с (8) появляется сигнал соответствующий логической единице. После достижения сигнашом модуля ошибки регулирования | {t)| своего максимального значения в соответствии с (5) реле 15 переключается, что приводит к ослаблению входного сигнала интегратора 20, на выходе которого при этом фиксируется величина сигнала s(t) . Так как величина сигнала ошибки регулирования начинает уменьшаться, то начинает возрастать выходной сигнал блока 2 jl (t)l . Это приводит к тому, что на выходе логического блока 11 в соответствии с (7) появляется сигнал соответствующий логическому нул1о() и,в соответствии с (б), на. выходе реле 16 появляется,сигнал равный в, (t) |l(t)l - e(t) , На выходе интегратора 22 при этом формируется сигнал оценки максимального значения модуля производной от ошибки регулирования ь.,(t) на участке переходного процесса, где ошибка регулирования под действием регулятора уменьшается. После достижения сигналом jl (t)l своего максимального значения на выходе логического блока 10 в соответствий с (о) появляется сигнал соответствующий логической единице. Одновременно происходит переключение реле 16 в соответствии q (6) и на выходе интегратора 21 фиксируется величина сигнала I., (t) i При условии, то фиксированные значения сигналов €(t) и (t) больше значений опреде ляемых заданной зоной нечувствительности , и S , на выходе логического блока 13 появляется сигнал, при котором реле 17 и 18 в соответствии с (4) переключается и на выходе блока деления 25 появляется сигнал, соответствующий корректирующему коэффициенту. Далее, если выходной сигна интегратора 23 отличается от выходно го сигнала блока деления на величину достаточную для того, чтобы на выходе логического блока 14 произошла смена логического сигнала в соответствии с (3) с логического нуля до логической е иницы, срабатывает реле 19 и,в соответствии с (1),на выходе интегратора 24 формируется сигнал соответствующий, адаптируемому относительно своего начального значения к pn(t) и значения поправочного коэффициента gf ;,д , параметру, Как только начинается- очередной процесс формирования новых значений сиг налов e-i{t) и -i(t), значение стаёт равным и на выходе логического блока 14 появляется сигнал раз.ный логическому нулю, что приводит, в соответствии с (1) и (3), к обрыву посредством реле 19 ВХОДЕЧОГО сигнала интегратора 24, значение выходного сигнала которого при этом фиксируется. На выходе логического инвертора появляется логическая единица и на входе интегратора 23, ввиду того, что контакты реле 20 замыкаются, формируется новое начальное значение сигнала адаптируемого параметра в соответствии с (2). Далее процесс повторяется. Блок адаптации с алгоритмом Функционирования , определяемь м формулами (1)-(8), целесообразно использовать для самонастройки коэффициентов усиления регуляторов в системах автоматического регулирования промышленными объектами, -характеризующимися наличием инерционностей и запаздывания,, причем параметры объекта: К - коэффициент усиления; Т - посто янная времени иЕ - запаздывание в процессе регулирования, могут менят ься в широких пределах. Изменение параметров объекта при водит к тому,-что переходные процес сы становятся колебательными, колебательно неустойчивыми; или апериодическими, настолько медленными, чт перестают удовлетворять требованиям на качество переходного процесса. В первом случае сигнал Кр,,, (t) , формируемый блоком адаптации уменьшается до величины ,-«. К pH(t) , за счет того, что значение корректирую щего коэффициента ,х (кроме случая, когда ), вычисленное в течени полуволны переходного процесса, мен ше единицы. Если изменять коэффициент усиления регулятора в системе втоматического регулирования пропорионально выходной величине блока даптации/ то это приводит к уменьению общего коэффициента усиления онтура регулирования и повышению стойчивости. Во втором случае выходной сигнал лока адаптации увеличивается до веичины ж- Kpц(t), определяемойЗнаением корректирующего коэффициента начальным значением адаптируемого араметра, которое в случае. Если А 1, меньше единицы, если пропорциоально выходной величине блока адаптации изменять коэффициент усиления ругулятора, то коэффициент контура регулирования увеличивается, что риводит к улучшению качества переодных процессов. Формула изобретения 1. Устройство адаптации, содержащее последовательно соединенные дифференциатор, первый блок определения модуля, первый сумматор, первое реле, интегратор и второй сумматор, первый вход которого соединен со вторым входом первого сумматора, а второй входс выходом первого формирователя установки, и последователно соединенные второй блок определения модуля, третий сумматор, второе реле, второй интегратор и четвертый сумматор, первый вход которого соединен со вторым входом третьего сумматора, а второй вход - с выходом второго формирователя уставки, отличающ е ё с я тем, что, с целью повышения точноети устройства при изменении параметров объекта и внешних помех устройство адаптации содержит первый логический блок, последовательно соединенные второй логичес кий блок, формирователь коэффициента коррекции и формирователь адаптируемого коэффициента, выход первого сумматора соединен с первым входом второго логического блока и вторым входом формирователя коэффициента коррекции, а через первый логический блок - со вторым входом Первого реле, выход третьего сумматора соединен со вторым входом второго логического блока, выход второго и четвертого сумматоров соединены соответственно с третьим и четвертым входами формирователя коэффициента коррекции, выход второго логического блока соединен со вторым входом первого логического блока, первые входы второго и четвертого сумматоров соединены соответственно с пятым и шестым входамц формирователя коэффициента коррекции2. Устройство по п. 1, отличающееся тем, что второй логический блок, содержит последовательно соединенные первый и второй функциональный преобразователи, пер вый вход второго логического блока соединен с первым входом первого функционального преобразователя и вторым входом второго функционального преобразователя, второй вход со вторьм входом первого функционального преобразователя и третьим входом второго функционального преобразователя, а выход - с выходом второго функционального преобразователя и третьим входом первого функционального преобразователя.

0 интегратора соединен с первым входом блока умножения и вторым входсж шестого сумматора, выход третьего интегратора соединен со вторым входом пятого сумматора, первый вход которого соединен со вторым входом четвертого логического блока, вход формирователя адаптируемого коэффициента соединен со вторым входом блока умножения, выход четвертого лоп гического блока соединен со вторым входом пятого .реле.

Источники информации, принятые во внимания при экспертизе

Регулирующие модули, приборы и система управления 1, 1974, с. 5-6

(прототип)..

Авторы

Даты

1981-03-15—Публикация

1979-01-04—Подача