Изобретение относится к средствам вычислительной техники и может быть использовано при создании мультипроцессорных систем, л частности упрагшякш(их мультипроцессорных систем повышенной надежности.

Пель изобретения - повышение быстродействия при идентификации и обслуживании экстренных запросов прерывания и расширения.

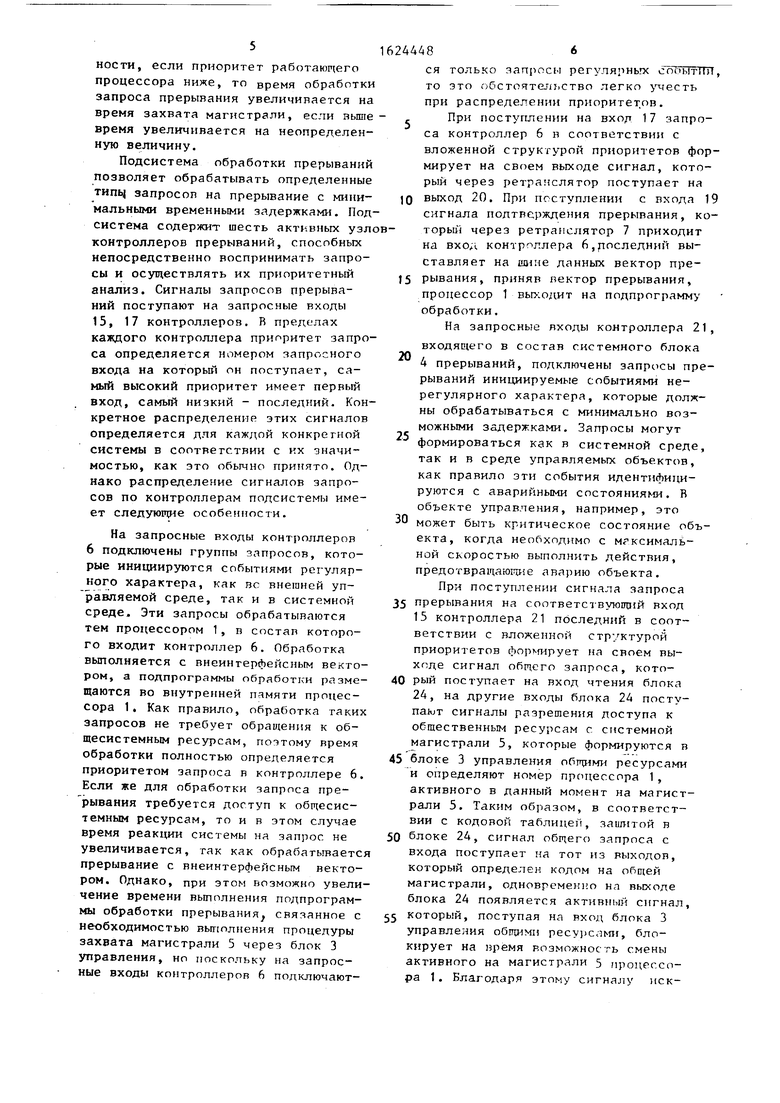

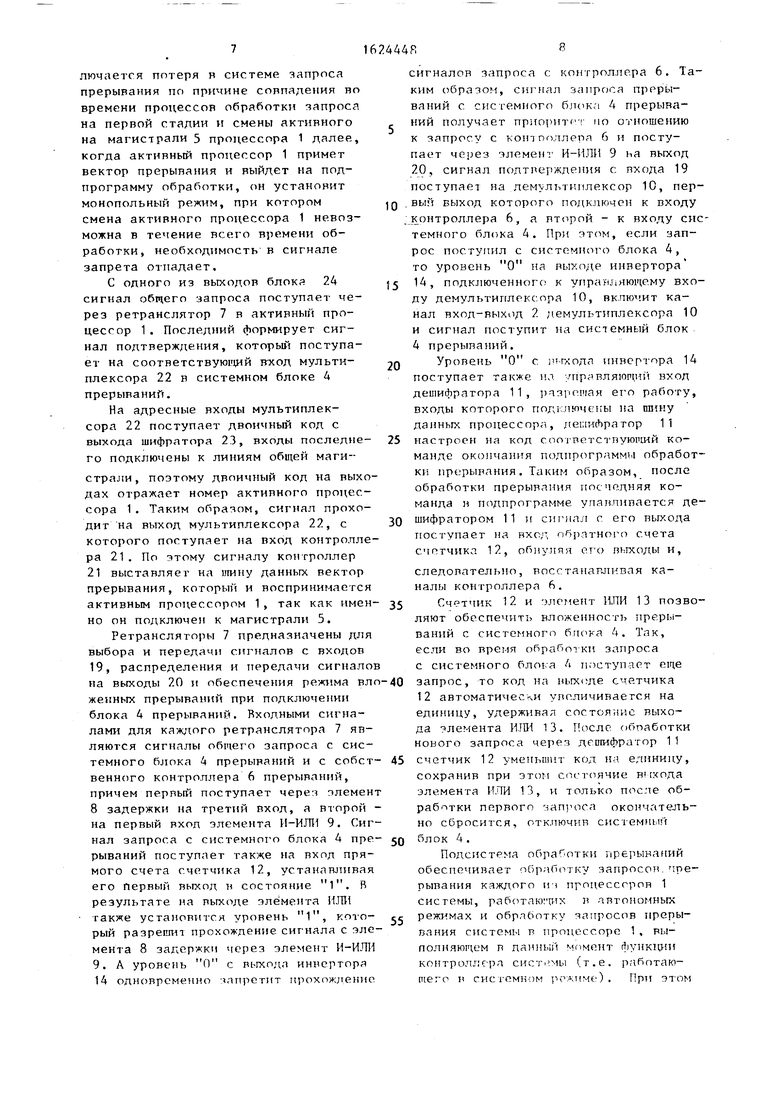

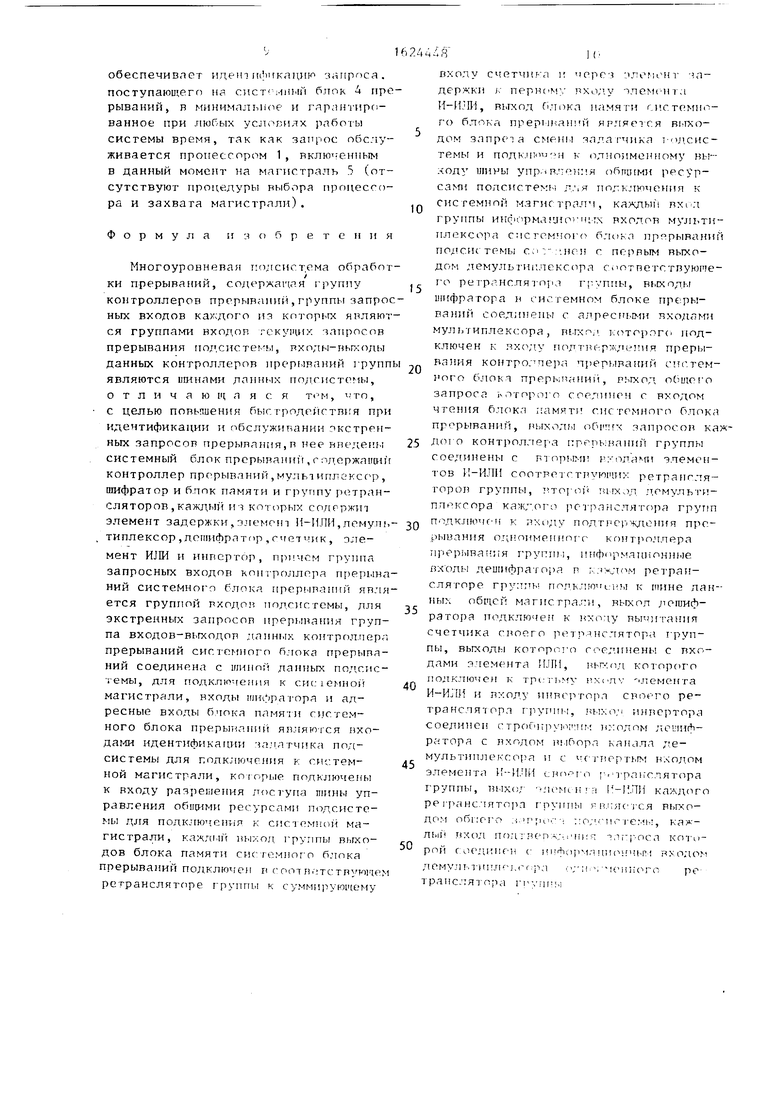

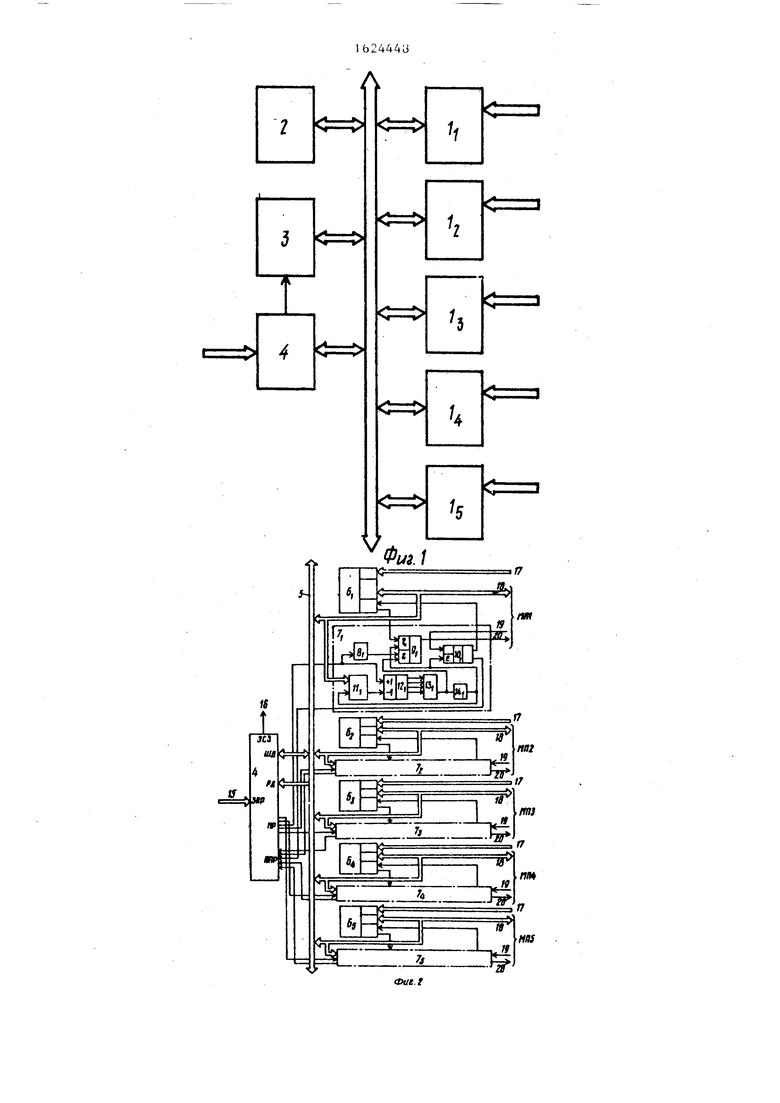

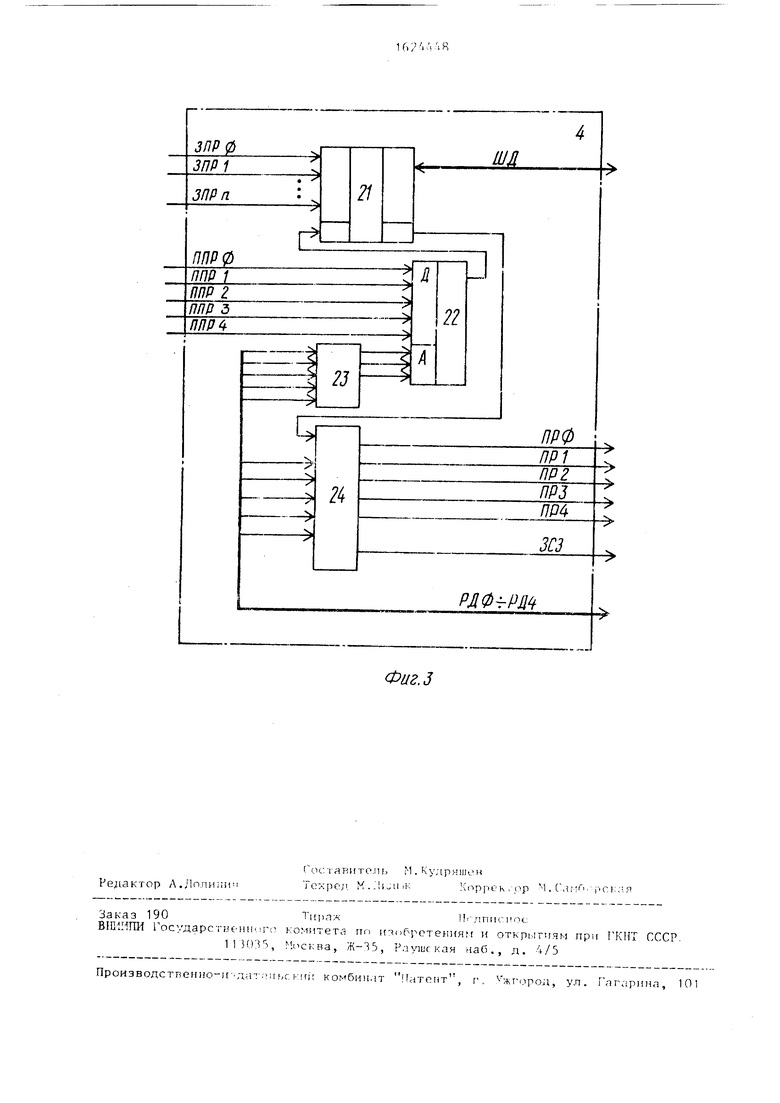

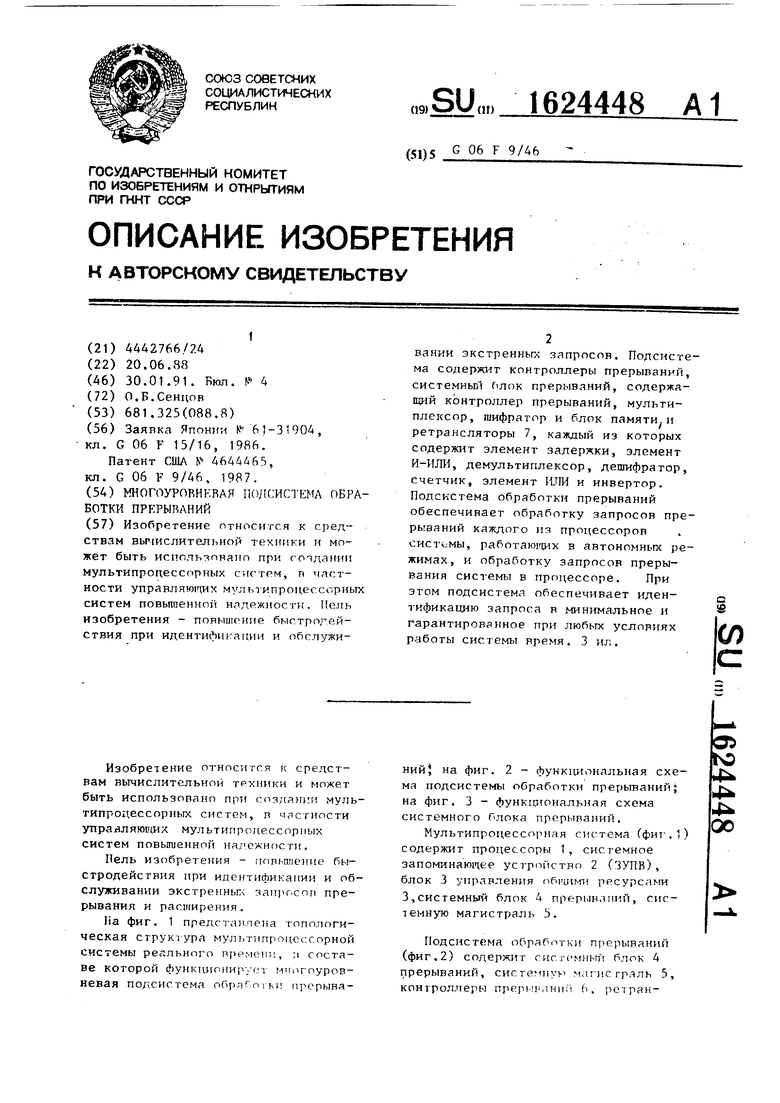

На фиг. 1 представпена гопопоги- ческая структура мультипроцессорной системы реального времени, и составе которой функционир;с 1 многоуровневая подсистема обряго:ы прерываний} на фиг. 2 - функциональная схема подсистемы обработки прерываний; на фиг. 3 - функциональная схема системного блока прерываний.

Мультипроцессорная система (фиг.1) содержит процессоры 1, системное запоминающее устройство 2 С ЗУПВ) , блок 3 управления обгшми ресурсами 3,системный блок 4 прерываний, системную магистраль Ь.

Подсистема обработки прерываний (фиг.2) содержит системный блок 4 прерываний, сие темпvn магистраль 5, контроллеры npept i .iHibi Ь, ре i ран00

316

слягоры /, каждый in которых содержи элемент 8 , тдемемп И-ИЛ11 9, демупьтиплексор 10, дешифратор 11, счетчик 17, -элемент НИИ 13 и инвертор 14.

Подсистема содержит группу входов 15 подсистемы дня ткстренных чапро- сок, пыход 16 чапрета смени задатчи- ка подсистемы группы входов 17 текущих запросов подсиггемм, тины 18 данных подсистемы, пходы 14 подтверждения запроса подсистемы, выходы 20 общего запроса подсистемы.

Системный блок прерывании (Лиг.З) содержит контроллер прерывании 71, мультиплексор 2, шифратор 3, блок 24 памяти.

Годсис тема обработки прерывании функционирует в составе мультипроцессорной сие темы и обеспечивает ее оффективную работу в масштабе реального времени. Мультипроцессорная система (еЪиг.1) состоит из процессоров Koiopbie в зависимости от ее конкретно го использования могут быть, как центральными процессорами, образующими вычислиiельную подсистему, так процессорами ввода-вывода , образующими подсис ему ввода-вывода в любом соотношении сисюмнгго запоминающего устройства 7 произвольной выборки, используемого в режиме коллек швного доемупа, блока 3 управления общими ресурсами, который выполняет Мнкции сиеiемного арбитра и обеспечивает доступ любого HI процессоров 1 к общесистемным ресурсам в соответствии с установленной структурой приоритетов системный блок 4 прерываний и магистраль 5, которая объединяет пге устройства системы по магпс1ральному принципу.

Подсистема обработки прерываний (фиг.2) и apxiiTiKiype мультипроцессоной системы является функционально законченным структурным элементом, обеспечнтющим поддержку режима реального времени, по существу и определяемся vponenb управляющих функции всей системы. Географически блоки подсистемы обработки прерывани рассредоточены но устройствам системы, однако е шн т во их назначения, взаимосвязи и взаимодействие определяют их (Ъ нкцпонадьное и структурное единство и выделение в самостоятельную потсиг г CMV

0

5

0

5

0

5

0

45

ЬО

5

Основными (b v нкпнчми подсистемы рлбогки прерывании являемся лосприя- .ие Kiiipnc in i pi-рын 1Ч1Ы, K roptu инициирую TI я и) ж in п но HI врем ьи при возпикнон нпи опрс ттг i лньг- событии либо во внешней . редз вм-шппьи усг- роигтвами, гчбо в сие ге шоп ср де сис- 1емшгми средствами, о раооткп запросов в соогветгтнин i впогенной структурен приоритетов тан г в iр рыва- ний, причем кгм ши из контроллеров 6 пргрынаний и контроллер 21 лреры- вании имею) свою cipyKivpy приоритетов, формирование Г, гттстемного запроса в процессгр 1, нахо, TFUH JCH в систе пшм режиме, ч чокс,лг НРХ пищи х запросов в ры , находя- |диеся Р ачтономннч рекима, .тгпри- ятие и рагпргдет те гигнапов под- твер ь1ения прерывт.шя г пре есеоров 1, шгработ1а и i ° т да с средствам процессоров 1 интерфейсных нчи вноин- герфенгних BPKiopo} прерываний, а таьже обегпеч ни( вложенное т и пре- рыв, нип.

Ii i б г4ем слула с Fot временное гь и успе тбработки i т-шо-лнбо из сов п н рычанш каким- гиб i upoi tcC i- ром 1 м; iiir lJdu С ОРИОН системы, если для т 1 ,у( |ся дос к ei п;е- сис i -МЧС ) s vp if, з linear г с i лук- iipnopnieioB id o.jci1 в i АДОМ кошргл ере i p i i H(MMIH - и т лепной ступени обработки, м i pyRiypbi приоритетов процессоров 1 eirci Mbi л блоке упрявлепи i61 ими ресурсами 3- на BII рои гтугтчи обрабоПчн и от с ос т о-имя cue i емы на таи с « момент времени, i oiopoe в г IT, r и in оце с сорной cncie e рет,ного i pi менг непредсказуемо в каждый i юдуюнм .ент времени.

При ,-1 с 11 ои привя ке , ч i г-пибо запроса прерчв 1пи ЧГ-IPI одт н из ь он i рол перов npr miii (например , пхоляии н в с глт npi цегсорч) v KcnnpeiiioMV npoiitcrp- систем нсВОЗМС Т1 С I 1) 14 Г ТТЧ Н411

нос чиним,) IT ьое в г °с г к зтппо- сл Л и , ее ти т м-iMf нт ч 1мт е1 чч запроса на MI- i с i ра 1ь р |бптае т пр ГГ тро- цессор,т о процесс р,обрт ттн лкгшп я- прос ,лол-кеь т ыпо ни i г, процедур ia MC iисjрч ur, причем %сгех j ix тт полностью завит, ч р тотно чечия приоритетов огт и % , i также др гц чроци ( in, ггрртечлут1 / в Д1ЧЧЫИ момент н iai не 1 таль я чтетности, если приоритет работающего процессора ниже, то время обработки запроса прерывания увеличивается на время захвата магистрали, если выше время увеличивается на неопределенную величину.

Подсистема обработки прерываний позволяет обрабатывать определенные типц запросол на прерывание с минимальными временными задержками. Подсистема содержит шесть активных узл контроллеров прерываний, способных непосредственно воспринимать запросы и осуществлять их приоритетный анализ. Сигналы запросов прерываний поступают на запросные входы 15, 17 контроллеров. В пределах каждого контроллера приоритет запроса определяется номером запросного входа на который он поступает, самый высокий приоритет имеет первый вход, самый низкий - последний. Конкретное распределение этих сигналов определяется для каждой конкретной системы в соответствии с их значимостью, как это обычно принято. Однако распределение сигналов запросов по контроллерам подсистемы имеет следующие особенности.

На запросные входы контроллеров 6 подключены группы запросов, которые инициируются событиями регулярного характера, как вс внешней управляемой среде, так и в системной среде. Эти запросы обрабатываются тем процессором 1, и состап которого входит контроллер 6. Обработка выполняется с внеингерфенсным вектором, а подпрограммы обработки размещаются во внутренней памяти процессора 1. Как правило, обработка таких запросов не требует обращения к общесистемным ресурсам, поэтому время обработки полностью определяется приоритетом запроса в контроллере 6. Если же для обработки запроса прерывания требуется доступ к общесистемным ресурсам, то и в этом случае время реакции системы на запрос не увеличивается, так как обрабатывается прерывание с внеинтерфейсным вектором. Однако, при этом возможно увеличение времени выполнения подпрограммы обработки прерывания7 связанное с необходимостью выполнения процедуры захвата магистрали 5 через блок 3 управления, но поскольку на запросные входы контроллеров 6 подключают

-

10

15

20

25

624448

ся только запросы регулярных сооытип, то это обстоятельство легко учесть при распределении приоритетов.

При поступлении на вход 17 запроса контроллер 6 в соответствии с вложенной структурой приоритетов формирует на своем выходе сигнал, который через ретранслятор поступает на выход 20. При поступлении с входа 19 сигнала подтверждения прерывания, который через ретранслятор 7 приходит на вход контроллера 6,последний выставляет на шине данных вектор прерывания, приняв вектор прерывания, процессор 1 выходит на подпрограмму обработки.

На запросные входы контроллера 21,

входящего в состав системного блока 4 прерываний, подключены запросы прерываний инициируемые событиями нерегулярного характера, которые должны обрабатываться с минимально возможными задержками. Запросы могут формироваться как я системной среде, так и в среде управляемых объектов, как правило эти события идентифицируются с аварийными состояниями. В объекте управления, например, это может быть критическое состояние объекта, когда необходимо с максимальной скоростью выполнить действия, предотвращающие аварию объекта.

При поступлении сигнала запроса прерывания на соответствующий вход 15 контроллера 21 последний в соответствии с вложенной структурой приоритетов фор -гирует на своем выходе сигнал общего запроса, кото- 40 рый поступает на вход чтения блока 24, на другие входы блока 24 поступают сигналы разрешения доступа к общественным ресурсам с системной магистрали 5, которые формируются в 45 блоке 3 управления общими ресурсами и определяют номер процессора 1, активного в данный момент на магистрали 5. Таким образом, в соответствии с кодовой таблицей, зашитой в блоке 24, сигнал общего запроса с входа поступает на тот из выходов, который определен кодом на общей магистрали, одновременно на выходе блока 24 появляется активный сигнал, который, поступая на вход блока 3 управления общими ресурспми, блокирует на время возможность смены активного на магистрали 5 процессора 1. Благодаря этому сигналу иск30

35

50

55

лючаетгя потеря в системе запроса прерывания по причине совпадения во времени процессов обработки запроса на первой стадии и смены активного на магистрали 5 процессора 1 далее, когда активный процессор 1 примет вектор прерывания и выйдет на подпрограмму обработки, он установит монопольный режим, при котором смена активного процессора 1 невозможна в течение всего времени обработки, необходимость в сигнале запрета отпадает.

С одного из выходов блокя 24 сигнал общего запроса поступает через ретранслятор 7 в активный процессор 1. Последний формирует сигнал подтверждения, который поступает на соответствующий в-ход мультиплексора 22 в системном блоке 4 прерываний.

На адресные входы мультиплексора 22 поступает двоичный код с выхода шифратора 23, входы последнего подключены к линиям общей магистрали, поэтому двоичный код на выходах отражает номер активного процессора 1. Таким образом, сигнал проходит на выход мультиплексора 22, с которого поступает на вход контроллера 21. По этому сигналу контроллер 21 выставляет на шину данных вектор прерывания, который и воспринимается активным процессором 1, так как именно он подключен к магистрали 5.

Ретрансляторы 7 предназначены для выбора и передачи сигналов с входов 19, распределения и передачи сигнало на выходы 20 и обеспечения режима вл женных прерываний при подключении блока 4 прерываний. Входными сигналами для каждого ретранслятора 7 являются сигналы общего запроса с системного блока 4 прерываний и с собственного контроллера 6 прерываний, причем первый поступает через элемен 8 задержки на третий вход, а второй на первый вход элемента Н-ИЛИ 9. Сигнал запроса с системного блока 4 прерываний поступает также на вход прямого счета счетчика 12, устанавливая его Первый выход в состояние 1. В результате на выходе элемента ИЛИ также установится уровень 1, который разрешит прохождение сигнала с элемента 8 задержки через элемент И-ИЛИ 9. А уровень О с выхода инвертора 14 одновременно запретит прохождение

0

5

0

0

5

5

0

5

сигналов запроса с контроллера 6. Таким образом, сигнал запроса прорываний с системного блока 4 прерываний получает приоритет по отношению к запросу с контроллера 6 и поступает через элемент И-ИЛИ 9 на выход 20, сигнал подтверждения с входа 19 поступает на демультиплексор 10, пер- .выи выход которого подключен к входу .контроллера 6, а второй - к входу системного блока 4. При этом, если запрос поступил с системного блока 4, то уровень О на выходе инвертора 14, подключенного к упраш1яюще,му входу демультиплексора 10, включит канал вход-выход 2 демультиплексора 10 и сигнал поступит на системный блок 4 прерываний.

Уровень О с лихо/та инвертора 14 поступает также ил управляющий вход дешифратора 11, разрешая его работу, входы которого под; люмены па шину данных процессора, дешиЛратор 11 настроен на код соответствующий команде окончания подпрограммы обработки прерывания. Таким образом, после обработки прерывания последняя команда в подпрограмме улавливается дешифратором 11 и сигнал с его выхода поступает на вход, обратного счета счетчика 12, обнуляя его выходы и,

следовательно, восстанавливая каналы контроллера 6.

Счетчик 12 и элемент ИЛИ 13 позволяют обеспечить вложенность прерываний с системного бпока 4. Так, если во время обработки запроса с системного блока 4 поступает еще запрос, то код на выходе счетчика 12 автоматически увеличивается на единицу, удерживал состояние выхода элемента ИЛИ 13. После обработки нового запроса через дешифратор 11

счетчик 12 уменьшит код на единицу, сохранив при этом состояние вмхода элемента ИЛИ 13, и только после об- работки первого запроса окончательно сбросится, отключив системный блок 4.

Подсистема обработки прерываний обеспечивает обработку запросов.прерывания каждого ич процессоров 1 системы, работаю:чих в автономных режимах и обработку запросов прерывания системы в процессоре 1, выполняющем в данный момент функции контроллера системы (т.е. работающего и системном режиме). При этом

обеспечивает идет т шкадню запроса. поступающего на сист мный биок 4 прерываний, в минимальное и гарантированное при любых условиях работы системы время, так как запрос обслуживается процессором 1, включенным в данный момент на магистраль 5 (отсутствуют процедуры выбора процес о- ра и захвата магистрали).

Формула изобретения

Многоуровневая т:о;гснот.ема обработки прерываний, содержащая группу контроллеров прерываний,группы запросных входов каждого из которых являются группами входов текущих запросов прерывания подсистемы, входы-ньгходы данных контроллеров прерываний групп являются шинами данных подсистемы, отличающаяся тем, «то, с целью повышения быстродействия при идентификации и обслуживании экстренных запросов прерывания, в нее введены системный блок прерывании,содержащий контроллер прерываний,мулыипленсор, шифратор и бпок памяти и группу ретрансляторов, каждый и которых содержит элемент задержки,племент И-ИЛИ,лемут типлексор,дешифратор, счетчик, элемент ИЛИ и инвертор, причем группа запросных входов контроллера прерываний системного блока прерываний является группой входов подсистемы, для экстренных запросов прерывания группа входов-выходов данных контролперл прерываний системного блока прерываний соединена с шиной данных подоис- ;емы, для подключения к системной магистрали, входы шифратора и адресные входы бчока памяти системного блока прерываний являю1ся входами идентификации задагчнка подсистемы для подключения к системной магистрали, коюрые подключены к входу разрешения доступа шины управления общими ресурсами подсистемы для подключения к системной магистрали, каждый выход группы выходов блока памяти сие-томного блока прерываний подключен в соответствующем ретрансляторе группы к суммирующему

5

0

0

входу счетчш-а и через чломент задержки i первом1; входу элемента И-ИЛИ, выход блока памяти системного блока прерываний является выходом запрета смены задагчика тодсис- темы и подым 1 н ь одноименному выходу шины упр. общими ресурсами подсистемы для подключения к системной магистрали, каждый BXIл группы инсн рмлнло чигх входов мультиплексора системного блоьа прерываний подсистемы с, .лен с первым выходом демулътиплексора соответствующего ретр нспятора группы, вькоды шифратора в системном блоке прерываний соединены с адресными входами мультиплексора, вых, ьоторпго подключен к входу подтверждения преры- взния контрогпера прерываний системного блока прерывании, выход общего запроса o-ropoio соединен с входом чтения блока памяти системного блока прерывании, выходы обгт х запросов каж- 5 AOI о контроллера прерь.ваний группы соединены с вторыми г:- одами эпемен- тов П-ИЛИ соотве i e TBVJOIHHX ретрансляторов группы, PTOJ он Birxo.n демульти- ппексора каждого ретранслятора групп д подключен к входу подтверждения прерывания одноименного контроллера прерывания группы, информационные входы дешифратора л г- i-стом ретрансляторе группы погкдю ч I M к шине данных общей магистрали, выход дешифратора подключен к входу вычитания счетчика своего ретранслятора группы, выходы которого соединены с входами элемента ИЛИ, выход которого подключен к rpi члемен га И-ИЛН и входу инвертора свое-то ре- транспяторл rjiynni-i, лихом инвертора соединен CTpoOiiiiyiiir nt )с:одом дсишгЬ- ратора с входом выбора каната де- мультиплексора и с 1ч гпоргым входом элемента Н--ИЛН (.волг о , тракотятора группы, выхо/ .-leMiH 1 Г-НЛН каждого ре i рансчятора группы гппясчс.я дом обиет о -i трО 1 :TV ncjer t-:, каждый вход под : веп л-, . in-1 Т роса которой соединен с информационны) дему.чг.т ипл ч.ег p,i ;; ченпс т ре т ранслят ора n-vrii,,

5

0

5

0

Фш.

t

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультипроцессорная вычислительная система | 1988 |

|

SU1522227A1 |

| РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1991 |

|

RU2010315C1 |

| СИСТЕМА КОММУТАЦИИ ПРОЦЕССОРОВ | 1991 |

|

RU2006931C1 |

| Устройство приоритетного прерывания | 1990 |

|

SU1793440A1 |

| Контроллер с переменным приоритетом | 1980 |

|

SU907550A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| МУЛЬТИПРОЦЕССОРНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1978 |

|

SU768323A1 |

| Устройство для прерывания программ | 1985 |

|

SU1341636A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Процессор для мультипроцессорной системы | 1988 |

|

SU1541626A1 |

Изобретение относится к средствам вышслительной техники и может быть использовано при создании мультипроцессорных систем, R частности управляющих мультипроцессорных систем повышенной надежности. Цель изобретения - повышение быстродействия при идентификации и обслуживании экстренных запросов. Подсистема содержит контроллеры прерываний, системный блок прерываний, содержащий контроллер прерываний, мультиплексор, шифратор и блок памяти.и ретрансляторы 7, каждый из которых содержит элемент задержки, элемент И-ИЛИ, демультиплексор, дешифратор, счетчик, элемент ИЛИ и инвертор. Подсистема обработки прерываний обеспечивает обработку запросов прерываний каждого из процессоров системы, работающих в автономных режимах, и обработку запросов прерывания системы в процессоре. При этом подсистема обеспечивает идентификацию запроса в минимальное и гарантированное при любых условиях работы системы время. 3 ил. с S / с

и

Httl

я тз

17

im

/7

HOS

Фиг.З

| Устройство для сортировки каменного угля | 1921 |

|

SU61A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США У 4644465, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-01-30—Публикация

1988-06-20—Подача