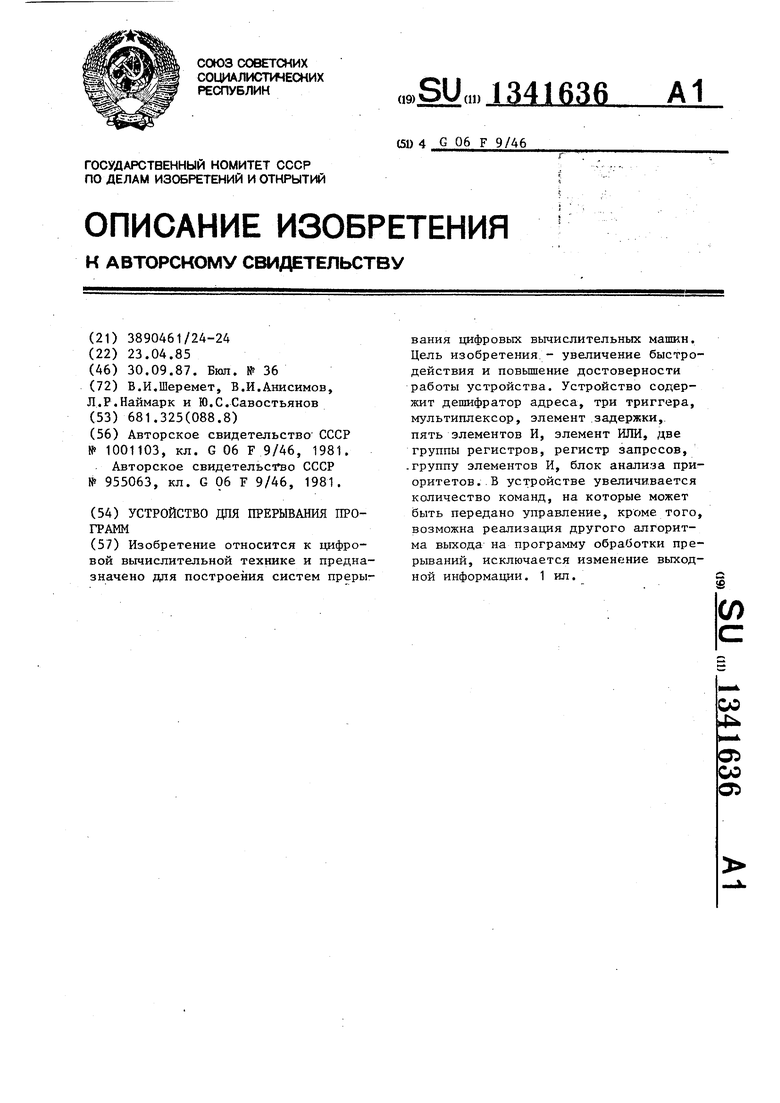

Изобретение относится к цифровой вычислительной технике и может быть использовано в системах прерывания цифровых вычислительных машин, а также может быть применено как средство для отладки программ.

Цель изобретения - увеличение быстродействия и повышение достоверности работы устройства.

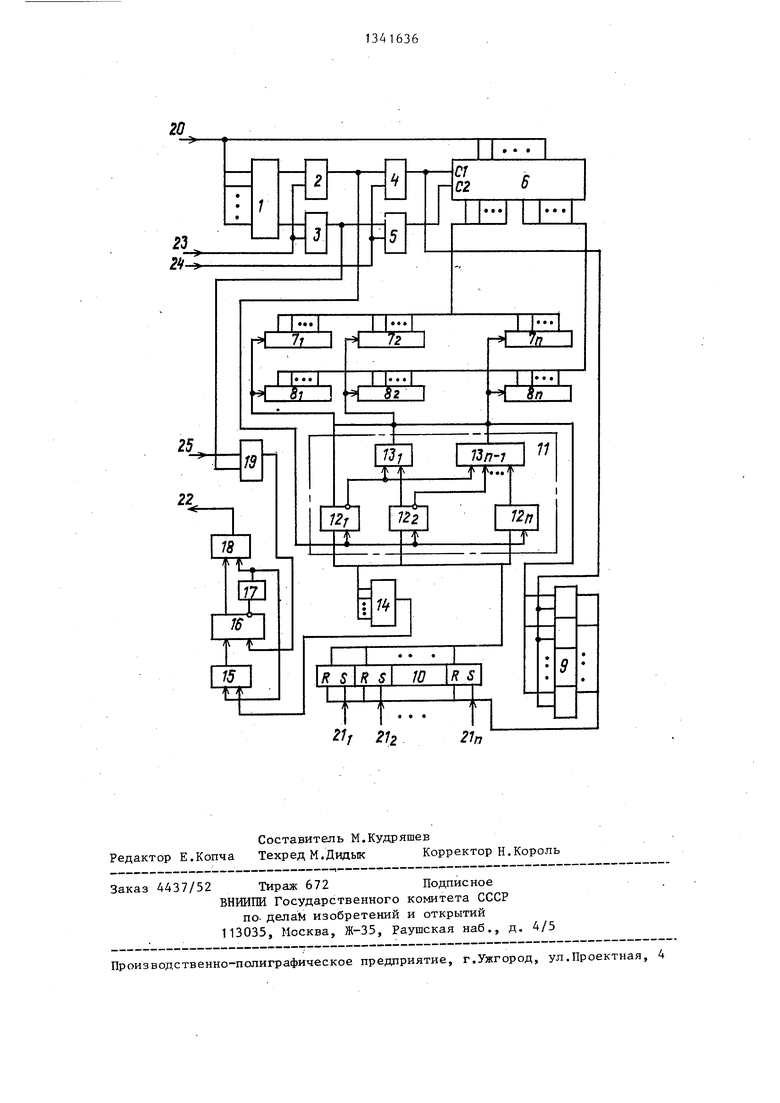

На чертеже приведена функциональная схема устройства.

Устройство содержит дешифратор 1 адреса, триггеры 2 И 3, элементы И 4 и 5, мультиплексор 6, первую группу регистров 7, вторую группу регистров 8, группу элементов И 9, регистр 10 запросов, блок 11 анализа приоритетов (в состав которого входит группа триггеров 12, груйпа элементов И 13), элемент ИЛИ 14, элемент И 15, триггер 16, элемент.17 задержки, элементы И 18 и 19, информационные входы-выходы 20 устройства, запросные

Все сигналы, поступающие на входы предлагаемого устройства (кроме сигналов прерываний), поступают и на совходы 21 устройства, запросный выход 25 ответствующие входы-выходы других 22 устройства, вход сигнала 23 Об- устройств системы, подключенные к обмен устройства, вход сигнала 24 Чте- щей магистрали. Следовательно, эти ние и вход сигнала 25 Ответ устрой- сигналы поступают на соответствующие

ства.

Устройство работает следующим образом.

В начальном состоянии триггеры 2, 3 и 16, группа триггеров 12, регистр 10 находятся в нулевом состоянии (цепи установки в нулевое состояние не показаны), на выходах регистров 7 и 8 и на выходах мультиплексора 6 поддерживаются сигналы, соответствующие О.

В каждый регистр предварительно занесены код начального состояния счетчика команд процессора при выполнении программы обработки соответствующего прерывания, код начального состояния регистра состояний процессора при выполнении инициируемой соответствующим прерыванием программы.

В момент прихода положительного импульса сигнала запроса на прерывание по входам 21 на соответствующем выходе регистра 10 запросов образуется единичный сигнал, который через элемент ИЛИ 14 и через элемент И 15, на второй вход которого подан разрешающий сигнал с выхода элемента 17 задержки, поступает на вход синхронизации триггера 16 и положительным фронтом устанавливает его в единичное состояние. При этом благодаря

введению элемента 17 задержки на выходе элемента И 18 образуется поло- жительньш импульс, который поступает

на выход 22 устройства. Процессор, приняв сигнал запроса на прерывание, переходит в режим обработки прерывания. Он помещает в стек.содержимое счетчика команд и регистра состояНИИ процессора, после чего загружает новое содержимое счетчика команд и регистра состояний процессора, причем загрузка происходит путем вьшол- нения операции чтения ячеек внешней

памяти с адресами соответственно А и Ао+2, при этом адрес А определяется процессором микропрограммно и не требует предварительного считывания этого адреса из источника прерывания, как прэисходит в случае реализации векторного прерывания.

Все сигналы, поступающие на входы предлагаемого устройства (кроме сигналов прерываний), поступают и на соответствующие входы-выходы других устройств системы, подключенные к общей магистрали. Следовательно, эти сигналы поступают на соответствующие

входы-выходы внешней памяти. В ячей- ках внешней памяти с адресами АО и Ао+2 занесена нулевая информация.

При выполнении операции чтения по адресу АО процессор передает через магистраль на информационные входы- выходы 20 устройства код., соответст- тзуюш й адресу А и затем вырабатывает сигнал 23 Обмен. При этом на первом выходе дешифратора 1 адреса появляется единичный сигнал, кото- рый поступает на информационный вход триггера 2 и по переднему фронту сигнала 23 Обмен триггер 2 устанавливается в единичное состояние.

Сигнал с прямотх) выхода триггера 2 поступает на синхронизирующей вход блока 11 анализа приоритетов и передним фронтом производит запись принятых сигналов прерываний с выхода регистра 10 запросов в соответствующие триггеры 12. При этом только на одном из выходов блока 11 анализа приоритетов присутствует сиг.нал, соответствующий наиболее приоритетному запросу на прерывание.

Сигнал, соответствующий наиболее приоритетному запросу, с соответствующего выхода блока 11 анализа приоритетов поступает на вход соответствующих регистров 7 и 8. При этом на

выходах соответствующего регистра .появляется код начального состояция счетчика команд процессора, а на выходах соответствующего регистра 8 - код начального состояния регистра состояния процессора при обработке данного прерывания. Коды начального состояния счетчика команд и начального состояния регистра состояний процессора поступают соответственно 10 на первую и вторую группы входов мультиплексора 6.

Процессор, сняв с информационных входов-выходов 20 устройства код адреса Ар, выставляет сигнал 24 Чте- кие, который через элемент И 4 поступает на первьш стробирующий вход мультиплексора 6 и на входы элементов И 9. При этом на вькоде соответствующего элемента И 9 появляется 20 сигнал, который устанавливает в нулевое состояние соответствующий триггер регистра 10 запросов, а сигнал на первом стробирующем входе мультиплексора 6 обеспечивает передачу на его выход информации, поступающей на первую группу его входов. Таким образом, на информационных входах-выходах 20 устройства появляется код начального состояния счетчика команд процессора, который задан при обработке этого пре рывания.

Считьюание из внешней памяти происходит одновременно со считыванием из устройства для прерывания программ, 35 но данные выставляет устройство, так как .по адресу А внешней памяти занесена нулевая информация. Внешняя память, приняв сигнал 24 Чтение, вы25

30

этого мультиплексора с выходов регистров 8.

Таким образом, на информационные входы-выходы 20 устройства передается код начального состояния регистра состояний процессора, соответствующий тому же запросу на прерывание.

Внешняя память вырабатывает сигнал 25 Ответ, который поступает в процессор, вызывает прекращение операции чтения и одновременно поступает в устройство, где через элемент И 19 (на второй вход которого подан единичный сигнал с выхода триггера 3) устанавливается в нулевое состояние триггер 16, и через время, определяемое элементом 17 задержки, на первом входе элемента И 15 устанавливается разрешающий потенциал. Таким образом, на запросном выходе 22 устройства, может появиться (при наличии необслуженного запроса на прерывание в регистре 10 запросов) новый сигнал запроса на прерывание процессора, который запоминается процессором, но обслуживается только после окончания программы обработки уже

принятого прерьшания. 1

В случае, если процессор, к которому подключено устройство, по сигналу прерывания загруясает код команды, в соответствующие регистры 7 и 8 могут быть занесены коды соответст- вую1цих команд.

Формула изобретения

Устройство для прерывания программ, содержащее регистр запросов.

рабатывает сигнал 25 Ответ, и про- элементов И, блок анализа при- цессор, приняв сигнал 25 Ответ, за- оритетов, первьй и второй элемен- вершает процедуру чтения, т.е.

снимает сигналы 24 Чтение и 23 Обмен.

Аналогично процессор вьшолняет операцию чтения по адресу Ао+2, При этом сигнал появляется на втором выходе дешифратора 1 адреса и поступает на информационный вход второго триггера 3. При поступлении сигнала 23 обмен триггер 2 устанавливается

45

50

ты и, причем группа информационных входов регистра запросов является группой входов запросов устройства, отличающе еся тем, что, с целью увеличения быстродействия и повышения достоверности работы устройства, в него введены дешифратор адреса, три триггера, третий, четвертый и пятый элементы И, мультиплексор, элемент задержки, элемент ИЛИ и две группы регистров, причем входы дешифратора адреса соединены с соответствующими входами-выходами устройства, выходы мультиплексора соединены с соответствующими информационными входами-выходами устройства, первьш и второй выходы дешифра О

а триггер 3 - в единичное состояние. При появлении сигнала 24 Чтение с вькода элемента И 5 пере- дается сигнал на второй стробирующий вход мультиплексора 6 и на выходах последнего появляется информация, поступившая на вторую группу входов

10 0

5

5

0

этого мультиплексора с выходов регистров 8.

Таким образом, на информационные входы-выходы 20 устройства передается код начального состояния регистра состояний процессора, соответствующий тому же запросу на прерывание.

Внешняя память вырабатывает сигнал 25 Ответ, который поступает в процессор, вызывает прекращение операции чтения и одновременно поступает в устройство, где через элемент И 19 (на второй вход которого подан единичный сигнал с выхода триггера 3) устанавливается в нулевое состояние триггер 16, и через время, определяемое элементом 17 задержки, на первом входе элемента И 15 устанавливается разрешающий потенциал. Таким образом, на запросном выходе 22 устройства, может появиться (при наличии необслуженного запроса на прерывание в регистре 10 запросов) новый сигнал запроса на прерывание процессора, который запоминается процессором, но обслуживается только после окончания программы обработки уже

принятого прерьшания. 1

В случае, если процессор, к которому подключено устройство, по сигналу прерывания загруясает код команды, в соответствующие регистры 7 и 8 могут быть занесены коды соответст- вую1цих команд.

Формула изобретения

Устройство для прерывания программ, содержащее регистр запросов.

0 элементов И, блок анализа при- оритетов, первьй и второй элемен-

элементов И, блок анализа при- оритетов, первьй и второй элемен-

ты и, причем группа информационных входов регистра запросов является группой входов запросов устройства, отличающе еся тем, что, с целью увеличения быстродействия и повышения достоверности работы устройства, в него введены дешифратор адреса, три триггера, третий, четвертый и пятый элементы И, мультиплексор, элемент задержки, элемент ИЛИ и две группы регистров, причем входы дешифратора адреса соединены с соответствующими входами-выходами устройства, выходы мультиплексора соединены с соответствующими информационными входами-выходами устройства, первьш и второй выходы дешифратора соединены с информационными входами первого и второго триггеров соответственно, синхрокизируняцие вхо ды которых объединены и соединены с входом сигнала Обмен устройства, выход первого триггера соединен с первым входом первого элемента И и с синхрокизирукицим входом блока анализа приоритетов, выход второго.триггера соединен с первым входом второго элемента Икс первьш входом третьего элемента И, второй вход которого соединен с входом сигнала Ответ устройства, выход третьего элемента И соединен с входом сброса третьего триггера, вторые входы первого и второго элементов И объединены и соединены с входом сигнала Чтение устройства, выход первого элемента И соединен с первым стробирую- щим входом мультиплексора и с первыми входами элементов И группы, вторые входы которых соединены с соответствующими выходами блока анализа . приоритетов и с входами синхронизации соответствующих регистров первой

5

0

5

и второй группы, выходы элементов И группы соединены с входами сброса соответствующих разрадов регистра запросов, выход второго элемента И соединен с вторым стробирунщим входом мультиплексора, первая группа информационных входов которого соединена с выходами регистров первой группы, вторая группа информационных входов мультиплексора соединена с выходами регистров второй группы, выходы регистра запросов соединены с группой входов блока анализа приоритетов и с входами элемента ИЛИ, выход которого соединен с первым входом четвертого элемента И, выход которого соединен с синхронизирующим входом третьего триггера, прямой выход которого соединен с первым входом пятого элемента И,инверсный выход третьего триггера соединен с входом элемента задержки, выход которого соединен с вторым входом четвёртого элемента И и с вторым входом пятого элемента И, выход которого соединен с запросным выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Устройство прерывания | 1982 |

|

SU1084795A1 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1988 |

|

SU1536393A1 |

| Устройство для сопряжения процессора с внешним устройством | 1988 |

|

SU1550524A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Устройство для прерывания программ | 1985 |

|

SU1277109A1 |

Изобретение относится к цифровой вычислительной технике и предназначено для построения систем прерывания цифровых вычислительных машин. Цель изобретения. - увеличение быстродействия и повышение достоверности работы устройства. Устройство содержит дешифратор адреса, три триггера, мультиплексор, элемент .задержки,, пять элементов И, элемент ИЛИ, две группы регистров, регистр запросов, .группу элементов И, блок анализа приоритетов.. В устройстве увеличивается количество команд, на которые может быть передано управление, кроме того, возможна реализация другого алгоритма выхода на программу обработки прерываний, исключается изменение выходной информации. 1 ил. со 4 Oi ОЭ о:

| Устройство для прерывания программ | 1981 |

|

SU1001103A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство приоритетного прерывания | 1980 |

|

SU955063A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-30—Публикация

1985-04-23—Подача