Изобретение относится к вычислительной технике и может быть использовано при построении контролепригодных последовательных устройств.

Цель изобретения - расширение области применения D-триггера за счет возмож- ности его использования в контролепригодных последовательностиых устройствах.

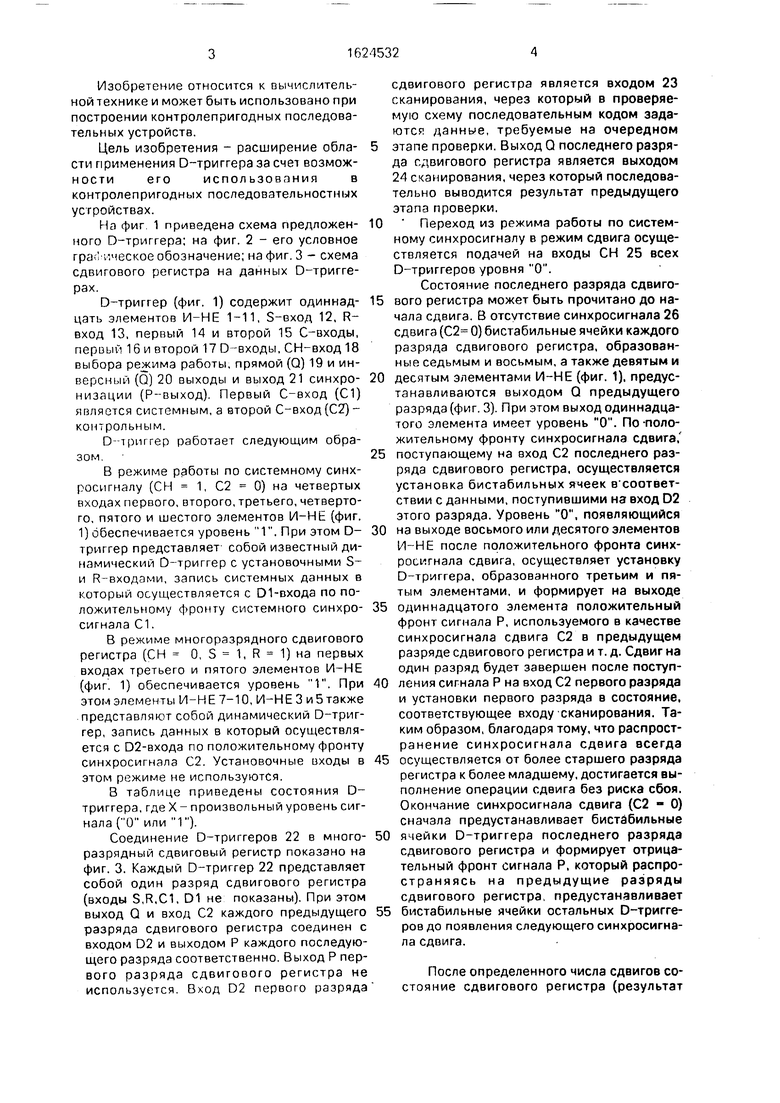

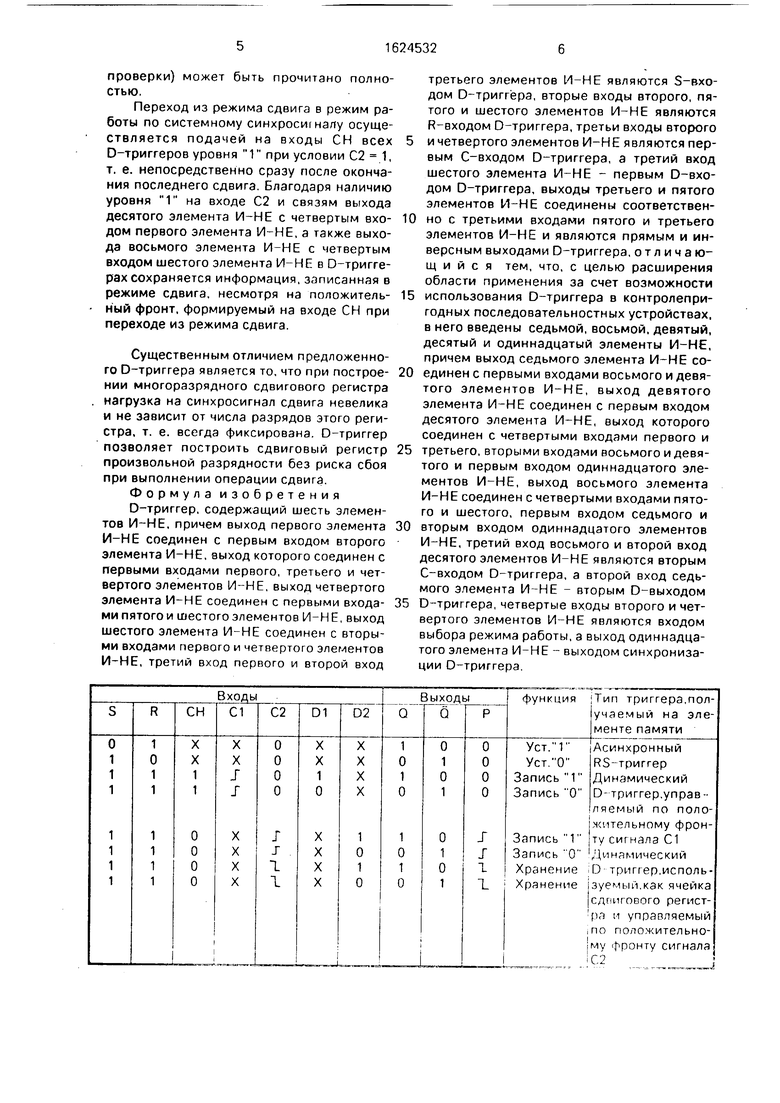

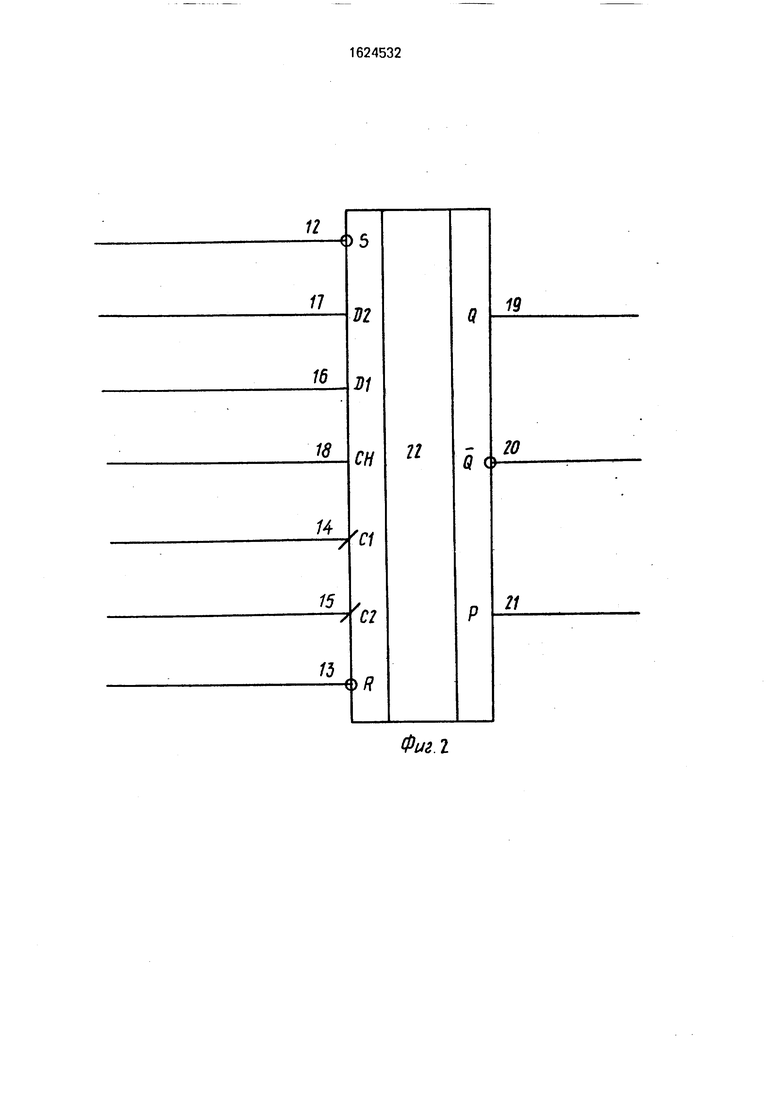

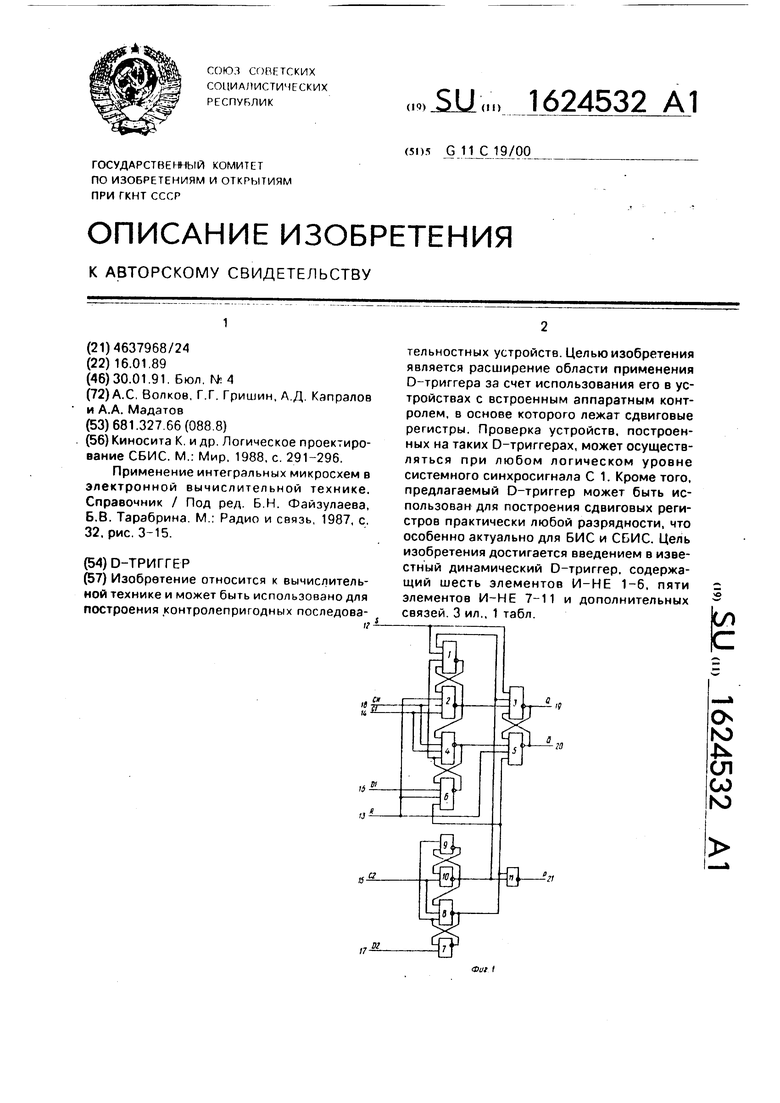

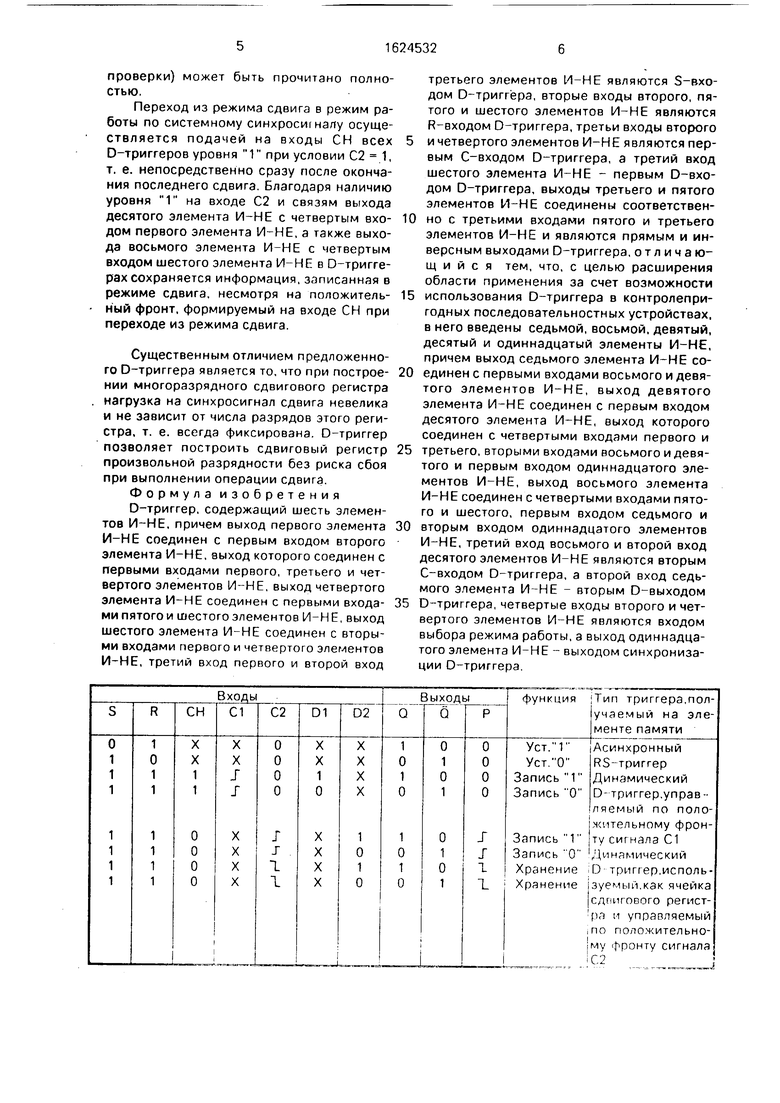

На фиг 1 приведена схема предложенного D-триггера; на фиг. 2 - его условное графическое обозначение; на фиг. 3 - схема сдвигового регистра на данных D-тригге- рах.

D-триггер (фиг. 1) содержит одиннадцать элементов И-НЕ 1-11, S-вход 12, R- вход 13, первый 14 и второй 15 С-входы, первый 16 и второй 17 D-входы, СН-вход 18 выбора режима работы, прямой (Q) 19 и инверсный (Q) 20 выходы и выход 21 синхронизации (Р-выход). Первый С-вход (С1) является системным, а второй С-вход (С2) - контрольным.

D-триггер работает следующим образом.

В режиме работы по системному синхросигналу (СН 1, С2 0) на четвертых входах первого, второго,третьего, четвертого, пятого и шестого элементов И-НЕ (фиг. 1) обеспечивается уровень 1. При этом D- триггер представляет собой известный динамический D-триггер с установочными S- и R-входами, запись системных данных в который осуществляется с О1-входа по положительному фронту системного синхросигнала С1.

В режиме многоразрядного сдвигового регистра (СН О, S 1, R 1) на первых входах третьего и пятого элементов И-НЕ (фиг. 1) обеспечивается уровень 1. При этом элементы И-НЕ 7-10, И-НЕЗ и5 также представляют собой динамический D-триггер, запись данных в который осуществляется с 02-входа по положительному фронту синхросигнала С2. Установочные входы в этом режиме не используются.

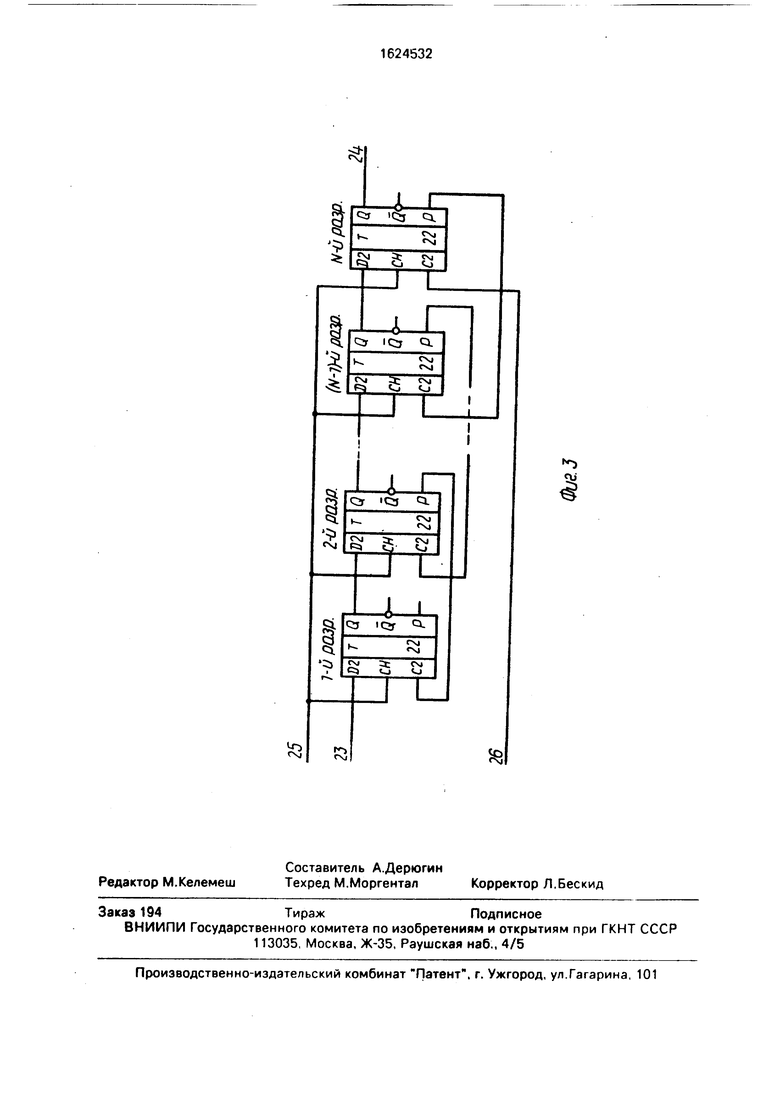

В таблице приведены состояния D- триггера, где X - произвольный уровень сигнала (О или 1).

Соединение D-триггеров 22 в многоразрядный сдвиговый регистр показано на фиг. 3. Каждый D-триггер 22 представляет собой один разряд сдвигового регистра (входы S,R,C1, D1 не показаны). При этом выход Q и вход С2 каждого предыдущего разряда сдвигового регистра соединен с входом D2 и выходом Р каждого последующего разряда соответственно. Выход Р первого разряда сдвигового регистра не используется. Вход D2 первого разряда

сдвигового регистра является входом 23 сканирования, через который в проверяемую схему последовательным кодом задаются данные, требуемые на очередном

этапе проверки. Выход Q последнего разряда сдвигового регистра является выходом 24 сканирования, через который последовательно выводится результат предыдущего этапа проверки,

Переход из режима работы по системному синхросигналу в режим сдвига осуществляется подачей на входы СН 25 всех D-триггеров уровня О.

Состояние последнего разряда сдвигового регистра может быть прочитано до начала сдвига. В отсутствие синхросигнала 26 сдвига (С2 0) бистабильные ячейки каждого разряда сдвигового регистра, образованные седьмым и восьмым, а также девятым и

десятым элементами И-НЕ (фиг. 1), предустанавливаются выходом Q предыдущего разряда (фиг. 3). При этом выход одиннадцатого элемента имеет уровень О. По-положительному фронту синхросигнала сдвига,

поступающему на вход С2 последнего разряда сдвигового регистра, осуществляется установка бистабильных ячеек в соответ- ствии с данными, поступившими на вход D2 этого разряда. Уровень О, появляющийся

на выходе восьмого или десятого элементов И-НЕ после положительного фронта синхросигнала сдвига, осуществляет установку D-триггера, образованного третьим и пятым элементами, и формирует на выходе

одиннадцатого элемента положительный фронт сигнала Р, используемого в качестве синхросигнала сдвига С2 в предыдущем разряде сдвигового регистра и т. д. Сдвиг на один разряд будет завершен после поступления сигнала Р на вход С2 первого разряда и установки первого разряда в состояние, соответствующее входу сканирования. Таким образом, благодаря тому, что распространение синхросигнала сдвига всегда

осуществляется от более старшего разряда регистра к более младшему, достигается выполнение операции сдвига без риска сбоя. Окончание синхросигнала сдвига (С2 - 0) сначала предустанавливает бистабильные

0 ячейки D-триггера последнего разряда сдвигового регистра и формирует отрицательный фронт сигнала Р, который распространяясь на предыдущие разряды сдвигового регистра, предустанавливает

5 бистабильные ячейки остальных D-триггеров до появления следующего синхросигнала сдвига.

После определенного числа сдвигов состояние сдвигового регистра (результат

проверки) может быть прочитано полностью.

Переход из режима сдвига в режим работы по системному синхросигналу осуществляется подачей на входы СН всех D-триггеров уровня 1 при условии С2 1, т. е. непосредственно сразу после окончания последнего сдвига. Благодаря наличию уровня 1 на входе С2 и связям выхода десятого элемента И-НЕ с четвертым входом первого элемента И-НЕ, а также выхода восьмого элемента И-НЕ с четвертым входом шестого элемента И-НЕ в D-тригге- рах сохраняется информация, записанная в режиме сдвига, несмотря на положительный фронт, формируемый на входе СН при переходе из режима сдвига.

Существенным отличием предложенного D-триггера является то, что при построении многоразрядного сдвигового регистра нагрузка на синхросигнал сдвига невелика и не зависит от числа разрядов этого регистра, т. е. всегда фиксирована. D-триггер позволяет построить сдвиговый регистр произвольной разрядности без риска сбоя при выполнении операции сдвига. Формула изобретения D-триггер, содержащий шесть элементов И-НЕ, причем выход первого элемента И-НЕ соединен с первым входом второго элемента И-НЕ, выход которого соединен с первыми входами первого, третьего и четвертого элементов И-НЕ, выход четвертого элемента И-НЕ соединен с первыми входами пятого и шестого элементов И-НЕ, выход шестого элемента И-НЕ соединен с вторыми входами первого и четвертого элементов И-НЕ, третий вход первого и второй вход

третьего элементов И-НЕ являются S-RXO- дом D-триггёра, вторые входы второго, пятого и шестого элементов И-НЕ являются R-входом D-триггера, третьи входы второго 5 и четвертого элементов И-НЕ являются первым С-входом D-триггера, а третий вход шестого элемента И-НЕ - первым D-вхо- дом D-триггера, выходы третьего и пятого элементов И-НЕ соединены соответствен0 но с третьими входами пятого и третьего элементов И-НЕ и являются прямым и инверсным выходами D-триггера, отличающийся тем, что, с целью расширения области применения за счет возможности

5 использования D-триггера в контролепри- годных последовательностных устройствах, в него введены седьмой, восьмой, девятый, десятый и одиннадцатый элементы И-НЕ, причем выход седьмого элемента И-НЕ со0 единен с первыми входами восьмого и девятого элементов И-НЕ, выход девятого элемента И-НЕ соединен с первым входом десятого элемента И-НЕ, выход которого соединен с четвертыми входами первого и

5 третьего, вторыми входами восьмого и девятого и первым входом одиннадцатого элементов И-НЕ, выход восьмого элемента И-НЕ соединен с четвертыми входами пятого и шестого, первым входом седьмого и

0 вторым входом одиннадцатого элементов И-НЕ, третий вход восьмого и второй вход десятого элементов И-НЕ являются вторым С-входом D-триггера, а второй вход седьмого элемента И-НЕ - вторым D-выходом

5 D-триггера, четвертые входы второго и четвертого элементов И-НЕ являются входом выбора режима работы, а выход одиннадцатого элемента И-НЕ - выходом синхронизации D-триггера.

12

-OS

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления динамической памятью | 1990 |

|

SU1800481A1 |

| УСТРОЙСТВО СОВМЕСТНОГО КОДИРОВАНИЯ ГРАНИЦ ПРИ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЯХ | 2012 |

|

RU2497180C1 |

| ДЕКОДЕР ФАЗОМОДУЛИРОВАННОГО СИГНАЛА | 2010 |

|

RU2453991C1 |

| БОРТОВОЙ СПЕЦВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2522852C1 |

| Реверсивный регистр сдвига | 1990 |

|

SU1721632A1 |

| Устройство для сдвига информации | 1985 |

|

SU1291962A1 |

| Устройство для ввода информации | 1988 |

|

SU1667121A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| УСТРОЙСТВО БУФЕРИЗАЦИИ И СИНХРОНИЗАЦИИ ДЛЯ ОБРАБОТКИ НЕПРЕРЫВНОГО СИГНАЛА | 1990 |

|

SU1812885A1 |

| Устройство для задания циклов в системах цифрового программного управления | 1985 |

|

SU1280575A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения контролепригодных последовательностных устройств. Целью изобретения является расширение области применения D-триггера за счет использования его в устройствах с встроенным аппаратным контролем, в основе которого лежат сдвиговые регистры. Проверка устройств, построенных на таких D-триггерах, может осуществляться при любом логическом уровне системного синхросигнала С 1. Кроме того, предлагаемый D-триггер может быть использован для построения сдвиговых регистров практически любой разрядности, что особенно актуально для БИС и СБИС. Цель изобретения достигается введением в известный динамический D-триггер. содержащий шесть элементов Й-НЕ 1-6, пяти элементов И-НЕ 7-11 и дополнительных связей. 3 ил., 1 табл. сл сь ю -N сл со ю

/7

16

18

и

15

15

ъг

19

si

CH

II

Q О

го

с/

С2

21

о/

Фм. г

| Киносита К | |||

| и др | |||

| Логическое проектирование СБИС | |||

| М.: Мир | |||

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

| СТЕРЕООЧКИ | 1920 |

|

SU291A1 |

| Применение интегральных микросхем в электронной вычислительной технике | |||

| Справочник / Под ред | |||

| Б.Н | |||

| Файзулаева, Б.В | |||

| Тарабрина | |||

| М.: Радио и связь, 1987, с | |||

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-01-30—Публикация

1989-01-16—Подача