Изобретение относится к импульсной технике.

Цель изобретения - повышение точности аппроксимации функций при одновременном расширении функциональных возможностей за счет обеспечения формирования N выходных функций.

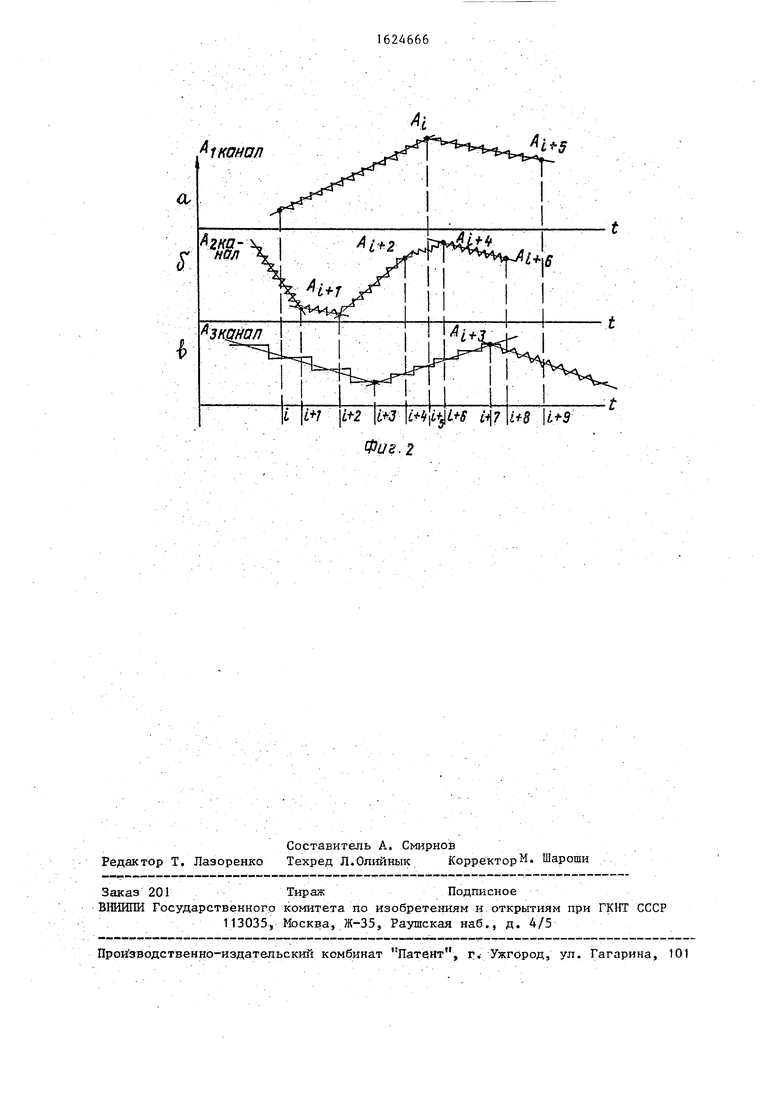

На фиг, 1 приведена структурная схема устройства; на фиг. 2 - временные диаграммы, характеризующие его работу.

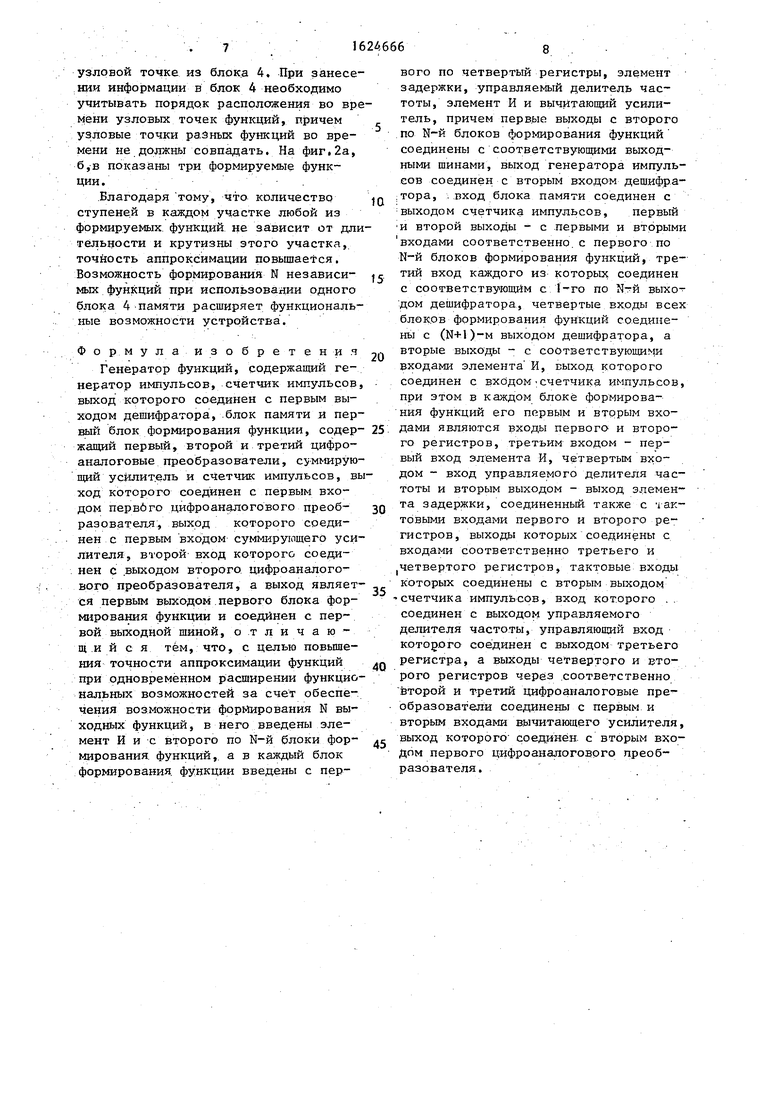

Устройство содержит генератор 1 импульсов, дешифратор 2, счетчик 3 импульсов, блок 4 памяти, элемент И 5, с первого по Н-й блоки 6-1.«.б-N формирования функций, в каждый из кото- рых входят с первого по четвертый регистры 7,.% 10, первый И, второй 12 и третий 13 цифроаналоговые преобразователи, вычитающий усилитель 4, счетчик 15 импульсов, элемент И 16, элемент 17 задержки, управляемый делитель 18 частоты и суммирующий усилитель 19. Первые выходы с первого по N-й блоков 6-1...6-N соединены с соответствующими выходными шинами 20-1...2CHN.

Выход элемента И 5 соединен с входом счетчика 3, выход которого соединен с первым входом дешифратора 2 и входом блока 4, первый выход которого соединен с первыми входами всех блоков 6-1...6-N, а второй вход соединен с вторыми входами этих блоков. Второй вход дешифратора 2 соединен с выходом генератора 1, с первого по N-й выходы - с третьими входами блоков 6т1...6-К соответственно, а (N+0-й выход - с четвертыми входами всех этих блоков. Вторые выходы с первого по N-й блоков 6-1...6-N соединены с соответствующими входами элемента И 5.

В каждом из блоков 6-1 ...6-N входы первого 7 и второго 8 регистров являются соответственно первым и вторым входами данного блока, третьим входом которого является первый вход элемента И 16, четвертым входом - вход управляемого делителя 18, первым выходом - выход суммирующего усилителя 19 вторым выходом - выход элемента 17, соединенный также с тактовыми входами первого 7 и второго 8 регистров, выходы которых соединены с входами соответственно третьего 9 и четвертого 10 регистров, тактовые входы которых соединены с входом элемента 17 и выходом элемента И 16. Выход третьего регистра 9 соединен с управляющим входом управляемого делителя 18, выход которого соединен с входом счетчика 15, первый выход которого соединен с первым входом первого цифроана- логового преобразователя 11, а второй выход - с вторым входом элемента И 16 Выходы четвертого 10 и второго 3 регистров соединены с входами соответственно втордго 12 и третьего 13 цифроаналоговых преобразователей, выходы которых соединены соответственно с первый и вторым входами вычитающего усилителя 14, выход которого подключен к второму входу первого цифроаналогового преобразователя I1. Первый и второй входы суммирующего усилителя 19 соединены с выходами

соответственно первого 11 и второго 12 цифроаналоговых преобразователей.

Дешифратор 2 может быть выполнен на основе БИС ПЗУ или ПЛМ. Его первый вход является многоразрядным кодовым входом, а второй вход - стро- бирующим. При коде на выходе счетчика 3 равном 0 и 1, импульсы проходят на первый выход дешифратора 2, при коде, равном 2 и 3 - на второй выход дешифратора 2, и т.д., наконец при коде, равном 2N-2, и 2N-1 импульсы проходят на N-й выход дешифратора 2. При всех последующих значениях кода на выходе счетчика 3 стробирую- щие импульсы проходят на (N+0-й выход дешифратора 2.

Блок 4 памяти представляет собой постоянное запоминающее устройство, в котором записаны параметры узловых точек формируемых функций. При этом в разрядах, образующих первый выход блока 4, содержится информация о длительности данного участка функции, а в разрядах, образующих второй выход - информация о значении напряжения начальной точки данного участка. Первые 2N слов, записанных в блок 4, содержат информацию о первых двух узловых точках функции, формируемых соответственно блоками с 6-1 по 6-N. В последующих словах блока 4 содержится информация о следующих узловы Точках. При этом должно выполняться условие несовпадения во времени узловых точек разных функций.

Работа генератора состоит из двух стадий.

В течение первой стадии происходит занесение информации о первых двух узловых точках всех формируемых функций в соответствующие блоки 6-1. . ..6-JJ. Предварительно счетчики 3 и 15, регистры 7...10 во всех блоках 6-1...6-И обнуляются (цепи обнуления не показаны. Первый импульс с выхода генератора I проходит (в виде отрицательного импульса) на первый выход дешифратора 2, а затем на третий вход первого блока 6-1, в котором он через элемент И 16 поступает на тактовые входы регистров 9,10, в которых перезаписываются нули из регистров 7,8, Пройдя элемент 17 этот импульс записывает код, хранящийся по нулевому адресу в блоке 4, в регистры 7,8, после чего проходит чере элемент И 5 и своим задним фронтом п

6

реключает счетчик 3 в следующее состояние. Второй импульс с генератора 1, пройдя аналогичный путь, вызывает перезапись информации о первой узловой точке из регистров 7,8 в регистры 9, 10, запись информации о второй узловой точке в регистры 9, 10 и переход счетчика 3 в следующее состояJQ ние. Аналогично происходит запись информации в следующие блоки 6-2... ...6-N, (2К+1)-й и все следующие импульсы проходят на (N+lJ-й выход дешифратора 2.

15 Рассмотрим формирование функции

в блоке 6-1. В регистре 10 записан код значения напряжения в начальной точке первого участка, в регистре 8 - конечной точке, а в регистре 9 - код,

20 обратно пропорциональный длительности первого участка. Напряжение начальной точки с выхода цифроаналогового преобразователя 12 поступает на суммирующий усилитель 19. Разность напря25 жений конечной и начальной точек первого участка поступает на вход опорного напряжения цифроаналогового преобразователя 1 1 .

Счетчик 15 подсчитывает импульсы

30 генератора 1, частота которых делится управляемым делителем 18. По мере нарастания числа н счетчике 15 напряжение на выходе цифроаналогового преобразователя 11 изменяется от нуля до разности напряжеиий второй и первой узловых точек участка формируемой функции, а напряжение на выходной шине 20-1 меняется от значения первой до значения второй точки формируемого участка. Количество ступеней всегда одинаково и определяется коэффициентом пересчета счетчика 15. Длительность каждой ступени и, следовательно, всего участка определяется кодом в регистре 9.

При переполнении счетчика 15 отрицательный импульс с его выхода проходит через элемент И 16, перезаписывает информацию из регистров 7, 8 в

50 регистры 9, 10, а в регистры 7,8 записывает очередное слово из блока 4, после чего увеличивает состояние счетчика 3 на единицу. Б блоке 6-1 начинается формирование следующего участка

55 ФУНКЦИИ.

Аналогично работают остальные блоки 6-2...6-N. Каждый из них, закончив Формирование очередного участка функции, считывает информацию о следующей

35

40

45

узловой точке из блока 4, При занесении информации в блок 4 необходимо учитывать порядок расположения во времени узловых точек функций, причем узловые точки разных функций во времени не должны совпадать. На фиг.2а, б,в показаны три формируемые функции.

Благодаря тому, что количество ступеней в каждом участке любой из формируемых функций не зависит от длительности и крутизны этого участка, точность аппроксимации повышается. Возможность формирования N независи- мых функций при использовании одного блока 4 памяти расширяет функциональные возможности устройства.

Формула изобретения Генератор функций, содержащий генератор импульсов, счетчик импульсов, выход которого соединен с первым выходом дешифратора, блок памяти и первый блок формирования функции, содер- жащий первый, второй и третий цифро- аналоговые преобразователи, cj-ммирую- щий усилитель и счетчик импульсов, выход которого соединен с первым входом первбго цифроаналогового преоб- разователя, выход которого соединен с первым входом суммирующего усилителя, второй вход которого соединен с выходом второго цифроаналогового преобразователя, а выход являет- ся первым выходом первого блока формирования функции и соединен с первой выходной шиной, отличающийся тем, что, с целью повышения точности аппроксимации функций при одновременном расширении функциональных возможностей за счет обеспечения возможности формирования N выходных функций, в него введены элемент И И С ВТОРОГО ПО N-Й блОКИ фор-

мирования функций, а в каждый блок формирования функции введены с перQ

0

5 30Q 45

вого по четвертый регистры, элемент задержки, управляемый делитель частоты, элемент И и вычитающий усилитель, причем первые выходы с второго по N-й блоков формирования функций соединены с соответствующими выходными шинами, выход генератора импульсов соединен с вторым входом дешифратора, вход блока памяти соединен с выходом счетчика импульсов, первый и второй выходы - с первыми и вторыми входами соответственно с первого по N-Й блоков формирования функций, третий вход каждого из которых соединен с соответствующим с 1-го по N-й выходом дешифратора, четвертые входы всех блоков формирования функций соединены с (N+1)-M выходом дешифратора, а вторые выходы - с соответствующими входами элемента И, выход которого соединен с входом .счетчика импульсов, при этом в каждом блоке формирования функций его первым и вторым входами являются входы первого и второго регистров, третьим входом - первый вход элемента И, четвертым входом - вход управляемого делителя частоты и вторым выходом - выход элемента задержки, соединенный также с тактовыми входами первого и второго регистров, выходе. которых соединены с входами соответственно третьего и , четвертого регистров, тактовые входы которых соединены с вторым выходом -счетчика импульсов, вход которого соединен с выходом управляемого делителя частоты, управляющий вход которого соединен с выходом третьего регистра, а выходы четвертого и второго регистров через соответственно второй и третий цифроаналоговые преобразователи соединены с первым и вторым входами вычитающего усилителя, выход которого соединен с вторым входом первого цифроаналогового преобразователя.

-I1) |11-

I i+2 |frJ Mi$L+S Ц7

i+5

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь двух переменных | 1984 |

|

SU1168964A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Калибратор сигналов, нормированных по коэффициенту гармоник | 1988 |

|

SU1555677A1 |

| Устройство для решения задач оптимального управления | 1985 |

|

SU1327135A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Устройство для решения инверсных задач нестационарной теплопроводности | 1983 |

|

SU1179388A1 |

| Многоканальный функциональный генератор | 1984 |

|

SU1191922A1 |

| Устройство для контроля температуры погружного электродвигателя и давления на приеме насоса | 1989 |

|

SU1652525A1 |

| Устройство для управления меткой на экране индикатора | 1983 |

|

SU1160451A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1300542A1 |

Изобретение относится к импульсной технике. Цель изобретения - повышение точности аппроксимации функции при одновременном расширении функциональных возможностей за счет обеспечения формирования N выходных функций. Для достижения цели в генератор, содержащий генератор 1 импульсов,

Фиг. 2

| Управляемый генератор ступенчатого напряжения | 1980 |

|

SU911696A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Формирователь напряжения ступенчатой формы | 1980 |

|

SU936403A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-01-30—Публикация

1988-04-11—Подача