Изобретение относится к радиотехнике и может быть использовано в приемопередающей и измерительной аппаратуре.

Цель изобретения - повышение спектральной чистоты выходных колебаний за счет уменьшения помех дробности.

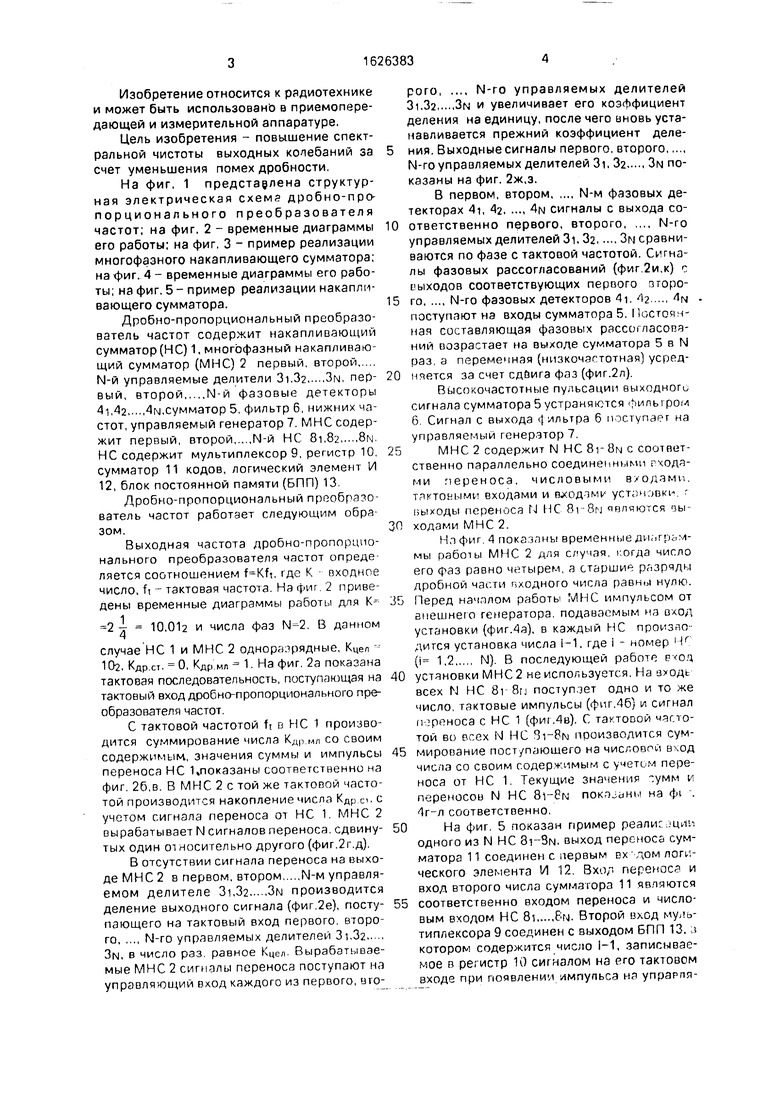

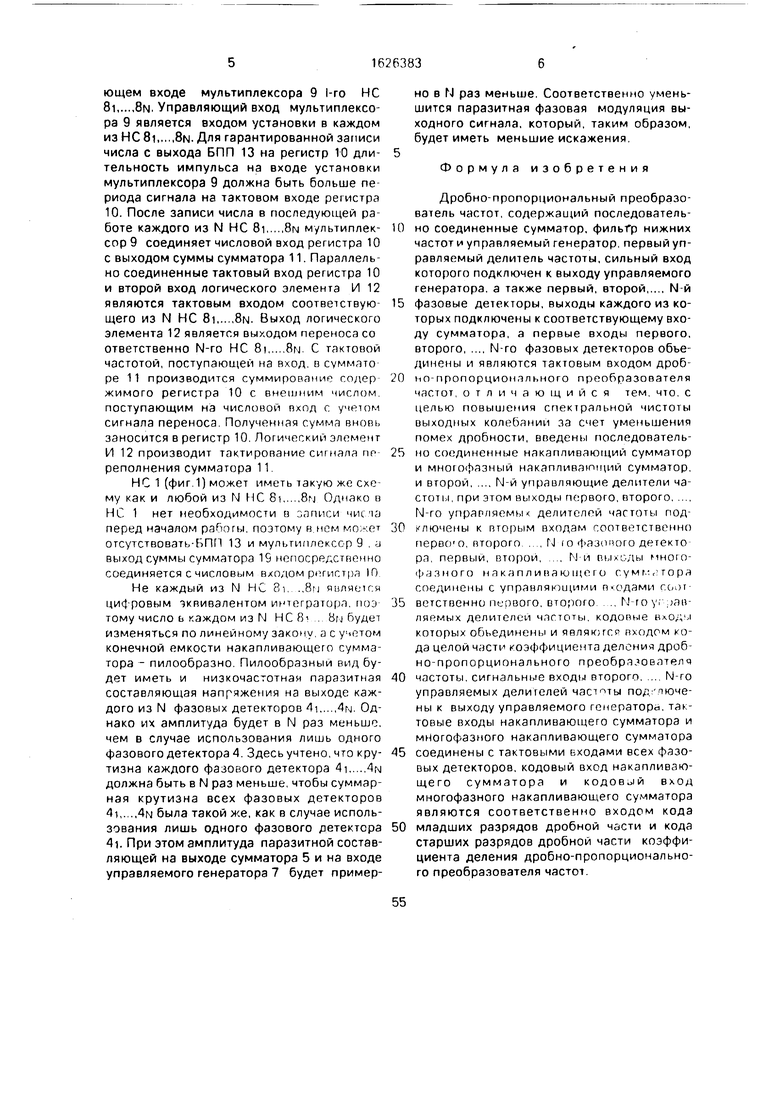

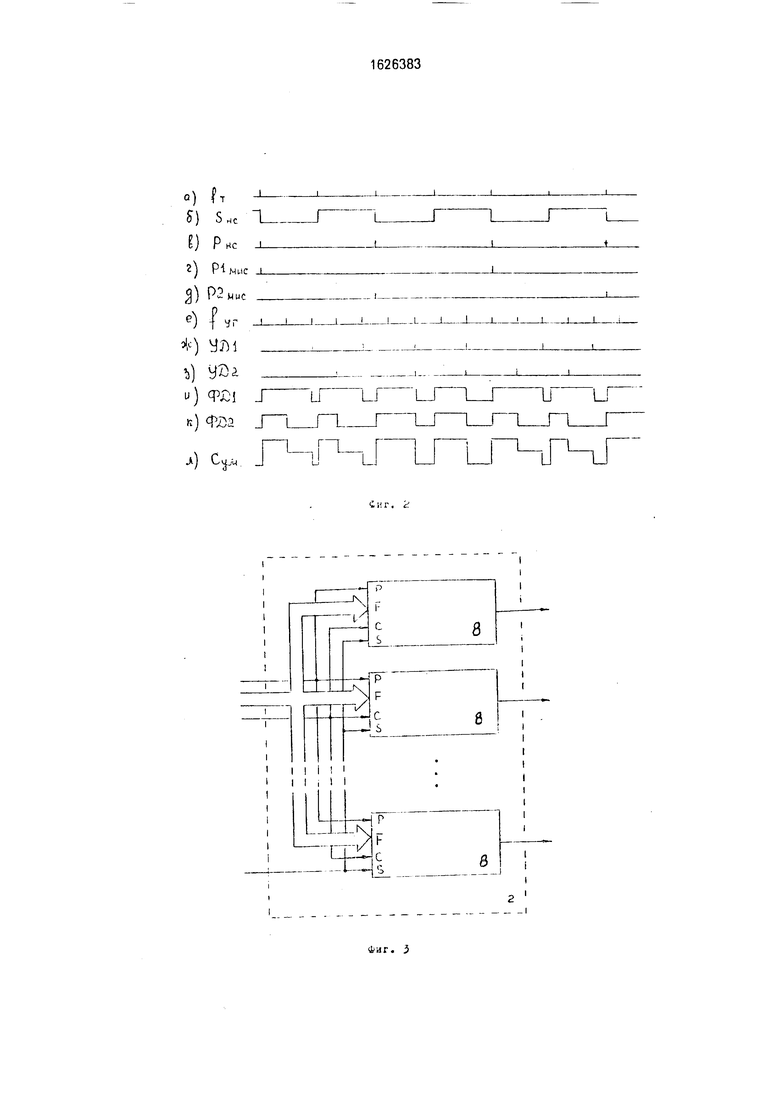

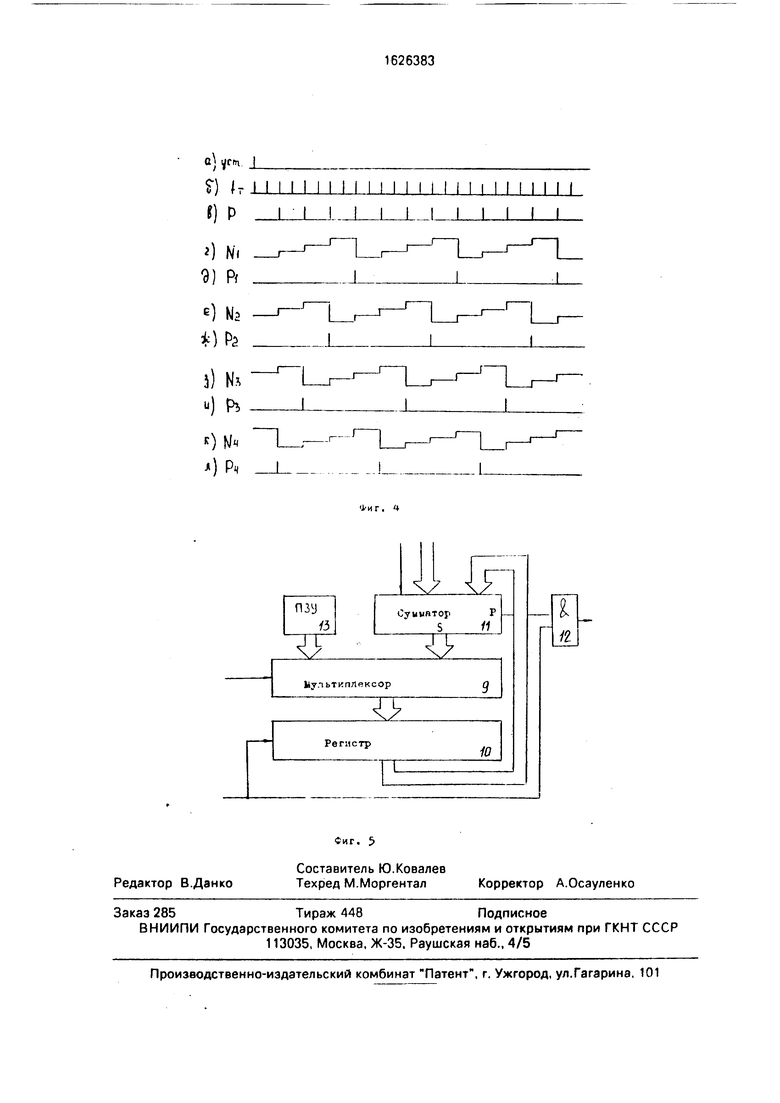

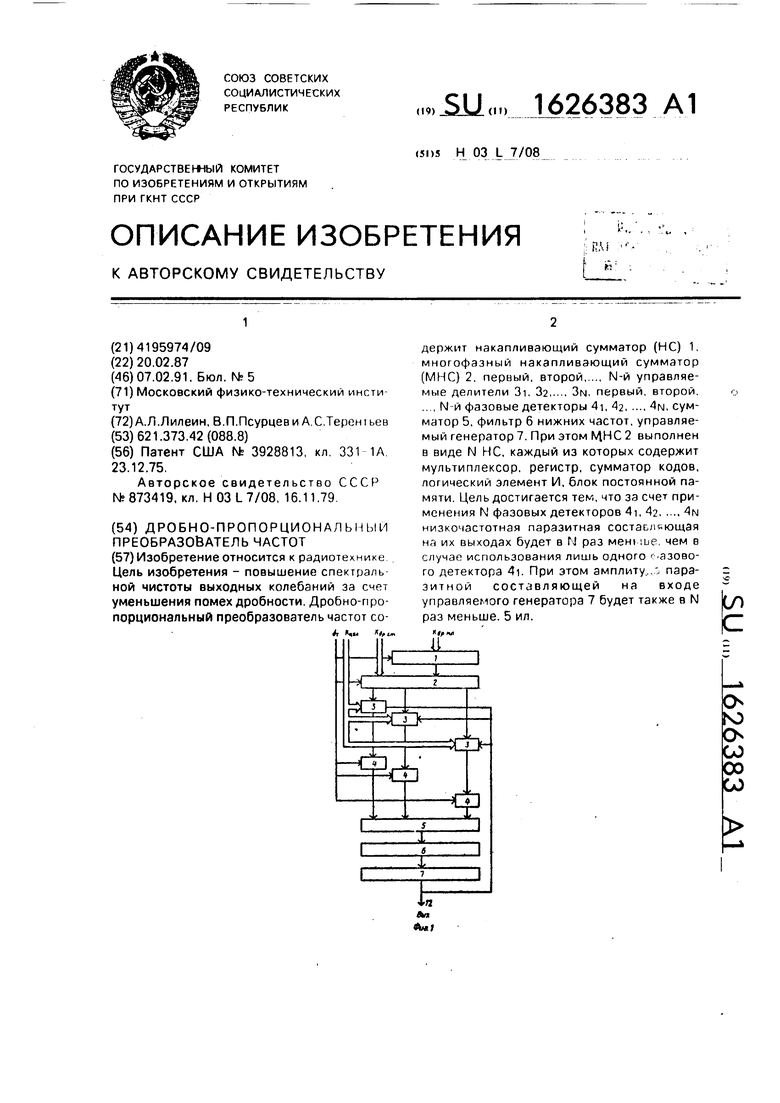

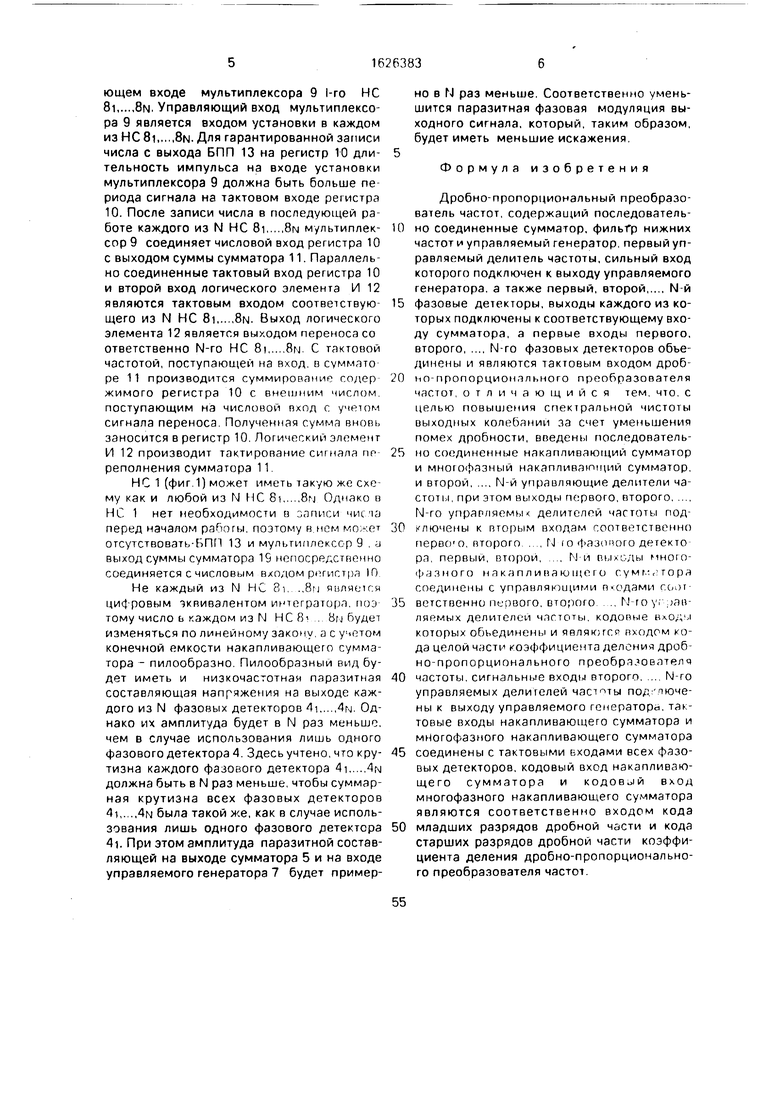

На фиг. 1 представлена структурная электрическая схема дробно-пропорционального преобразователя частот; на фиг. 2 - временные диаграммы его работы; на фиг. 3 - пример реализации многофазного накапливающего сумматора; на фиг. 4 - временные диаграммы его работы; на фиг. 5 - пример реализации накапливающего сумматора.

Дробно-пропорциональный преобразователь частот содержит накапливающий сумматор (НС) 1, многофазный накапливающий сумматор (МНС) 2 первый, второй

N-й управляемые делители 3i,32Зм. пер-

вый, второйN-й фазовые детекторы

4-|,424м,сумматор 5, фильтр 6, нижних частот, управляемый генератор 7. МНС содержит первый, второйN-й НС 81,8г,...,8м.

НС содержит мультиплексор 9, регистр 10, сумматор 11 кодов, логический элемент И 12, блок постоянной памяти (БПП) 13.

Дробно-пропорциональный преобразователь частот работает следующим образом.

Выходная частота дробно-пропорционального преобразователя частот определяется соотношением , где К - входное число, ft тактовая частота. На фиг 2 приведены временные диаграммы работы для К-

2 -т - 10,012 и числа фаз . В данном

случае НС 1 и МНС 2 одноразрядные, Кцел - 102, Кдр.ст. 0, Кдр мл 1. На фиг. 2а показана тактовая последовательность, поступающая на тактовый вход дробно-пропорционального преобразователя частот.

С тактовой частотой ft в НС 1 производится суммирование числа Кдр мл со своим содержимым,, значения суммы и импульсы переноса НС показаны соответственно на фиг. 26,в. В МНС 2 с той же тактовой частотой производится накопление числа Кдр С . с учетом сигнала переноса от НС 1. МНС 2 вырабатывает N сигналов переноса, сдвину- тых один от носигельно другого (фиг.2г.д).

В отсутствии сигнала переноса на выходе МНС 2 в первом, второмN-м управляемом делителе 3i,32Зы производится

деление выходного сигнала (фиг.2е), посту- лающего на тактовый вход первого, второго N-ro управляемых делителей 3i,32

Зм, в число раз, равное Кцел. Вырабатываемые МНС 2 сигналы переноса поступают на управляющий вход каждого из первого, второго N-ro управляемых делителей

3i,32SN и увеличивает его коэффициент

деления на единицу, после чего вновь устанавливается прежний коэффициент деления. Выходные сигналы первого, второго

N-ro управляемых делителей Зт, 32SN показаны на фиг. 2ж,з.

В первом, втором N-м фазовых детекторах 4i, 42, ..., AN сигналы с выхода соответственно первого, второго N-ro

управляемых делителей 3i, 32Зм сравниваются по фазе с тактовой частотой. Сигналы фазовых рассогласований (фиг.2и,к) с выходов соответствующих первого згорогоN-ro фазовых детекторов 4i, 24м

поступают на входы сумматора 5. Постоянная составляющая фазовых рассогласований возрастает на выходе сумматора 5 в N раз, а переменная (низкочагтотная) усредняется за счет сдвига фаз (фиг.2л).

Высокочастотные пульсации выходного сигнала сумматора 5 устраняются ром 6. Сигнал с выхода фильтра 6 поступает на управляемый генератор 7.

МНС 2 содержит N НС 8г SN с соответственно параллельно соединенными гхода- ми переноса, числовыми входами, тактовыми входами и вводами установки - выходы переноса N НС 8г8м являются выходами МНС 2.

Нл фиг. 4 показаны временные ди гром- мы работы МНС 2 для случая, когда число его фаз равно четырем, а старшие разряды дробной части входного числа равно) нулю. Перед началом работы МНС импульсом от внешнею генератора, подаваемым на сход установки (фиг.4а), в каждый НС производится установка числа 1-1, где i - номер Нг

(i 1,2 N). В последующей работе

установки МНС 2 не используется. На аходь всех N НС 8г 8и поступает одно и то же число, тактовые импульсы (фиг.46) и сигнал п-греноса с НС 1 (фш.4в). С тактовой частотой во всех N НС пооизводится суммирование поступающего на числовой вход числа со своим содержимым с учетом переноса от НС 1. Текущие значения умм v переносов N НС SI-SN покованы на ф1 -. 4г-л соответственно.

На фиг. 5 показан пример реалис.- цш- одного из N НС . выход переноса сумматора 11 соединен с первым вх дом логического элемента И 12. Вхоя переноса и вход второго числа сумматора 11 являются соответственно входом переноса и числовым входом НС 8iBN. Второй вход мулотиплексора 9 соединен с выходом БПП 13, л котором содержится число 1-1, записываемое в регистр 10 сигналом на его тактовом входе при появлении импульса на упраппяющем входе мультиплексора 9 1-го НС 8iBN. Управляющий вход мультиплексора 9 является входом установки в каждом

из НС 8iSN. Для гарантированной записи

числа с выхода БПП 13 на регистр 10 длительность импульса на входе установки мультиплексора 9 должна быть больше периода сигнала на тактовом входе регистра 10. После записи числа в последующей работе каждого из N НС 81SN мультиплексор 9 соединяет числовой вход регистра 10 с выходом суммы сумматора 11. Параллельно соединенные тактовый вход регистра 10 и второй вход логического элемента И 12 являются тактовым входом соответствующего из N НС 8i8м. Выход логического

элемента 12 является выходом переноса со

ответственно N-ro НС 8i8м. С тактовой

частотой, поступающей на вход, в суммато ре 11 производится суммирование содер жимого регистра 10 с внешним числом поступающим на числовой вход с учетом сигнала переноса. Полученная сумма вновь заносится в регистр 10. Логический элемент И 12 производит тактирование сигнала переполнения сумматора 11

НС 1 (фиг.1) может иметь такую же схему как и любой из N НС 818rj Однако в

НС 1 нет необходимости в записи чиста перед началом работы, поэтому в нем мо/чет отсутствовать-БПП 13 и мультиплексор 9 , а выход суммы сумматора 19 непосредственно соединяется с числовым входом регистра IO

Не каждый из N НС 81, .,8u является цифровым эквивалентом интегратора, поэ тому число ь каждом из N НС 8-i 8м будет изменяться по линейному закону, а с учетом конечной емкости накапливающего сумматора - пилообразно. Пилообразный вид будет иметь и низкочастотная паразитная составляющая напряжения на выходе каждого из N фазовых детекторов 4iAN. Однако их амплитуда будет в N раз меньше, чем в случае использования лишь одного фазового детектора 4. Здесь учтено, что крутизна каждого фазового детектора 4i4ы

должна быть в N раз меньше, чтобы суммарная крутизна всех фазовых детекторов 4i4м была такой же, как в случае использования лишь одного фазового детектора 4i. При этом амплитуда паразитной составляющей на выходе сумматора 5 и на входе управляемого генератора 7 будет примерно в N раз меньше. Соответственно уменьшится паразитная фазовая модуляция выходного сигнала, который, таким образом, будет иметь меньшие искажения.

Формула изобретения

Дробно-пропорциональный преобразователь частот, содержащий последовательно соединенные сумматор, фильГр нижних частот и управляемый генератор, первый управляемый делитель частоты,сильный вход которого подключен к выходу управляемого генератора, а также первый, второй М-й

фазовые детекторы, выходы каждого из которых подключены к соответствующему входу сумматора, а первые входы первого, второго N-ro фазовых детекторов объединены и являются тактовым входом дробно-пропорционального преобразователя частот, отличающийся тем, что. с целью повышения спектральной чистоты выходных колебании за счет уменьшения помех дробности, введены последовательно соединенные накапливающий сумматор и многофазный накапливающий сумматор, и второйN-й управляющие делители частоты, при этом выходы первого, второго

N-ro упрапляемьи делителей частоты подключены к вторым входам соответственно перво о, второго . , N го фазшюго детекто ра, первый, второй, , N и пылоды мною- фазного накапливающего гумг/г-торд соединены с управляющими п«одами гоот

ветственно nt oooro, второго ., N-ro у г .являемых делителей частоты, кодовые входм которых объединены и ЯВЛЯЮГСР входом кода целой части коэффициента деления дробно-пропорционального преобразователя

частоты, сигнальные входы второго, .. N-ro управляемых делителей частоты по/т- пюче- ны к выходу управляемого генератора, тактовые входы накапливающего сумматора и многофазного накапливающего сумматора

соединены с тактовыми входами всех фазовых детекторов, кодовый вход накапливающего сумматора и кодовош вход многофазного накапливающего сумматора являются соответственно входом кода

младших разрядов дробной части и кода старших разрядов дробной части коэффициента деления дробно-пропорционального преобразователя частот.

о)Ь

Ј)SHC

ОРИС

г)Pi мне

j)P2uuc

e) r

)УЛ1

%)У u)Фл)1

к)Фй2

Л)Сил

Г

L

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1987 |

|

SU1741260A1 |

| Программируемый формирователь многочастотного сигнала | 1989 |

|

SU1739472A1 |

| СИНТЕЗАТОР ЧАСТОТЫ ДЛЯ СОЗДАНИЯ СИНТЕЗИРОВАННОЙ ВЫХОДНОЙ ЧАСТОТЫ | 1989 |

|

RU2085031C1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1356222A1 |

| СИНТЕЗАТОР ЧАСТОТЫ С ДЕЛЕНИЕМ НА ДРОБНОЕ ЧИСЛО И КОРРЕКЦИЕЙ ОСТАТОЧНОЙ ПОГРЕШНОСТИ И СПОСОБ СИНТЕЗА ЧАСТОТЫ | 1994 |

|

RU2134930C1 |

| Синтезатор частот | 1989 |

|

SU1646053A1 |

| ЦИФРОВОЙ МНОГОФАЗНЫЙ ГЕНЕРАТОР | 1992 |

|

RU2066918C1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| Синтезатор частот | 1987 |

|

SU1610599A1 |

| Цифровой измеритель электрической энергии многофазной сети | 1988 |

|

SU1647443A1 |

Изобретение относится к радиотехнике Цель изобретения - повышение спектраль ной чистоты выходных колебаний за счет уменьшения помех дробности. Дробно-пропорциональный преобразователь частот содержит накапливающий сумматор (НС) 1. многофазный накапливающий сумматор (МНС) 2. первый, второй N-й управляемые делители 3i. 32 Зм, первый, второй. .. , N-й фазовые детекторы 4i, 424м, сумматор 5, фильтр 6 нижних частот, управляемый генератор 7. При этом ОДНС 2 выполнен в виде N НС, каждый из которых содержит мультиплексор, регистр, сумматор кодов, логический элемент И, блок постоянной памяти. Цель достигается тем, что за счет применения N фазовых детекторов 4i, 424ы низкочастотная паразитная составляющая на их выходах будет в N раз MCHI ше. чем в случае использования лишь одного г.азово- го детектора 4i. При этом амплиту„.о паразитной составляющей на входе управляемого генератора 7 будет также в N раз меньше. 5 ил. (Л С L о ю о со оо CJ ь

С к г. d

8

иг. 3

Z,

Мультиплексор

Регистр

/2

| Патент США № 3928813, кл | |||

| Накладной висячий замок | 1922 |

|

SU331A1 |

| Устройство фазовой автоподстройки частоты | 1979 |

|

SU873419A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-02-07—Публикация

1987-02-20—Подача