Изобретение относится к радиотехнике и может быть использовано в приемопередающей и измерительной аппаратуре.

Известны устройства для цифрового фазового детектирования импульсных последовательностей на неравных частотах, содержащие фазовый детектор, первый вход которого является входом первой последовательности, а выход соединен с входом фильтра, выход которого является выходом устройства, управляемый делитель, тактовый вход которого является входом второй последовательности, а управляющий вход соединен с выходом переноса накапливающего сумматора, тактовый вход которого соединен с выходом управляемого делителя и вторым входом фазового детектора, числовые входы управляемого делителя и накапливающего сумматора являются соответственно входами старших и младших разрядов кода настройки.

Недостатком этих устройств является низкая динамическая точность детектирования.

Наиболее близким по технической сущности к устройству для цифрового фазового детектирования импульсных последовательностей на неравных частотах является устройство, содержащее последовательно соединенные накапливающий сумматор, тактовый и числовой входы которого являются соответственно входом первой последовательности и входом кода настройки,

vi

го о о

цифроаналоговый преобразователь и фильтр, выход которого является выходом устройства, кроме того, оно содержит импульсный фазовый детектор, выполненный в форме RS-триггера, R-вход которого является входом второй последовательности, S- вход соединен с выходом переноса накапливающего сумматора, а выход - с входом старшего разряда цифроаналогово- го преобразователя,

Недостатком этого устройства является низкая динамическая точность детектирования, которая здесь ограничена прежде всего быстродействием и разрядностью цифроаналогового преобразователя.

Целью изобретения является повышение динамической точности детектирования путем усреднения фазовых рассогласований сдвинутых по фазе последовательностей..

Поставленная цель достигается тем, что устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах, содержащее накапливающий сумматор, тактовый и числовой входы которого являются соответственно входом первой последовательности и входом младших разрядов кода настройки, а выход суммы соединен с входом цифроа- налогозого преобразователя, фильтр, выход которого является выходом устройства, и фазовый детектор, первый вход которого является входом второй последовательности, содержит сумматор, дополнительные фазовые детекторы и многофазный накапливающий сумматор, числовой вход которого является входом старших разрядов кода настройки, тактовый вход и вход переноса соединены соответственно с тактовым входом и выходом переноса накапливающего сумматора, первые входы всех фазовых детекторов объединены, выходы многофазного накапливающего сумматора соединены с вторыми входами всех фазовых детекторов, выходы которых и выход цифроаналогового преобразователя соединены с входами сумматора, выход которого соединен с входом фильтра.

Кроме того, многофазный накапливающий сумматор выполнен в виде N накапливающих сумматоров, где N прямо пропорционально необходимой точности детектирования, соответственно параллельно объединенные входы переноса, числовой, тактовый и установки которых являются входами переноса, кода настройки, тактовым и установки многофазного накапливающего сумматора, а выходы переноса накапливающих сумматоров являются выходами многофазного накапливающего сумматора.

Кроме того, каждый накапливающий сумматор, входящий в состав многофазного

накапливающего сумматора, содержит соединенные в кольцо цифровой сумматор, мультиплексор и регистр, выход переноса цифрового сумматора соединен с первым входом логического элемента И, второй

0 вход мультиплексора соединен с выходом постоянного запоминающего устройства, определяющим начальное состояние накапливающего сумматора, второй вход и вход переноса цифрового сумматора являются

5 входами числовым и переноса накапливающего сумматора, параллельно соединенные тактовый вход регистра и второй вход логического элемента И являются тактовым входом накапливающего сумматора,

0 управляющий вход мультиплексора является входом установки накапливающего сумматора, выход логического элемента является выходом переноса накапливающего сумматора.

5Кроме того, многофазный накапливающей сумматор содержит соединенные в кольцо регистр и постоянное запоминающее устройство, дополнительные выходы которого являются выходами многофазного

0 накапливающего сумматора, а дополнительные входы постоянного запоминающего устройства и параллельно соединенные дополнительный вход постоянного запоминающего устройства и тактовый вход реги5 стра являются соответственно входом переноса, числовым и тактовым многофазного накапливающего сумматора.

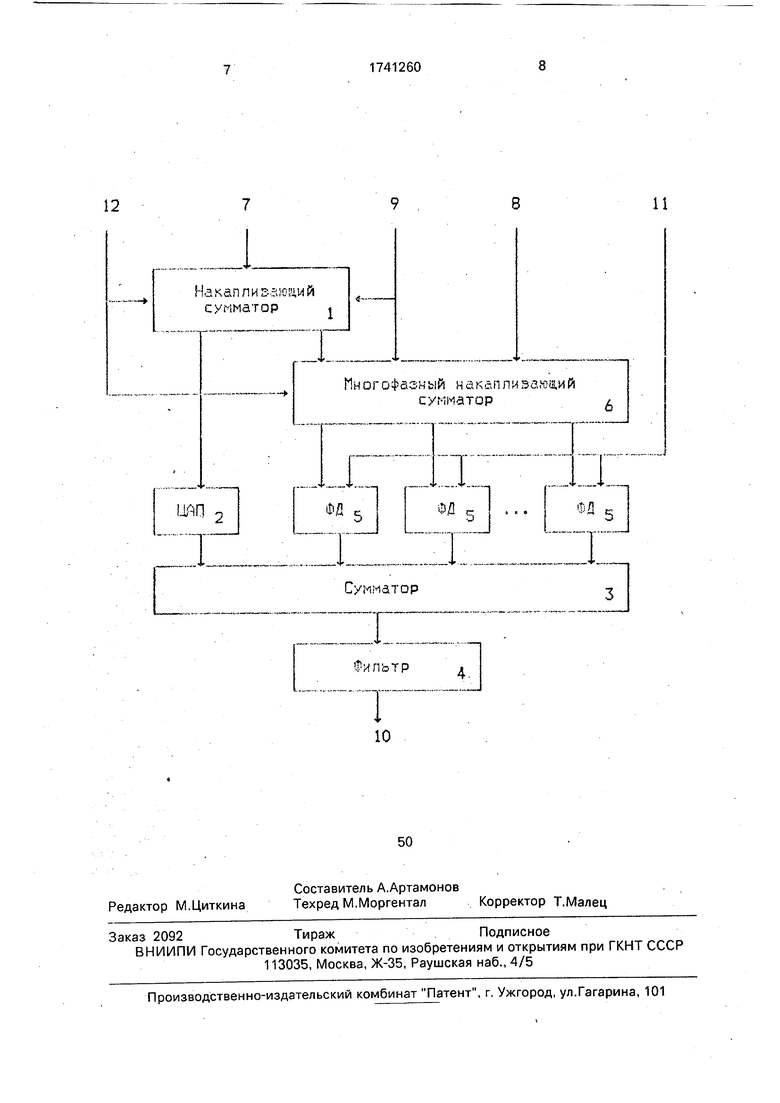

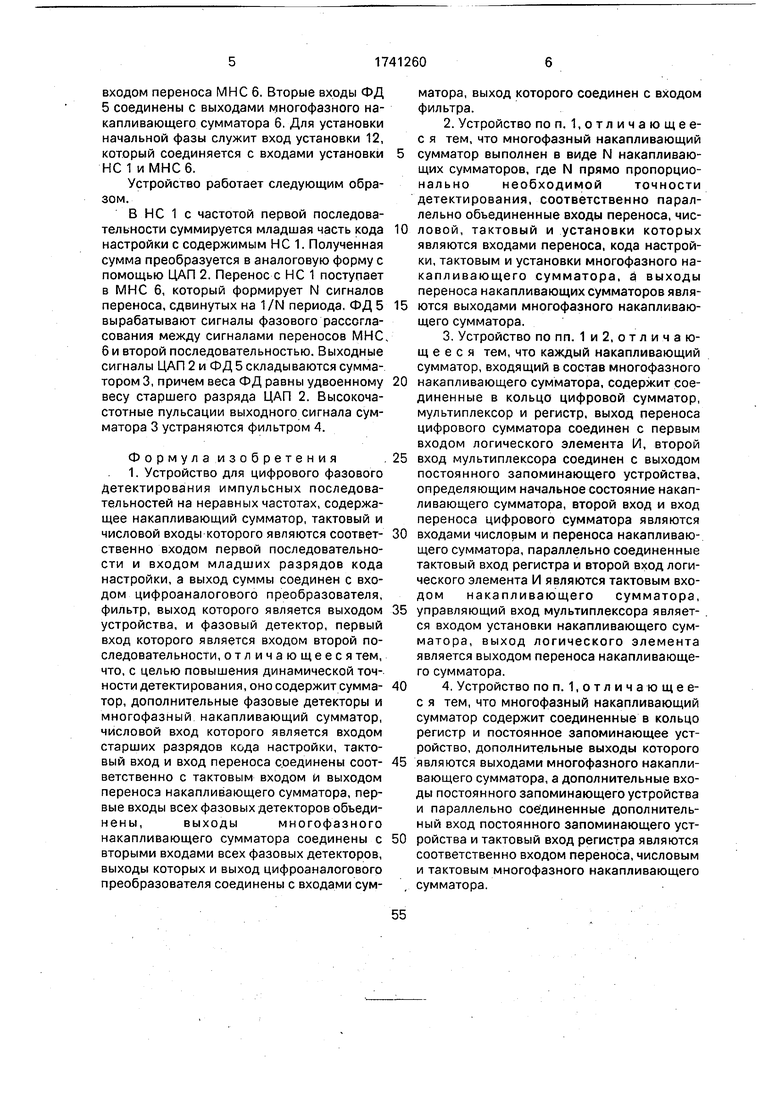

На чертеже приведена блок-схема устройства для цифрового фазового детектиро0 вания импульсных последовательностей на неравных частотах.

Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах содержит

5 последовательно соединенные накапливающий сумматор (НС) 1, цифроаналоговый преобразователь (ЦАП) 2, сумматор 3, фильтр 4, фазовые детекторы (ФД) 5, выходы которых соединены с входами сумматора

0 3, и многофазный накапливающий сумматор (МНС) 6.

Числовые входы НС 1 и МНС 6 являются входами 7 и 8 соответственно младших и старших разрядов кода настройки. Парал5 лельно соединенные тактовые входы НС 1 и МНС б являются входом 9 первой последовательности. Выход фильтра 4 является выходом 10 устройства. Первые входы ФД 5 являются входом 11 второй последовательности. Выход переноса НС 1 соединен с

входом переноса МНС 6. Вторые входы ФД

5соединены с выходами многофазного накапливающего сумматора 6. Для установки начальной фазы служит вход установки 12, который соединяется с входами установки НС 1 и МНС 6.

Устройство работает следующим образом.

В НС 1 с частотой первой последовательности суммируется младшая часть кода настройки с содержимым НС 1. Полученная сумма преобразуется в аналоговую форму с помощью ЦАП 2. Перенос с НС 1 поступает в МНС 6, который формирует N сигналов переноса, сдвинутых на 1/N периода. ФД 5 вырабатывают сигналы фазового рассогласования между сигналами переносов МНС,

6и второй последовательностью. Выходные сигналы ЦАП 2 и ФД 5 складываются сумматором 3, причем веса ФД равны удвоенному весу старшего разряда ЦАП 2. Высокочастотные пульсации выходного сигнала сумматора 3 устраняются фильтром 4.

Формула изобретения 1. Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах, содержащее накапливающий сумматор, тактовый и числовой входы которого являются соответственно входом первой последовательности и входом младших разрядов кода настройки, а выход суммы соединен с входом цифроаналогового преобразователя, фильтр, выход которого является выходом устройства, и фазовый детектор, первый вход которого является входом второй последовательности, отличающееся тем, что, с целью повышения динамической точности детектирования, оно содержит сумматор, дополнительные фазовые детекторы и многофазный накапливающий сумматор, числовой вход которого является входом старших разрядов кода настройки, тактовый вход и вход переноса соединены соответственно с тактовым входом и выходом переноса накапливающего сумматора, первые входы всех фазовых детекторов объеди- нены,выходымногофазного

накапливающего сумматора соединены с вторыми входами всех фазовых детекторов, выходы которых и выход цифроаналогового преобразователя соединены с входами сумматора, выход которого соединен с входом фильтра.

2.Устройство по п. 1,отличающее- с я тем, что многофазный накапливающий

сумматор выполнен в виде N накапливающих сумматоров, где N прямо пропорционально необходимой точности детектирования, соответственно параллельно объединенные входы переноса, числовой, тактовый и установки которых являются входами переноса, кода настройки, тактовым и установки многофазного на- капливающего сумматора, а выходы переноса накапливающих сумматоров являются выходами многофазного накапливающего сумматора.

3.Устройство по пп. 1 и 2, отличающее с я тем, что каждый накапливающий сумматор, входящий в состав многофазного

накапливающего сумматора, содержит соединенные в кольцо цифровой сумматор, мультиплексор и регистр, выход переноса цифрового сумматора соединен с первым входом логического элемента И, второй

вход мультиплексора соединен с выходом постоянного запоминающего устройства, определяющим начальное состояние накапливающего сумматора, второй вход и вход переноса цифрового сумматора являются

входами числовым и переноса накапливающего сумматора, параллельно соединенные тактовый вход регистра и второй вход логического элемента И являются тактовым входом накапливающего сумматора,

управляющий вход мультиплексора является входом установки накапливающего сумматора, выход логического элемента является выходом переноса накапливающего сумматора.

4. Устройство по п. 1,отличающее- с я тем, что многофазный накапливающий сумматор содержит соединенные в кольцо регистр и постоянное запоминающее устройство, дополнительные выходы которого

являются выходами многофазного накапливающего сумматора, а дополнительные входы постоянного запоминающего устройства и параллельно соединенные дополнительный вход постоянного запоминающего устройства и тактовый вход регистра являются соответственно входом переноса, числовым и тактовым многофазного накапливающего сумматора.

12

В

11

| название | год | авторы | номер документа |

|---|---|---|---|

| Дробно-пропорциональный преобразователь частот | 1987 |

|

SU1626383A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1988 |

|

SU1757080A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1068838A1 |

| Цифровой фазовый детектор | 1980 |

|

SU892654A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1987 |

|

SU1631700A1 |

| Устройство для формирования базисно-тригонометрических функций | 1990 |

|

SU1792542A3 |

| СИНТЕЗАТОР ЧАСТОТЫ | 2002 |

|

RU2237972C2 |

| ЦИФРОВОЙ СИНТЕЗАТОР ГАРМОНИЧЕСКИХ КОЛЕБАНИЙ | 2003 |

|

RU2239281C2 |

| Цифровой фазовый детектор | 1980 |

|

SU875303A1 |

| МУЛЬТИПЛЕКСОР ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2295148C1 |

Изобретение относится к радиотехнике и предназначено для приемопередающей и измерительной аппаратуры. Цель изобретения - повышение динамической точности детектирования путем усреднения фазовых рассогласований сдвинутых по фазе последовательностей. В устройство, содержащее накапливающий сумматор, цифроаналого- вый преобразователь, фильтр и фазовый детектор, введены сумматор, дополнительные фазовые детекторы и многофазный накапливающий сумматор. Содержимое накапливающего сумматора с частотой первой последовательности суммируется с младшей частью кода настройки и полученная сумма преобразуется в аналоговую форму. Перенос с накапливающего сумматора поступает в многофазный накапливающий сумматор, формирующий N-сигналов переноса, а дополнительные фазовые детекторы вырабатывают сигналы рассогласования между ними и второй последовательностью. 3 з.п. ф-лы, 1 ил. СП С

Накаппиэз сглий сумматор

ФД

1

Сумматор

:zri

ИЛЬТР

10

Многофазный накйплизакш.ий сумматор

ОД

ОД 5

i:

3

| Патент США № 3928813, кл | |||

| Накладной висячий замок | 1922 |

|

SU331A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1981 |

|

SU1109872A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Синтезатор частот | 1982 |

|

SU1117839A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1992-06-15—Публикация

1987-02-20—Подача