Изобретение относится к радисггех- нике и может быть использовано в приемопередающей и измерительной аппаратуре «

Целью изобретения является уменьшение шага сетки синтезируемых частот при одновременном повышении быстродействия.

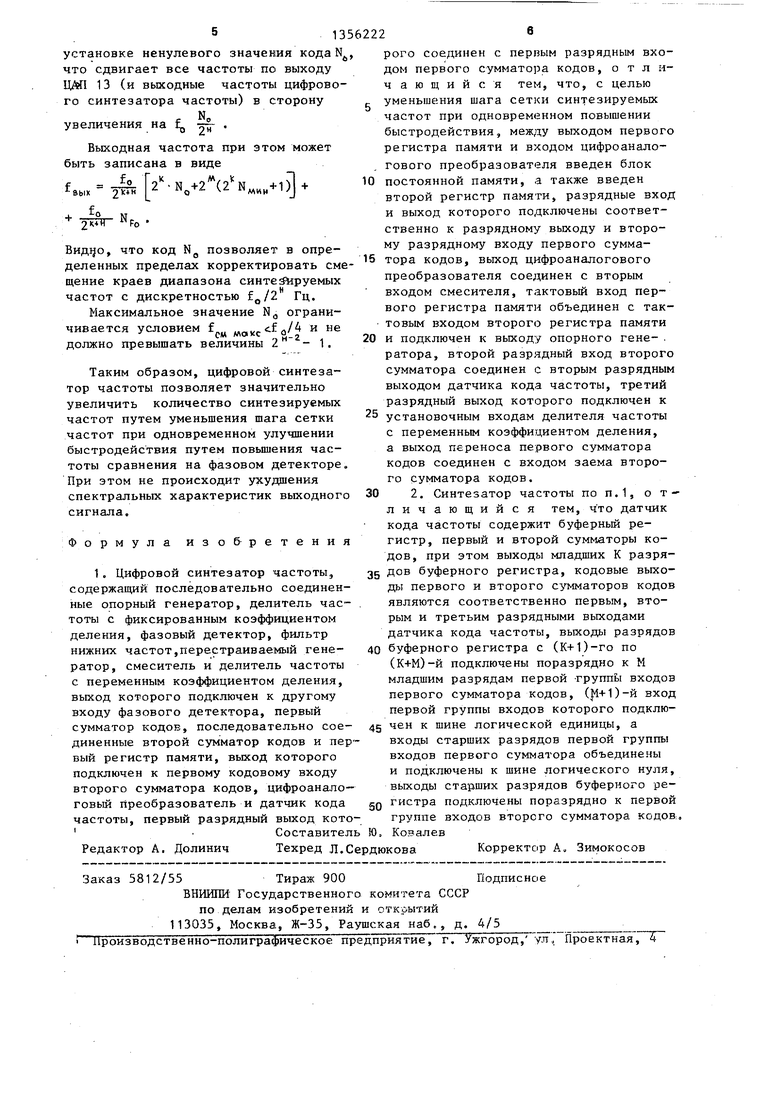

На чертеже представлена электричес-ю Риод сигнала опорной частоть f плюс

кая структурная схема цифрового синтезатора частоты.

Цифровой синтезатор частоты содержит перестраиваемый генератор 1, смеситель 2, делитель 3 частоты с переменным коэффициентом деления (ДПКД), фазовый детектор 4, фильтр 5 нижних частот, опорный генератор 6, делитель 7 частоты с фиксированным коэффициентом деления (ДФКД), датчик 8 кода частоты, первый сумматор 9 кодов второй сумматор 10 кодов, первый регистр 11 памяти,-блок 12 постоянной памяти (БПП), цифроанапоговый преобразователь (ЦАП) 13, второй регистр 14 памяти. При этом датчик 8 кода содержит первый сумматор 15 кодов, второй сумматор 16 кодов, буферный регистр 17,

Цифровой синтезатор частоты работает следующим образом.

В БПП 12 записаны 2 округленных до целого числа отсчетов синусоиды.

i

« l)6in -i- 2

где

Т - количество разрядов слова в ячейках цамяти БПП 12, Н - количество разрядов в адресе ячейки, j. - текущий адрес ячейки, изменяющийся от О до . датчика 8 кода число g.. равно нулю, Фильтром 5, при частоте сигнала на

Таким образом, при изменении ко gцИ g на соответствующих входах первого и второго сумматоров 9 и 1 частота сигнала на выходе ЦАП 13 может изменяться от ,о дискретом: /2 . Кольцо фазовой автоподстройки, образованное перес раиваемым генератором 1, смесителем

f./4

Если на перэом разрядном выходе 40 фазовым детектором 4 и

втором входе фазового детектора 4, равной f. /2 , где 2 - коэффициент деления ДФКД 7, синтезирует частот

а на втором разрядном выходе число g. э О, то с каждым тактовым импуль- ,сом f с выхода опорного генератора 6 содержимое первого регистра 11 увеличивается на величину g, поскольку содержимое первого регистра 11 суммируется с числом gu во втором сумматоре 10. При этом на вход заема второго сумматора 10 не поступает сигнал с выхода переноса первого сумматора 9. Код на выходе первого регистра 11 поступает в виде адреса на БПП 12, с выхода которого код i отсчета синусоиды поступает на вход ЦАП 13, на выходе которого формируется отсчет синусоиды с фазой 2Т Вц/ каждые /tg секунд и частота сигнала на ви ходе ЦАП 13 в этом режиме равна

Г о - п может и:)М(, Нлтьс я от

Д fo/ i (выбирать значения g макс.больше,чем 2 нецелесообразно) .При сме- Р: кода g на втором разрядном выходе датчика 8 кода частоты сигнал на выходе liAII 13 изменяется и устанавли- вается не позднее, чем через один певремя выборки БПП 12 и время установления ЦАП 13.

Рассмотрим случай, когда код g на первом разрядном выходе датчика 8 кода не равен нулю. Первый сумматор 9 и второй регистр 14 образуют так

называемый накапливающий сумматор с

емкостью / , при этом на выходе переноса первого сумматора 9 будет возни- кать импульс переполнения каждые g /2

периодов опорной частоты f . С

Г1(/

этой

дискретностью синусоида на выходе ЦАП 13 будет получать приращение фазы. В связи с этим частота сигнала на вы- 5 ходе ЦАП 13, равная f gH/, получит

Время,

-о ьн приращение, равное f ,

необходимое для установки этого привыходе ПАП 13,

0

5

Фильтром 5, при частоте сигнала на

ращения частоты на

2 равно -г- тактов опорной частоты f .

ь

Таким образом, при изменении кодов gцИ g на соответствующих входах первого и второго сумматоров 9 и 10 частота сигнала на выходе ЦАП 13 может изменяться от ,о дискретом: /2 . Кольцо фазовой автоподстройки, образованное перестраиваемым генератором 1, смесителем

f./4

Фильтром 5, при частоте сигнала на

втором входе фазового детектора 4, равной f. /2 , где 2 - коэффициент деления ДФКД 7, синтезирует частоту

Е -if- вык 2У

N + f

см

f.

N

-частота сигнала на втором входе смесителя 2;

-коэффициент деления ДПКД 3.

Если выбрать параметры цифрового синтезатора частоты таким образом, чтобы изменение частоты f .. с выхода ЦАП 13 было не меньше величины fg/2 , 55 « О будет перекрываться диапазон частот 2Г NMOW - NM,,H + l с шагом jПри этом с уменьшением шага сетки синтезируемых частот путем увеличеПИЯ рачрял.И|1Стп fnHCTponeiicTuiio tJyjj.oT истлиаться прежним, пока с оОлкутается условие К L + 3, поскольку быстродействие установки частоты при изменении коэффициента N составляет, как минимум, несколько периодов (до десяти) частоты на выходе ДФКД 7 или при L+ 3

мерно А периодов опорной частоты

f . Т.е. допускается увеличение коли

чества синтезируемых частот в 2 раза при сохранении быстродействия

без изменения диапазона. Поскольку

„н + и 5

величина 2 может составлять несколько порядков, то возможно повысить быстродействие, увеличив частот сравнения на втором входе фазового детектора 4 путем уменьшения коэффициента деления ДФКД .7, Шаг сетки частот остается равным . Таким образом удается получить значительно увеличение количества синтезируемых частот при повьпиении быстродействия.

Поскольку максимальное значение , частоты .,„ может превосходить значеk.v

ние частоты на выходе ДФКД 7, то значения синтезируем Ь1х частот при смеж- ньпх значениях коэффициентов деления ДПКД 3 могут перекрываться и при это нарушается однозначное соответствие между кодом частоты Np, поступающим на вход датчика 8 кода, и выходной частотой цифрового синтезатора частоты. Кроме того, при наличии на младших К+М выходах да.тчика 8 кода нулевых состояний напряжение на выходе ЦАП 13 является постоянным и нормальная работа цифрового синтезатора частоты нарушается. Для исключения этих явлений и для обеспечения линейного и взаимно однозначного соответствия синтезируемой частоты входному коду частоты NP и исключения запретных комбинаций кодов частоты датчик 8 кода содержит буферный регистр 17, первый, и второй сумматоры 15 и 16, При этом на второй вход первого сумматора 15 поступает постоянное число N,, определяющее максимальное значение частоты , а на второй вход второго сумматора 16 поступает постоянное число N определяющее минимальный

МИН

коэффициент деления ДПКД 3. Выходы млад1иих К разрядов буферного регистра 17 .являются первой rpyniioii выходов датчика 8 кода, М выходо средних разрядов буферного региггрл 17 с (К+1)-го по (К+М)-й Г1(1.1ь ипчень к М младшим раз

рядам первого входа 1-ра рчдног (1 c.yMNtaTopa 15. При этом на 11-М старших разрядов первого входа пер- вого сумматора 15 подан код 00.,,01,

где

1 (М+1)-м разряде. Выходы перо

вого сумматора 15 являются Н-разряд- ным вторым выходом датчика 8 кода, причем выполняется соотношение ,

I

где 2 - коэффициент деления ДФКД 7. Второй сумматор 16 ос тцествляет суммирование числа с выхода старших разрядов (начиная с (K+M+I)-го) буферного регистра 17 с постоянным числом

5 N,,j и выходы второго сумматора 16 яв- ля ются третьим разрядным выходом датчика 8 кода.

Предположим, что код N равен нулю. Тогда при нулевом состоянии млад0 ших К+М разрядов буферного регистра 17 частота сигнала f(,д, на вы;:оде ЦАП

13 будет равна своему минимальному

„М

значению f „ о JiT где 2 5 вес сигнала логической единицы на о входе (М+1) второго сумматора 10. По мере увеличения значения кода на К+М младших разрядах буферного регистра 17 частота f., будет увеличиваться

сЛЛ

0 и, когда на входах первого и второго сумматоров 9, 10 будут присутствовать все единицы, достигает своего максимального значения

35

Разность между максимальным и минимальным значениями частоты f при

равна на величину шага сетки

If 4 М

частот fд/2 меньше частоты сравнения f. /2 на втором входе фазового детектора 4.

. Если теперь код частоты N увеличится , на единицу младшего разряда, то частота f., станет равной своему минимальному значению, а коэффициент деления ДПКД 3 увеличится на единицу, так как появится дополнительная единица на выходе второго сумматора 16, и выходная частота fg,, увеличится

ровно на величину шага сетки частот f,

55 При NQ О ч§стота f р будет изме- няться от значения „/2 до значения

L k 4-И

2f /2 fo Р больших значениях может оказаться достаточно низкой. Этот недостаток ус раняется при

5135

установке ненулевого значения кода N что сдвигает все частоты по выходу ЦМ1 13 (и выходные частоты цифрового синтезатора частоты) в сторону

увеличения на f -s .

Выходная частота при этом может быть записана в виде

- - fo Г |

-аь1к

,

Видцо, что код NQ позволяет в определенных пределах корректировать смщение краев диапазона синтезируемых

f./2 Гц.

частот с дискретностью

Максимальное значение чивается условием f.

/2

N

о ограни см Ала. И не должно превышать величины 2 - 1.

Таким образом, цифровой синтезатор частоты позволяет значительно увеличить количество синтезируемых частот путем уменьшения шага сетки частот при одновременном улучшении быстродействия путем повьш1ения частоты сравнения на фазовом детекторе. При этом не происходит ухудиения спектральных характеристик выходного сигнала.

Формула изобретения

1. Цифровой синтезатор частоты, содержащий последовательно соединенные опорный генератор, делитель час- тоты с фиксированным коэффициентом деления, фазовый детектор, фильтр нижних частот,перестраиваемый генератор, смеситель и делитель частоты с переменным коэффициентом деления, выход которого подключен к другому входу фазового детектора, первый сумматор кодов, последовательно соединенные второй сумматор кодов и первый регистр памяти, выход которого подключен к первому кодовому входу второго сумматора кодов, цифроанало- говый преобразователь и датчик кода частоты, первый разрядный выход кото Составител

Техред Л.С

Редактор А, Долинич

Заказ 5812/55Тираж 900Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул, Проектная,

6

25

Ю. Ковалев

рого соединен с первым разрядным входом первого сумматора кодов, отличающийся тем, что, с целью

.. уменьшения шага сетки синтезируемых о

частот при одновременном повышении

быстродействия, между выходом первого регистра памяти и входом цифроанало- гового преобразователя введен блок

0 постоянной памяти, а также введен

второй регистр памяти, разрядные вход и выход которого подключены соответственно к разрядному выходу и второму разрядному входу первого сумма5 тора кодов, выход цифроаналогового преобразователя соединен с вторым входом смесителя, тактовый вход первого регистра памяти объединен с тактовым входом второго регистра памяти

0 и подключен к выходу опорного гене- . ратора, второй разрядный вход второго сумматора соединен с вторым разрядным выходом датчика кода частоты, третий разрядный выход которого подключен к установочным входам делителя частоты с переменным коэффициентом деления, а выход переноса первого сумматора кодов соединен с входом заема второго сумматора кодов.

30 2. Синтезатор частоты по п.1, о т- личающийся тем, ч то датчик кода частоты содержит буферный регистр, первый и второй сумматоры кодов, при этом выходы младших К разря35 дов буферного регистра, кодовые выходы первого и второго сумматоров кодов являются соответственно первым, вторым и третьим разрядными выходами датчика кода частоты, выходы разрядов

40 буферного регистра с (К+1)-го по (К+М)-й подключены поразрядно к М младшим разрядам первой труппы входов первого сумматора кодов, (1+1)-й вход первой группы входов которого подклю42 чен к шине логической единицы, а

входы старших разрядов первой группы входов первого сумматора объединены и подключены к шине логического нуля, выходы старших разрядов буферного регистра подключены поразрядно к первой группе входов второго сумматора кодов;.

50

Корректор А, Зимокосов

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Частотный модулятор | 1989 |

|

SU1626320A1 |

| Синтезатор частот | 1985 |

|

SU1363457A1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1363458A1 |

| Цифровой синтезатор частот | 1989 |

|

SU1691926A1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| Цифровой синтезатор частот | 1990 |

|

SU1748251A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1172011A1 |

| Цифровой синтезатор частот | 1988 |

|

SU1566454A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

Изобретение относится к радиотехнике. Цель изобретения - уменьшение шага сетки синтезируемых частот при одновременном повышении быстродействия. Цифровой синтезатор частоты содержит кольцо фазовой автоподстройки, состоящее из перестраиваемого генератора 1, смесителя 2, делителя 3 частоты с переменным коэффициентом деления, фазового детектора 4 и фильтра 5 нижних частот, опорный генератор 6, делитель 7 частоты с фиксированным коэффициентом деления, датчик кода (ДК) 8 частоты, состоящий из сумматоров 15 и 16 кодов и буферного регистра 17, сумматоры 9 и 10 кодов, регистры 11 и 14 памяти, блок постоянной памяти (БПП) 12 и ЦАП 13. При изменении кодов отсчетов синусоиды на разрядных выходах ДК 8, поступающих на соответствующие . входы сумматоров 9 и 10, частота сигнала на выходе ЦАЦ 13 дискретно изменяется и кольцо фазовой автоподстройки синтезирует выходную частоту сигнала с заданным шагом сетки частот. Повышение быстродействия достигается за счет увеличения частоты сравнения на втором входе фазового детектора 4 путем уменьшения коэффициента деления делителя .7. Устр-во по п.1 ф-лы отличается введением БПП 12, в который записываются округленные до целого числа коды отсчетов синусоиды, и регистра 14, который совместно с сумматором 9 образует накапливающий сумматор. Устр-во по п.2 ф-лы отличается выполнением ДК 8. 1 3. п. ф-лы, 1 ил. , to (f сс СП о ю ю

| Синтезатор частот | 1982 |

|

SU1117839A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1172011A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-11-30—Публикация

1986-07-10—Подача