Изобретение относится к автомати- ке, вычислительной технике и может быть использовано для ввода информации в различных устройствах, в частности в персональных и микроЭВМ, где по алгоритму работы частот требует- ся многократная выдача кода любого символао

Цель изобретения - повышение быстродействия за счет организации автоматического многократного режима ввода

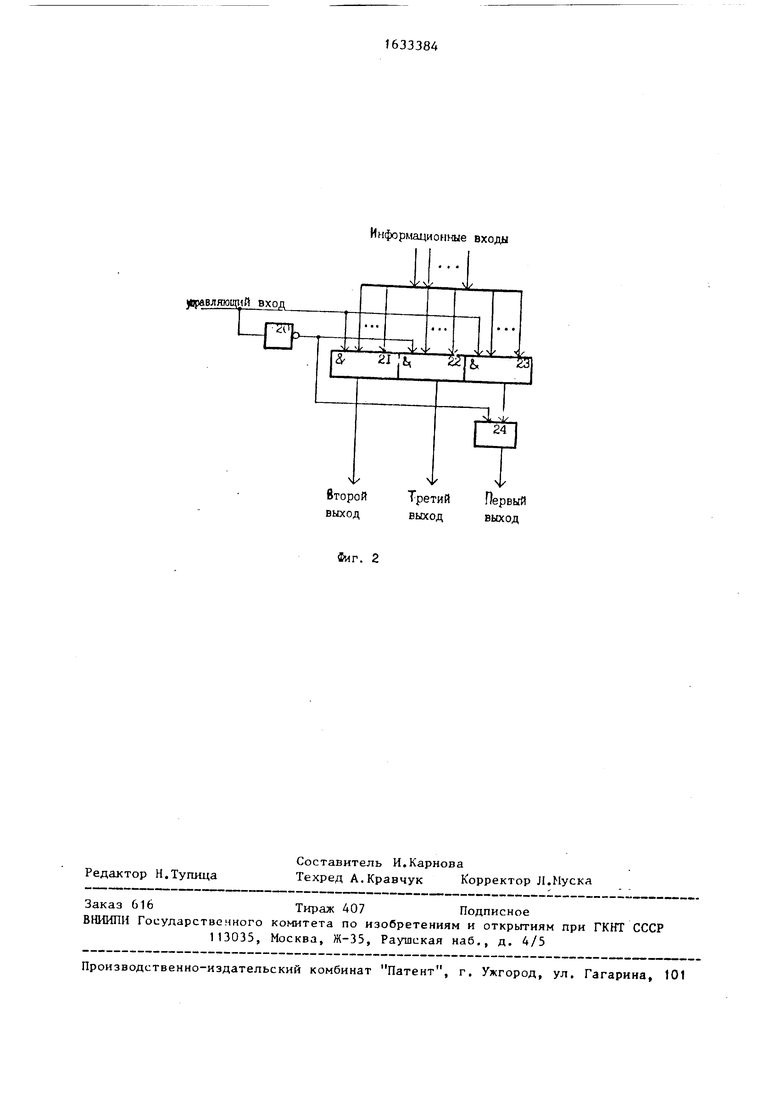

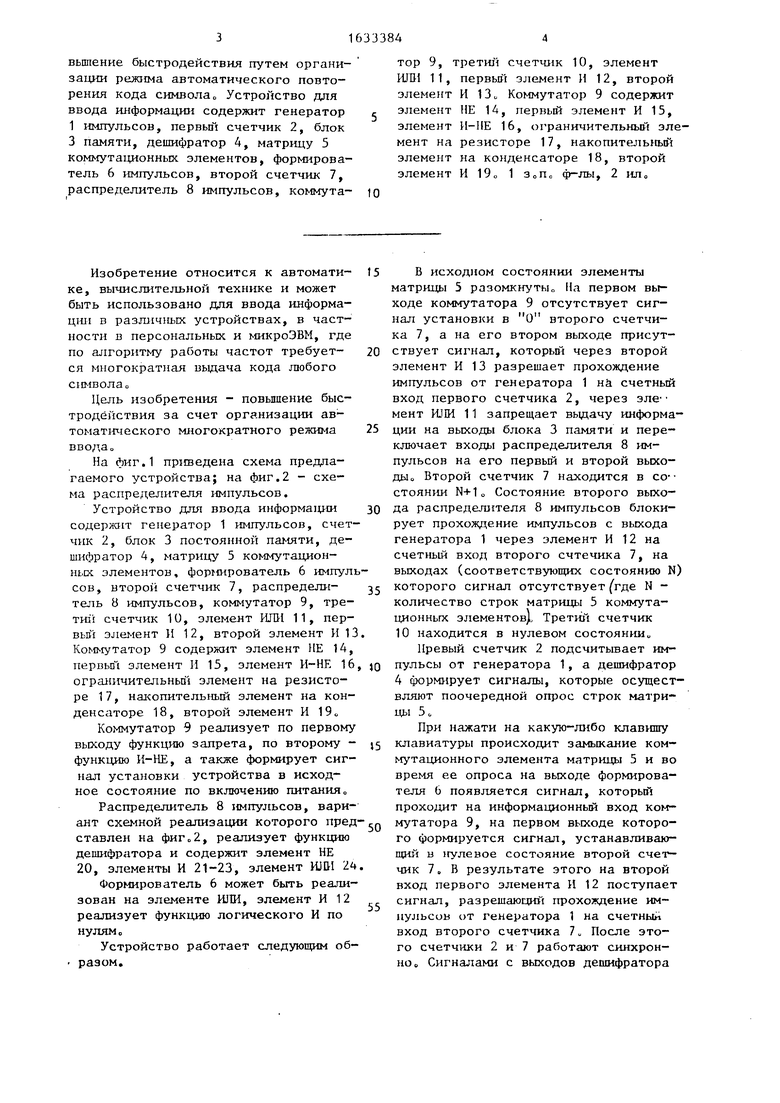

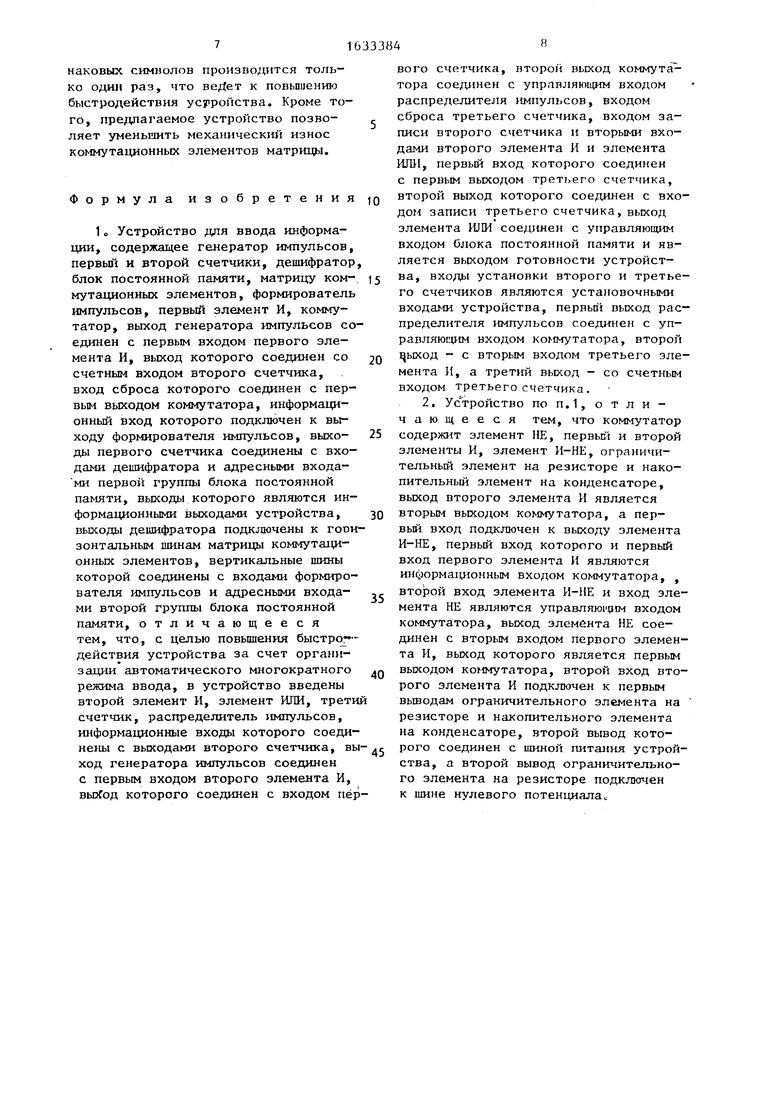

На фиг.1 приведена схема предлагаемого устройства; на фиг.2 - схема распределителя импульсов.

Устройство для ввода информации содержит генератор 1 импульсов, счетчик 2, блок 3 постоянной памяти, дешифратор 4, матрицу 5 коммутационных элементов, формирователь 6 импульсов, второй счетчик 7, распредели- тель 8 импульсов, коммутатор 9, третий счетчик 10, элемент ИЛИ 11, первый элемент И 12, второй элемент И 13 Коммутатор 9 содержит элемент НЕ 14, первый элемент И 15, элемент И-НЕ 16 ограничительный элемент на резисторе 17, накопительный элемент на конденсаторе 18, второй элемент И 19„

Коммутатор 9 реализует по первому выходу функцию запрета, по второму - функцию И-НЕ, а также формирует сигнал установки устройства в исходное состояние по включению питания

Распределитель 8 импульсов, вариант схемной реализации которого пред ставлен на фиг02, реализует функцию дешифратора и содержит элемент НЕ 20, элементы И 21-23, элемент ИЛИ 2 Формирователь 6 может быть реализован на элементе ИЛИ, элемент И 12 реализует функцию логического И по нулямо

Устройство работает следующим об- разом.

5 0

5

0 5

5

0

5

В исходном состоянии элементы матрицы 5 разомкнуты,, На первом выходе коммутатора 9 отсутствует сигнал установки в О второго счетчика 7, а на его втором выходе присутствует сигнал, который через второй элемент И 13 разрешает прохождение импульсов от генератора 1 на счетный вход первого счетчика 2, через эле- мент ИЛИ 11 запрещает выдачу информации на выходы блока 3 памяти и переключает входы распределителя 8 импульсов на его первый и второй выхо- ды0 Второй счетчик 7 находится в состоянии N+10 Состояние второго выхода распределителя 8 импульсов блокирует прохождение импульсов с выхода генератора 1 через элемент И 12 на счетный вход второго счтечика 7, на выходах (соответствующих состоянию N) которого сигнал отсутствует где N - количество строк матрицы 5 коммутационных элементов), Третий счетчик 10 находится в нулевом состоянии„

Превый счетчик 2 подсчитывает импульсы от генератора 1, а дешифратор 4 формирует сигналы, которые осуществляют поочередной опрос строк матрицы 5 о

При нажата на какую-либо клавишу клавиатуры происходит замыкание коммутационного элемента матрицы 5 и во время ее опроса на выходе формирователя Ь появляется сигнал, который проходит на информационный вход коммутатора 9, на первом выходе которого формируется сигнал, устанавливающий Б нулевое состояние второй счетчик 7„ В результате этого на второй вход первого элемента И 12 поступает сигнал, разрешающий прохождение импульсов от генератора 1 на счетнып вход второго счетчика 7„ После этого счетчики 2 и 7 работают синхронно,, Сигналами с выходов дешифратора

5И

4 продолжается опрос строк матрицы 5. Через N периодов работы генератора 1 сигналом с выхода дешифратора 4 вновь опрашивается строка с замкнутым коммутациоиным элементом, а на выходах второго счетчика 7, соответ- ствуюцих состоянию N,появляется сигнал, который по первому выходу распределителя 8 импульсов поступает на управляющий вход коммутатора 9„ Сигнал с выхода формирователя 6 проходит на второй выход коммутатора 9, через элемент И 13 запрещает работу первого счетчика 2, через элемент ИЛИ 1 1 разрешает выдачу информации на выходы блока 31 постоянной памяти, переключает входы распределителя 8 на его третий выход, а на втором выходе устанавливает сигнал Лог00, разрешающий прохождение импульсов от генератора 1 через элемент И 12 вне зависимости от состояния на информационных входах распределителя 8„

На первые адресные входы блока 3 постоянной памяти поступают сигналы с выхода счетчика 2, соответствующие номеру строки матрицы 5, а на вторые адресные входы блока 3 - сигнал с матрицы 5, соответствующий столбцу, На выходе блока 3 формируется информационный код, соответствуюций нажатой клавише о

Счетчик 7 работает в режиме поп- ного цикла„ Через определенное количество - Q тактов его работы, дешифратором числа которых является второй элемент И 22 распределителя 8, на третьем выходе распределителя 8 формируются импульсы, поступающие на счетный вход счетчика 10. Через К тактов работы счетчика 10 на его выходе формируется сигнал, запрещающий выдачу информации на выходм блока 3„ Через М тактов работы счетчика 10 на его выходе формируется сигнал, поступающий на его же установочньш вхоп Иь фронтом записывающий в счетчик 1C число L L - К При этом разрешается выдача информации на выход}, блока 3„ Счетчик 10 продолжает счет с начальной установкой чиспа L. Цикл работы устройства повторяется.

Таким образом, на выходе устройства периодически формируется информационный код замкнутого коммутационного элемента матрицы 5.

5

33846

Числа K,M,L,Q выбираются такими, чтобы обеспечить ожидание размыкания коммутационного элемента матрицы 5 на достаточно длительный промежуток времени (например, 0,5 с), а затем периодическую выдачу информации на выходе устройства через более кие промежутки времени (например, 0,1с) jg При отпускании клавиши происходит размыкание коммутационного элемента матрицы 5 и прекращается выдача формирователем b сигнала„ При этом сигнал с второго выхода коммутатора 9 5 запрещает выдачу информации на выходы блока 3, разрешает работу счетчика 2, сбрасывает счетчик 10 и фронтом производит начальную установку счетчика 7 в состояние1 N+1. Информа- 20 ционные входы распределителя 8 импульсов переключаются на первый и второй выходы,, Начинается поочередной опрос строк матрицы 5. Устройство переходит в исходное положение„ 5 Однократный ввод кода реализуется при нажатии клавиши на время, меньшее числа М тактов работы счетчика 10 (так как после набора счетчиком 10 числа М производится повторное 0 разрешение выдачи кода коммутационного элемента матрицы 5) При этом на выходе элемента 11Лн 11 будет сформирован только один сигнал считывания информациио Разрядность счетчика 7 выбирается исходя из количества N строк матрицы 5 и должна обеспечивать счет до числа не менее N-Н.При этом 4H-.no Q может быть любым числом, реализуемым счетчиком 7, но для умень- Q шения разрядности счетчика 10 оно долг жно быть максимально возможным

Числа N+1 и L коммутируются заранее на информационных входах счетчиков 7 и 10 соответственно„ Входы эле- 5 ментов И 21-23 подключены к информа- ционным входам распределителя 8 для дешифрации следую/них чисел: на элементе И 21 -чиста N+1 , на эаементе И 22 - числа Q, нл элементе И 0 числа Н„

Таким о&разом, предлагаемое устройство почполлет организовать режим автоматического повторения кода символа, т,е„ формирования группы, 5 состояией из одинаковых информационных символов, одноразовым нажатием коммутационного элемента,, При этом повторный опрос нажатого коммутационного элемента для всей группы оди-

5

маковых символов производится только один раз, что к повышению быстродействия устройства. Кроме того, предлагаемое устройство позволяет уменьшить механический износ коммутационных элементов матрицы.

Формула изобретения

1 о Устройство для ввода информации, содержащее генератор импульсов, первый и второй счетчики, дешифратор, блок постоянной памяти, матрицу ком- мутационных элементов, формирователь импульсов, первый элемент И, коммутатор, выход генератора импульсов соединен с первым входом первого элемента И, выход которого соединен со счетным входом второго счетчика, вход сброса которого соединен с первым выходом коммутатора, информационный вход которого подключен к выходу формирователя импульсов, выхо- ды первого счетчика соединены с входами дешифратора и адресными входа- ми первой группы блока постоянной памяти, выходы которого являются информационными выходами устройства, выходы дешифратора подключены к госи- зонтальным шинам матрицы коммутационных элементов, вертикальные шины которой соединены с входами формирователя импульсов и адресными входа- ми второй группы блока постоянной памяти, отличающееся тем, что, с целью повышения быстрсг -- действия устройства за счет организации автоматического многократного режима ввода, в устройство введены второй элемент И, элемент ИЛИ, третий счетчик, распределитель импульсов, информационные входы которого соединены с выходами второго счетчика, вы ход генератора импульсов соединен с первым входом второго элемента И, которого соединен с входом первого счетчика, второй выход коммутатора соединен с управляющим входом распределителя импульсов, входом сброса третьего счетчика, входом записи второго счетчика и вторыми входами второго элемента И и элемента ИЛИ, первый вход которого соединен с первым выходом третьего счетчика, второй выход которого соединен с входом записи третьего счетчика, выход элемента ИЛИ соединен с управляющим входом блока постоянной памяти и является выходом готовности устройства, входы установки второго и третьего счетчиков являются установочными входами устройства, первый выход распределителя импульсов соединен с управляющим входом коммутатора, второй ыход - с вторым входом третьего элемента И, а третий выход - со счетным входом третьего счетчика.

2. Устройство по п.1, о т л и - чающееся тем, что коммутатор содержит элемент НЕ, первый и второй элементы И, элемент И-НЕ, ограничительный элемент на резисторе и накопительный элемент на конденсаторе, выход второго элемента И является вторым выходом коммутатора, а первый вход подключен к выходу элемента И-НЕ, первый вход которого и первый вход первого элемента И являются информационным входом коммутатора, , второй вход элемента И-НЕ и вход элемента НЕ являются управлякнцим входом коммутатора, выход элемента НЕ соединен с вторым входом первого элемента И, выход которого является первым выходом коммутатора, второй вход второго элемента И подключен к первым выводам ограничительного элемента на резисторе и накопительного элемента на конденсаторе, второй вывод которого соединен с шиной питания устройства, а второй вывод ограничительного элемента на резисторе подключен к шине нулевого потенциала

Информационные входы

| название | год | авторы | номер документа |

|---|---|---|---|

| Оптоэлектронное устройство ввода информации | 1987 |

|

SU1501022A1 |

| Устройство для ввода информации | 1983 |

|

SU1173403A1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1988 |

|

SU1571594A1 |

| МОДУЛЬ ДЛЯ РЕТРАНСЛЯЦИИ СООБЩЕНИЙ В КОММУТАЦИОННОЙ СТРУКТУРЕ | 2002 |

|

RU2222044C2 |

| Устройство для записи информации в оперативную память | 1986 |

|

SU1322371A1 |

| Устройство для проверки электрического монтажа | 1986 |

|

SU1336035A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| Устройство для диспетчерской дуплексной связи | 1985 |

|

SU1293853A1 |

Изобретение относится к автома- тике, вычислительной технике и может быть использовано для ввода информации в различных устройствах, в частности в персональных и микроЭВМ, где по алгоритму работы частот требуется многократная выдача кода любого символа. Целью изобретения является no

второйТретий Первый

выходвыходвыход

Фиг. 2

| Устройство для ввода информации | 1985 |

|

SU1246085A1 |

Авторы

Даты

1991-03-07—Публикация

1989-04-25—Подача