«1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении цифровых вычислительных машин и контроллеров периферийных устройств.

Целью изобретения является повышение быстродействия в режиме ветвления микропрограммы по внешним логическим условиям.

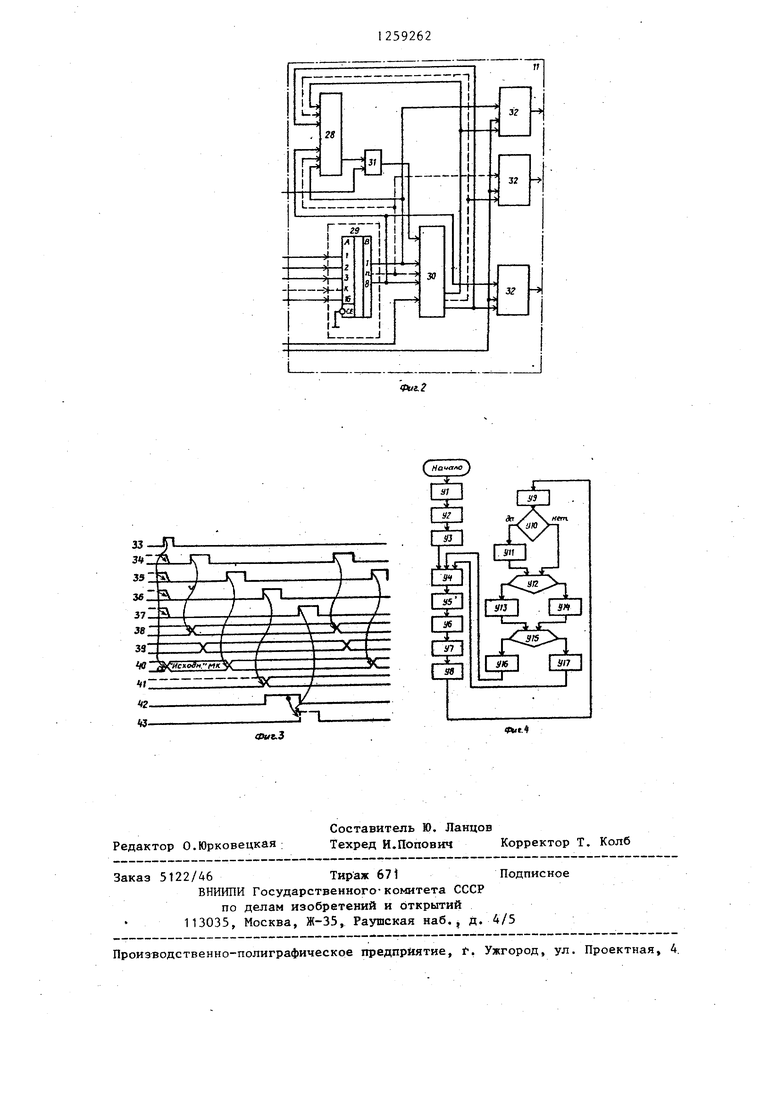

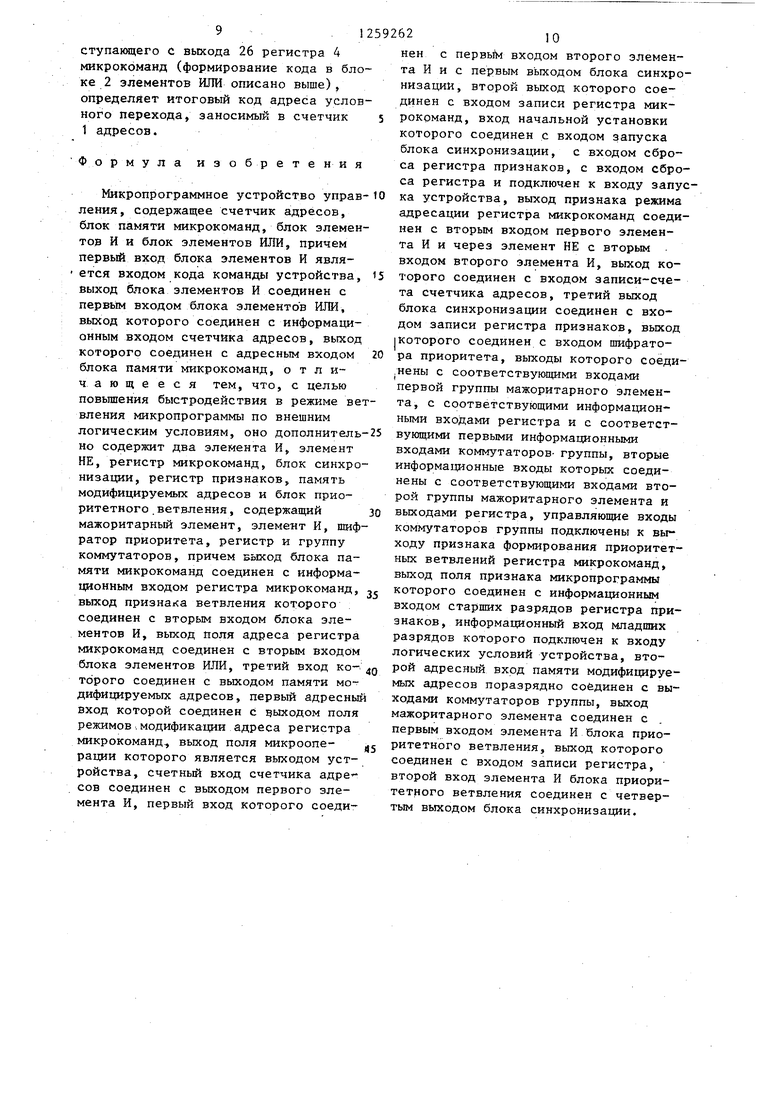

На фиг. 1 представлена структурна схема микропрограммного устройства управления; на фиг. 2 - функциональная схема блока приоритетного ветвления; на фиг. 3 - временная диаграмма функционирования устройства; на фиг. 4 - алгоритм функционирования.

Устройство (фиг. 1) содержит счетчик 1 адресов, блок 2 элементов ИЛИ, блок 3 элементов И, регистр 4 микрокоманд, блок 5 памяти микрокоманд, регистр 6 признаков, блок 7 синхронизации, злемент НЕ 8,, первый 9 и втрой 10 элементы И, блок 11 приоритетного ветвления, память 12 модифицируемых адресов, вход 13 кода команды, первый 14, второй 15, третий 16 и четвертый 17 выходы блока синхронизации, вход 18 логических условий, вход 19 запуска, выход 20 поля режимов модификации адреса регистра микрокоманд, выход 21 признака формирования приоритетных ветвлений регистра микрокоманд, выход 22 поля режимов модификации адреса регистра микрокоманд, выход 23 признака режимов адресации регистра микрокоманд, выход 24 поля микрооперации регистра микрокоманд, выход 25 признака ветвления регистра микрокоманд, выход 26 поля адреса и выход 2 7.

Блок 11 приоритетного ветвления (фиг. 2) содержит мажоритарньй элемент 28, шифратор 29 приоритета, регистр 30J злемент И 31 .и группу коммутаторов 32.

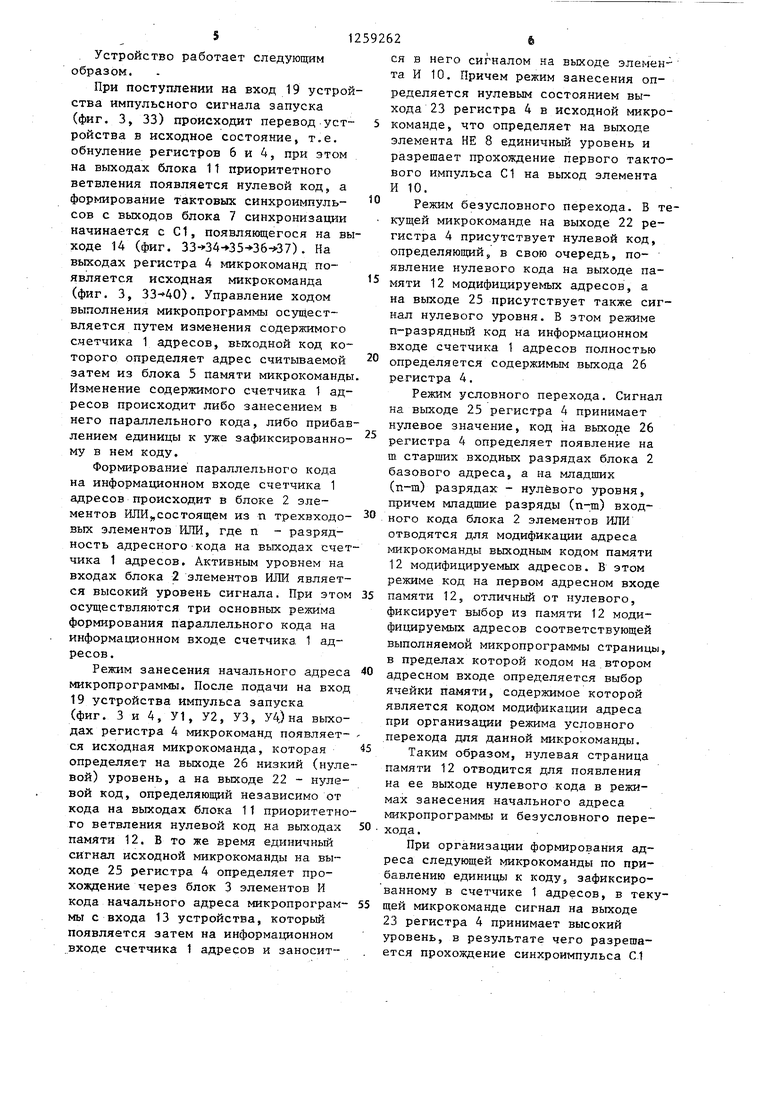

На временной диаграмме (фиг. 3) функционирования микропрограммного устройства управления обозначены: 33 - импульсный сигнал запуска (сигнал перевода устройства в исходное состояние); 34 - первый тактовый син хроимпульс (С1) цикла выполнения микрокоманды (соответствует сигналу на выходе 14 блока 7 синхронизации); 35 - второй тактовый синхроимпульс (С2) (соответствует сигналу на выходе 15 блока 7 синхронизаци 36

0

15

20

25

третий тактовый синхроимпульс (СЗ) (соответствует сигналу на выходе 16 блока 7 синхронизации); 37 - четвертый тактовый синхроимпульс (С4) (соответствует сигналу на выходе 17 блока 7 синхронизации); 38 - состояния выходов счетчика 1 адресов; 39 - состояния выходов блока 5 памяти микропрограмм; 40 - состояния выходов регистра 4 микрокоманд; 41 - состояния выходов регистра 6 признаков; 42 - процедура в мажоритарном элементе 28; 43 - занесение в регистр 30 нового кода ветвления (происходит, когда код на одних входах мажоритарного элемента 28 превьшает код на других его входах).

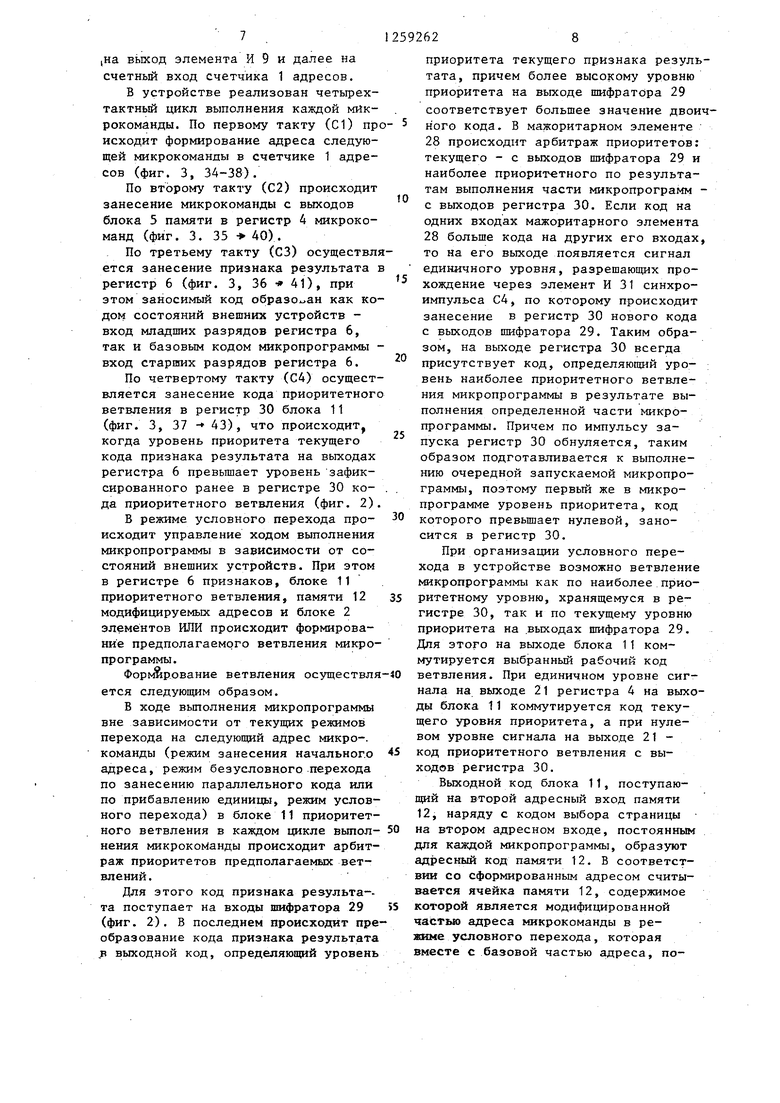

На алгоритмической схеме функционирования устройства (фиг. 4) обозначены: У1 - сигнал перевода устройства в исходное состояние, поступающий на его вход 19; У2 - установка на выходе регистра 4 микрокоманд исходной микрокоманды; УЗ - разрешение прохождения через блок 3 элементов И кода начального адреса микропрограммы (кода команды); У4 - занесение в счетчик 1 адресов кода начального адреса микропрограммы по С1; У5 - считывание микрокоманды с выходов блока 5 памяти микрокоманд; У6 - занесение микрокоманды в регистр 4 микрокоманд по С2; У7 - появление на выходе 27 устройства (с йыхода 24 регистра 4) кода, поступающего на внешнее устройство; У8 - занесение кода внешних условий в регистр 6 признаков по СЗ; У9 - процедура арбитража приоритетов в мажоритарном элементе 28; У10 - приоритет признака результата вьшхеза- фиксированного в регистре 30; У11 - занесение нового кода приоритетного ветвления в регистр 30; У12 - пере45 ход к следующей микрокоманде в зависимости от содержимого соответствующего поля текущей микрокоманды; У13 - появление на выходе блока приоритетного ветвления микро50 программы; У14 - появление на выходе блока 11 кода ветвления по текущему признаку результата; У15 - формирование на входах элементов И 9 и 10 режима перехода к следую55 щему адресу микрокоманды (согласно содержимому выхода 23 регистра 4 микрокоманд);У16 - переход по прибавлению единицы к содержимому счет30

35

40

:

чика 1 адресов; У17 - переход по параллельному занесению кода в счетчик 1 адресов.

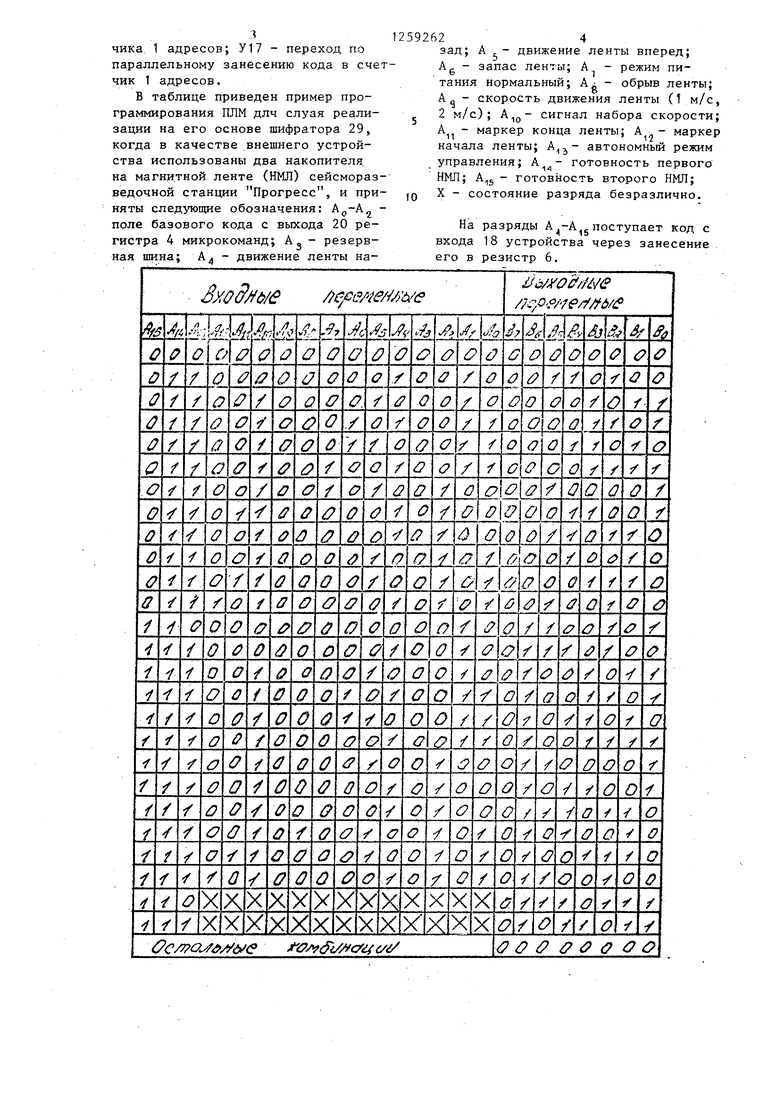

В таблиде приведен пример программирования ПЛМ длч слуая реали- задии на его основе шифратора 29, когда в качестве внешнего устройства использованы два накопителя, на магнитной ленте (НМЛ) сейсмораз- ведочной станции Прогресс, и приняты следующие обозначения: - поле базового кода с выхода 20 регистра 4 микрокоманд; А - резервная шина; А - движение ленты на624

зад; А - движение ленты вперед; Ag - запас ленты; А - режим питания нормальный; А - обрыв ленты; А„ - скорость движения ленты ( м/с, 2 м/с); сигнал набора скорости; К - маркер конда ленты; А . - маркер начала ленты; автономный режим управления; готовность первого НМЛ; - готовность второго НМЛ; X - состояние разряда безразлично.

На разряды А -А поступает код с входа 18 устройства через занесение его в резистр 6.

51

Устройство работает следующим образом.

При поступлении на вход 19 устройства импульсного сигнала запуска (фиг. 3, 33) происходит перевод устройства в исходное состояние, т.е. обнуление регистров 6 и 4, при этом на выходах блока 11 приоритетного ветвления появляется нулевой код, а формирование тактовых синхроимпульсов с выходов блока 7 синхронизации начинается с С1, появляющегося на выходе 14 (фиг. ). На выходах регистра 4 микрокоманд появляется исходная микрокоманда (фиг. 3, ). Управление ходом выполнения микропрограммы осуществляется путем изменения содержимого счетчика 1 адресов, выходной код которого определяет адрес считываемой затем из блока 5 памяти микрокоманды Изменение содержимого счетчика 1 адресов происходит либо занесением в него параллельного кода, либо прибалением единицы к уже зафиксированному в нем коду,

Формирование параллельного кода на информационном входе счетчика 1 адресов происходит в блоке 2 элементов ИЛИ состоящем из п трехвходо вых элементов ИЛИ, где п - разрядность адресного кода на выходах счечика 1 адресов. Активным уровнем на входах блока 2 элементов ИЛИ является высокий уровень сигнала. При это осуществляются три основных режима формирования параллельного кода на информационном входе счетчика 1 адресов.

Режим занесения начального адрес микропрограммы. После подачи на вхо 19 устройства импульса запуска (фиг. 3 и 4, У1, У2, УЗ, У4,)на выходах регистра 4 микрокоманд появляется исходная микрокоманда, которая определяет на выходе 26 низкий (нулвой) уровень, а на выходе 22 - нулевой код, определяющий независимо от кода на выходах блока 11 приоритетнго ветвления нулевой код на выходах памяти 12. В то же время единичный сигнал исходной микрокоманды на выходе 25 регистра 4 определяет прохождение через блок 3 элементов И кода начального адреса микропрограммы с входа 13 устройства, которьй появляется затем на информационном входе счетчика 1 адресов и заносит

ся в него сигналом на выходе элемен- та И 10. Причем режим занесения определяется нулевым состоянием выхода 23 регистра 4 в исходной микрокоманде, что определяет на выходе элемента НЕ 8 единичный уровень и разрешает прохождение первого тактового импульса С1 на выход элемента И 10.

Режим безусловного перехода. В те- к-ущей микрокоманде на выходе 22 регистра 4 присутствует нулевой код, определяющий, в свою очередь, появление нулевого кода на выходе па- мяти 12 модифицируемых адресов, а на выходе 25 присутствует также сигнал нулевого уровня. В этом режиме п-разрядный код на информационном входе счетчика 1 адресов полностью определяется содержимым выхода 26 регистра 4.

Режим условного перехода. Сигнал на выходе 25 регистра 4 принимает нулевое значение, код на выходе 26 регистра 4 определяет появление на m старших входных разрядах блока 2 базового адреса, а на младших (n-m) разрядах - нулевого уровня, причем младшие разряды (п-т) входного кода блока 2 элементов ИЛИ отводятся для модификации адреса микрокоманды выходным кодом памяти 12 модифицируемых адресов. В этом режиме код на первом адресном входе памяти 12, отличный от нулевого, фиксирует выбор из памяти 12 модифицируемых адресов соответствующей выполняемой микропрограммы страницы, в пределах которой кодом на втором адресном входе определяется выбор ячейки памяти, содержимое которой является кодом модификации адреса при организации режима условного .перехода для данной микрокоманды.

Таким образом, нулевая страница памяти 12 отводится для появления на ее выходе нулевого кода в режимах занесения начального адреса микропрограммы и безусловного перехода .

При организации формирования адреса следующей микрокоманды по прибавлению единии1Ы к коду, зафиксированному в счетчике 1 адресов, в текущей микрокоманде сигнал на выходе 23 регистра 4 принимает высокий уровень, в результате чего разрешается прохождение синхроимпульса С1

,на вькод элемента И 9 и далее на счетный вход счетчика 1 адресов.

В устройстве реализован четырехтактный цикл выполнения каждой микрокоманды. По первому такту (С1) про исходит формирование адреса следующей микрокоманды в счетчике 1 адресов (фиг. 3, 34-38).

По второму такту (С2) происходит занесение микрокоманды с выходов блока 5 памяти в регистр 4 микрокоманд (фиг. 3. 35 40).

По третьему такту (СЗ) осуществля ется занесение признака результата в регистр 6 (фиг. 3, 36 41), при этом заносимый код образован как кодом состояний внешних устройств - вход младших разрядов регистра 6, так и базовым кодом микропрограммы - вход старших разрядов регистра 6.

По четвертому такту (С4) осуществляется занесение кода приоритетного ветвления в регистр 30 блока 11 (фиг. 3, 37 - 43), что происходит, когда уровень приоритета текущего кода признака результата на выходах регистра 6 превышает уровень зафиксированного ранее в регистре 30 кода приоритетного ветвления (фиг. 2).

В режиме условного перехода происходит управление ходом выполнения микропрограммы в зависимости от состояний внешних устройств. При этом в регистре 6 признаков, блоке 11 приоритетного ветвления, памяти 12 модифицируемых адресов и блоке 2 элементов ИЛИ происходит формирование предполагаемого ветвления микропрограммы.

Формирование ветвления осуществля ется следующим образом.

Б ходе выполнения микропрограммы вне зависимости от текущих режимов перехода на следующий адрес микро-, команды (режим занесения начального адреса, режим безусловного перехода по занесению параллельного кода или по прибавлению единицы, режим условного перехода) в блоке 11 приоритетного ветвления в каждом цикле выпол- нения микрокоманды происходит арбитраж приоритетов предполагаемых ветвлений.

Для этого код признака результа-- та поступает на входы шифратора 29 (фиг. 2). В последнем происходит преобразование кода признака результата в выходной код, определяющий уровень

to

5

0

5

5

5

0

приоритета текущего признака результата, причем более высокому уровню приоритета на выходе шифратора 29 соответствует большее значение двоичного кода. В мажоритарном элементе 28 происходит арбитраж приоритетов: текущего - с выходов шифратора 29 и наиболее приоритетного по результатам выполнения части микропрограмм - с выходов регистра 30. Если код на одних входах мажоритарного элемента 28 больше кода на других его входах, то на его выходе появляется сигнал единичного уровня, разрешающих прохождение через элемент И 31 синхроимпульса С4, по которому происходит занесение в регистр 30 нового кода с выходов шифратора 29. Таким образом, на выходе регистра 30 всегда присутствует код, определяющий уровень наиболее приоритетного ветвления микропрограммы в результате выполнения определенной части микропрограммы. Причем по иг гпульсу запуска регистр 30 обнуляется, таким образом подготавливается к выполнению очередной запускаемой микропрограммы, поэтому первый же в микропрограмме уровень приоритета, код которого превьш1ает нулевой, заносится в регистр 30.

При организации условного перехода в устройстве возможно ветвление микропрограммы как по наиболее приоритетному уровню, хранящемуся в регистре 30, так и по текущему уровню приоритета на выходах шифратора 29. Для этого на выходе блока 11 коммутируется выбранный рабочий код ветвления. При единичном уровне сигнала на выходе 21 регистра 4 на выходы блока 11 коммутируется код текущего уровня приоритета, а при нулевом уровне сигнала на выходе 21 - код приоритетного ветвления с выходов регистра 30.

Выходной код блока 11, поступающий на второй адресный вход памяти 12, наряду с кодом выбора страницы на втором адресном входе, постоянным для каждой микропрограммы, образуют адресный код памяти 12. В соответствии со сформированным адресом считывается ячейка памяти 12, содержимое которой является модифицированной частью адреса микрокоманды в режиме условного перехода, которая вместе с базовой частью адреса, поступаимцего с выхода 26 регистра 4 микрокоманд (формирование кода в блоке 2 элементов ИЛИ описано выше), определяет итоговый код адреса условного перехода, заносимый в счетчик 1 адресов.

Ф о рмула изо б р е т е и и я

Микропрограммное устройство управления, содержащее счетчик адресов, блок памяти микрокоманд, блок элементов И и блок элементов ИЛИ, причем первый вход блока элементов И является входом кода команды устройства, выход блока элементов И соединен с первым входом блока элементов ИЛИ, выход которого соединен с информационным входом счетчика адресов, выход которого соединен с адресным входом блока памяти микрокоманд, о т л и- чающе еся тем, что, с целью повышения быстродействия в режиме ветвления микропрограммы по внешним логическим условиям, оно дополнитель но содержит два элемента И, элемент НЕ, регистр микрокоманд, блок синхронизации, регистр признаков, память модифицируемых адресов и блок приоритетного .ветвления, содержащий мажоритарньй элемент, элемент И, шифратор приоритета, регистр и группу коммутаторов, причем выход блока памяти микрокоманд соединен с информационным входом регистра микрокоманд, выход признака ветвления которого соединен с вторым входом блока элементов И, выход поля адреса регистра микрокоманд соединен с вторым входс м блока элементов ИЛИ, третий вход ко- торого соединен с выходом памяти модифицируемых адресов, первый адресны вход которой соединен С выходом поля режимов.модификации адреса регистра микрокоманд, выход поля микроопе- рации которого является выходом устройства. Счетный вход счетчика адре сов соединен с выходом первого элемента И, первый вход которого соеди2

s

1О 5 20 25ЗОо

59262 нен та

10

с первый входом второго злемен- И и с первым в ыходом блока синхронизации, второй выход которого соединен с входом записи регистра микрокоманд, вход начальной установки которого соединен с входом запуска блока синхронизации, с входом сброса регистра признаков, с входом сброса регистра и подключен к входу запуска устройства, выход признака режима адресации регистра микрокоманд соединен с вторым входом первого элемента И и через элемент НЕ с вторьм входом второго элемента И, выход которого соединен с входом записи-счета счетчика адресов, третий выход блока синхронизации соединен с входом записи регистра признаков, выход iKoToporo соединен с входом шифратора приоритета, выходы которого соеди- .нены с соответствующими входами первой группы мажоритарного элемента, с соответствующими информационными входами регистра и с соответствующими первыми информационными входами коммутаторов- группы, вторые информационные входы которых соединены с соответствующими входами второй группы мажоритарного элемента и выходами регистра, управляющие входы коммутаторов группы подключены к выходу признака формирования приоритетных ветвлений регистра микрокоманд, выход поля признака микропрограммы которого соединен с информационным входом старших разрядов регистра признаков, информационный вход младших разрядов которого подключен к входу логических условий устройства, второй адресный вход памяти модифицируе мых адресов поразрядно соединен с выходами ко1 1мутаторов группы, выход мажоритарного элемента соединен с первым входом элемента И блока приоритетного ветвления, выход которого соединен с входом записи регистра, второй вход элемента И блока приоритетного ветвления соединен с четвертым выходом блока синхронизации.

33

ЭД .-мх Ш

чг.

Wcnve.3

.4

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Программируемый контроллер | 1990 |

|

SU1714599A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134936A1 |

| Устройство управления контролем | 1985 |

|

SU1285471A1 |

| Процессор | 1983 |

|

SU1213485A1 |

| Микропрограммное устройство управления | 1978 |

|

SU798838A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1179337A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении цифровых вычислительных машин и контроллеров периферийных устройств. Целью изобретения является повьппение быстродействия в режиме ветвления микропрограммы по внешним логическим условиям. Устройство содержит счетчик 1 адресов, блок 2 элементов ИЛИ, блок 3 элементов И, регистр 4 микрокоманд, блок 5 памяти микрокоманд, регистр 6 признаков, блок 7 синхронизации, элемент НЕ 8, два элемента И 9, 10, блок 11 приоритетного ветвления и памяти 12 модифицируемых адресов, входы и выходы устройства. 4 ил., 1 табл. о 0 (Л ю СП со JNO Од Ю

Редактор О.Юрковецкая;

Составитель Ю. Ланцов

Техред И.Попович Корректор Т. Колб

Заказ 5122/46Тираж 671Подписное

ВНИИПИ Государственного-комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4.

| Микропрограммное устройство управления | 1980 |

|

SU934473A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1179337A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-23—Публикация

1984-05-23—Подача