Изобретение относится к вычислительной технике и может быть использовано при построении процессоров ЭВМ и устройств обработки цифровой информации.

Цель изобретения - сокращение аппаратных затрат.

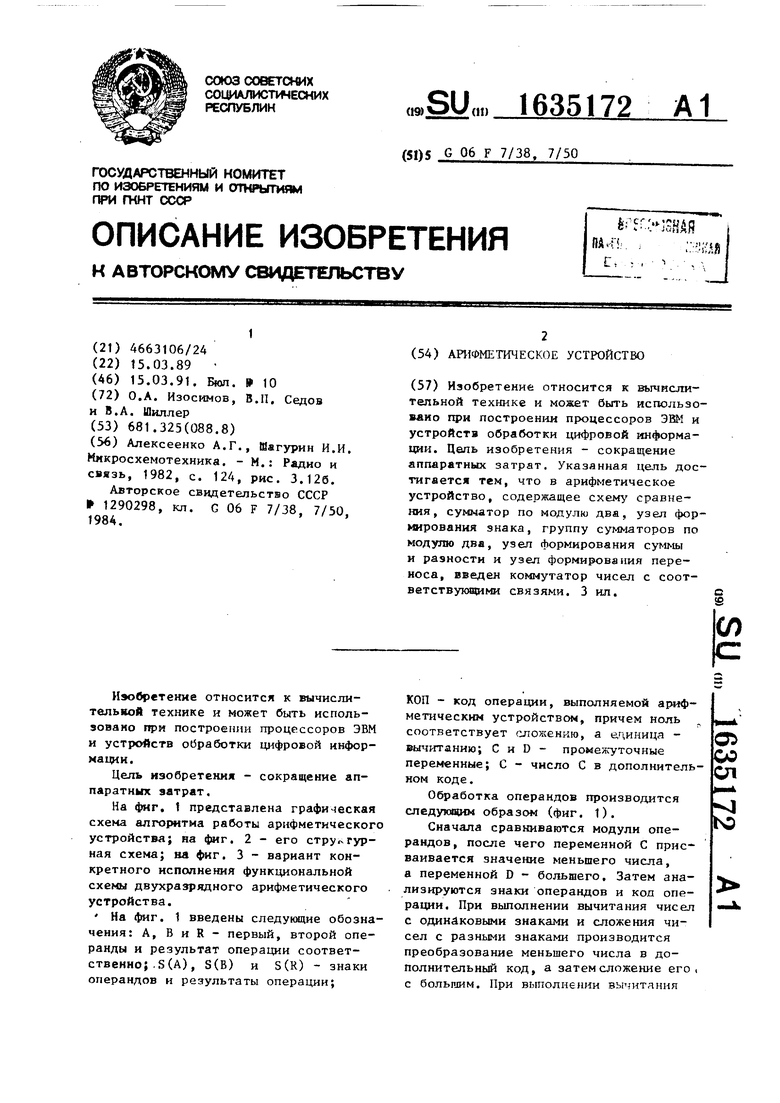

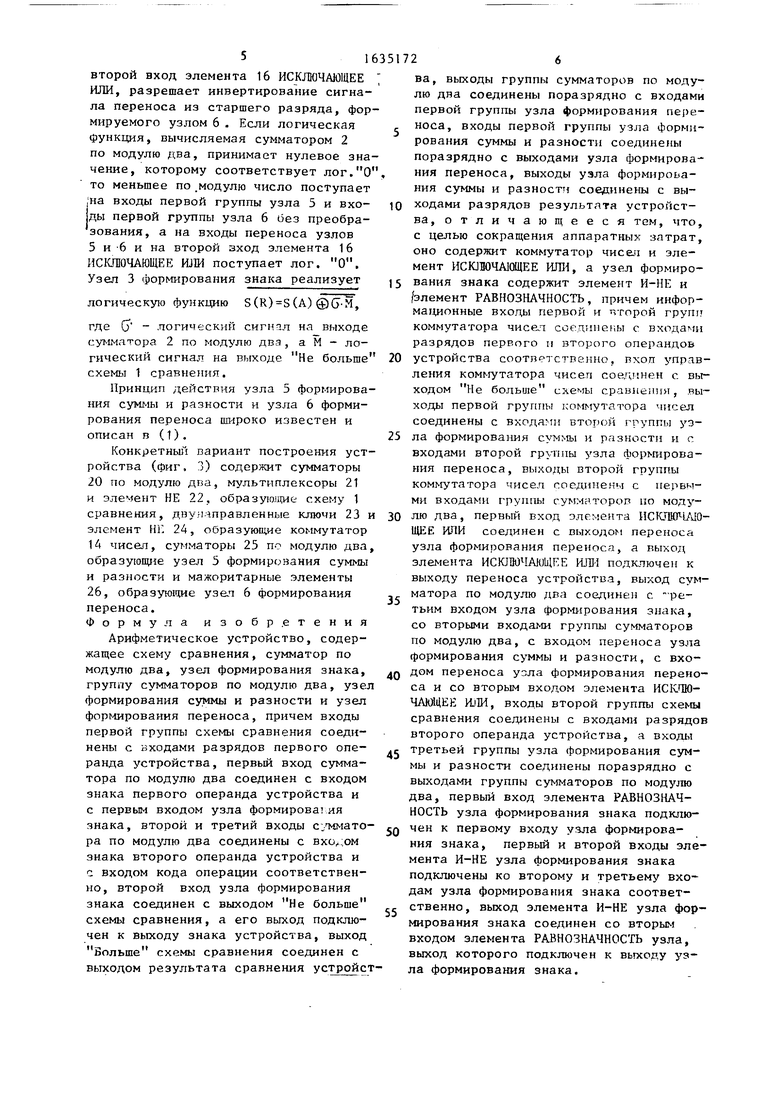

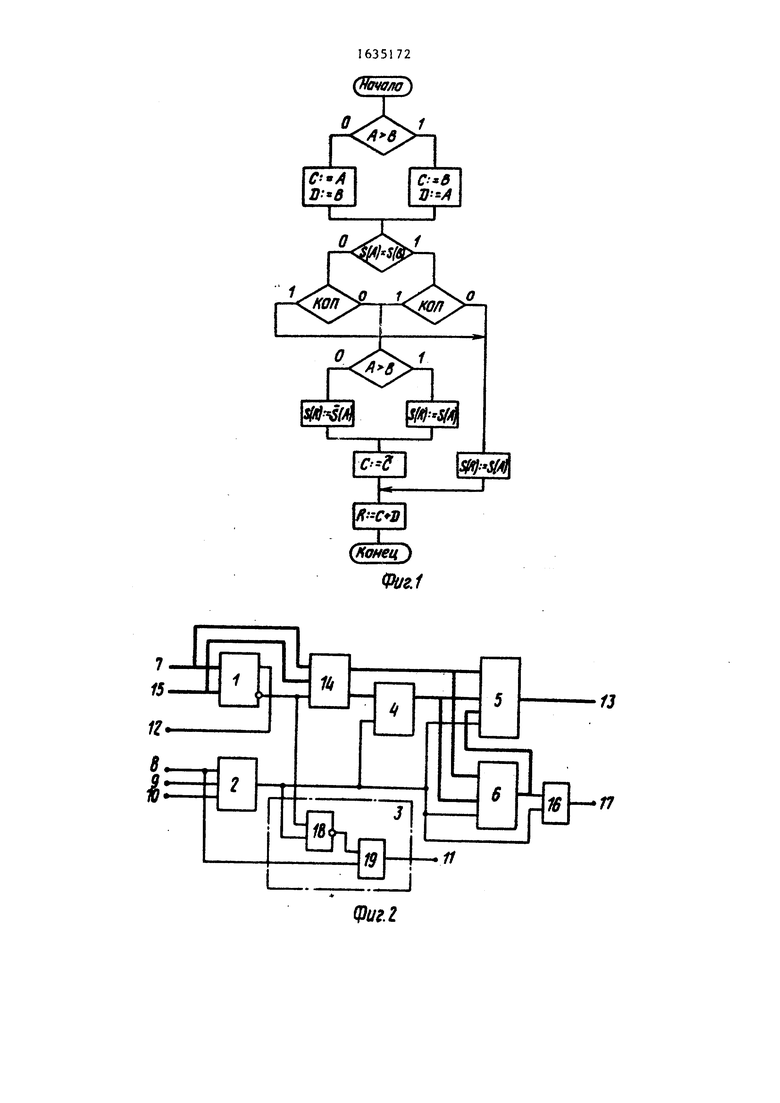

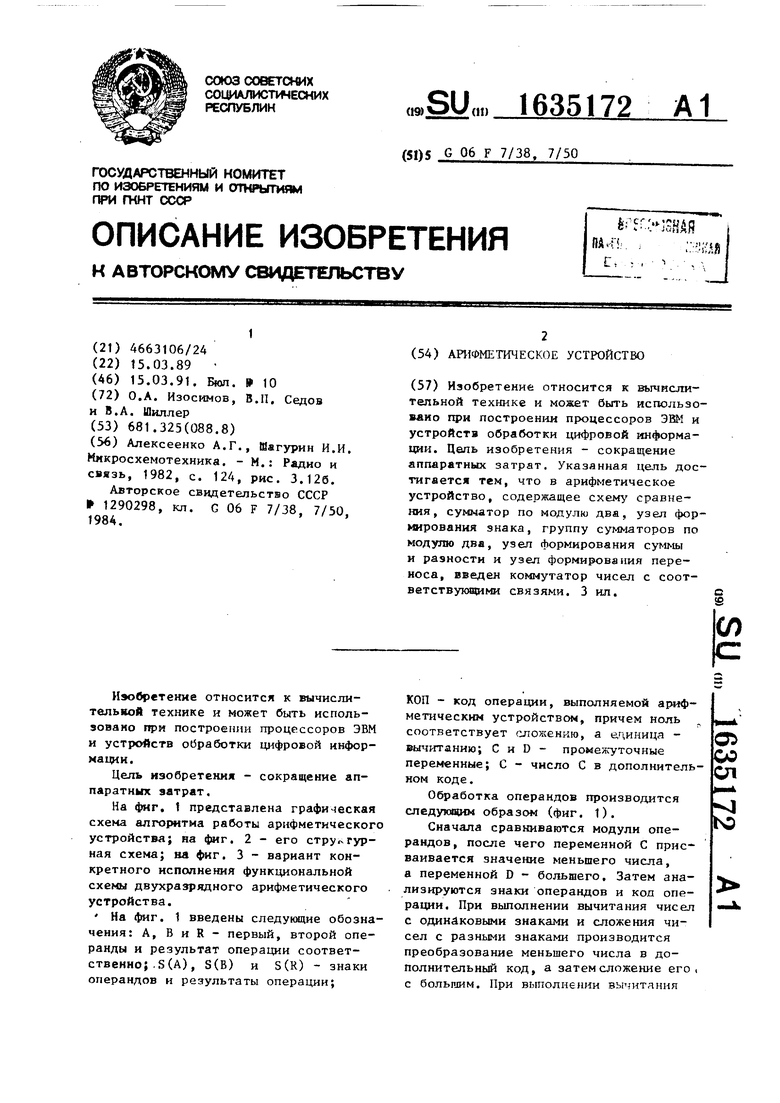

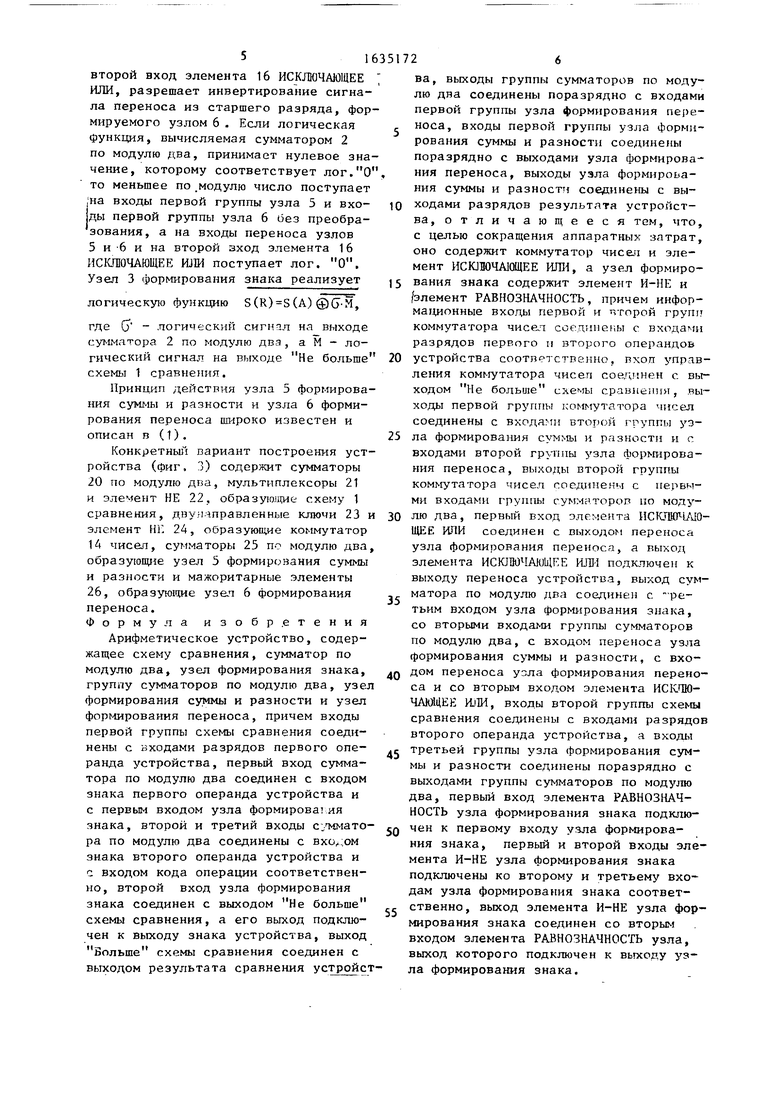

На фиг. t представлена графическая схема алгоритма работы арифметического устройства; на фиг. 2 - его ная схема; на фиг. 3 - вариант конкретного исполнения функциональной схемы двухразрядного арифметического устройства.

На фиг. 1 введены следующие обозначения: А, В и R - первый, второй операнды и результат операции соответственно; .S(А), S(B) и S(R) - знаки операндов и результаты операции;

КОП - код операции, выполняемой арифметическим устройством, причем ноль соответствует сложению, а единица - вычитанию; С и D - промежуточные переменные; С - число С в дополнительном коде.

Обработка операндов производится следующим образом (фиг. 1).

Сначала сравниваются модули операндов , после чего переменной С присваивается значение меньшего числа, а переменной D - большего. Затем анализируются знаки операндов и код операции. При выполнении вычитания чисел с одинаковыми знаками и сложения чисел с разными знаками производится преобразование меньшего числа в дополнительный код, а затем сложение его, с большим. При выполнении вычитания

О

со

СП

р

чисел с разными знаками и сложения чисел с одинаковыми знаками числа Складываются без преобразования. Результат операции всегда получается в прямом коде.

Арифметическое устройство (фиг.2) содержит схему 1 сравнения, сумматор 2 по модулю два, узел 3 формирования знака, группу 4 сумматоров по модулю два, узел 5,формирования суммы и разности и узел 6 формирования переноса, причем входы первой группы схемы 1 сравнения соединены с входами 7 разрядов первого операнда устройства, ктвый вход сумматора 1 по пяа соединен с входом В - / . а рпого перанда устройства а п .м чггодом узла 3 формирования ЗРЗК-, г торой и третий ячоды суммчтор. 1 по модт-тю

ДТЛ С СЛИЧ НП 1 Т-ь IT, М п цтяк г- - ро-

го оперзнлл /стргн стпя ч с 3 о лом 10 кода операции ас згветс гвешю, ,орой чо i ys.w S чю ,ния мика romit- ч ч с тгхо/ о Т о оллт,тт с тпми i сравнения, а его выход подключен г ыходу 11 знака устройств, Больше схшчы 1 сравнения гоедш о выходом 12 результата сравнения устройства, выходы группы 4 сумматоров по модулю два соединены с соответствующими входами первой группы узла 6 формирования переноса, входы первой группы узла 5 формирования суммы и раэности соединены с соответствующими выходами узла 6 формирования переноса выходы узла 5 формирования суммы и раэности соединены с выхода ® 11 разрядов результата устройства. Кроме того, арифметическое устройство содержит коммутатор 1 чисел, прячем ин- формацноакые входы первой и второй групп коммутаторе 14 чисел соединены с входами 7 и 15 разрядов первого и второго операндов устройства соответ- ственно, вход управления коммутатора 14 чисел соединен с выходом Не больше схемы 1 сравнения, выходы первой группы коммутатора 14 чисел соединены с входами второй группы узла 5 формирования суммы и раэности и с входами второй группы узла 6 формирования переноса, выходы второй группы коммутатора 14 чисел соединены с первыми входами группы 4 сумматоров по модулю два, устройство также содержит элемен 16 ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с выходом переноса уз- Jia 6 формирования переноса, а выход

0

5

0

0

5

5

0

подключен к выходу 17 переноса устройства, выход сумматора 2 по модулю два соединен с третьим входом узла 3 формирования знака, со вторыми входами группы 4 сумматоров по модулю два, с входом переноса узла 5 формирования суммы и разности, с входом переноса узла 6 формирования переноса и со вторым входом элемента 16 ИСКЛЮЧАЮЩЕЕ ИЛИ, входы второй группы схемы j сравнения соединены с входами 15 разрядов второго операнда устройства, а сходы третьей группы узла 5 формирования суммы и разности соединены с соответствующими выходами группы 4 сум;аторов по мсдуто два, узел 3 формирования знака содержит элемент 18 И--НЕ а элемент 19 РАВНОЗНАЧНОСТЬ, причем первый вход элемента 19 ТЧ ВНОЗНАЧЧОСТЬ

годключей к первому плоду узла 3 формирования знака, первый и второй входы элемента 18 И--НЕ подключены ко вто- пому и ретьему пллдал /члт 3 формирования нача i тст.твегно, вчх v элемента 18 И-НЕ соединен со вторым входом элемента 19 РАВНОЗНАЧНОСТЬ. выход которого подключи ч к выхо/ту у ла 3 формирования знака.

Устройство работает следующим образом.

Первый и второй операнды, представленные в прямом коде, поступают нв входы 7 и 15, а их знаки - на входы В и 9 соответственно. Схема 1 сравнения определяет какое из чисел меньше и вырабатывает соответствующий сигнал, который поступает на управляющий BTJ коммутатора 14 чисел. Коммутатор 14 чисел коммутирует первый и второй операнды таким образом, что больший из инк поступает на входы второй группы узла 5 и входы второй группы узла 6, а меньший - на первые вкоды группы 4 сумматоров по модулю два. Сумматор 2 по модулю два вычисляет логическую функцию Of «S(A))© КОП, которая принимает единичное значение при сложении чисел с разными знакани и при вычитании чисел с одинаковыми знаками. Лог. 1 на выходе сумматора 2 по модулю два разрешает группе 4 сумматоров по модулю два инвертировать меньшее по абсолютной величине число, а узлам 5 и 6 - прибавить единицу в младшем разряде для перевода меньшего по модулю числа в дополнительный код. Лог. 1 на выходе сумматора 2 по модулю два, поступая на

второй вход элемента 16 ИСКЛЮЧАЮЩЕЕ ИЛИ, разрешает инвертирование сигнала переноса из старшего разряда, формируемого узлом 6 . Если логическая Функция, вычисляемая сумматором 2 по модулю два, принимает нулевое значение, которому соответствует лог.О то меньшее по .модулю число поступает на входы первой группы узла 5 и входы первой группы узла 6 без преобразования, а на входы переноса узлов 5 и -6 и на второй зход элемента 16 ИСКЛЮЧАЮЩЕЕ ИЛИ поступает лог. О. Узел 3 формирования знака реализует

логическую функцию S(R)S(A) ©(J-M,

где (j1 - логический сипчл нп выходе сумматора 2 по модулю двч, а М - логический сигнал на выходе Не больше схемы 1 сравнения.

Принцип действия узла 5 формирования суммы и разности и узла 6 формирования переноса широко известен и описан в (1).

Конкретный вариант построения устройства (фиг, 3) содержит сумматоры 20 по модулю два, мультиплексоры 21 и элемент НЕ 22, образуюсь схему 1 сравнения, двунаправленные ключи 23 и элемент Hi, 24, образующие коммутатор 14 чисел, сумматоры 25 по модулю два, образующие узел 5 формирования суммы и разности и мажоритарные элементы 26, образующие узел 6 формирования переноса. Формула изобр.е тения

Арифметическое устройство, содержащее схему сравнения, сумматор по модулю два, узел формирования знака, группу сумматоров по модулю два, узел формирования суммы и разности и узел формирования переноса, причем входы первой группы схемы сравнения соединены с входами разрядов первого операнда устройства, первый вход сумматора по модулю два соединен с входом знака первого операнда устройства и с первым входом узла формироват ия знака, второй и третий входы с ммато- ра по модулю два соединены с вхс ом знака второго операнда устройства и с входом кода операции соответственно, второй вход узла формирования знака соединен с выходом Не больше схемы сравнения, а его выход подключен к выходу знака устройства, выход Больше схемы сравнения соединен с выходом результата сравнения устройст

5

0

5

0

5

0

5

0

5

ва, выходы группы сумматоров по модулю два соединены поразрядно с входами первой группы узла формирования переноса, входы первой группы узла формирования суммы и разности соединены поразрядно с выходами узла формирования переноса, выходы узла формирования суммы и разности соединены с выходами разрядов результата устройства, отличающееся тем, что, с целью сокращения аппаратных затрат, оно содержит коммутатор чисел и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, а узел формирования знака содержит элемент И-НЕ и элемент РАВНОЗНАЧНОСТЬ, причем информационные входы первой и яторой групп коммутатора чисел соединены о входами разрядов первого и второго операндов устройства соответственно, вхоп управления коммутатора чисел соединен с выходом Не больше схемы сравнения, выходы первой группы коммутатора чисел соединены с входами второй группы узла формирования суммы и разности и с входами второй группы узла формирования переноса, выходы второй группы коммутатора чисел гоединенч с первыми входами группы сумматороп по модулю два, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом переноса узла формирования переноса, а выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к выходу переноса устройства, выход сумматора по модулю два соединен с ре- тьим входом узла формирования знака, со вторыми входами группы сумматоров по модулю два, с входом переноса узла формирования суммы и разности, с входом переноса узла формирования переноса и со вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, входы второй группы схемы сравнения соединены с входами разрядов второго операнда устройства, а входы третьей группы узла формирования суммы и разности соединены поразрядно с выходами группы сумматоров по модулю два, первый вход элемента РАВНОЗНАЧНОСТЬ узла формирования знака подключен к первому входу узла формирования знака, первый и второй входы элемента И-НЕ узла формирования знака подключены ко второму и третьему входам узла формирования знака соответственно , выход элемента И-НЕ узла формирования знака соединен со вторым входом элемента РАВНОЗНАЧНОСТЬ узла, выход которого подключен к выходу узла формирования знака.

(Начало}

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1984 |

|

SU1290298A1 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1991 |

|

SU1784971A1 |

| Устройство для поиска чисел в заданном диапазоне | 1981 |

|

SU993250A1 |

| Устройство для алгебраического сложения чисел | 1986 |

|

SU1339552A1 |

| УСТРОЙСТВО ВЫРАВНИВАНИЯ ПОРЯДКОВ ОПЕРАНДОВ | 1992 |

|

RU2006910C1 |

| Одноразрядный двоичный сумматор | 1987 |

|

SU1411736A1 |

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1993 |

|

RU2069009C1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении процессоров ЭВМ и устройств обработки цифровой информации. Цель изобретения - сокращение аппаратных затрат. Указанная цель достигается тем, что в арифметическое устройство, содержащее схему сравнения, сумматор по модулю два, узел формирования знака, группу сумматоров по модулю два, узел формирования суммы и разности и узел формирования переноса, введен коммутатор чисел с соответствующими связями. 3 ил. с Ј

1

IflNfl

I

IZ3

Конец

Pve.f

/J

.2

| Алексеенко А.Г., Юагурин И.И | |||

| Микросхемотехника | |||

| - М.: Радио и связь, 1982, с | |||

| Аппарат для радиометрической съемки | 1922 |

|

SU124A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Арифметическое устройство | 1984 |

|

SU1290298A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-03-15—Публикация

1989-03-15—Подача