Изобретение относится к вычисли- тельной технике и может быть использовано при построении процессоров ЭВМ и устройств обработки цифровой информации.с

Цель изобретения - расширение области применения устройства за счет реализации сложения и вычитания чисел со знаками и операции сравнения.

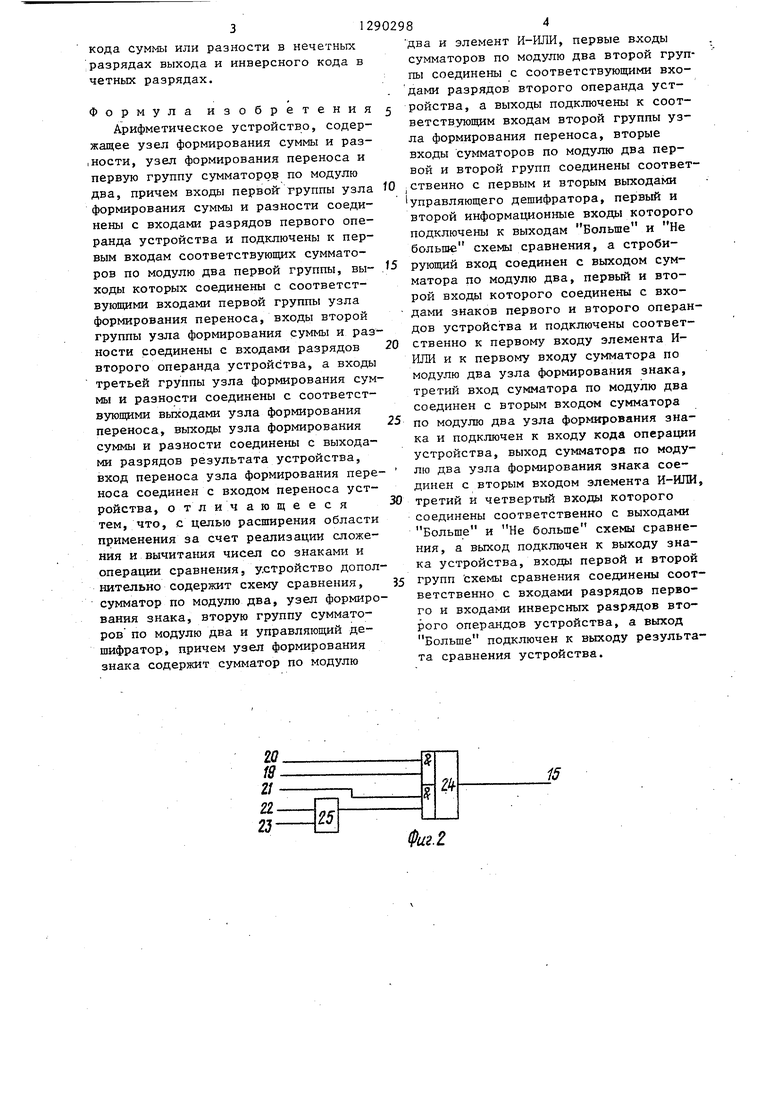

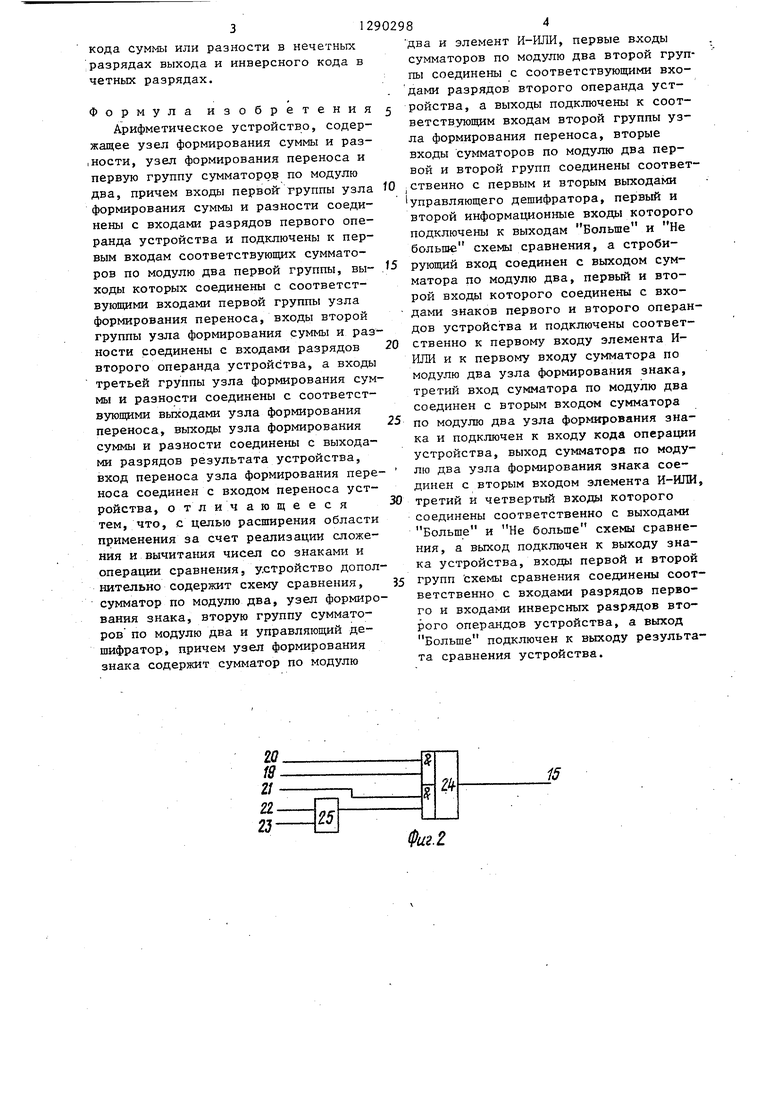

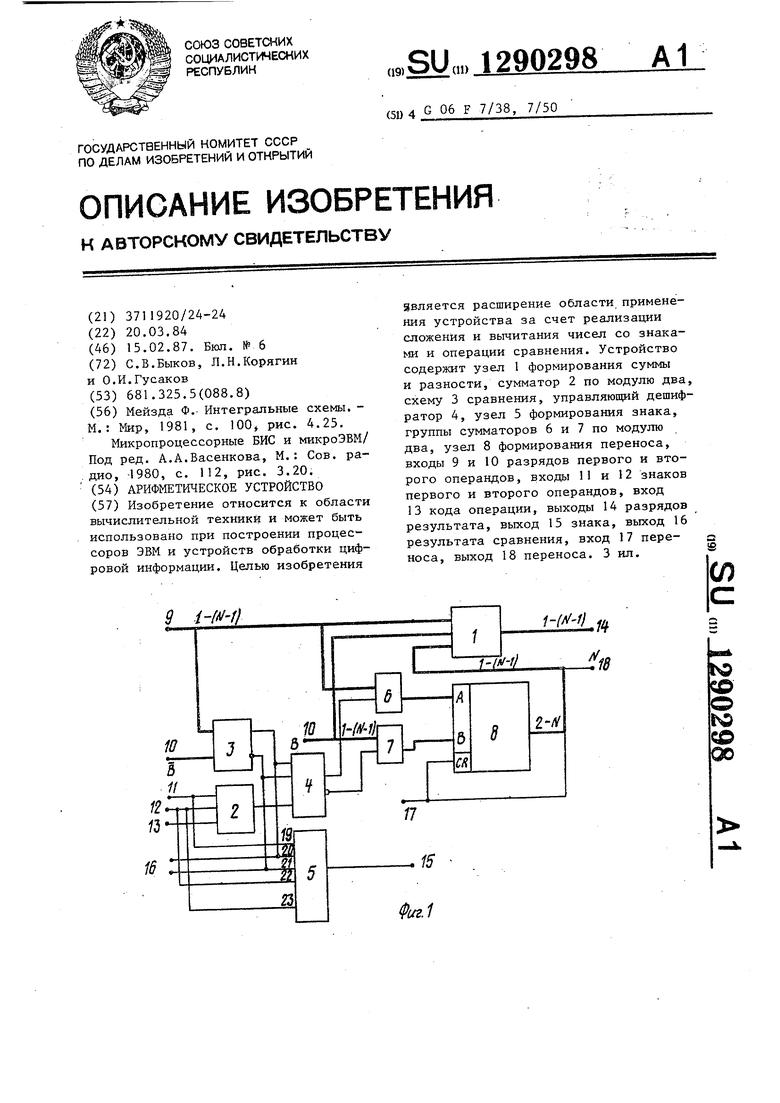

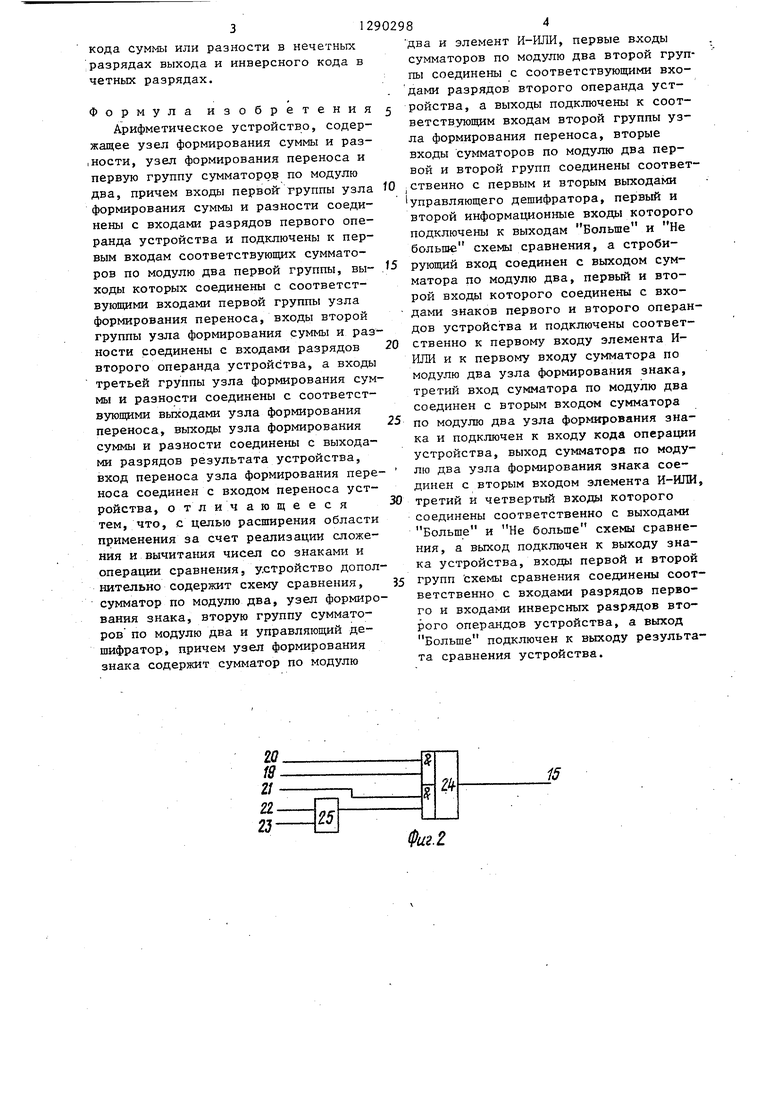

На фиг.1 представлена структурная О схема арифметического устройства; на фиг.2 - функциональная схема узла формирования знака; на фиг.З - вариант конкретного вьшолиения функциональной скемы двухразрядного арифме- тического устройства.

Устройство содержит узел I форми- рования суммы и разности, сумматор 2 по модулю два, схему 3 сравнения, управляющий дешифратор 4, узел 5 фор-- .мнрования знака, группы сумматоров 6 и 7 по модулю два, узел 8 формирования переноса, входы 9 и 10 разрядов первого и второго операндов, входы I и 12 знаков первого и вто- рого операндов, вход 3 кода операции j выходы 4 разрядов результата, |Вьпсод 15 знака, выход 16 результата сравнения, а также вход 17 и выход 18 переноса.

Узел 5 имеет нходы 19-23 и содержит элемент И-ИПИ 24 и сумматор 25 по модулю два.

Конкретный вариант построения устройства содержит сумматоры 26 по мо- 35 дулю два, образующие узел формирования суммы и разности, мажоритарные . элементы 27, образующие узел 8 формирования переноса, мажоритарные элементы 28, образующие схему 3 сравие- НИЛ, сумматоры б и 7 по модулю два, сумматор 2 по модулю два, элементы И-НЕ 29 и 30, образующие управляю1ций дешифратор 4, сумматор 25 по модулю ..два и элемент И-ШЖ 24, входящие з узел 5 фop иpoвaния знака, а также Ьлементы НЕ 31-34.

25

45

Устройство работает следующим об- разом. .

Логика работы узла 1 не зависит от операции сложения и вычитания, изменяется в эТом плане только логика формирования сигналов разрядных пере- носов: при суммировании YI ABC -н + ABC + ABC + ABC, при вычитании числа В из числа А Y2 ABC + АБС + + ABC + ABC, при вычитании числа А из числа В Y3 АВС.+ АВС + ABC

с

О

5

5

5

0

5

+ ABC, где С - входной перенос (заем) .

Формирование данных функций осуществляется следующим образом.

На сумматор 2 по модулю два подаются знак числа А и знак числа В; если код операции нулевой, что соответствует сложению, то при равенстве знаков чисел А и В на выходе сумматора 2 по модулю два присутствует сигнал, запрещающий прохождение сигналов со схемы 3 сравнения к группам суммаTojpoB по модулю два 6 и 7. Сумматоры 6 и 7 по модулю два в этом случае не инвертируют входные числа А и В, а так как их знаки одинаковы, то на зыходе узла 5 получим знак чис- ла В. Если число А положительно, а число В отрицательно или наоборот и присутствует единичный код операции (вычитание), то на выходе сумматора 2 по модулю два будет сигнал, запрещающий прохождение сигналов с выходов схемы 3 сравнения на группы сумматоров 6 и 7 по модулю два. В узле выполняется операция сложения чисел А и В по модулю два. Схема 3 сравнения определяет большее по модулю ЧИС/1О, -знак которого передается на выход 15, а узел 8 осуществля- ет функцию Y1.

При одинаковых знаках чисел А и В и операции вычитания сумматор 2 по модулю два дает разрешение на .вход дешифратора 4, при этом знак большего по модулю числа проходит на выход 15, знак числа В проинвер- тирован, а большее по модулю число проинвертируется на сумматорах 6 или 7 по модулю два. .Узел 8 выдает в этом случае сигналы переноса в соответствии с логической функцией Y2 или Y3. На вход 17 подается сигнал входного переноса. На выходах 14 получим разность двух чисел, а на выходе 18 - сигнал выходного переноса.

Таким образом, результат операции не зависит от вариации поступления чисел на входы А и В, знаки чисел и их величины анализируются самим устройством, операции сложения и вычитания выполняются без применения дополнительного кода. В каждой операции вместе с результатом сложения или вычитания выдается результат сравнения чисеш по модулю.

Устройство, представленное на фиг.З, осуществляет выдачу прямого

кода суммы или разности в нечетных разрядах выхода и инверсного кода в четных разрядах.

Формула изобретения Арифметическое устройство, содержащее узел формирования суммы и раз- ,ности, узел формирования переноса и первую группу сумматоре по модулю два, причем входы первой: группы узла формирования суммы и разности соединены с входами разрядов первого операнда устройства и подключены к первым входам соответствующих сумматоров по модулю два первой группы, выходы которых соединены с соответствующими входами первой группы узла формирования переноса, входы второй группы узла формирования суммы и разности соединены с входами разрядов второго операнда устройства, а входы третьей группы узла формирования суммы и разности соединены с соответствующими выходами узла формирования переноса, выходы узла формирования суммы и разности соединены с выходами разрядов результата устройства, вход переноса узла формирования пере носа соединен с входом переноса устройства, отличающееся тем, что, с целью расширения области применения за счет реализации сложения и вычитания чисел со знаками и операции сравнения, устройство дополнительно содержит схему сравнения, сумматор по модулю два, узел формирования знака, вторую группу сумматоров по модулю два и управляющий дешифратор, причем узел формирования знака содержит сумматор по модулю

o

5

0 5

5

0

два и элемент И-ИЛИ, первые входы сумматоров по модулю два второй группы соединены с соответствующими входами разрядов второго операнда устройства, а выходы подключены к соответствующим входам второй группы узла формирования переноса, вторые входы сумматоров по модулю два первой и второй групп соединены соответ- Iственно с первым и вторым выходами управляющего дешифратора, первый и второй информационные входы которого подключены к выходам Больше и Не больше схемы сравнения, а строби- рующий вход соединен с выходом сумматора по модулю два, первый и второй входы которого соединены с входами знаков первого и второго операндов устройства и подключены соответственно к первому входу элемента И- ИЛИ и к первому входу сумматора по модулю два узла формирования знака, третий вход сумматора по модулю два соединен с вторым входом сумматора по модулю два узла формирования знака и подключен к входу кода операции устройства, выход сумматора по модулю два узла формирования знака соединен с вторым входом элемента И-ИЛИ, третий и четвертый входы которого соединены соответственно с выходами Больше и Не больше схемы сравнения, а выход подключен к выходу знака устройства, входы первой и второй групп схемы сравнения соединены соответственно с входами разрядов первого и входами инверсных разрядов второго операндов устройства, а выход Больше подключен к выходу результата сравнения устройства.

Редактор М.Дылын

Составитель А.Степанов Техред Л.Олейник

Заказ 7902/46

Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор М.Демчик

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1989 |

|

SU1635172A1 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1991 |

|

SU1784971A1 |

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Устройство для алгебраического сложения чисел | 1983 |

|

SU1136148A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для алгебраического сложения чисел | 1986 |

|

SU1339552A1 |

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| Устройство для сложения (I) | 1989 |

|

SU1837281A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении процессоров ЭВМ и устройств обработки цифровой информации. Целью изобретения 9 i-(H является расширение области применения устройства за счет реализации сложения и вычитания чисел со знаками и операции сравнения. Устройство содержит узел 1 формирования суммы и разности, сумматор 2 по модулю два, схему 3 сравнения, управляющий дешифратор 4, узел 5 формирования знака, группы сумматоров 6 и 7 по модулю два, узел 8 формирования переноса, входы 9 и 10 разрядов первого и второго операндов, входы 11 и 12 знаков первого и второго операндов, вход 13 кода операции, выходы 14 разрядов результата, выход 15 знака, выход 16 результата сравнения, вход 17 переноса, выход 18 переноса. 3 ил. ) П (Л С Фиг.1

| Мейзда Ф.- Интегральные схемы | |||

| - М | |||

| : Мир, 1981, с | |||

| Облицовка комнатных печей | 1918 |

|

SU100A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Микропроцессорные БИС и микроЭВМ/ Под ред | |||

| А.А.Басенкова, М.: Сов | |||

| радио, -1980, с | |||

| Прялка для изготовления крученой нити | 1920 |

|

SU112A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-02-15—Публикация

1984-03-20—Подача