Предполагаемое изобретение Относится к области вычислительной техники и может быть применено в высокопроизводительных системах обработки информации.

Известно устройство для сложения- вычитания чисел с плавающей запятой, содержащее сумматор, двигатель и блок дешифрации 1,

Это устройство имеет низкое быстродействие по следующим причинам: а) требуется дополнительный такт преобразования дополнительного кода результата в прямой код, если результат отрицательный; б) формирование кода нормализации происходит только после сложения-вычитания мантисс. К недостаткам данного устройства следует отнести и низкую достоверность формируемых на выходе устройства результатов из-за отсутствия средств встроенного контроля.

Известно устройство для сложения-вычитания чисел с плавающей запятой, содержащее сумматор, сдвигатель и узел предсказания кода нормализации 2.

Это устройство имеет более высокое быстродействие, чем предыдущее вследствие того, что в составе устройства имеется узел предсказания кода нормализации, который вырабатывает код нормализации мантиссы параллельно с формированием мантиссы результата.

Недостатком данного устройства является то, что требуется дополнительный такт преобразования дополнительного кода результата в прямой код в случае хранения чисел в памяти в прямом коде (в ЕС ЭВМ числа в форме с плавающей запятой хранятся в памяти в прямом коде), а также низкая достоверность формируемых на выходе устxj00 Јь Ю VI

ройства результатов из-за отсутствия средств встроенного контроля.

Наиболее близким по технической сущности к предлагаемому изобретению является устройство для сложения-вычитания чисел с плавающей запятой, содержащее три сумматора, четыре вычитателя, два сдвигателя, два узла предсказания кода нормализацТМГвйсемь коммутаторов, три узла управления коммутатором, узел обработки знаков, узел сравнения четностей и узел поразрядного сравнения, причем вход мантиссы первого операнда устройства соединен с первыми входами первого и второго коммутаторов, вторые входы которых соединены с входом мантиссы второго операнда устройства, вход порядка первого операнда которого соединен с первым входом третьего коммутатора, с входом уменьшаемого первого вычитателя и с входом вычитаемого второго вычитателя, вход порядка второго операнда устройства соединен с вторым входом третьего коммутатора, с входом вычитаемого первого вычитателя и с входом уменьшаемого второго вычитателя, выход второго вычитателя - с первым входом четвертого коммутатора, второй вход которого соединен с первым выходом первого вычитателя, второй выход которого соединен с управляющими входами коммутаторов с первого по четвертый и с первым входом узла обработки знаков, второй,

третий и четвертый входы которого соединены с входом знака мантиссы первого операнда, входом знака мантиссы второго операнда и с входом режима устройства соответственно, первый и второй входы первого узла предсказания кода нормализации соединены с выходом функций генерации переноса и с выходом функций транзита переноса первого сумматора соответственно, первый и второй входы второго узла предсказания кода нормализации - с выходом функций генерации переноса и с выходом функций транзита переноса второго сумматора соответственно, выход суммы первого сумматора соединен с первыми входами пятого коммутатора, узла сравнения четностей и узла поразрядного сравнения, выход суммы второго сумматора - с вторыми входами пятого коммутатора, узла сравнения четностей и узла поразрядного сравнения, выход первого узла предсказания кода нормализации - с первым входом шестого коммутатора и третьим входом узла поразрядного сравнения, выход второго узла предсказания кода нормализации - с вто- рым входом шестого коммутатора и четвертым входом у,зла поразрядного сравнения, выход первого коммутатора - с информационным входом первого сдвигателя, вход величины сдвига которого соединен с выходом четвертого коммутатора, выход второго коммутатора - с первым входом первого сумматора, второй вход которого соединен с выходом первого сдвигателя и с первым входом второго сумматора, второй вход которого соединен с первым входом первого сумматора, вход уровня

0 логической единицы устройства соединен с первым входом третьего сумматора, второй вход которого соединен с выходом третьего коммутатора и с входом уменьшаемого вычитателя, вход вычитаемого которого соеди5 нен с входом вычитаемого четвертого вычитателя, выходом шестого коммутатора и с входом величины сдвига второго сдвигателя, информационный вход которого соединен с выходом пятого коммутатора,

0 управляющий вход которого соединен с выходом первого узла управления коммутатором и третьим входом узла сравнения четностей, первый выход второго сдвигателя соединен с первым входом седьмого ком5 мутатора, выход которого соединен с четвертым входом узла сравнения четностей, выход которого является первым разрядом выхода признака ошибки устройства, выход мантиссы результата которого -среди0 нен со старшими разрядами выхода седьмого коммутатора, старшие разряды второго входа седьмого коммутатора соединены с входом константы устройства, а младшие разряды - с первым выходом второго с дви5 гателя, выход знака мантиссы результата с первым выходом узла обработки знаков,

пятый вход которого соединен с выходом

переноса первого сумматора, с первыми

входами узлов управления коммутатором с

0 первого по третий и с пятым входом узла поразрядного сравнения, управляющий вход которого соединен с вторыми входами узлов управления коммутатором с первого по третий, с управляющими входами узлов

5 предсказания кода нормализации, с входами переносов первого и второго суммато- рое с входами режима первого и второго сумматоров и с вторым выходом узла обработки знаков, шестой вход которого соеди0 нен с выходом переноса второго сумматора, с третьими входами первого и второго узлов управления коммутатором и с шестым входом узла поразрядного сравнения, выход которого является вторым разрядом выхода

5 признака ошибки устройства, вход разрешения нормализации которого соединен с четвертым входом второго узла управления коммутатором, выход которого соединен с управляющим входом шестого коммутатора,пятый вход узла сравнения четностей соединен с первым выходом третьего узла управления коммутатором, третий вход которого соединен с вторым выходом второго сдвигателя, управляющий вход седьмого коммутатора соединен с вторым выходом третьего узла управления коммутатором и с управляющим входом восьмого коммутатора, первый вход которого соединен с выходом третьего вычитателя, выход третьего сумматора соединен с входом уменьшаемого четвертого вычитателя, выход которого соединен с вторым входом восьмого коммутатора, выход которого является, выходом порядка результата устройства 3.

По сравнению с предыдущим, данное устройство имеет б9лее высокое быстродействие за счет того, что отсутствует дополнительный такт преобразования дополнительного кода отрицательного результата в прямой код в случае хранения чисел в памяти в прямом коде (в ЕС ЭВМ числа в форме с плавающей запятой хранятся в памяти в прямом коде) и более высокую достоверность формируемых результатов устройства, т.к. полным контролем (т.е. контроль осуществляется как при сложении, так и при вычитании мантисс) охвачены второй сдвигатель, пятый и седьмой коммутаторы, а также частичным контролем (т.е. контролем только при сложении мантисс) охвачены первые и вторые сумматоры и узлы предсказания кода нормализации.

Недостатком этого устройства является низкая достоверность формируемых на выходе устройства результатов при вычитании мантисс, т.к. в этом случае не контролируется функционирование сумматоров и узлов предсказания кода нормализации.

Цель изобретения - повышение достоверности формируемых результатов устройства.

Поставленная цель достигается тем, что устройство для сложения-вычитания чисел с плавающей запятой, содержащий три сумматора, два узла предсказания кода нормализации, четыре вычитателя, два сдвигателя, восемь коммутаторов, три узла управления коммутатором, узел обработки знаков, узел сравнения четностей и узел поразрядного сравнения, причем вход мантиссы первого операнда устройства соеди- нен с первыми входами первого и второго коммутаторов, вторые входы которых соединены с входом мантиссы второго операнда устройства, вход порядка первого операнда которого соединен с первым входом третьего коммутатора, с входом уменьшаемого первого вычитателя и с входом вычитаемого второго вычитателя, вход порядка второго операнда устройства - с 5 вторым входом третьего коммутатора, с входом вычитаемого первого вычитателя и с входом уменьшаемого второго вычитателя, выход второго вычитателя - с первым входом четвертого коммутатора, второй вход

0 которого соединен с первым выходом первого вычитателя, второй выход которого соединен с управляющими входами коммутаторов с первого по четвертый и с первым входом узла обработки знаков, вто5 рой, третий и четвертый входы которого соединены с входом знака мантиссы первого операнда, с входом знака мантиссы второго операнда и с входом режима устройства соответственно, первый и второй входы пер0 вого узла предсказания кода нормализации соединены с выходом функций генерации переноса и с выходом функций транзита переноса первого сумматора соответственно, первый и второй входы второго узла

5 предсказания кода нормализации - с выходом функций генерации переноса и с выходом функций транзита переноса второго сумматора соответственно, выход суммы первого сумматора соединен с первым вхо0 дом пятого коммутатора, выход суммы второго сумматора - с вторым входом пятого коммутатора, выход первого узла предсказания кода нормализации - с первым входом шестого коммутатора, выход второго

5 узла предсказания кода нормализации - с

вторым входом шестого коммутатора, выход

первого коммутатора - с информационным

входом первого сдвмгателя, вход величины

сдвига которого соединен с выходом четвер0 того коммутатора, выход второго коммутатора - с первым входом первого сумматора, второй вход которого соединен с выходом первого сдвигателя и с первым входом второго сумматора, второй вход которого сое5 динен с первым входом первого сумматора, вход уровня логической единицы устройства - с первым входом третьего сумматора, второй вход которого соединен с выходом третьего коммутатора и с входом

0 уменьшаемого третьего вычитателя, вход вычитаемого которого соединен с входом вычитаемого четвертого вычитателя, выходом шестого коммутатора и с входом величиньТ сдвига второго сдвигателя, информацион5 ный вход которого соединен с выходом пятого коммутатора, управляющий вход пятого коммутатора - с выходом первого узла управления коммутатором, первый выход второго сдвигателя соединен с первым входом седьмого коммутатора, выход которого соединен с первым входом узла сравнения четностей, выход которого является первым разрядом выхода признака ошибки устройства, выход мантиссы результата которого соединен со старшими разрядами выхода седьмого коммутатора, старшие разряды второго входа которого соединены с входом константы устройства, а-младшие разряды - с первым выходом второго сдвигателя, выход знака мантиссы результата - с первым выходом узла обработки знаков, пятый вход которого соединен с выходом переноса первого сумматора,с первыми входами первого и третьего узлов управления коммутатором и с первым входом узла поразрядного сравнения, управляющий вход которого соединен с вторыми входами первого и третьего узлов управления коммутатором, с управляющими входами первого и второго узлов предсказания кода нормализации, с входами переносов первого и второго сумматоров, с входами режима первого и второго сумматоров и с вторым выходом узла обработки знаков, шестой вход которого соединен с выходом переноса второго сумматора, с третьим входом первого узла управления коммутатором и с вторым входом узла поразрядного сравнения, выход которого является вторым разрядом выхода признака ошибки устройства, вход разрешения нормализации которого соединен с первым входом второго узла управления коммутатором, выход которого соединен с управляющим входом шестого коммутатора, второй вход узла сравнения четностей - с первым выходом третьего узла управления коммутатором, третий вход-которого соединен с вторым выходом второго сдвигателя, управляющий вход седьмого коммутатора - с вторым выходом третьего узла управления коммутато-. ром и с управляющим входом восьмого коммутатора, первый вход которого соединен с выходом третьего вычитателя, выход третьего сумматора - с входом уменьшаемо- го четвертого вычитателя, выход которого соединен с вторым входом восьмого коммутатора, выход которого является выходом порядка результата устройства. Дополнительно введены четвертый сумматор, третий узел предсказания кода нормализации, девятый м десятый коммутаторы причем первый вход девятого коммутатора соединен с первым входом десятого коммутатора и с выходом второго коммутатора, выход девятого коммутатора - с первым входом четвертого сумматора, второй вход которого соединен с выходом десятого коммутатора, второй вход девятого коммутатора - с вторым входом десятого коммутатора и с выходом первого сдвигателя, управляющие входы девятого и десятого коммутаторов соединены с выходом первого узла управления коммутатором и с вторым входом второго узла управления коммутатора, первый и второй входы третьего узла предсказания кода нормализации - с выходом функций генерации переноса и с выходом

функции транзита переноса четвертого сум- матора соответственно, выход суммы четвертого сумматора соединен с третьим входом узла поразрядного сравнения, четвертый вход которого соединен с выходом

пятого коммутатора и с третьим входом узла сравнения четностей, входы переноса и режима четвертого сумматора и управляющий вход третьего узла предсказания кода нормализации соединены с вторым выходом узла обработки знаков, выход третьего узла предсказания кода нормализации соединен с пятым входом узла поразрядного сравнения, шестой вход которого соединен с выходом шестого коммутатора.

Предлагаемое устройство для сложения-вычитания чисел с плавающей запятой содержит такие отличительные признаки, как четвертый сумматор, третий узел предсказания кода нормализации, девятыми десятый коммутаторы, которые отсутствуют во всех аналогах и благодаря которым достигается положительный эффект - повышение достоверности формируемых результатов

устройства за счет контроля вычитания мантисс.

Таким образом, т.к. в предлагаемом техническом решении имеются отличительные признаки, отсутствующие во всех аналогах

и обеспечивающие достижение поставленной цели, то данное техническое решение соответствует критерию существенные отличия.

На фиг.1 приведена структурная схема

устройства для сложения-вычитания чисел с плавающей запятой; на фиг.2 - функциональная схема девятого коммутатора; на фиг.З - структурная схема узла сравнения четностей; на фиг.4 - структурнай схема

узла поразрядного сравнения; на фиг,5 - функциональная схема второго узла управления коммутатором,

Устройство для сложения-вычитания чисел с плавающей запятой (фиг.1) содержит сумматоры 1-4 с первого по четвертый соответственно, узлы 5-7 предсказания кода нормализации с первого по третий соответственно, вычитатели 8-11 с первого по четвертый соответственно, первый 12 и второй 13 сдвигатели, коммутаторы 14-23 с первого по десятый соответственно, узел 24 обработки знаков, узел 25 сравнения четно- стей, узел 26 поразрядного сравнения, узлы 27-29 управления коммутатором с первого по третий соответственно, вход 30 мантиссы первого операнда, вход 31 мантиссы второго операнда, вход 32 порядка первого операнда, вход 33 порядка второго операнда, вход 34 знака мантиссы первого операнда, вх од 35 знака мантиссы второго операнда, вход 36 режима устройства, вход 37 разрешения нормализации, вход 38 константы устройства, вход 39 уровня логической единицы устройства, выход 40 мантиссы результата, выход 41 порядка результата, выход 42 знака мантиссы результата, выход 43 признака ошибки устройства, первый 44 и второй 45 выходы.вычитателя 8, выход 46 вычитателя 9, выходы 47-50 коммутаторов 14-17 соответственно, выход 51 сдчигателя 12, второй выход 52 узла 24 обработки знаков, выходы 53-55 сумм сумматоров 1, 2 и 4

соответственно, выходы 56-58 функций генерации переноса сумматоров 1, 2 и 4 соответственно, выходы 59-61 функций транзита переноса сумматоров 1,2 и 4 соответственно, выходы 62, 63 переноса сумматоров 1, 2 соответственно, выходы 64-66 узлов 5-7 предсказания кода нормализации соответственно, выходы 67, 68 коммутаторов 18,19 соответственно, первый 69 и второй 70 выходы сдвигателя 13, выход 71 коммутатора 20, выходы 72, 73 узлов 27, 28. управления коммутатором соответственно, пе рвый 74 и второй 75 выходы узла 29 управления коммутатором, выход 76 сумматора 3У выходы 77, 78 вычитателей 10, 11 соответственно, выходы 79, 80 коммутаторов 22, 23 соответственно.

Вход 30 мантиссы первого операнда устройства соединен с первыми входами первого 14 и второго 15 коммутаторов, вторые входы которых соединены с входом 31 мантиссы второго операнда устройства, вход 32 порядка первого операнда которого соединен с первым входом третьего коммутатора 16, с входом уменьшаемого первого вычитателя 8 и с входом вычитаемого второго вычитателя 9, вход 33 порядка второго операнда устройства соединен с вторым входом третьего коммутатора 16, с входом вычитаемого первого вычитателя 8 и с входом уменьшаемого второго вычитателя 9, выход 46 второго вычитателя 9 - с первым входом четвертого коммутатора 17, второй вход которого соединен с первым выходом 44 первого вычитателя 8, второй выход 45 которого соединен с управляющими входами коммутаторов 14-17 и с первым входом узла 24 обработки знаков, второй, третий и четвертый входы которого соединены с входом 34 знака мантиссы первого опе- 5 ранда, входом 35 знака мантиссы второго операнда и с входом 36 режима устройства соответственно, первый и второй входы первого узла 5 предсказания кода нормализации соединены с выходом 56 функций 10 генерации переноса и с выходом 59 функций транзита переноса перв ого сумматора 1 соответственно, первый и второй входы второго узла 6 предсказания кода нормализации - с выходом 57 функций генера- 5 ции переноса и с выходом 60 функций транзита переноса второго сумматора 2 соответственно, выход 53 суммы первого сумматора 1 соединен с первым входом пятого коммутатора 18, выход 54 суммы 0 второго сумматора 2-е вторым входом пятого коммутатора 18, выход 64 первого узла 5 предсказания кода нормализации - с первым входом шестого коммутатора 19, выход 65 второго узла 6 предсказания коде 5нормализации - с вторым входом шестого коммутатора 19, выход 47 первого коммутатора 14 - с информационным входом первого сдвигателя 12, вход величины сДви- га которого соединен с выходом 50 четвер- 0 того коммутатора 17, выход 48 второго коммутатора 15 соединен с первым входом первого сумматора 1, вторым входом второго сумматора 2 и с первыми входами девятого 22 и десятого 23 коммутаторов, выход 51 пер- 5 вого сдвигателя 12 - с первым входом второго сумматора 2, вторым входом первого сумматора 1 и с вторыми входами девятого 22 и десятого 23 коммутаторов, вход 39 уровня логической единицы 0. устройства соединен с первым входом третьего сумматора 3, второй вход которого соединен с выходом 49 третьего коммутатора 16 и с входом уменьшаемого третьего вычитателя 10, вход вычитаемого которого 5 соединен с входом вычитаемого четвертого вычитателя 11, выходом 68 шестого коммутатора 19 и с входом величины сдвига второго сдвигателя 13, информационный вход которого соединен с выходом 67 пятого ком- 0 мутатора 18, управляющие входы пятого 18, девятого 22 и десятого 23 коммутаторов соединены с выходом 72 первого узла 27 управления коммутатором и с вторым входом второго узла 28 управле- 5 ния коммутатором, первый выход 69 второго сдвигателя 13 - с первым входом седьмого коммутатора 20, выход 71 которого соединен с первым входом узла 25 сравнения четностей, 1выход 43i которого является первым разрядом выхода 43

признака ошибки устройства, выход 40 мантиссы результата которого соединен о старшими разрядами выхода 71 седьмого коммутатора 20, старшие разряды второго входа которого соединены с входом 38 константы устройства, а младшие разряды - с первым выходом 69 второго сдвигателя 13, выход 42 знака мантиссы результата соединен с первым выходом узла 24 обработки знаков, пятый вход которого соединен с выходом 62 переноса первого сумматора

1,с первыми входами первого 27 и третьего 29 узлов управления коммутатором и с первым входом узла 26 поразрядною сравнения, управляющий вход которого соединен с вторыми входами первого 27 и третьего 29 узлов управления коммутатором, с управляющими входами узлов 5-7 предсказания кода нормализации, с входами переноса и режима сумматоров 1, 2 и 4 и с вторым выходом 52 узла 24 обработки знаков, шестой вход которого соединен с выходом 63 переноса второго сумматора

2,с третьим входом первого уола 27 управления коммутатором и с вторым входом узла 26 поразрядного сравнения, выход 43а которого является вторым разрядом выхода 43 признака ошибки устройства, вход 37 разрешения нормализации которого соединен с первым входом второго узла 28 управления коммутатором, выход 73 которого соединен с управляющим входом шестого коммутатора 19, второй вход узла 25 сравнения четностей соединен с первым выходом 74 третьего узла 29 управления коммутатором, третий вход которого соединен с вторым выходом 70 второго сдвигателя 13, управляющий вход седьмого коммутатор 20 соединен с вторым выходом 75 третьего узла 29 управления коммутатором и с управляющим входом восьмого ком-, мутатора 21, nepet вход которого соединен с выходом 77 третьего вычи- тателя 10, выход 76 третьего сумматора 3 соединен с входом уменьшаемого

четвертого вычитателя 11, выход 78 которого соединен с вторым входом восьмого коммутатора 21, выход которого является выходом 41 порядка результата устройства, выход 79 девятого коммутатора 22 соединен с первым входом четвертого сумматора 4, второй вход которого соединен с выходом 80 десятого коммутатора 23, первый и второй входы третьего узла 7 предсказания кода нормализации соединены с выходом 58 функций генерации переноса и с выходом функций 61 транзита переноса четвертого сумматора 4 соответственно, выход 55 суммы четвертого сумматора 4

соединен с третьим входом узла-26 поразрядного сравнения, четвертый вход которого соединен с выходом 67 пятого коммутатора 18 и с третьим входом узла

25 сравнения четностей, выход 56 третьего узла 7 предсказания кода нормализации соединен с пятым входом узла 26 поразрядного сравнения, шестой вход которого соединен с выходом 68 шестого

коммутатора 19.

Коммутатор 22 (23) содержит группу 81 элементов 2И-ИЛИ (фиг 2).

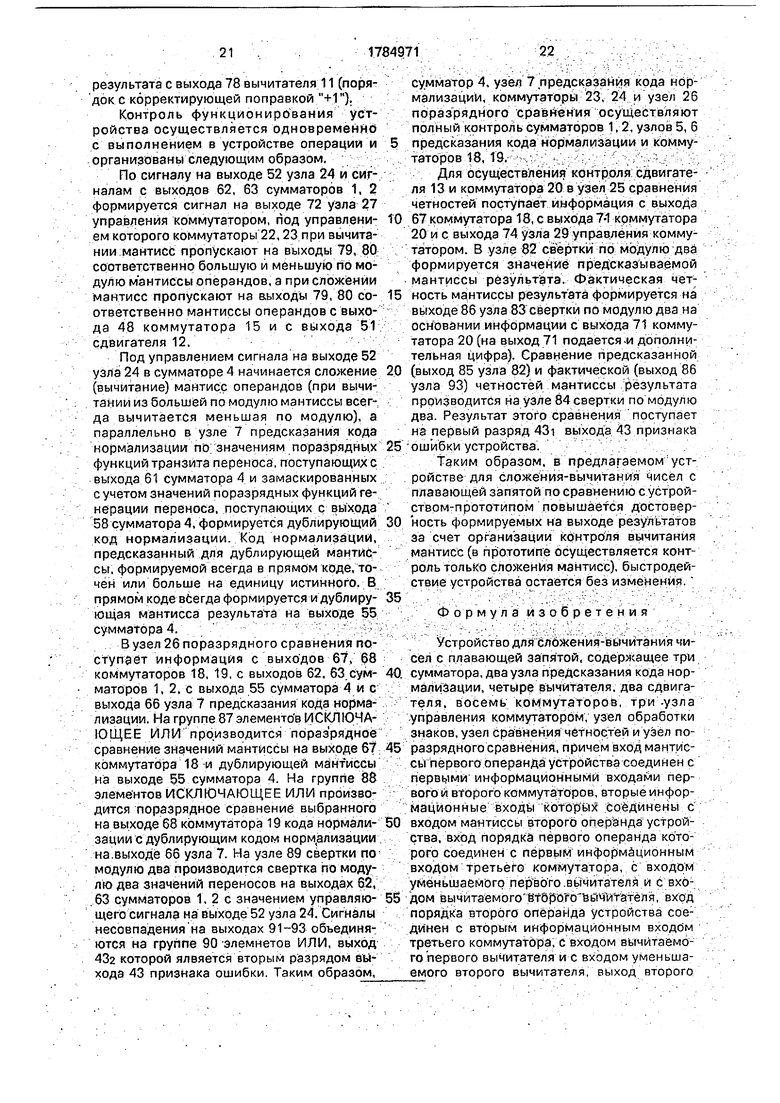

Узел 25 сравнения четностей содержит

(фиг,3) узлы группы 82-84 свертки по модулю два.,„, „

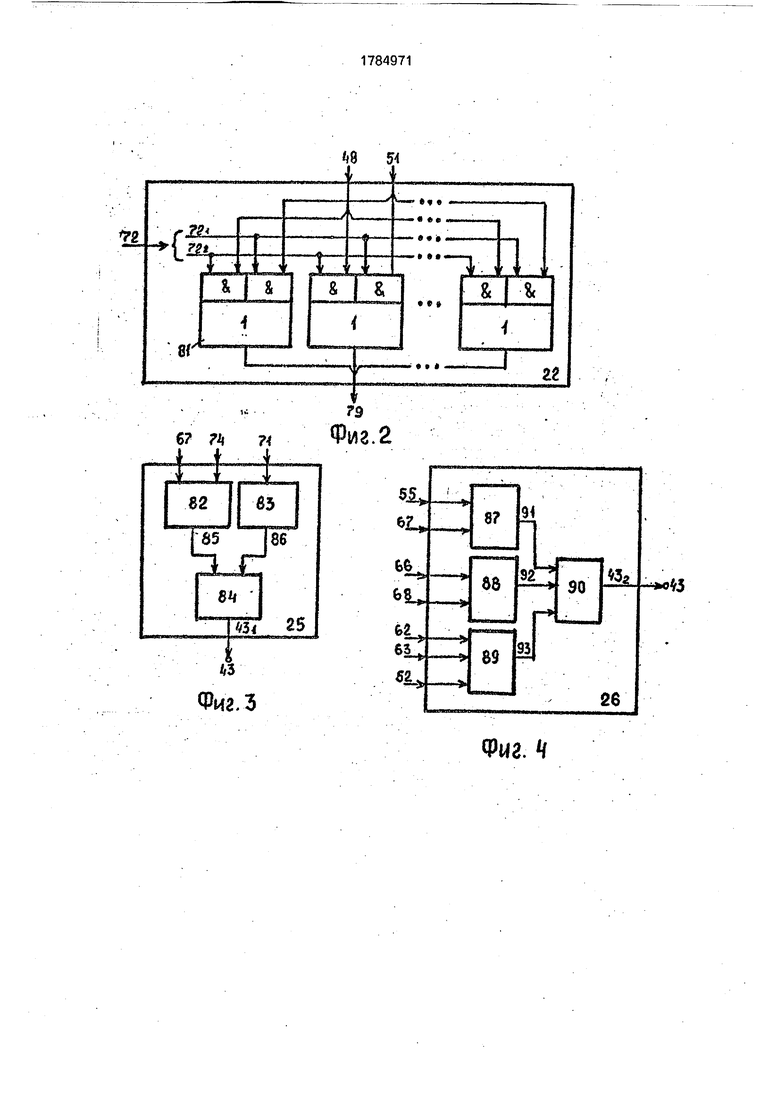

Узел 26 поразрядного сравнения содержит (фиг.4) группы 87, 88 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, узел 89 свертки по

модулю два и группы 90 элементов ИЛИ.

Второй узел 28 управления коммутатором содержит (фиг.5) два элемента И 94, 95.

Рассмотрим функциональное назначение и реализацию основных блоков и узлов устройства для сложения-вычитания чисел с плавающей запятой.

Вычитатели 8, 9, сдвигатель 12, коммутаторы 14-17 обеспечивают выравнивание

порядков операндов,

Вычитатели 8,9 предназначены для определения разности порядков операндов, причем на выходе 44 вычитателя 8 формируется разность между порядком первого и

второго операндов, а на выходе 46 вычитателя 9 - разность между порядком второго и первого операндов. На выходе 45 вычитателя 8 формируется значение заема, уровень логического нуля которого показывает

на то, что порядок первого операнда больше порядка второго операнда. Вычитатели 8,9 могут быть реализованы различными способами, например, на сумматорах с инверторами.

Коммутаторы 14-17 управляются сигналом с выхода 45 вычитателя 8. Так, при значении заема, равном О (Т), на выход 49 коммутатора 16 поступает значение порядка первого (второго) операнда, на выход 48 коммутатора 15 - значение мантиссы первого (второю) операнда, на выход 47 коммутатора 14 - значение мантиссы второго (первого) операнда, iw выход 50 коммутатора 17 - значение разности порядков операндов выхода 44 вычитателя 8 (с выхода 46 вычитателя 9) в прямом коде. Коммутаторы 14-17 могут быть реализованы различными способами, например на элементах 2И-ИЛИ

Сдвигатель 12 предназначен для выполнения необходимого при выравнивании порядков операндов сдвига вправо мантиссы операнда с меньшим порядком. На вход величины сдвига сдвигателя 12 поступает информация с выхода 50 коммутатора 17. В ЕС ЭВМ с целью повышения точности выполнения арифметических операций при выполнении сложения-вычитания используется дополнительная шестнадца- теричная цифра (тетрада), Поэтому может быть предусмотрено расширение выхода 51 сдвигателя 12 на одну дополнительную цифру, Сдвигатель 12 может быть реализован различными способами, например, как это описано .

Таким образом, на выход 49 коммутатора 1 б поступает значение большего порядка операндов, на выход 48 коммутатора 15 - значение мантиссы операнда с большим порядком, на выход 51 сдвигателя 12 -значение сдвинутой вправо мантиссы операнда с меньшим порядком.

Сумматоры 1, 2, коммутатор 18, узел 27 управления комму татором и узел 24 обработки знаков обеспечивают сложение-вычитание мантисс операндов с учетом знаков мантисс операндов (знаки мантисс операндов поступают на входы 34, 35 устройства) и режима работы устройства (режим,опера- ции сложение или вычитание задается на входе 36 устройства), На первом выходе блока 24 формируется знак мантиссы результата, который поступает на выход 42 устройства. На втором выходе 52 блока 24 формируется сигнал, настраивающий узлы устройства на сложение или вычитания мантисс.

Сумматоры 1, 2 предназначены для сложения-вычитания мантисс операндов, поступающих на их входы после выравнивания порядков с выхода 48 коммутатора 15 и с выхода 51 сдвигателя 12. Режим работы сумматоров 1, 2 определяется уровнем логического сигнала, поступающего на их входы режима с выхода 52 узла 24 обработки знаков (для определенности предполагается, что уровень логического нуля соответствует сложению мантисс, а уровень логической единицы - вычитанию мантисс, которое выполняется путем сложения уменьшаемой мантиссы с дополнительным кодом вычитаемой мантиссы). Отметим, что при вычитании мантисс сумматор 1 выполняет вычитание мантиссы операнда с меньшим порядком из мантиссы операнда с большим порядком, а сумматор 2 - вычитание мантиссы операнда с большим порядком из мантиссы операнда с меньшим порядком. Это позволяет при любых значениях мантисс и порядка всегда иметь в устройстве результат вычитания мантисс в прямом коде (либо на выходе 53 суммы сумматора 1, либо на выходе 54 суммы сум- 5 матора 2). Отметим также, что при выполнении в устройстве сложения мантисс сумматоры 1 и 2 при правильном функционировании формируют на своих выходах одинаковые результаты. Сумматоры 1,2 мо0 гут быть построены любым .из известных способов.

Коммутатор-18 предназначен для выбора с выходов 53, 54 суммы сумматоров 1, 2 мантиссы результата в прямом коде. При

5 сложении мантисс на выход 67 коммутатора 18 всегда передается значение суммы с выхода 53 сумматора 1. Коммутатор 18 может быть реализован на элементах 2И-ИЛИ. Узел 27 управления коммутатором уп0 равляет работой коммутатора 18, причем на его выходе 711 (722) формируется уровень логической единицы в случае необходимости пропуска на выход 67 коммутатора 18 информации с выхода 53 суммы сумматора

5 1 (с выхода 54 суммы сумматора 2). Узел 27 управления коммутатором может быть реализован на двух элементах 2И и одном элементе 2ИЛИ,

Узел 24 обработки знаков формирует

0 управляющий сигнал на выходе 52 для сумматоров 1, 2 и 4, узлов 5, 6 и 7 предсказания кода нормализации, узла 26 поразрядного сравнения и узлов 27,29 управления коммутатором на основе анализа знаков мантисс

5 операндов (знаки поступают на входы 34 и 35 устройства) и сигнала режима работы, поступающего на вход 36 устройства, а также формирует знак мантиссы результата, дополнительно используя значение управ0. ляющего сигнала на выходе 45 заема вычи- тателя 8 и значения выходных переносов сумматоров f, 2 на выходах 62, 63 соответственно. Узел 24 обработки знаков может быть реализован на элементах И, ИЛИ, НЕ

5 и ИСКЛЮЧАЮЩЕЕ ИЛИ 3.1

Узлы 5,6 предсказания кода нормализации, коммутатор 19 и узел 28 управления коммутатором обеспечивают предсказание кода нормализации для мантиссы результа0 та, формируемой в прямом коде. Узлы 5, 6 предсказания кода нормализации могут быть реализованы так же, как в прототипе 5. Узлы 5, 6 предсказания кода нормализации на основе функций генерации и транзита

5 переносов предсказывают коды нормализации мантисс, формируемых на выходах 53, 54 сумматоров 1, 2 соответственно, причем код нормализации предсказывается с точностью до единицы младшего разряда только для мантиссы результата, формируемой в

прямом коде (получаемый код нормализации либо равен истинному, либо больше его на единицу младшего разряда). Код нормализации для мантиссы, формируемой в дополнительном коде, предсказывается неверно, однако он в дальнейшем в устройстве не используется, т.к. не передается на выход 68 коммутатора 19. При сложении мантисс двух операндов (операнды могут быть как нормализованными, так и ненор- мализованными) код нормализации мантиссы результата можно определить по функциям транзита переноса с точностью

до единицы младшего разряда (предсказанный код равен истинному либо боль- ше его на единицу младшего разряда). При вычитании мантисс двух операндов функции генерации переноса используются для формирования кода маски, а код нормализации мантиссы результата определяется по маскированным функциям транзита переноса с точностью до единицы младшего разряда(лредсказанный код равен истинно му, либо больше его на единицу младшего разряда).

Коммутатор 19 предназначен для выбора с выходов 64, 65 узлов соответственно 5, 6 предсказанного кода нормализации мантиссы в прямом коде. Коммутатор 19 может быть реализован на элементах 2И-2ИЛИ.

Узел 28 управления коммутатором (фиг.5) управляет работой коммутатора 19, причем на его выходе 73т (732) формируется уровень логической единицы в случае необходимости пропуска на выход 68 коммутато- ра 19 информации с выхода 64 узла 5 (с выхода 65 узла 6). При выполнении операций сложения-вычитания без нормализации. мантиссы результата на вход 37 устройства поступает уровень логического нуля, под действием которого на выходах 73i, 732узла 28 формируются нулевые уровни. В этом случае на выход 68 коммутатора 19 выдает- ся нулевая информация независимо от значений на выходах 64, 65 узлов 4, 5. Узел 28 управления коммутатором может быть реализован на двух элементах 2И, как это показано на фиг.5.

Сдвигатель 13, коммутатор 20 и узел 29 управления коммутатором обеспечивают выполнение нормализующего сдёига мантиссы результата.

Сдвигатель 13 выполняет сдвиг влево мантиссы результата, поступающей с выхода 67 коммутатора 18,.по коду нормализации, поступающему с выхода 68 коммутатора 1.9. Сдвигатель 13, как и сдви- гатель 12, может быть реализован известными способами

Коммтуатор20 выполняет корректирующий сдвиг мантиссы результата вправо на один разряд (на тетраду) в случае нарушения нормализации влево либо при сложении мантисс на сумматорах 1, 2 (значения переносов на выходах 62, 63 равны 1 при значении уровня логического сигнала на выходе 52 узла 24 равном О) либо при нормализирующем сдвиге на сдвигателе 13 из-за неправильно предсказанного кода нормализации (на выходе 70 старшего дополнительного разряда сдвигателя 13 сформирован уровень логической единицы), при этом в старший разряд мантиссы результата со входа 36 устройства вводится код 0001. В противном случае информация через коммутатор проходит транзитом. Коммутатор 20 может быть реализован на элементах И, ИЛИ, НЕ.

Узел 29 управления коммутатором управляет работой коммутаторов 20, 21, причем в случае необходимости корректирующего сдвига мантиссы вправо на шест- надцатеричный разряд (на одну тетраду) на вход коммутатора 21 передается результат с выхода 78 вычитателя 11. Узел 29 управления коммутатором может быть реализован на элементе 2И и элементе 2ИЛИ 3.

Сумматор 3, вычитатели 10, 11 и коммутатор 21 обеспечивают быстрое внесение корректирующей поправки в порядок результата при выполнении нормализующего сдвига влево мантиссы на сдвигателе 13 л корректирующего сдвига вправо мантиссы на коммутаторе 20.

Сумматор 3 предназначен для внесений в порядок результата корректирующей поправки -Н, которая необходима при нарушении нормализации влево мантиссы результата либо при сложении мантисс на сумматорах 1, 2 либо при нормализирующем сдвиге на сдвигателе 13 в связи с неточным предсказанием кода нормализации. Сумматор 3 может быть построен любым из известных способов.

Вычитатель 10 вычитает из большего порядка операндов, поступающего с выхода 49 коммутатора 16, значение кода нормализации, поступающего с выхода 68 коммутатора 19.

Вычитатель 1 вычитает из большего порядка операндов с учетом его предваритель- ной поправки на +1 в сумматоре 3, значение кода нормализации, поступающее с выхода 68 коммутатора 19.

Вычитатели 10, 11 могут быть реализованы различными способами, например на сумматорах с инверторами.

Коммутатор 21 предназначен для выдачи на выход 41 устройства конечного значения порядка результата либо с выхода 77 вычитателя 10, либо с выхода 78 вычитателя 11 под управлением сигнала, сформированного на выходе 75 узла 29 управления коммутатором. Коммутатор 21 может быть реализован на элементах 2И-2ИЛИ.

Сумматор 4, узел 7 предсказания кода нормализации, коммутаторы 22,23, узел 25 сравнения четностей и узел 26 поразрядного сравнения обеспечивают полный контроль устройства. Сумматор 4 и узел 7 Предсказания кода нормализации предназначены для формирования дублирующих результатов для мантисс результатов, получаемых на выходах соответственно 67 и 68 коммутаторов 18 и 19, При сложении ман- тисс операндов фактически дублируется работа обоих сумматоров 1, 2 и узлов 5, 6 Предсказания кода нормализации (то есть в устройстЁе осуществляется троирование), а при вычитании - только работа одного из сумматоров 1 и 2. на выходе которого результат сформирован в прямом коде, и соответствующего ему узла предсказания кода нормализации.

Сумматор 4 предназначен для сложения-вычитания мантисс операндов, поступающих на его входы с выходов 79, 80 коммутаторов соответственно 22, 23. При вычитании мантисс на выход 79 всегда подается большая по модулю мантисса операнда, а на выход 80 - меньшая по модулю мантисса операнда, поэтому на выходе 55 сумматора 4 результат всегда будет положительный в прямом коде. При сложении мантисс порядок их поступления на входы сумматора 4 произвольный Режим работы Сумматора 4 определяется уровнем логического, сигнала, поступающего на его вход режима с выхода 52 узла 24 обработки знаков. Сумматор 4 может быть построен лю- Фым из известных способов.

Узел 7 предсказания кода нормализации обеспечивает предсказание дублирующего кода нормализации для мантиссы результата, формируемого на сумматоре 4, Он по построению и функционированию аналогичен узлам 5, 6 предсказания кода Нормализации.

Коммутаторы 22,23 управляются сигналом с выхода 72 узла 27 управления коммутатором. Коммутаторы 22, 23 могут быть реализованы на элементах 2И-2ИЛИ, как показано на фиг.З для коммутатора 22.

При вычитании мантисс коммутатор 22 предназначен для выбора с выхода 48 коммутатора 15 илил выхода 51 сдвигателя 12 большей по модулю мантиссы опернадов, а коммутатор 23 - для выбора с выхода 48 коммутатора 15или выхода 51 сдвигателя 12

меньшей по модулю мантиссы операндов. При сложении мантисс коммутатор 22 всегда пропускает, например, мантиссу с выхода 48, а коммутатор 23 - с выхода 51. 5Узел 25 сравнения четностей предназначен для контроля сдвигатеяя 13 и коммутатора 20 путем сравнения предсказанной и фактической четностей мантиссы результата. Предсказанная .четность мантиссы

0 результата определяется четностью результата на выходе 67 коммутатора 18 (перенос учитывается только при сложении мантисс сигналом на выходе 74 узла 29 управления коммутатором). Предсказанная четность

5 формируется на выходе 85 узла 82 свертки по модулю два (фиг.З). Фактическая четность результата формируется на выходе 86 узла 83 свертки по модулю два. Сравнение фактической и предсказанной четностей ре0 зультата производится в узле 84 свертки по модулю два.

Узел 26 поразрядного сравнения предназначен для контроля функционирования сумматоров 1, 2, узлов 5, 6 предсказания

5 кода нормализации и коммутаторов 18, 19 при сложении-вычитании мантисс операндов путем поразрядного сравнения значения мантиссы результата на выходе 67 коммутатора 18 и дублирующего значения

0 мантиссы результата на выходе 55 сумматора 4, значения предсказанного кода нормализации на выходе 68 коммутатора 19 и дублирующего значения предсказаного кода нормализации на выходе 66 узла 7 пред5 сказания кода норализацми, а также сравнения сигналов переноса на выходах 62,63 сумматоров 1,2с учетом управляющего сигнала на выходе 52 узла 24 обработки знаков Узел 26 поразрядного сравнения

0. может быть реализован в соответствии с фиг.4.

Устройство для сложения-вычитания чисел с плавающейзапятой работает следующим образом.

5

На входы 30, 31 устройства поступают значения мантисс первого и второго операндов соответственно. На входы 32,33 устройства поступают значения порядков

0 первого и второго операндов соответственно, На входы 34, 35устройства поступают значения знаков мантисс первого и второго операндов соответственно. На вход 36 режима устройства поступает уровень

5 логического нуля при выполнении олера- . ции сложение и уровень логической единицы - при выполнении операции вычитание. Исходные операнды могут быть как нормализованными, так и ненормализованными

Вычитатели 8. 9 определяют разность между порядками первого и второго операндов. На выходе 45 вычитателя 8 формируется уровень логического нуля при большем порядке первого операнда, и уровень логической единицы - при большем порядке второго операнда. Под управлением сигнала на выходе 45 вычитателя 8 коммутаторы 14,15 пропускают на свои выходы 47, 48 мантиссы операндов с меньшим и с большим порядками соответственно, коммутатор 16 пропускает на выход 49 больший порядок, а коммутатор 17 - положительную разность порядков операндов в прямом коде, которая далее поступает на вход величины сдвига сдвигателя 12, на котором производится выравнивающий порядки операндов сдвиг вправо мантиссы операнда с меньшим порядком.

Узел 24 в соответствии с информацией на входах 34-36 формирует на выходе 52 уровень логического нуля (при неободимо- сти выполнения сложения мантисс операндов) или логической единицы (при необходимости выполнения вычитания мантисс операндов).

Под управлением сигнала на выходе 52 узла 24 в сумматорах 1, 2 начинается сложение (вычитание) мантисс операндов, а параллельно в узлах 5, б предсказания кода нормализации по зйач енийм пор йГ|5йдных функций транзита переноса, поступающих с выходов59,60 сумматоров 1,2 и замаскированных с учетом значений поразрядных функций генерации переноса, поступающих с выходов 56, 57 сумматоров 1, 2, формируются два кода нормализации, котоыре совпадают при сложении мантисс (эти коды равны истинному или больше его на единицу младшего разряда). При сложении мантиссы результата на выходах 53, 54 сумматоров 1, 2 формируются всегда в прямом коде. При вычитании на одном из сумматоров мантисса результата формируется в прямом коде, а на другом сумматоре - в дополнительном коде. Код нормализации, предсказанный для мантиссы, формируемой в прямом коде, точен или больше на единицу истинного. Код нормализации, предсказанный для мантиссы, формируемой в дополнительном коде, неправильный и в дальнейшем не используется.

При1 вычитании мантисс в зависимости от формируемых на выходах 62, 63 сумматоров 1,2 уровней логических сигналов коммутаторы 18, ,19 под управлением узлов 27,28 управления коммутатором пропускают на выходы 67,68 мантиссу результата, сформированную в прямом коде и ее предсказанный код нормализации соответственно,

узел 24 формирует значение знака мантиссы результата, которое поступает на выход 42 устройства. При сложении мантисс коммутаторы 18, 19 под управлением узлов 27,

2.8 управления коммутатором пропускают на выходы 67,68 мантиссу результата, сформированную в прямом коде, с выхбда 53 сумматора 1 и ее предсказанный код нормализации с выхода 64 узла 5 предсказания

0 кода нормализации соответственно.

В случае выполнения операции сложения (вычитания) без нормализации (на входе 37 разрешения нормализации устройства в этом случае присутствует уровень логиче5 ского нуля) на выходе 68 коммутатора 19 формируется нулевой код нормализации мантиссы результата.

На сдвигателе 13 выполняется нормализирующий сдвиг мантиссы результата, по0 ступающей с выхода 67 коммутатора 18 влево на величину предсказанного кода нормализации, поступающего на вход величины сдвига сдвигателя 13 с выхода 68 коммутатора 19.

5 Параллельно с работой сдвигателя 13 на вычитателях 10, 11 из значения большего порядка операндов (больший порядок сформирован на выходе 49 коммутатора 16) вь- читается значение предсказанного на

0 выходе 68 коммутатора 19 кода нормализации, причем сумматор 3 осуществляется корректирующую поправку +1.у

В случае отсутствия нарушения нормализации мантиссы результата влево под

5 управлением узла 29 управления коммутатором коммутатор 20 пропускает на выход 40 устройства значение мантиссы результата с выхода 69 сдвигателя 13, а коммутатор 21 пропускает на выход 41 устройства зна0 чение порядка результата с выхода 77 вычитателя 10. .

В случае нарушения нормализации мантиссы результата влево (это происходит, когда на выходе 62 сумматора 1 формирует5 ел уровень логической единицы при установленном на выходе 52 узла 24 уровне логического нуляд или же когда на выходе 70 сдвигателя 13 формируется уровень логической единицы вследствие неточного пред0 сказания кода нормализации), на выходе 75 узла 29 управления коммутатором формируется уровень логической единицы, под действием которого коммутатор 20 осуществляет корректирующий сдвиг впра5 во на одну шестнадцатиричную цифру (тетраду) значения мантиссы результата, поступающей с выхода 69 сдвигателя 13, с внесением в старшие разряды цифры 1 (тетрады 0001), а коммутатор 21 пропускает на выход 41 устройства значение порядка

результата с выхода 78 вычитателя 11 (порядок с корректирующей поправкой +1).

Контроль функционирования устройства осуществляется одновременно с выполнением в устройстве операции и организованы следующим образом.

По сигналу на выходе 52 узла 24 и сигналам с выходов 62, 63 сумматоров 1, 2 формируется сигнал на выходе 72 узла 27 управления коммутатором, под управлением которого коммутаторы 22,23 при вычитании мантисс пропускают на выходы 79, 80 соответственно большую и меньшую по модулю мантиссы операндов, а при сложении мантисс пропускают на выходы 79, 80 соответственно мантиссы операндов с выхода 48 коммутатора 15 и с выхода 51 сдвигателя 12.

Под управлением сигнала на выходе 52 узла 24 в сумматоре 4 начинается сложение (вычитание) мантисс операндов (при вычитании из большей по модулю мантиссы всегда вычитается меньшая по модулю), а параллельно в узле 7 предсказания кода нормализации по значениям поразрядных функций транзита переноса, поступающих с выхода 61 сумматора 4 и замаскированных с учетом значений поразрядных функций генерации переноса, поступающих с выхода 58 сумматора 4, формируется дублирующий код нормализации. Код нормализации, предсказанный для дублирующей мантиссы, формируемой всегда в прямом коде, точен или больше на единицу истинного. В прямом коде всегда формируется и дублирующая мантисса результата на выходе 55 сумматора 4.

В узел 26 поразрядного сравнения поступает информация с выходов 67, 68 коммутаторов 18, 19, с выходов 62, 63 сумматоров 1, 2, с выхода 55 сумматора 4 и с выхода 66 узла 7 предсказания кода нормализации. На группе 87 элементо в ИСКЛ ЮЧА- ЮЩЕЕ ИЛИ производится поразрядное сравнение значений мантиссы на выходе 67 коммутатора 18 и дублирующей мантиссы на выходе 55 сумматора 4. На группе 88 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ производится поразрядное сравнение выбранного на выходе 68 коммутатора 19 кода нормализации с дублирующим кодом нормализации на выходе 66 узла 7. На узле 89 свертки по модулю два производится свертка по модулю два значений переносов на выходах 62, 63 сумматоров 1,2с значением управляющего сигнала на выходе 52 узла 24. Сигналы несовпадения на выходах 91-93 объединяются на группе 90 элемнетов ИЛИ, выход 43г которой ялвяется вторым разрядом выхода 43 признака ошибки Таким образом,

сумматор 4, узел 7 предсказания кода нормализации, коммутаторы 23, 24 и узел 26 поразрядного сравнения осуществляют полный контроль сумматоров 1, 2, узлов 5, 6

5 предсказания кода нормализации и коммутаторов 18, 19.

Для осуществления контроля сдвигателя 13 и коммутатора 20 в узел 25 сравнения четностей поступает информация с выхода

0 67 коммутатора 18, с выхода 7-1 коммутатора 20 и с выхода 74 узла 29 управления коммутатором. В узле 82 свертки по модулю два формируется значение предсказываемой мантиссы результата. Фактическая чет5 ность мантиссы результата формируется на выходе 86 узла 83 свертки по модулю два на основании информации с выхода 71 коммутатора 20 (на выход 71 подается-и дополнительная цифра). Сравнение предсказанной

0 (выход 85 узла 82) и фактической (выход 86 узла 93) четностей мантиссы результата производится на узле 84 свертки по модулю два. Результат этого сравнения поступает на первый разряд 43ч выхода 43 признака

5 ошибки устройства.

Таким образом, в предлагаемом устройстве для сложения-вычитания чисел с плавающей запятой по сравнению с устройством-прототипом повышается достовер0 ность формируемых на выходе результатов за счет организации контроля вычитания мантисс (в прототипе осуществляется контроль только сложения мантисс), быстродействие устройства остается без изменения.

5

Формула изобретения

Устройство для сложения-вычитания чисел с плавающей запятой, содержащее три

0 сумматора, два узла предсказания кода нормализации, четыре вычитателя. два сдвигателя, восемь коммутаторов, три .узла управления коммутатором, узел обработки знаков, узел сравнения четностей и узел по5 разрядного сравнения, причем вход мантиссы первого операнда устройства соединен с первыми информационными входами первого и второго коммутаторов, вторые информационные входы которых соединены с

0 входом мантиссы второго операнда устройства, вход порядка первого операнда которого соединен с первым информационным входом третьего коммутатора, с входом уменьшаемого первого вычитателя и с вхо5 дом вычитаемого ётбрйго выч итателя, вход порядка второго операнда устройства соединен с вторым информационным входом третьего коммутатора, с входом вычитаемого первого вычитателя и с входом уменьшаемого второго вычитзтеля, выход второго

вычитателя соединен с первым информационным входом четвертого коммутатора, второй информационный вход которого соединен с выходом разности первого вычитателя, выход заема которого соединен с управляющими входами коммутаторов с первого по четвертый и с первым входом узла обработки знаков, второй, третий и четвертый входы которого соединены с входами знака мантиссы первого операнда, знака мантиссы второго операнда и режима устройства соответственно, первый и второй входы первого узла предсказания кода нормализации соединены с выходом функций генерации переноса и с выходом функций транзита переноса первого сумматора соответственно, первый и второй, входы второго узла предсказания кода нормализации соединены с выходом функций генерации переноса и с выходом функций транзита переноса второго сумматора соответственно, выход суммы первого сумматора соединен с первым информационым входом пятого коммутатора, выход суммы второго сумматора соединён с вторым информационным входом пятого коммутатора, выход первого узла предсказания кода нормализации соединен с первым информационным входом шестого коммутатора, выход второго узла предсказания кода нормализации соединен с вторым информационным входом шестого коммутатора, выход первого коммутатора соединен с информационным входом первого сдвигателя, вход величины сдвига которого соединен с выходом четвертого коммутатора, выход второго коммутатора соединен с первым входом первого сумматора, второй вход которого соединен с выходом первого сдвигателя и с первым входом второго сумматора, второй вход которого соединен с первым входом первого сумматора, вход уровня логической единицы устройства соединен с первым входом третьего сумматора, второй вход которого соединен с выхоДбмТретьего коммутатора и с входом уменьшаемого третьего вычитателя, вход вычитаемого которого соединен с входом вычитаемого четвертого вычитателл, выходом шестого коммутатора и с входом величины сдвига второго сдвигателя, информационный сход которого соединен с выходом пятого коммутатора, упраёляющий вход которого соединен с выходом первого узла управления коммутатором, первый выход второго сдвигателя соединен с первым информационным входом седьмого коммутатора, выход которого соединен с первым входом узла сравнения четнйстей, выход которого является выходом первого разряда признака ошибки устройства, выход мантиссы результата которого соединен с выходом старших разрядов седьмого коммутатора, второй информационный вход старших и младших разрядов которого соединен с входом константы

устройства и с первым выходом второго сдвигателя соответственно,выход знака мантиссы результата соединен с первым выходом узлз обработки знаков, пятый вход которого соединен с выходом переноса пер0 вого сумматора, с первыми входами первого и третьего узлов управления коммутатором и с первым входом узла поразрядного сравнения, управляющий вход которого соединен с вторыми входами первого и третьего

5 узлов управления коммутатором, с управляющими входами первого и второго узлов предсказания кода нормализации, с входами переносов первого и второго сумматоров, с входами режима первого и второго

0 сумматоров и с вторым выходом узла обработки знаков, шестой вход которого соеди-. нен с выходом переноса второго сумматора, с третьим входом первого узла управления коммутатором и с вторым входом узла по5 разрядного сравнения, выход которого является выходом второго разряда признака ошибки устройства, вход разрешения нормализации которого соединен с первым входом второго узла управления коммутатором, вы0 ход которого соединен с управляющим входом шестого коммутатора, второй вход узла сравнения четностей соединен с первым выходом третьего узла управления коммутатором, третий вход которого соединен с вторым

5 выходом второго сдвигателя, управляющий вход седьмого коммутатора соединен с вторым выходом третьего узла управления ком- мутатором и с управляющим входом восьмого коммутатора, первый информаци0 онный вход которого соединен с выходом третьего вычитателя, выход третьего сумматора соединен с входом уменьшаемого четвертого вычитателя, выход которого соединен с вторым информационным вхо5 дом восьмого коммутатора, выход которого является выходом порядка результата устройства, отличающееся тем, что, с целью повышения достоверности формируемых в устройстве результатов, оно допол0 нительно содержит четвертый сумматор, третий узел предсказания кода нормализации, девятый и десятый коммутаторы, причем первые информационные входы девятого и десятого коммутаторов соедине5 иы с выходом второго коммутатора, выход девятого коммутатора соединен с первым входом четвертого сумматора, второй вход которого соединен с выходом десятого коммутатора, вторые входы девятого и десятого коммутаторов соединены с выходом первого

сдвигателя, управляющие входы девятого и десятого коммутаторов соединены с выходом первого узла управления коммутатором и с вторым входом второго узла управления коммутатором, первый и второй входы третьего узла предсказания кода нормализации соединены с выходами функций генерации переноса и транзита переноса четвертого сумматора соответственно, выход суммы четвертого сумматора соединен с третьим входом узла поразрядного сравнения, четвер0

тый вход которого соединен с выходом пятого коммутатора и с третьим входом узла сравнения четностей, входы переноса и режима четвертого сумматора и управляющий вход третьего узла предсказания кода нормализации соединены с вторым выходом узла обработки знаков, выход третьего узла предсказания кода нормализации соединен с пятым входом,узла поразрядного сравнения, шестой вход которого соединен с выходом шестого коммутатора.

48 54

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для сложения и вычитания чисел с плавающей точкой | 1987 |

|

SU1481743A1 |

| Арифметическое устройство | 1984 |

|

SU1193661A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ | 1991 |

|

RU2006915C1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Устройство для суммирования нормализованных чисел с плавающей запятой | 1987 |

|

SU1418704A1 |

Изобретение относится к области вычислительной техники и может быть применено в высокопроизводительных системах обработки информации. Целью изобретения является повышение достоверности формируемых результатов устройства. Устройство содержит три сумматора, два сдвигателя, два узла предсказания кода нормализации, четыре вычитателя, восемь коммутаторов, три узла управления коммутатором, узел обработки знаков, узел сравнения четностей, узел поразрядного сравнения и введенные дополнительно четвертый сумматор, третий узел предсказания кода нормализации, девятый и десятый коммутаторы. 5 ил.

Фиг. Ч

Фиг 5

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1986 |

|

SU1376080A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР №1714587, кл.3 06 F 7/50 | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-12-30—Публикация

1991-02-25—Подача