Изобретение относится к автоматике и вычислительной технике и может быть использовано в радиометрической аппаратуре, устройствах синхронизации и цифровых синтезаторах частот.

Целью изобретения является повышение надежности преобразователя путем исключения нестабильности временного положения выходного сигнала.

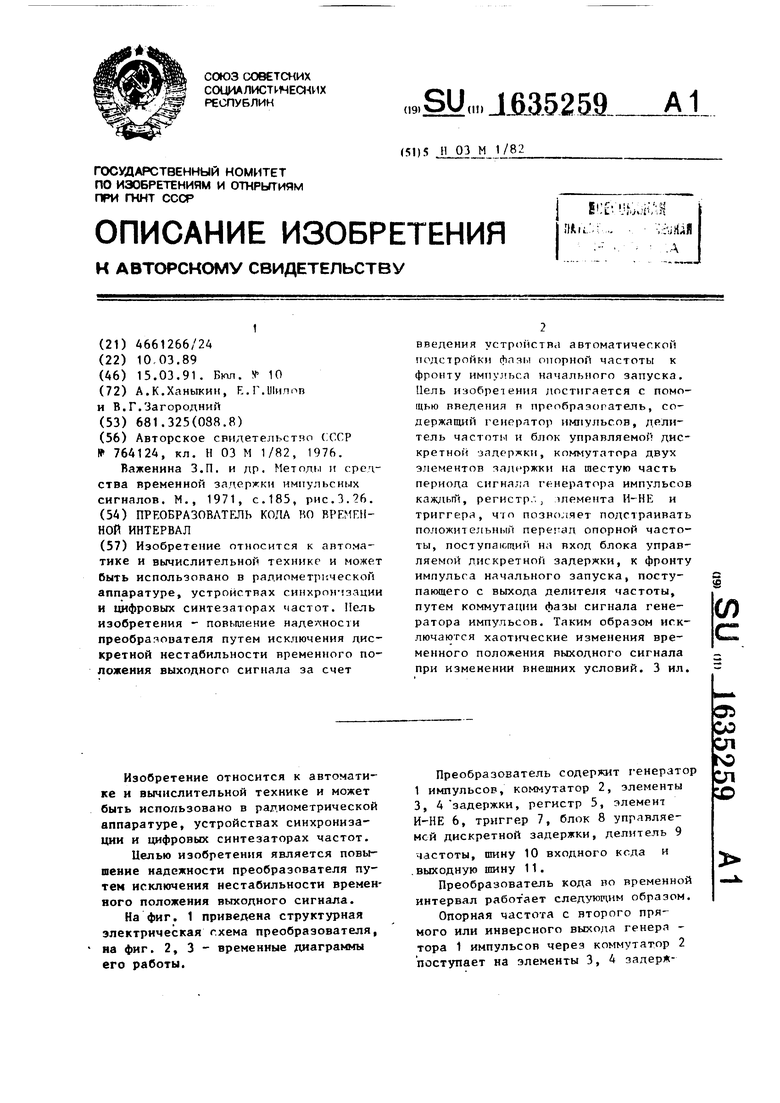

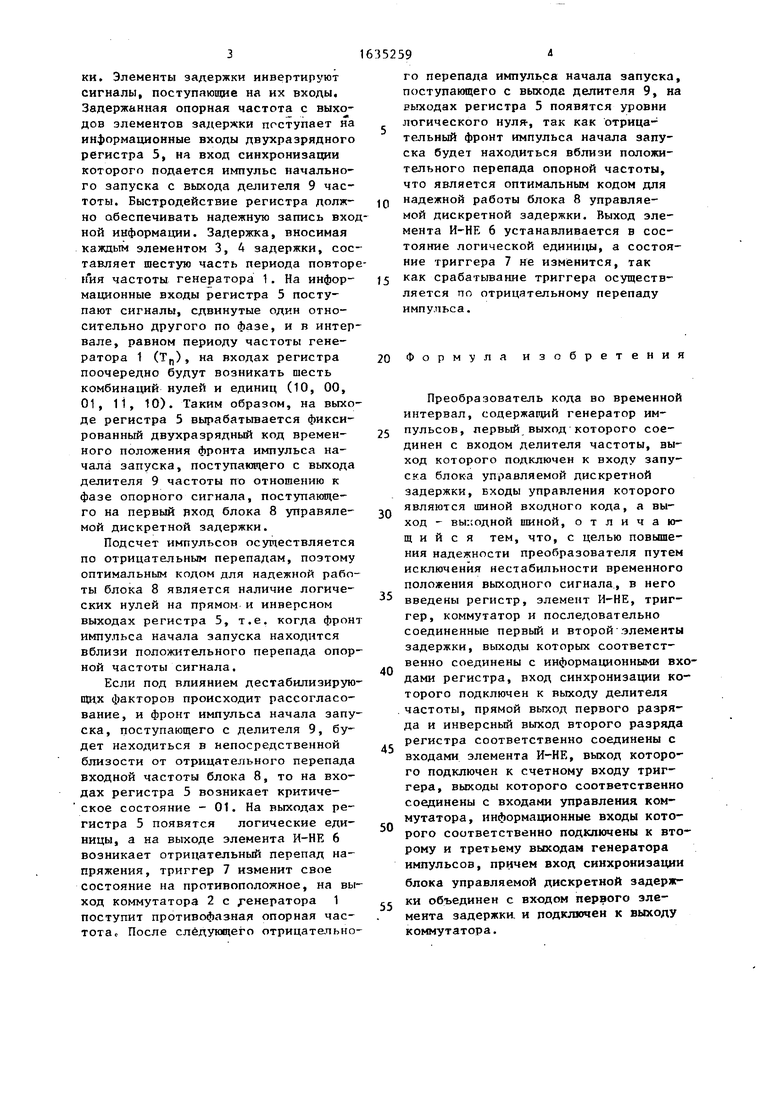

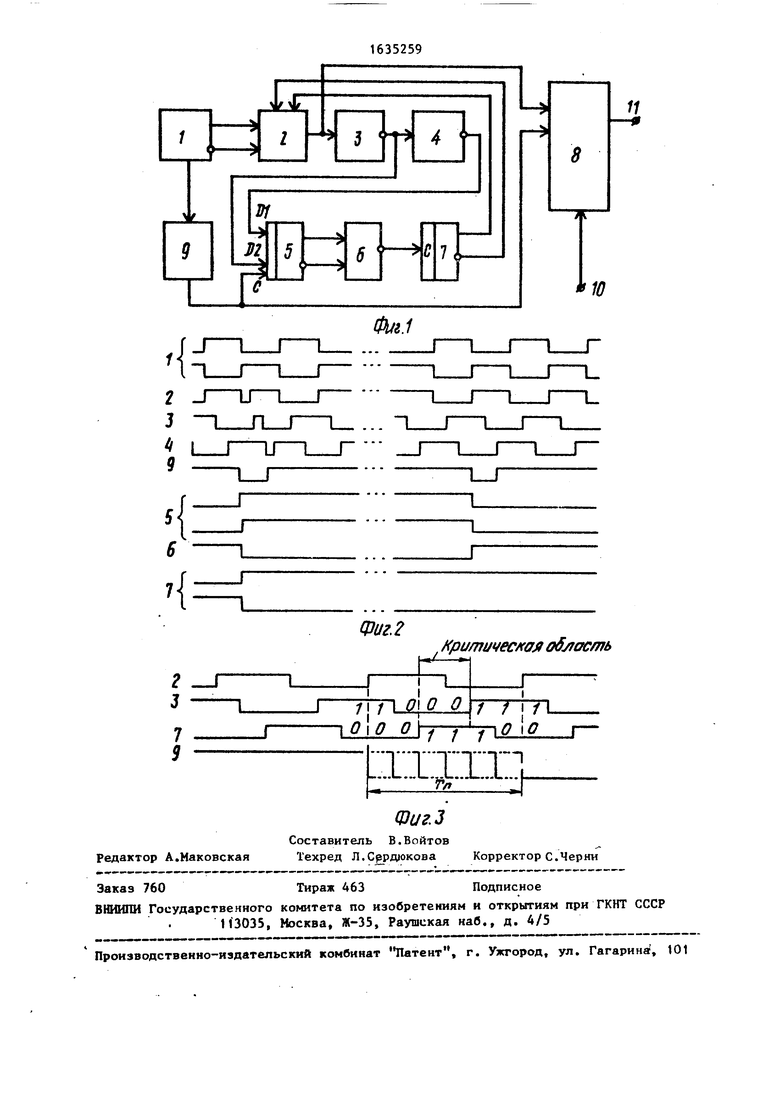

На фиг. 1 приведена структурная электрическая схема преобразователя, на фиг. 2, 3 - временные диаграммы его работы.

Преобразователь содержит генератор 1 импульсов, коммутатор 2, элементы 3, 4 задержки, регистр 5, элемент И-НЕ 6, триггер 7, блок 8 управляемой дискретной задержки, делитель 9 частоты, шину 10 входного кода и .выходную шину 11.

Преобразователь кода во временной интервал работает следующим образом.

Опорная частота с второго прямого или инверсного выхода генера - тора 1 импульсов через коммутатор 2 поступает на элементы 3, 4 задерж

ки. Элементы задержки инвертируют сигналы, поступающие на их входы. Задержанная опорная частота с выходов элементов задержки поступает на информационные входы двухразрядного регистра 5, на вход синхронизации которого подается импульс начального запуска с выхода делителя 9 частоты. Быстродействие регистра должно обеспечивать надежную запись вход ной информации. Задержка, вносимая каждым элементом 3, А задержки, составляет шестую часть периода повторения частоты генератора 1. На информационные входы регистра 5 поступают сигналы, сдвинутые один относительно другого по фазе, и в интервале, равном периоду частоты генератора 1 (Тп), на входах регистра поочередно будут возникать шесть комбинаций нулей и единиц (10, 00, 01, 11, 10). Таким образом, на выходе регистра 5 вырабатывается фиксированный двухразрядный код временного положения фронта импульса начала запуска, поступающего с выхода делителя 9 частоты по отношению к фазе опорного сигнала, поступающего на первый вход блока 8 управяле- мой дискретной задержки.

Подсчет импульсов осуществляется по отрицательным перепадам, поэтому оптимальным кодом для надежной работы блока 8 является наличие логических нулей на прямом и инверсном выходах регистра 5, т.е. когда фронт импульса начала запуска находится вблизи положительного перепада опорной частоты сигнала.

Если под влиянием дестабилизирующих факторов происходит рассогласование, и фронт импульса начала запуска, поступающего с делителя 9, будет находиться в непосредственной близости от отрицательного перепада входной частоты блока 8, то на входах регистра 5 возникает критическое состояние - 01. На выходах регистра 5 появятся логические единицы, а на выходе элемента И-НЕ 6 возникает отрицательный перепад напряжения, триггер 7 изменит свое состояние на противоположное, на выход коммутатора 2 с генератора 1 поступит противофазная опорная частота с После следующего отрицательного перепада импульса начала запуска, поступающего с выхода делителя 9, на выходах регистра 5 появятся уровни логического нуля-, так как отрицательный фронт импульса начала запуска будет находиться вблизи положительного перепада опорной частоты, что является оптимальным кодом для

надежной работы блока 8 управляемой дискретной задержки. Выход элемента И-НЕ 6 устанавливается в состояние логической единицы, а состояние триггера 7 не изменится, так

как срабатывание триггера осуществляется по отрицательному перепаду импупьса.

Формула изобретения

Преобразователь кода во временной интервал, содержащий генератор импульсов, первый выход которого соединен с входом делителя частоты, выход которого подключен к входу запуска блока управляемой дискретной задержки, входы управления которого являются шиной входного кода, а выход - выгодной шиной, отличающийся тем, что, с целью повышения надежности преобразователя путем исключения нестабильности временного положения выходного сигнала, в него

введены регистр, элемент И-НЕ, триггер, коммутатор и последовательно соединенные первый и второй элементы задержки, выходы которых соответственно соединены с информационными входами регистра, вход синхронизации которого подключен к выходу делителя частоты, прямой выход первого разряда и инверсный выход второго разряда регистра соответственно соединены с входами элемента И-НЕ, выход которого подключен к счетному входу триггера, выходы которого соответственно соединены с входами управления коммутатора, информационные входы которого соответственно подключены к второму и третьему выходам генератора импульсов, причем вход синхронизации блока управляемой дискретной задержки объединен с входом первого элемента задержка и подключен к выходу коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь код-временной интервал | 1989 |

|

SU1654980A1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Статистический анализатор конечной разности фазы | 1987 |

|

SU1422182A1 |

| Преобразователь кода во временнойиНТЕРВАл | 1978 |

|

SU809557A1 |

| Устройство стабилизации амплитуды видеосигнала | 1989 |

|

SU1748283A1 |

| Генератор ступенчатого напряжения | 1980 |

|

SU936404A2 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в радиометрической аппаратуре, устройствах синхрончзации и цифровых синтезаторах частот. Цель изобретения - повышение надедности преобразователя путем исключения дискретной нестабильности временного положения выходного сигнала за счет введения устройстве автоматической подстройки фазы опорной частоты к фронту импульса начального запуска. Цель изобретения достигается с помощью введения л преобраэогатель, содержащий генератор импульсов, делитель частоты и блок управляемой дискретной задержки, коммутатора двух элементов задержки на шестую часть периода сигнала генератора импульсов каждый, регистр.., элемента И-НЕ и триггера, что позволяет подстраивать положительный перегад опорной частоты, поступающий на вход блока управляемой дискретной задержки, к фронту импульса начального запуска, поступающего с выхода делителя частоты, путем коммутации фазы сигнала генератора импульсов. Таким образом исключаются хаотические изменения временного положения выходного сигнала при изменении внешних условий. 3 ил. € (Л

| Преобразователь двоичного кода во временной интервал | 1976 |

|

SU764124A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Важенина З.П | |||

| и др | |||

| Методы и средства временной задержки импульсных сигналов | |||

| М., 1971, с.185, рис.3.26. | |||

Авторы

Даты

1991-03-15—Публикация

1989-03-10—Подача