1

Изобретение относится к импульсной технике и предназначено для использования в телемеханике, связи и других системах передачи цифровой информации.

Известны декодирующие устройства, выполненные на базе регистров сдвига с логическими обратными связями , и известны комбинационные дешифраторы, которые выполняют по матричной схеме с применением логических элементов и с различным числом вхо-.

дов t lНаиболее совершенным является декодер, содержаиций последовательно соединенные, синхронизатор, распределитель и дешифратор, регистр, вы-полненный в виде последовательно с.оединенных первого элемента И, трех триггеров, первого сумматора по мог дулю два и второго элемента И,многовходовый элемент И, третий элемент И, элемент ИЛИ, вход которого соединен с выходами распределителя, а выход - С синхронизирующими входами -Триггеров регистра, нулевые выходы первого и третьего триггеров и единичный выход второго триггера регистра соединены с соответствующими входами многовхолового элемента И, выходом подключенного к первому входу третьего элемента И, выход второго элемента И соединен с выходом первого элемента И, выход второго триггера регистра подключен к одному из входов сумматора по модулю два, выходы диодной матрицы являются выходами устройства .21.

Однако при увеличении разрядности

10 кода и числа минимальных кодовых колец усложнятся построение элементов И, которые дешифрируют кодовые кольца, необходим отдельный регистр сдвига с К-ячейками, предназначен15ный только для дешифрации принятого кода. Декодирование принятой кодовой комбинации, т.е. выделение истинных информационных символов, это устройство производить не может,

20 и для этой цели требуется дополнительное оборудование.

Цель изобретения - упрощение устройства.

Поставленная цель достигается

25 тем, что в декодер, содержащий последовательно соединенные синхронизатор, первым входом подключенный к входной шине, распределитель и дешифратор, регистр, выполненный в виде 30 последовательно соединенных первого

элемента И, первого, второго и третего триггеров, первого сумматора п модулю два и второго элемента И, многовходовой элемент И, третий элемент И, элемент ИЛИ, вход которого соединен с выходами распределителя, а выход - с синхронизирующими входа,ми триггеров и регистра, нулевые вы ходы первого и третьего триггеров, а также единичный выход второго триггера регистра соединены с соответствующими входами многовходового элемента И, выходом подключенного к первому входу третьего элемента И выход второго элемента И соединен с выходом первого элемента И, выход второго триггера регистра подключен к одному из входов первого сумматора по модулю два, выход дешифратора является выходом устройства,содержит элемент сравнения, выполненный в виде последовательно соединенных четвертого элемента И, второго сумматора по модулю два и пятого элемента И, два управляющих триггера, причем первый -вход первого управляющего триггера соединен с одним из выходов распределителя, другой вход - с первым выходом синхронизатора, а первый и второй выходы - с первым входом первого элемента И и с объединенными первыми входами второго, четвертого и IlHToro элементов И соответственно, выход последнего соединен с вторым входом синхронизатора, третий вход которого подключен к выходу третьего элемента И и к соответствующим входам дешифратора, один из входов второго сумматора по модулю два подключен к выходу первого триггера регистра, второй выход синхронизатора соедине с вторыми входами первого и четвертого элементов И, вход второго управляющего триггера соединен с одни из выходов распределителя, а выход триггера подключен к одному из входов третьег-о элемента И.

Таким образом, упрощается наиболее громоздкая часть декодирующего устройства (дешифратор) за счет использования кольцевых свойств двоичных кодов.

Число К входовых элемектов И, определяемых в известном устройстве числом дешифрируемых колец, рав 2Н

цое са , где К - число информа

к

ционных символов кода, в предназначенном устройстве введено до минимума, т.е. до одного.

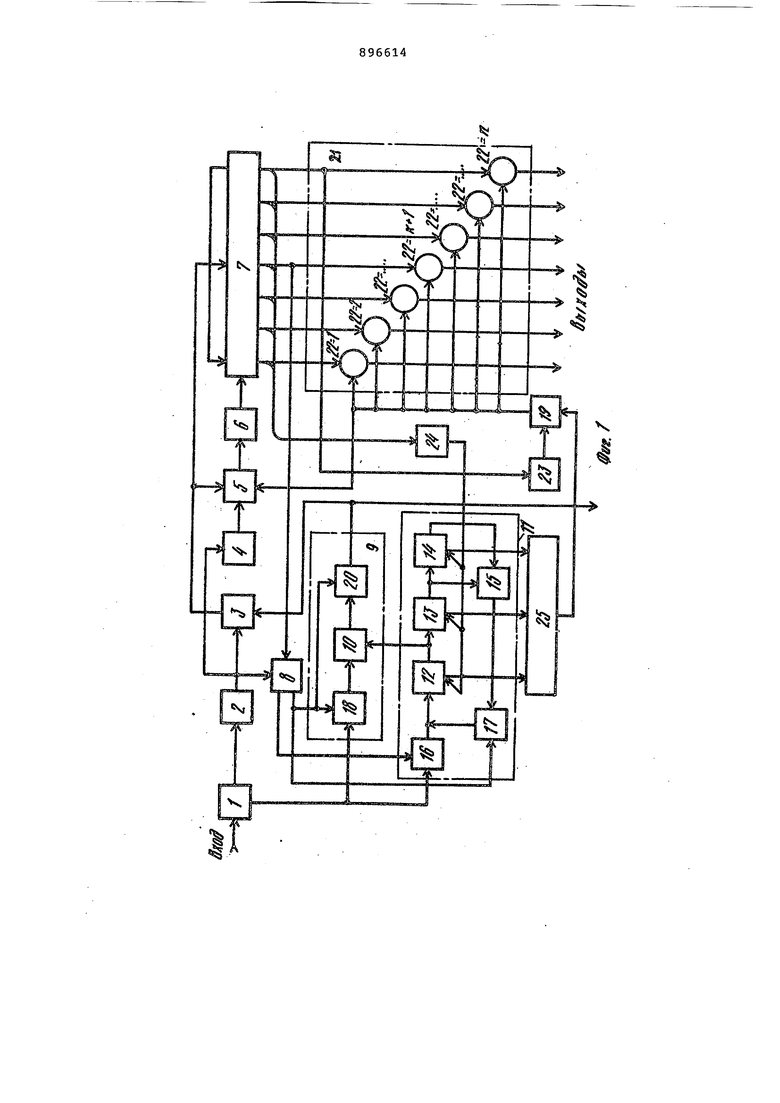

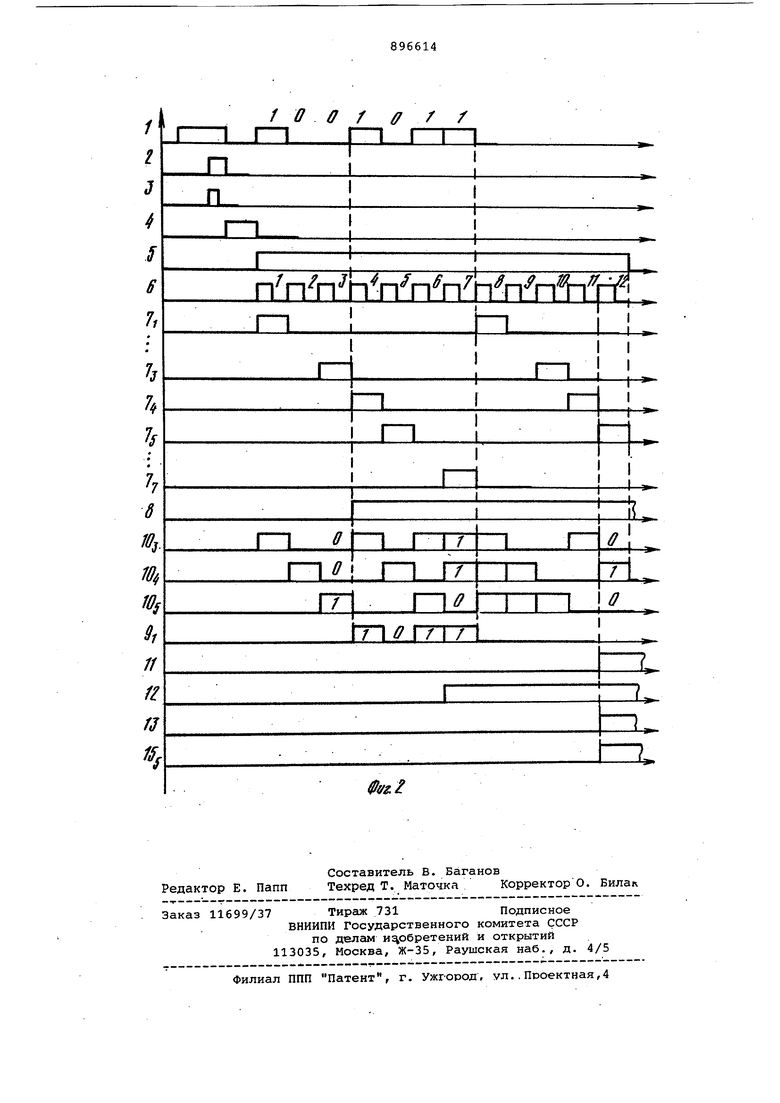

На фиг. 1 представлена схема декодера; на фиг1 2 - временная диаграмма его работы.

Предлагаемый декодер содержит входной блок 1, селектбр 2 пускового элемента, с01)асывакхций узел 3, фазорегулятор 4, пусковой уЗел 5, генерат ч) 6 импульсов, распределитель 7, первый, управлякнций триггер 8, элемент 9 сравнения, в состав которого входит сумматор 10 по модулю два, регистр 11 сдвиг-а с логической обратной связью, выполненный йа триггерах 12-14 и сумматоре 15 по модулю два, элементы И 16-20, дешифратор 21 на элементах И 22 (22-1,22-2...22-п), триггер 23,элемент ИЛИ 24, многовходовый элемент И 25.

Элементы 1-6 составляют схему синхронизатора 26.

После выделения синхронизирующего импульса и подготовки всей схемы к приему информации, которая производится с помощью селектора 2 пускового элемента и сбрасывающего узла 3 регулируется фаза начала работы спускового узла, по сигналу которого начинает работать генератор импульсов 6. При этом распределитель 7 выдает импульсы через элемент ИЛИ 24 которые являются тактовыми импульсами для регистра 11 с логической обратной связью. Поскольку первый управляющий триггер 8 подключен к селектору 2 и к распределителю 7, то по сигналу с селектор а 2 в начале цикла триггер 8 устанавливается в сотояние 1 и открывает элемент И 16, через который в регистр 11 под действием тактовых импульсов, поступающих в распределитель через элемент ИЛИ 24, записываются информационные символы принимаемой.кодовой комбинации. Сигналом с (К+1) ячейки распределителя первый триггер переводится в состояние О, при этом закрывается вход регистра сдвига (запирается элемент И 16) и открываются вход и выход элемента 9 сравг нения, т.е. отпираются элементы И 18 20 и замыкается цепь обратной связи в регистре 11 (открывается эл&лент И 17) .

Начиная с (К+1) такта работы распределителя, в регистре образуются проверочные символы, вычисляемые по принятым информационным. Эти символы с выхода первого триггера регистра подаются на элемент И 19, на второй вход которого поступают проверочные символы, принимаемые из линии связи.

При правильном приеме кодовой комбинации проверочные символы,вычисленные и принятые, совпадают, и сигнала защитного отказа не последует.

На такте работы распределителя сигналом с последней ячейки распределителя второйуправляющий триггер 23 устанавливается в состояние 1, т.е. открывается элемент И 19. При дальнейшей работе регистра сдвига на определенн 1 такте, номер которого зависит от положения символов кодовой комбинации в кодовом кольце, происходит срабатывание многовходового,элемента И 25, настроенного на опорную комбинацию кольца.Распределитель 7 импульсов при этом за (n-K+N) тактов, где п - длина кода, К - число информационных символов и N - номер информационной части кодовой комбинации в кольце, производит выбор выходной шины деоиифратора 21. Выходная шина дешифратора 21 возбуждается, так как на входах выбранног элемента И 22 i матрицы присутствуют два сигнала - один с распределителя 7, другой - с элемента И 1

.. Следовательно, весь процесс де.кодирования и дешифрирования зани- мает (n-K+N) тактов, плюс К тактов на прием информационной части. В итоге на обработку всей информации тратится (n+N) тактов работы устройства.

При приеме кодовой комбинации с ошибкой принятые и вычисленные проверочные символы не совпадают, и элемент сравнения выдает сигнал защитного отказа, по которому происходит -сброс всех триггеров в исходное состояние и формируется запрос по обратному каналу системы.

На чертеже приведена схема декодера, выполненного для циклического кода {7,3)-с провероч ным поли номом п(х) 1+х +х , Связи в регистре сдвига соответствуют виду этого полинома.

Многовходовый элемент И 25 настроен, на опорную кодовую комбинацию - 010-. Регистр 11 сдвига генерирует кодовое множество (см.таблицу) .

Работа устройства (фиг.2) поясняется временными диаграммами, гд для примера выбран случай правильного приема кодовой комбинации 100101 в которой первые три символа являются информационными, а последующие - проверочными.

Такты работы устройства обозначены на временной диаграмме генератора импульсов.

За п.ервые три такта происходит прием информационных символов в регистр сдвкга, а за последующие дерять тактов - сдвиг принятой информации до опорной комбинации.

Таким образом, за 12 тактов работы устройства информация декодируется и дешифрируется.

Формула изобретения

Декодер, содержащий последовательно соединенные синхронизатор,первым входом подключенный к входной шине, распределитель и дешифратор,регистр,

o выполненный в виде последовательно соединенных первого элемента И, первого, второго и третьего триггеров, первого сумматора по модулю два и второго элемента И, многовходовой

5 элемент И, третий элемент И, элемент ИЛИ, вход которого соединен с выходами распределителя, а выход-с синхронизирующими входами триггеров регистра, нулевые выходы первого

0 и третьего триггеров, а также единичный выход второго триггера регистра соединены с соответствующими входами многовходового элемента И,выходом подключенного к первому входу третьего элемента И,выход второго эле5мента И соединен с выходом первого элемента И,выход второго триггера регистра подключен к одному из входов первого сумматора по модулю два, выход дешифратора.является выходом

D устройства, отлич ающийся тем, что, с целью упрощения декодера, он содержит элемент сравнения, выполненный в виде последовательно соединенных четвертого элемента И,

5 второго сугчматора по модулю два и пятого элемента И, два управляющих триггера, причем первый вход первого управлякицего триггера соединен с одним из выходов распределителя,дру0гой вход - с первым выходом синхронизатора, а первый и второй В1аходы с первым входом первого элемента И и с объединенными первыми входами второго, четвертого и пятого элементов И соответственно, выход послед5него соединен с вторым входом синхронизатора, третий вход которого подключен к выходу третьего элемента И и к соответствующим входам дешифратора, один из входов второго

0 сумматора по модулю два подключен к выходу первого триггера регистра, второй выход синхронизатора соединен с вторыми входами первого и четвертого элементов .И, вход второго

5 управляющего триггера соединен с одним из выходов распределителя, выход триггера подключен к одному из входов третьего элемента И.

Источники информации,

О принятые во внимание при экспертизе

1.Шляпоберский В.И. Основы техники, передачи дискретных сообщений. М., Связь, 1973, с. 142.

2.Авторское свидетельство СССР № 263994, кл. G Об F 5/00, 1969.

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

| Система для передачи и приема цифровой информации | 1989 |

|

SU1637025A1 |

| Кодер | 1990 |

|

SU1783623A1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Устройство для приема телесигналов | 1981 |

|

SU1003127A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Устройство для исправления пакетных ошибок модульными кодами | 1988 |

|

SU1596465A1 |

| Пороговый декодер сверточного кода | 1986 |

|

SU1443180A1 |

| Декодер сверточного кода | 1986 |

|

SU1388998A1 |

Авторы

Даты

1982-01-07—Публикация

1978-12-13—Подача